# ARM Architecture Reference Manual Security Extensions Supplement

Copyright © 2004, 2005 ARM Limited. All rights reserved. ARM DDI 0309F

## **ARM Architecture Reference Manual**

Copyright © 2004, 2005 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

**Change History**

| Date          | Issue | Change                                                          |

|---------------|-------|-----------------------------------------------------------------|

| July 2004     | А     | Internal release only                                           |

| July 2004     | В     | First release                                                   |

| December 2004 | С     | Second release                                                  |

| April 2005    | Е     | Updated to incorporate corrections to errata                    |

| November 2005 | F     | Updated to incorporate corrections to errata. Non-confidential. |

#### **Proprietary Notice**

ARM, the ARM Powered logo, Thumb, and StrongARM are registered trademarks of ARM Limited.

The ARM logo, AMBA, Angel, ARMulator, EmbeddedICE, ModelGen, Multi-ICE, PrimeCell, ARM7TDMI, ARM7TDMI-S, ARM9TDMI, ARM9E-S, ETM7, ETM9, TDMI, STRONG, are trademarks of ARM Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith.

1. Subject to the provisions set out below, ARM hereby grants to you a perpetual, non-exclusive, nontransferable, royalty free, worldwide licence to use this ARM Architecture Reference Manual for the purposes of developing; (i) software applications or operating systems which are targeted to run on microprocessor cores distributed under licence from ARM; (ii) tools which are designed to develop software programs which are targeted to run on microprocessor core manufactured under licence from ARM; (iii) integrated circuits which incorporate a microprocessor core manufactured under licence from ARM.

2. Except as expressly licensed in Clause 1 you acquire no right, title or interest in the ARM Architecture Reference Manual, or any Intellectual Property therein. In no event shall the licences granted in Clause 1, be construed as granting you expressly or by implication, estoppel or otherwise, licences to any ARM technology other than the ARM Architecture Reference Manual. The licence grant in Clause 1 expressly excludes any rights for you to use or take into use any ARM patents. No right is granted to you under the provisions of Clause 1 to; (i) use the ARM Architecture Reference Manual for the purposes of developing or having developed microprocessor cores or models thereof which are compatible in whole or part with either or both the instructions or programmer's models described in this ARM Architecture Reference Manual; or (ii) develop or have developed models of any microprocessor cores designed by or for ARM; or (iii) distribute in whole or in part this ARM Architecture Reference Manual to third parties without the express written permission of ARM; or (iv) translate or have translated this ARM Architecture Reference Manual into any other languages.

3.THE ARM ARCHITECTURE REFERENCE MANUAL IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE. 4. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the ARM tradename, in connection with the use of the ARM Architecture Reference Manual or any products based thereon. Nothing in Clause 1 shall be construed as authority for you to make any representations on behalf of ARM in respect of the ARM Architecture Reference Manual or any products based thereon.

Copyright © 2004, 2005 ARM limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19

The right to use and copy this document is subject to the licence set out above.

## Contents ARM Architecture Reference Manual Security Extensions Supplement

## Preface

|           |         | About this manual<br>Using this manual<br>Conventions<br>Further reading<br>Feedback | . ix<br>x<br>xii |

|-----------|---------|--------------------------------------------------------------------------------------|------------------|

| Chapter 1 | Introdu | uction                                                                               |                  |

| •         | 1.1     | About the ARM Architecture Security Extensions                                       | 1-2              |

|           | 1.2     | Security state, Monitor mode, and the NS-bit                                         | 1-3              |

|           |         | NS attributes                                                                        |                  |

|           | 1.4     | Exception handling                                                                   | 1-6              |

|           | 1.5     | Switching between Secure and Non-secure contexts                                     | 1-7              |

|           |         | Memory accesses                                                                      |                  |

|           | 1.7     | Debug 1-                                                                             | -10              |

| Chapter 2 |         | rchitecture                                                                          |                  |

| -         | 2.1     | Processor modes                                                                      | 2-2              |

|           | 2.2     | Registers                                                                            | 2-4              |

|           |         | Program Status Registers                                                             |                  |

|           | 2.4                                                         | Exception model 2-7                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           | 2.5                                                         | ARM instruction set 2-19                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|           | 2.6                                                         | Security Extensions and VFP support 2-21                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Chapter 3 | Mem                                                         | ory and System Architecture                                                                                                                                                                                                                                                                                                                                                               |  |  |

| -         | 3.1                                                         | System control coprocessor 3-2                                                                                                                                                                                                                                                                                                                                                            |  |  |

|           | 3.2                                                         | Register 1, control registers 3-9                                                                                                                                                                                                                                                                                                                                                         |  |  |

|           | 3.3                                                         | Access to registers in Monitor mode 3-19                                                                                                                                                                                                                                                                                                                                                  |  |  |

|           | 3.4                                                         | Memory management unit 3-20                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           | 3.5                                                         | L1 caches                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|           | 3.6                                                         | Tightly coupled memory 3-43                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           | 3.7                                                         | L1 DMA                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Chapter 4 | Debug Architecture                                          |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Chapter 4 | Debu                                                        | ig Architecture                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Chapter 4 | <b>Debu</b><br>4.1                                          | •                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Chapter 4 |                                                             | IG Architecture<br>Overview of Security Extensions debug                                                                                                                                                                                                                                                                                                                                  |  |  |

| Chapter 4 | 4.1                                                         | Overview of Security Extensions debug         4-2           CP14 register 0, Debug ID Register         4-3                                                                                                                                                                                                                                                                                |  |  |

| Chapter 4 | 4.1<br>4.2                                                  | Overview of Security Extensions debug 4-2                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3                                           | Overview of Security Extensions debug       4-2         CP14 register 0, Debug ID Register       4-3         CP14 register 1, Debug Status and Control Register       4-4                                                                                                                                                                                                                 |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4                                    | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8                                                                                                                                                                                                   |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5                             | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8CP14 register 7, Vector Catch Register4-9                                                                                                                                                          |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                      | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8CP14 register 7, Vector Catch Register4-9CP14 registers 80-95: Breakpoint Control Registers4-12                                                                                                    |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7               | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8CP14 register 7, Vector Catch Register4-9CP14 registers 80-95: Breakpoint Control Registers4-12CP14 registers 112-127: Watchpoint Control Registers4-13                                            |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8        | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8CP14 register 7, Vector Catch Register4-9CP14 registers 80-95: Breakpoint Control Registers4-12CP14 registers 112-127: Watchpoint Control Registers4-13External debug interface4-14                |  |  |

| Chapter 4 | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Overview of Security Extensions debug4-2CP14 register 0, Debug ID Register4-3CP14 register 1, Debug Status and Control Register4-4CP14 register 6, Watchpoint Fault Address Register4-8CP14 register 7, Vector Catch Register4-9CP14 registers 80-95: Breakpoint Control Registers4-12CP14 registers 112-127: Watchpoint Control Registers4-13External debug interface4-14Debug event4-17 |  |  |

## Glossary

## Preface

This preface introduces the ARM Architecture Reference Manual, Security Extensions supplement. It contains the following sections:

- About this manual on page viii

- Using this manual on page ix

- *Conventions* on page x

- Further reading on page xii

- *Feedback* on page xiii.

## About this manual

The purpose of this manual is to describe the Security Extensions to the ARM<sup>®</sup> architecture. It is a supplement to the *ARM Architecture Reference Manual* (ARM DDI 0100), version F or later, and is intended to be used with it.

It is assumed that the reader is familiar with the ARM Programmers' Model (described in *ARM Architecture Reference Manual Part A*, chapter 2), and the memory system architecture support (described in *ARM Architecture Reference Manual Part B*). The System Coprocessor, Virtual Memory System Architecture, and Cache chapters are particularly relevant.

## Intended audience

This book is written for all developers designing:

- ARM processors with Security Extensions

- hardware using ARM processors with Security Extensions

- software for systems using ARM processors with Security Extensions.

## Using this manual

This manual is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an introduction to the purpose of the ARM Architecture Security Extensions, and an overview of how this purpose is achieved.

It also describes the relationship of Security Extensions with the memory system, memory management, exception handling and system debug.

#### Chapter 2 CPU Architecture

Read this chapter for details of the changes to the Programmer's Model and instruction set.

### Chapter 3 Memory and System Architecture

Read this chapter for details of the features added to the ARM Memory and System architecture as part of Security Extensions.

### Chapter 4 Debug Architecture

Read this chapter for details of the features added to the ARM Debug architecture as part of Security Extensions.

## Conventions

This manual employs typographic and other conventions intended to improve its ease of use.

### General typographic conventions

| typewriter     | Is used for assembler syntax descriptions, pseudo-code descriptions of instructions, and source code examples. In the cases of assembler syntax descriptions and pseudo-code descriptions, see the additional conventions below. |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | The typewriter font is also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudo-code descriptions of instructions and source code examples.     |

| italic         | Highlights important notes, introduces special terminology, and denotes internal cross-references and citations.                                                                                                                 |

| bold           | Is used for emphasis in descriptive lists and elsewhere, where appropriate.                                                                                                                                                      |

| SMALL CAPITALS | Are used for a few terms which have specific technical meanings. Their meanings can be found in the <i>Glossary</i> .                                                                                                            |

### Pseudo-code descriptions of instructions

A form of pseudo-code is used to provide precise descriptions of what instructions do. This pseudo-code is written in a typewriter font, and uses the following conventions for clarity and brevity:

- Indentation is used to indicate structure. For example, the range of statements that a for statement loops over, goes from the for statement to the next statement at the same or lower indentation level as the for statement (both ends exclusive).

- Comments are bracketed by /\* and \*/, as in the C language.

- English text is occasionally used outside comments to describe functionality that is hard to describe otherwise.

- All keywords and special functions used in the pseudo-code are described in the *Glossary*.

- Assignment and equality tests are distinguished by using = for an assignment and == for an equality test, as in the C language.

#### Assembler syntax descriptions

This manual contains numerous syntax descriptions for assembler instructions and for components of assembler instructions. These are shown in a typewriter font, and are as follows:

Any item bracketed by < and > is a short description of a type of value to be supplied by the user in that position. A longer description of the item is normally supplied by subsequent text. Such items often correspond to a similarly named field in an encoding diagram for an instruction. When the correspondence simply requires the binary encoding of an integer

|        | value or register number to be substituted into the instruction encoding, it is not described explicitly. For example, if the assembler syntax for an ARM instruction contains an item <pre><pre>Rn&gt;</pre> and the instruction encoding diagram contains a 4-bit field named Rn, the number of the register specified in the assembler syntax is encoded in binary in the instruction field.</pre>                                               |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | If the correspondence between the assembler syntax item and the instruction encoding is more complex than simple binary encoding of an integer or register number, the item description indicates how it is encoded.                                                                                                                                                                                                                                |

| { }    | Any item bracketed by { and } is optional. A description of the item and of how its presence or absence is encoded in the instruction is normally supplied by subsequent text.                                                                                                                                                                                                                                                                      |

| I      | This indicates an alternative character string. For example, LDM STM is either LDM or STM.                                                                                                                                                                                                                                                                                                                                                          |

| spaces | Single spaces are used for clarity, to separate items. When a space is obligatory in the assembler syntax, two or more consecutive spaces are used.                                                                                                                                                                                                                                                                                                 |

| +/-    | This indicates an optional + or - sign. If neither is coded, + is assumed.                                                                                                                                                                                                                                                                                                                                                                          |

| *      | When used in a combination like <immed_8> <math>*</math> 4, this describes an immediate value which must be a specified multiple of a value taken from a numeric range. In this instance, the numeric range is 0 to 255 (the set of values that can be represented as an 8-bit immediate) and the specified multiple is 4, so the value described must be a multiple of 4 in the range <math>4*0 = 0</math> to <math>4*255 = 1020</math>.</immed_8> |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

All other characters must be encoded precisely as they appear in the assembler syntax. Apart from { and }, the special characters described above do not appear in the basic forms of assembler instructions documented in this manual. The { and } characters need to be encoded in a few places as part of a variable item. When this happens, the long description of the variable item indicates how they must be used.

## System and debug coprocessors

This document refers to registers in coprocessors 14 (debug) and 15 (system configuration and control) using the following notation:

| CP14r <n></n> | refers to the <n>th CP14 register</n>  |

|---------------|----------------------------------------|

| CP15r <n></n> | refers to the <n>th CP15 register.</n> |

## **Further reading**

This section lists publications that provide additional information on the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda, and the ARM Frequently Asked Questions.

## **ARM** publications

This book is a supplement to, and must be read in conjunction with, the *ARM Architecture Reference Manual* (ARM DDI 0100), version F or later.

## Feedback

ARM Limited welcomes feedback on its documentation.

## Feedback on this book

If you notice any errors or omissions in this book, send email to errata@arm giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of the problem.

General suggestions for additions and improvements are also welcome.

Preface

## Chapter 1 Introduction

This chapter introduces the ARM® Architecture Security Extensions.

— Note —

The ARM Architecture Security Extension, its associated implementations and supporting software are commonly referred to as TrustZone Technology.

This chapter contains the following sections:

- About the ARM Architecture Security Extensions on page 1-2

- Security state, Monitor mode, and the NS-bit on page 1-3

- *NS attributes* on page 1-4

- *Exception handling* on page 1-6

- Switching between Secure and Non-secure contexts on page 1-7

- *Memory accesses* on page 1-8

- *Debug* on page 1-10.

## 1.1 About the ARM Architecture Security Extensions

ARM Architecture Security Extensions is an enhancement to the ARM architecture. It integrates hardware security features to facilitate the development of secure applications.

Security Extensions is based on a small number of fundamental principles:

- It defines a class of core state, that can be switched between Secure and Non-secure state. Most code runs in Non-secure state. Only trusted code runs in Secure state.

- It defines some memory as Secure memory. Secure memory can only be accessed by the core when the core is in Secure state.

- Entry into Secure state is strictly controlled.

- Exit from Secure state can only occur at programmed points.

- Debug is strictly controlled.

- Reset enters Secure state.

Exceptions are generally handled in a similar way to other ARM architectures. However, support is provided for some exceptions to be handled only by code running in Secure state.

## 1.2 Security state, Monitor mode, and the NS-bit

Security Extensions defines a processor mode, Monitor mode. Monitor mode is designed to provide a bridge between code running in Non-secure state and code running in Secure state.

For all modes except Monitor mode, the security state (Secure or Non-secure) is controlled by the *Non-Secure bit*, the NS-bit. The NS-bit is a bit in a register, the Secure Configuration Register (SCR). See *Secure Configuration Register* on page 3-11 for details.

In Monitor mode, the security state is always Secure, regardless of the state of the NS-bit.

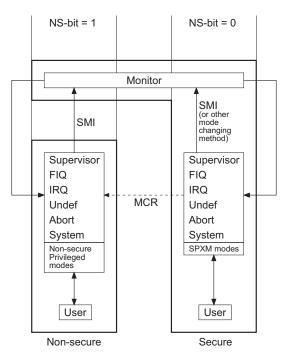

Figure 1-1 shows the normal routes of transfer of control between different modes and security states. The dashed transfer marked MCR is a possible but not normally recommended route.

## Figure 1-1 Security state, Monitor Mode, and the NS-bit

SPXM modes means Secure Privileged modes, Excluding Monitor mode.

— Note ———

It is important to distinguish Monitor mode (a processor mode) from Monitor debug-mode (a debug mode).

## 1.3 NS attributes

This document refers to several attributes that specify whether particular resources are Secure or Non-secure. In all cases, the value of the attribute has the following meanings:

0 Secure

1 Non-secure.

Primary NS attributes are architecturally defined state maintained in various system locations. These are shown in Table 1-1.

#### Table 1-1 Primary NS attribute definitions

| NS attribute | Description                                                                                                                      | Location                 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| NS-bit       | Determines NS-state, except in Monitor mode. In Monitor mode, controls whether the core accesses Secure or Non-secure resources. | CP15 r1 SCR[0]           |

| NS-dma       | Used by L1 DMA requests.                                                                                                         | CP15 r1 NSAC[18]         |

| NS-desc      | Security descriptor read by a page table walk.                                                                                   | Page tables              |

| NSTID        | Security identifier for TLB entry. Indicates whether Secure or<br>Non-secure page tables used to create the entry.               | TLB entries              |

| NS-tag       | Security tag for cache line.                                                                                                     | Cache lines              |

| NS-itcm      | Access control for Instruction (or unified) TCM.                                                                                 | CP15 r9 ITCM-NSAC[0]     |

| NS-dtcm      | Access control for Data TCM.                                                                                                     | CP15 r9 DTCM-NSAC[0]     |

| NS-prot      | Security identifier for external memory and peripherals.                                                                         | Bus Interface Unit (BIU) |

Derived NS attributes are defined by combinations of the primary attributes. These are shown in Table 1-2.

## Table 1-2 Derived NS attribute definitions

| NS attribute | Definition                                  | Derivation                                                                          |

|--------------|---------------------------------------------|-------------------------------------------------------------------------------------|

| NS-state     | Current execution state of the core         | Secure if (NS-bit==0) or (mode==Monitor)                                            |

| NS-req       | Security state of the memory access request | NS-state for core requests (unless explicitly stated differently), otherwise NS-dma |

| NS-attr      | Security attribute of the memory location   | if (MMU==OFF) then NS-req else if<br>(NS-state==0) then NS-desc else 1              |

## 1.3.1 Notes

- Some CP15 registers are banked, with both Secure and Non-secure versions.

- The NS-bit controls reads and writes to banked CP15 registers, for example for MRC and MCR instructions.

- NS-req and NS-dma form part of a request to determine which banked CP15 registers are used, for example during address translation.

- NS-state can be stored or calculated from NS-bit and the mode.

- NS-state and NS-bit can be different only in Monitor mode.

- NS-state is visible for debug purposes. It is bit[18] in the CP14 r1 *Debug Status and Control register* (DSCR).

- NS-desc is defined as stored in all page tables, both Secure and Non-secure. However, it is IGNORED for Non-secure page tables (because its value cannot be trusted).

- NS-desc may be cached in a TLB entry along with the rest of the descriptor after it has been fetched from a page table walk.

- NS-attr is required to access the appropriate memory, Secure or Non-secure, at any level of abstraction.

- NSTID only applies to systems with a TLB.

- NS-tag only applies to systems with caches.

- NS-dma only applies to systems with one or more TCMs.

## 1.3.2 Secure and Non-secure worlds

NS-state describes the running state of the system. The resources available, both core and system, are described as:

- the *Non-secure World* when NS-state==1

- the *Secure World* when NS-state==0.

## 1.4 Exception handling

On reset, Supervisor mode is entered with NS-state==0 and unrestricted access to the memory map.

Compatibility is a key feature of Security Extensions, allowing VMSAv6 compliant operating system ports to run without change.

The changes to exception handling are as follows:

- There is a new Monitor mode exception.

- There are options to take certain aborts normally, or to switch to Monitor mode to handle them. The options are configured by SCR[3:1] in CP15r1.

This applies to IRQ, FIQ, precise external aborts, and imprecise external aborts.

- There are options to prevent modification of the CPSR\_A and CPSR\_F bits by software when NS-state==1. This is configurable by SCR[5:4] in CP15r1.

- For register definitions see *Register 1, control registers* on page 3-9. For details of exception entry for all modes see *Exception model* on page 2-7. Only Secure Privileged modes can modify the secure control register (SCR) associated with these features.

## 1.5 Switching between Secure and Non-secure contexts

Software running predominantly in Monitor mode is responsible for switching safely between operations in Non-secure and Secure states. This software is called the *secure monitor code*.

It is the responsibility of the secure monitor code to stack and recover all register context associated with the ARM programmers' model during an NS-state transition.

Monitor mode has two banked general-purpose registers and a banked SPSR:

- R13\_mon, the Stack Pointer (SP)

- R14\_mon, the Link Register (LR)

- SPSR\_mon, the Saved Program Status Register.

These registers can only be read or written in Monitor mode. In addition, the SRS instruction can only be used with R13\_mon when NS-state==0.

— Note –

Hardware is not responsible for guaranteeing safe context switching. It assumes that the code running in Secure Privileged modes can be trusted.

## 1.6 Memory accesses

This section describes the secure memory access model for data, instructions, and address translations. In ARMv6, an ARM memory access can be initiated from two sources:

**Core** Instruction Read or Data Read/Write, cache writebacks, and page table walks.

L1 DMA Background task to fill TCMs from external memory.

For each request, the access can be for External Memory or L1 Memory (Caches or TCMs).

## 1.6.1 Security of memory accesses

NS-attr indicates the security of memory accesses. Values of NS-attr depend on two primary NS attributes and whether the MMU is enabled, as defined in Table 1-3.

| NS-req     | Secure M-bit <sup>a</sup> | NS-desc    | NS-attr    |

|------------|---------------------------|------------|------------|

| Non-secure | any                       | any        | Non-secure |

| Secure     | MMU On                    | Non-secure | Non-secure |

| Secure     | MMU On                    | Secure     | Secure     |

| Secure     | MMU Off                   | any        | Secure     |

#### Table 1-3 NS-attr values

a. Non-secure M-bit has no effect on NS-attr.

#### — Note —

For page table walks, NS-attr is defined to be NS-req of the transaction which caused the TLB miss and associated page table walk.

#### 1.6.2 Memory management

Memory management involves:

- Address Translation (stored as page tables in external memory) from virtual to physical address space.

- Memory Attributes, for example sharing, caching and protection.

Security Extensions adds an attribute to the VMSAv6 page tables. The attribute is called NS-desc, the PTE-NS bit. For every memory access, an address translation is required when the MMU is on. This requires one or more additional memory accesses from either:

#### External page table walk

A page table walk involves one or two memory accesses.

TLB A Translation Look-aside Buffer (TLB). This provides a cache of address translations.

There is no architectural requirement to implement a TLB. However, where a TLB exists, each entry must be associated with an NSTID to identify whether it was created by a Secure or Non-secure page table. It must also have information on the translated address:

NS-desc Raw value from Page Table. This cannot be trusted if NS-req==1.

If NS-desc is stored in TLB entries, it must be dynamically modified when it is read during a Non-secure address translation.

#### 1.6.3 Caches

Every cache line must include the NS-tag attribute. This can be considered as an additional address tag that must match NS-attr for a cache hit.

## 1.6.4 TCMs and L1 DMA

For ARMv6, both instruction and data TCM regions can be assigned to either value of NS-state. The architected DMA model that supports TCMs can be reserved exclusively for NS-state==0, or made available to the Non-secure world. See section *Tightly coupled memory* on page 3-43 and *L1 DMA* on page 3-46 for more details.

The security access registers associated with these features can only be modified in Secure Privileged modes.

#### 1.6.5 External memory accesses

All memory must be partitioned into Secure and Non-secure regions. The partitioning can be static or dynamic. It can be done at different levels of the memory hierarchy, with all resources beyond the chosen point allocated to the prescribed region. All memory accesses must be checked against NS-attr. NS-attr is exported to the rest of the system on external memory transactions as NS-prot. System infrastructures must support NS-prot to ensure correctness in, for example, external memory, peripherals, system caches, and page tables.

## 1.7 Debug

ARM processors support two types of debug:

- **Invasive** Debug of a halted system or running system, using watchpoints or breakpoints.

- **Non-invasive** Data observation of running system, for example, trace, performance monitoring, or PC sampling.

Debug and security have diametrically opposed objectives:

**Security** Aims to protect security critical data from being corrupted or leaked.

**Debug** Aims to reveal as much information as possible, using shortcuts not allowed in normal operation.

Security Extensions debug is strictly controlled to avoid compromising security:

- The architecture allows debug in all Non-secure states.

- A system can be configured to enable or disable both types of debug in Secure states. This can be done independently for User and Privileged modes.

System design must configure debug access appropriately for the security needs of the application.

## 1.7.1 Invasive debug

Invasive debug supports:

- Halting debug-mode. The core can be stopped for examination, then restarted.

- Monitor debug-mode. The foreground task can be stopped and started, but background tasks are not halted.

Invasive debug is controlled by the existing **DBGEN** input and two debug-enables for Security Extensions:

| DBGEN input  | Debug Enable. Required in ARMv6.                                                                                                                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SPIDEN input | Secure Privileged Invasive Debug Enable.                                                                                                        |

| SUIDEN bit   | Secure User Invasive Debug Enable. This bit is in the SDE register in CP15r1. See <i>Secure Debug Enable register</i> on page 3-15 for details. |

Table 1-4 shows a summary of invasive debug control.

#### Table 1-4 Invasive debug control

| DBGEN <sup>a</sup> | SPIDEN | SUIDEN | Secure Privileged modes | Secure User<br>mode | All Non-secure<br>modes |

|--------------------|--------|--------|-------------------------|---------------------|-------------------------|

| 0                  | Х      | Х      | Disabled                | Disabled            | Disabled                |

| 1                  | 0      | 0      | Disabled                | Disabled            | Enabled                 |

| 1                  | 0      | 1      | Disabled                | Enabled             | Enabled                 |

| 1                  | 1      | X b    | Enabled                 | Enabled             | Enabled                 |

a. This input is called **DBGEN**, not **IDEN**, for compatibility with previous ARM cores.

b. **SPIDEN** = 1 overrides SUIDEN = 0. This enables debug in Secure User mode.

## 1.7.2 Non-invasive debug

Non-invasive debug allows data observation, but does not allow halting, or any alteration to state. This allows for the following:

- Tracing, for example, ETM.

- Performance monitoring.

- External PC sampling.

Non-invasive debug is controlled by three debug-enables:

| NIDEN input   | Non-Invasive Debug Enable. Optional input, recommended.                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| SPNIDEN input | Secure Privileged Non-Invasive Debug Enable.                                                                                                        |

| SUNIDEN bit   | Secure User Non-Invasive Debug Enable. This bit is in the SDE register in CP15r1. See <i>Secure Debug Enable register</i> on page 3-15 for details. |

Table 1-5 shows a summary of non-invasive debug control.

#### Table 1-5 Non-invasive debug control

| NIDEN <sup>a</sup> | SPNIDEN | SUNIDEN | Secure Privileged modes | Secure User<br>mode | All Non-secure<br>modes |

|--------------------|---------|---------|-------------------------|---------------------|-------------------------|

| 0                  | Х       | Х       | Disabled                | Disabled            | Disabled                |

| 1                  | 0       | 0       | Disabled                | Disabled            | Enabled                 |

| 1                  | 0       | 1       | Disabled                | Enabled             | Enabled                 |

| 1                  | 1       | X b     | Enabled                 | Enabled             | Enabled                 |

a. Optional input.

b. **SPNIDEN** = 1 overrides SUNIDEN = 0. This enables debug in Secure User mode.

## Chapter 2 CPU Architecture

This chapter describes the changes to the CPU architecture introduced with Security Extensions. It contains the following sections:

- Processor modes on page 2-2

- *Registers* on page 2-4

- Program Status Registers on page 2-5

- Exception model on page 2-7

- ARM instruction set on page 2-19

- Security Extensions and VFP support on page 2-21.

## 2.1 Processor modes

All the modes in earlier ARM<sup>®</sup> architectures exist in both Secure and Non-secure states (NS-state==0 and NS-state==1). There is an additional mode, Monitor mode.

Table 2-1 shows the modes.

| Processor  | Mode | Description                                          |

|------------|------|------------------------------------------------------|

| User       | usr  | Normal program execution mode                        |

| FIQ        | fiq  | Supports high-speed data transfer or channel process |

| IRQ        | irq  | Used for general-purpose interrupt handling          |

| Supervisor | svc  | Protected mode for the operating system              |

| Abort      | abt  | Implements virtual memory or memory protection       |

| Undefined  | und  | Supports software emulation of hardware coprocessors |

| System     | sys  | Runs privileged operating system tasks               |

| Monitor    | mon  | Runs the secure monitor kernel                       |

#### Table 2-1 Processor modes

Monitor mode is a Privileged mode. In Monitor mode, the processor is always in Secure state (NS-state = 0).

Monitor mode is entered when a software monitor interrupt (SMI) instruction is executed, or any of the following exceptions is trapped in the secure monitor:

- FIQ

- IRQ

- external abort.

In Secure Privileged modes, it is also possible to change directly to Monitor mode by modifying the mode bits in the CPSR, for details see *PSR mode bits* on page 2-5.

Table 2-2 shows the state and mode structure.

| Modes      | Privilege  | Processor state  |              |

|------------|------------|------------------|--------------|

|            |            | NS-bit = 1       | NS-bit = 0   |

| User       | User       | Non-secure state | Secure state |

| FIQ        | Privileged | Non-secure state | Secure state |

| IRQ        | Privileged | Non-secure state | Secure state |

| Supervisor | Privileged | Non-secure state | Secure state |

| Abort      | Privileged | Non-secure state | Secure state |

| Undefined  | Privileged | Non-secure state | Secure state |

| System     | Privileged | Non-secure state | Secure state |

| Monitor    | Privileged | Secure state     | Secure state |

Table 2-2 Processor states and modes

## 2.2 Registers

Security Extensions introduces two banked general-purpose registers and a banked SPSR. These three registers are highlighted in Table 2-3.

| User | System | Supervisor | Abort    | Undefined | Interrupt | Fast<br>interrupt | Monitor  |

|------|--------|------------|----------|-----------|-----------|-------------------|----------|

| R0   | R0     | R0         | R0       | R0        | R0        | R0                | R0       |

| R1   | R1     | R1         | R1       | R1        | R1        | R1                | R1       |

| R2   | R2     | R2         | R2       | R2        | R2        | R2                | R2       |

| R3   | R3     | R3         | R3       | R3        | R3        | R3                | R3       |

| R4   | R4     | R4         | R4       | R4        | R4        | R4                | R4       |

| R5   | R5     | R5         | R5       | R5        | R5        | R5                | R5       |

| R6   | R6     | R6         | R6       | R6        | R6        | R6                | R6       |

| R7   | R7     | R7         | R7       | R7        | R7        | R7                | R7       |

| R8   | R8     | R8         | R8       | R8        | R8        | R8_fiq            | R8       |

| R9   | R9     | R9         | R9       | R9        | R9        | R9_fiq            | R9       |

| R10  | R10    | R10        | R10      | R10       | R10       | R10_fiq           | R10      |

| R11  | R11    | R11        | R11      | R11       | R11       | R11_fiq           | R11      |

| R12  | R12    | R12        | R12      | R12       | R12       | R12_fiq           | R12      |

| R13  | R13    | R13_svc    | R13_abt  | R13_und   | R13_irq   | R13_fiq           | R13_mon  |

| R14  | R14    | R14_svc    | R14_abt  | R14_und   | R14_irq   | R14_fiq           | R14_mon  |

| PC   | PC     | PC         | PC       | PC        | PC        | PC                | PC       |

|      |        |            |          |           |           |                   |          |

| CPSR | CPSR   | CPSR       | CPSR     | CPSR      | CPSR      | CPSR              | CPSR     |

|      |        | SPSR_svc   | SPSR_abt | SPSR_und  | SPSR_irq  | SPSR_fiq          | SPSR_mor |

| Table 2-3 Register organization | Table 2 | 2-3 Rec | gister or | anization |

|---------------------------------|---------|---------|-----------|-----------|

|---------------------------------|---------|---------|-----------|-----------|

## 2.3 Program Status Registers

The format of the CPSR and SPSRs is unchanged.

### 2.3.1 PSR mode bits

The encoding of the mode bits is shown in Table 2-4. Only the Monitor mode is specific to Security Extensions.

| M[4:0]  | Mode       | Accessible registers                         |

|---------|------------|----------------------------------------------|

| 0b10000 | User       | PC, R14-R0, CPSR                             |

| 0b10001 | FIQ        | PC, R14_fiq-R8_fiq, R7-R0, CPSR, SPSR_fiq    |

| 0b10010 | IRQ        | PC, R14_irq, R13_irq, R12-R0, CPSR, SPSR_irq |

| 0b10011 | Supervisor | PC, R14_svc, R13_svc, R12-R0, CPSR, SPSR_svc |

| 0b10111 | Abort      | PC, R14_abt, R13_abt, R12-R0, CPSR, SPSR_abt |

| 0b11011 | Undefined  | PC, R14_und, R13_und, R12-R0, CPSR, SPSR_und |

| 0b11111 | System     | PC, R14-R0, CPSR                             |

| 0b10110 | Monitor    | PC, R14_mon, R13_mon, R12-R0, CPSR, SPSR_mon |

#### Table 2-4 Mode encoding

## Updating PSR mode bits

Programs running in SPXM modes can switch to Monitor mode by:

- using a CPS instruction

- using an MSR instruction

- using an SMI, RFE, or LDM^ instruction

- using a flag-setting data processing instruction (for example MOVS, ADDS, or SUBS) with Rd = R15.

If the core is in Secure or Non-secure User mode, an attempt to enter Monitor mode by changing the CPSR directly using an MSR instruction is IGNORED. RFE is UNPREDICTABLE in User mode.

In Non-secure Privileged modes, an attempt to enter Monitor mode by changing the CPSR Mode into Monitor Mode using a CPS, MSR, or RFE instruction is UNPREDICTABLE. The Mode field in the SPSR can be changed to Monitor Mode using an MSR instruction. However, any instruction executed from a Non-secure Privileged state, which copies the SPSR to CPSR when the SPSR mode field is set to Monitor mode is UNPREDICTABLE.

— Note —

The UNPREDICTABLE behavior cannot introduce a security violation, and as a result cannot enter Monitor mode or any secure state.

A program running in a Privileged mode, either in Secure state or Non-secure state, can switch to Monitor mode by executing an SMI instruction. See *SMI* on page 2-20 for details.

A program running in User mode, either in Secure state or Non-secure state, can only switch to Monitor mode by first switching into a Privileged mode using a SWI instruction.

## 2.3.2 PSR F and A bits (ARMv6 only)

The F bit in the CPSR cannot be changed in Non-secure state if the FW bit in the SCR (bit[4]) is 0.

The A bit in the CPSR cannot be changed in Non-secure state if the AW bit in the SCR (bit[5]) is 0.

See Secure Configuration Register on page 3-11 for details.

—— Note ———

The F bit and the A bit in the SPSR can be changed in Non-secure state even if the corresponding bits in the SCR are 0. However, they are not copied into the CPSR if the corresponding bits in the SCR are 0.

## 2.3.3 PSR E bit (ARMv6 only)

The E bit in the CPSR is updated with the secure EE bit (CP15 r1 Control[25]) whenever the core switches from Non-secure to Secure state.

When the core stays in the current state on an exception, The E bit in the CPSR is updated with the EE bit of the current state.

## 2.4 Exception model

Security Extensions introduces an additional type of exception, the Software Monitor exception. This exception is generated by the SMI instruction.

IRQ, FIQ, or external abort exceptions can be configured to enter either Secure state or Non-secure state. This is controlled by SCR bits[3:1]. See *Secure Configuration Register* on page 3-11 for details.

The base address of the exception vector tables varies according to the mode the processor is in when the exception occurs. There are two banked registers for the base addresses, and a unique register for Monitor mode. All three registers are in CP15. These are shown in Table 2-5.

|                         |                                           | <b>333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333333</b> |

|-------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Register name           |                                           | Modes                                                                                                                                 |

| Non_Secure_Base_Address | Vector Base Address (VBAR <sub>NS</sub> ) | All Non-secure states                                                                                                                 |

| Secure_Base_Address     | Vector Base Address (VBAR <sub>S</sub> )  | All Secure states except Monitor mode                                                                                                 |

| Monitor_Base_Address    | Monitor Vector Base Address (MVBAR)       | Monitor mode                                                                                                                          |

#### Table 2-5 Exception vector registers

See CP15 register 12, miscellaneous registers on page 3-27 for details.

High vectors can be enabled independently for the Secure and Non-secure states using the banked V-bit in CP15r1 (bit[13]). If high vectors are enabled, the associated Non\_Secure\_Base\_Address and/or the Secure\_Base\_Address register are treated as being 0xFFFF0000, regardless of the value of these registers.

The sequence of operations when an exception occurs are generally the same as in implementations without Security Extensions. The operation of each exception state, including any differences and additional steps, is listed in the following subsections.

## 2.4.1 Reset

When Reset is de-asserted:

```

SCR[0]

= 0

/* NS-bit = 0, Secure state */

R14_svc

= UNPREDICTABLE

SPSR_svc = UNPREDICTABLE

CPSR[4:0] = 0b10011

/* Enter supervisor mode */

if Thumb-2 then

CPSR[5] = Secure TE-bit

/* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable fast interrupts */

CPSR[6]

= 1

CPSR[7]

= 1

/* Disable interrupts */

/* Disable imprecise aborts (from v6) */

CPSR[8]

= 1

= Secure EE bit /* Store value of Secure CP15r1 Control[25] (from v6) */

CPSR[9]

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

if high vectors configured then

PC = 0xFFFF0000

else

PC = 0 \times 00000000

```

Operation is the same whether Reset is entered from Secure or Non-secure state.

## 2.4.2 Undefined instruction

On an Undefined instruction in Non-secure state:

```

/* NS-bit UNCHANGED */

= address of next instruction after the Undefined instruction

R14_und

SPSR_und = CPSR

CPSR[4:0] = 0b11011

/* Enter Undefined mode */

if Thumb-2 then

CPSR[5] = TE-bit

/* Store value of CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable interrupts */

CPSR[7] = 1

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

/* Clear J bit (from v5TEJ) */

CPSR[24] = 0

if high vectors configured then

PC = 0 \times FFFF0004

else

PC = Non_Secure_Base_Address + 0x00000004

```

The behavior in Secure state is identical to that in Non-secure state, except that:

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

## 2.4.3 Software interrupt

On a SWI in Non-secure state:

```

/* NS-bit UNCHANGED */

R14_svc = address of next instruction after the SWI instruction

SPSR_svc = CPSR

CPSR[4:0] = 0b10011

/* Enter supervisor mode */

if Thumb-2 then

CPSR[5] = TE-bit

/* Store value of CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5]

/* Execute in ARM state */

= 0

/* Disable interrupts */

CPSR[7]

= 1

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

/* Clear J bit (from v5TEJ) */

CPSR[24] = 0

if high vectors configured then

PC = 0xFFFF0008

else

PC = Non_Secure_Base_Address + 0x0000008

```

The behavior in Secure state is identical to that in Non-secure state, except that:

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

#### 2.4.4 External prefetch abort

On an external prefetch abort in Non-secure state:

```

/* NS-bit UNCHANGED */

if SCR[3] == 1 then

/* external prefetch trapped to Monitor mode */

R14_mon

= address of next instruction + 4

SPSR mon = CPSR

CPSR[4:0] = 0b10110

/* Enter Monitor mode */

if Thumb-2 then

CPSR[5] = Secure TE-bit /* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable fast interrupts */

CPSR[6] = 1

CPSR[7] = 1

/* Disable interrupts */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

CPSR[9] = Secure EE bit /* Store value of Secure CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

PC = Monitor_Base_Address + 0x0000000C

else

/* external prefetch trapped to Abort mode */

= address of next instruction + 4

R14_abt

SPSR abt = CPSR

CPSR[4:0] = 0b10111

/* Enter Abort mode */

if Thumb-2 then

CPSR[5] = TE-bit

/* Store value of CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

/* Execute in ARM state */

CPSR[5] = 0

CPSR[7] = 1

/* Disable interrupts */

if SCR[5] == 1 then

/* bit AW */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

/* else CPSR[8] = UNCHANGED */

/* Store value of CP15r1 Control[25] (from v6) */

CPSR[9] = EE bit

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

if high vectors configured then

PC = 0xFFFF000C

else

PC = Non Secure Base Address + 0x0000000C

```

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[8] (Abit) is updated regardless of bit[5] of the SCR.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

## 2.4.5 Internal prefetch abort

On an internal prefetch abort in Non-secure state:

```

/* NS-bit UNCHANGED */

R14_abt

= address of next instruction + 4

SPSR_abt = CPSR

CPSR[4:0] = 0b10111

/* Enter Abort mode */

if Thumb-2 then

/* Store value of CP15r1 Control[30] */

CPSR[5] = TE-bit

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable interrupts */

CPSR[7] = 1

if SCR[5] == 1 then

/* bit AW */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

/* else CPSR[8] = UNCHANGED */

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

/* Clear J bit (from v5TEJ) */

CPSR[24] = 0

if high vectors configured then

PC = 0xFFFF000C

else

PC = Non Secure Base Address + 0x0000000C

```

= NON\_SECURE\_BASE\_ADDRESS + 0X0000000C

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[8] (Abit) is updated regardless of bit[5] of the SCR.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

#### 2.4.6 External data abort

On an external precise data abort, or an external imprecise abort with CPSR[8] = 0, in Non-secure state:

```

/* NS-bit UNCHANGED */

if SCR[3] == 1 then

/* external aborts trapped to Monitor mode */

R14_mon

= address of next instruction + 8

SPSR mon = CPSR

CPSR[4:0] = 0b10110

/* Enter Monitor mode */

if Thumb-2 then

CPSR[5] = Secure TE-bit /* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable fast interrupts */

CPSR[6] = 1

CPSR[7] = 1

/* Disable interrupts */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

CPSR[9] = Secure EE bit /* Store value of Secure CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

PC = Monitor_Base_Address + 0x00000010

else

/* external aborts trapped to current state Abort mode */

= address of next instruction + 8

R14_abt

SPSR abt = CPSR

CPSR[4:0] = 0b10111

/* Enter Abort mode */

if Thumb-2 then

CPSR[5] = TE-bit

/* Store value of CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

/* Execute in ARM state */

CPSR[5] = 0

CPSR[7] = 1

/* Disable interrupts */

if SCR[5] == 1 then

/* bit AW */

CPSR[8] = 1

/* Disable imprecise aborts (from v6) */

/* else CPSR[8] = UNCHANGED */

/* Store value of CP15r1 Control[25] (from v6) */

CPSR[9] = EE bit

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

if high vectors configured then

PC = 0 \times FFFF0010

else

PC = Non Secure Base Address + 0x0000010

```

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[8] (Abit) is updated regardless of bit[5] of the SCR.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

## 2.4.7 Internal data abort

On an internal data abort in Non-secure state:

```

/* NS-bit UNCHANGED */

R14_abt

= address of next instruction + 8

SPSR_abt = CPSR

CPSR[4:0] = 0b10111

/* Enter Abort mode */

if Thumb-2 then

/* Store value of CP15r1 Control[30] */

CPSR[5] = TE-bit

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable interrupts */

CPSR[7] = 1

if SCR[5] == 1 then

/* bit AW */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

/* else CPSR[8] = UNCHANGED */

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

/* Clear J bit (from v5TEJ) */

CPSR[24] = 0

if high vectors configured then

PC = 0 \times FFFF0010

else

PC = Non Secure Base Address + 0x00000010

```

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[8] (Abit) is updated regardless of bit[5] of the SCR.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

#### 2.4.8 Interrupt request

On an interrupt request (IRQ), with the I bit, CPSR[7] = 0, in Non-secure state:

```

/* NS-bit UNCHANGED */

if SCR[1] == 1 then

/* IRQ trapped to Monitor mode */

R14_mon = address of next instruction + 4

SPSR_mon = CPSR

CPSR[4:0] = 0b10110

/* Enter Monitor mode */

if Thumb-2 then

CPSR[5] = Secure TE-bit /* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable fast interrupts */

CPSR[6] = 1

CPSR[7] = 1

/* Disable interrupts */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

CPSR[9] = Secure EE bit /* Store value of Secure CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

PC = Monitor_Base_Address + 0x00000018

else

/* IRQ trapped to current state IRQ mode */

R14_irg = address of next instruction + 4

SPSR_irq = CPSR

CPSR[4:0] = 0b10010

/* Enter IRO mode */

if Thumb-2 then

CPSR[5] = TE-bit

/* Store value of CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

/* Execute in ARM state */

CPSR[5] = 0

CPSR[7] = 1

/* Disable interrupts */

if SCR[5] == 1 then

/* bit AW */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

/* else CPSR[8] = UNCHANGED */

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

if VE == 0 then

/* Core with VIC port only */

if high vectors configured then

PC = 0xFFFF0018

else

PC = Non Secure Base Address + 0x0000018

else

```

PC = IMPLEMENTATION DEFINED

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[8] (Abit) is updated regardless of bit[5] of the SCR.

- If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

#### 2.4.9 Fast interrupt request

On a fast interrupt request (FIQ), with the F bit, CPSR[6] = 0, in Non-secure state:

```

/* NS-bit UNCHANGED */

if SCR[2] == 1 then

/* FIQ trapped to Monitor mode */

R14_mon = address of next instruction + 4

SPSR_mon = CPSR

CPSR[4:0] = 0b10110

/* Enter Monitor mode */

if Thumb-2 then

CPSR[5] = Secure TE-bit /* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

/* Disable fast interrupts */

CPSR[6] = 1

CPSR[7] = 1

/* Disable interrupts */

/* Disable imprecise aborts (from v6) */

CPSR[8] = 1

CPSR[9] = Secure EE bit /* Store value of Secure CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

PC = Monitor_Base_Address + 0x000001C

else

/* FIQ trapped to FIQ mode */

/* SCR[4] (FW) must be set */

/* to avoid infinite loop until FIO asserted */

R14 fia

= address of next instruction + 4

SPSR_fiq = CPSR

CPSR[4:0] = 0b10001

/* Enter FIO mode */

if Thumb-2 then

/* Store value of CP15r1 Control[30] */

CPSR[5] = TE-bit

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

if SCR[4] == 1 then

/* bit FW */

CPSR[6] = 1

/* Disable fast interrupts */

/* else CPSR[6] = UNCHANGED */

/* Disable interrupts */

CPSR[7] = 1

if SCR[5] == 1 then

/* bit AW */

CPSR[8] = 1

/* Disable imprecise aborts (from v6) */

/* else CPSR[8] = UNCHANGED */

CPSR[9] = EE bit

/* Store value of CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

if VE == 0 then

/* Core with VIC port only */

if high vectors configured then

PC = 0xFFFF001C

else

PC = Non_Secure_Base_Address + 0x000001C

else

PC = IMPLEMENTATION DEFINED

```

- Secure\_Base\_Address is used instead of Non\_Secure\_Base\_Address

- CPSR[6] (F bit) and CPSR[8] (Abit) are updated regardless of bits[5:4] of the SCR.

• If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* on page 2-18 for more details.

## 2.4.10 Software monitor exception

On an SMI in Secure or Non-secure state:

```

if (MonitorMode)

SCR[0] = 0

/* NS-bit set to Secure */

else

/* NS-bit UNCHANGED */

if (UserMode) then

/* Undefined instruction */

(see Undefined instruction on page 2-9)

else

R14_mon = address of next instruction after SMI

SPSR_mon = CPSR

/* Enter Monitor mode */

CPSR[4:0] = 0b10110

if Thumb-2 then

CPSR[5] = Secure TE-bit /* Store value of Secure CP15r1 Control[30] */

/* Execute in ARM/Thumb */

else

CPSR[5] = 0

/* Execute in ARM state */

CPSR[6] = 1

/* Disable fast interrupts */

/* Disable interrupts */

CPSR[7]

= 1

CPSR[8] = 1

/* Disable imprecise aborts (from v6) */

CPSR[9] = Secure EE bit /* Store value of CP15r1 Control[25] (from v6) */

CPSR[24] = 0

/* Clear J bit (from v5TEJ) */

PC = Monitor_Base_Address + 0x00000008

/* SMI vectored to the SWI vector */

```

— Note —

If the exception occurs from Monitor mode, the value of NS-bit is changed to 0, that is Secure. See *Exceptions occurring in Monitor mode* for more details.

#### 2.4.11 Exception priorities

Exception priorities are the same as in other ARM architectures. The SMI exception has the same priority as BKPT, Undefined instruction, and SWI exceptions. That is, it has the lowest priority.

#### 2.4.12 Exceptions occurring in Monitor mode

Except reset, the software model does not expect any other exception to occur in secure Monitor mode. Any exception occurring in Monitor mode causes the NS-bit in the Secure Configuration register (SCR[0]) to reset, forcing secure state entry for all exceptions. IRQ, FIQ, and external aborts will remain in Monitor mode if the relevant SCR[3:1] bit is set, otherwise the exception is taken in IRQ, FIQ, or Abort mode respectively.

# 2.5 ARM instruction set

Security Extensions introduces one new ARM instruction, SMI, as defined in *SMI* on page 2-20. In addition, several other instructions are modified. Specifically, all instructions which directly manipulate the CSPR are modified, that is, MSR, RFE, and CPS. In addition, all instructions which cause a copy of the SPSR to the CSPR are also modified. These changes mean that any attempts to change into Monitor mode from a Non-secure Privileged mode are UNPREDICTABLE.

The list of modified instructions is as follows:

- CPS

- LDM (3)

- MSR

- RFE

- SRS

- Flag setting data operations (includes MOV) which write to the PC, for example, ADDS PC, Rn, Rm.

#### 2.5.1 SMI

| 31 | 28   | 27 |   |   |   |   |   |   | 20 | 8   | 7 | 6 | 5 | 4 | 3 | 0    |

|----|------|----|---|---|---|---|---|---|----|-----|---|---|---|---|---|------|

|    | cond | 0  | 0 | 0 | 1 | 0 | 1 | 1 | 0  | SBZ | 0 | 1 | 1 | 1 |   | imm4 |

The SMI (Software Monitor) instruction causes an SMI exception.

#### Syntax

```

SMI{<cond>} <imm4>

```

where:

- <cond> Is the condition under which the instruction is executed. The conditions are defined in the *ARM Architecture Reference Manual, Part A.* If <cond> is omitted, the AL (always) condition is used.

- <imm4> Is a 4-bit immediate value. This is ignored by the ARM processor. It can be used by the SMI exception handler (monitor code) to determine what service is being requested, but this is not recommended (see *Notes*).

## Exceptions

Software Monitor Interrupt, Undefined instruction.

## Operation

See Software monitor exception on page 2-18.

#### Usage

Use the SMI instruction to request a secure monitor kernel service.

#### Notes

**User mode** The SMI instruction can only be executed in a Privileged mode. Attempting to execute an SMI instruction in User mode causes an Undefined Instruction exception.

#### Use of the Immediate value

The SMI instruction from the non-secure world causes entry into the secure world. This means that the code sequence for the secure world to read the instruction and determine the imm4 value is very complicated, particularly in systems using virtual memory. It is recommended that any arguments used to communicate which service is being requested are passed using registers, rather than using immediate values.

# 2.6 Security Extensions and VFP support

None of the registers in VFP are banked in the Security Extensions.

CPU Architecture

# Chapter 3 Memory and System Architecture

This chapter describes the changes to the memory and system architecture introduced with Security Extensions. It contains the following sections:

- System control coprocessor on page 3-2

- Register 1, control registers on page 3-9

- Access to registers in Monitor mode on page 3-19

- Memory management unit on page 3-20

- *L1 caches* on page 3-30

- *Tightly coupled memory* on page 3-43

- *L1 DMA* on page 3-46.

# 3.1 System control coprocessor

This section summarizes the CP15 register space, and the read/write permissions of CP15 registers that are affected by Security Extensions. See the *ARM Architecture Reference Manual* for information about other CP15 registers, for example, common CP15r0 and implementation-defined CP15r15.

Access to CP15 registers is only allowed in Privileged modes, with the following exceptions:

- the PrefetchFlush and data memory barrier (DMB, DWB/DSB) operations

- L1 DMA (ARMv6 only) when configured for user access

- Smartcache operations (ARMv6 only).

The access permissions of IMPLEMENTATION DEFINED registers are IMPLEMENTATION DEFINED, but must not introduce any scope for security violations into the processor.

All other accesses are UNDEFINED in User mode, in both Secure and Non-secure state (when NS-state = 0 and 1 respectively). Where privileged accesses are further restricted due to Security Extensions, this is noted in the relevant sections.

## 3.1.1 Terminology for CP15 register selection

The following terminology is used to distinguish the application and the selection of CP15 registers:

**CP15 access** Reading or writing a CP15 register using an MRC, MCR, or MCRR instruction.

Selected by NS-bit. This allows Monitor mode to access both Secure and Non-secure CP15 registers.