# ARM Architecture Reference Manual Debug supplement

Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0379A

# **ARM Architecture Reference Manual**

Copyright © 2006 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

|                 |       | ·                | Change History |

|-----------------|-------|------------------|----------------|

| Date            | Issue | Confidentiality  | Change         |

| 8 February 2006 | А     | Non-Confidential | First release. |

#### **Proprietary Notice**

ARM, the ARM Powered logo, Jazelle, RealView, and Thumb are registered trademarks of ARM Limited.

The ARM logo, AMBA, and CoreSight are trademarks of ARM Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith.

1. Subject to the provisions set out below, ARM Limited hereby grants to you a perpetual, non-exclusive, nontransferable, royalty free, worldwide licence to use this ARM Architecture Reference Manual for the purposes of developing; (i) software applications or operating systems which are targeted to run on microprocessor cores distributed under licence from ARM Limited; (ii) tools which are designed to develop software programs which are targeted to run on microprocessor cores distributed under licence from ARM Limited; (iii) integrated circuits which incorporate a microprocessor core manufactured under licence from ARM Limited.

2. Except as expressly licensed in Clause 1 you acquire no right, title or interest in the ARM Architecture Reference Manual, or any Intellectual Property therein. In no event shall the licences granted in Clause 1, be construed as granting you expressly or by implication, estoppel or otherwise, licences to any ARM technology other than the ARM Architecture Reference Manual. The licence grant in Clause 1 expressly excludes any rights for you to use or take into use any ARM patents. No right is granted to you under the provisions of Clause 1 to; (i) use the ARM Architecture Reference Manual for the purposes of developing or having developed microprocessor cores or models thereof which are compatible in whole or part with either or both the instructions or programmer's models described in this ARM Architecture Reference Manual; or (ii) develop or have developed models of any microprocessor cores designed by or for ARM Limited; or (iii) distribute in whole or in part this ARM Architecture Reference Manual to third parties without the express written permission of ARM Limited; or (iv) translate or have translated this ARM Architecture Reference Manual into any other languages.

#### 3.THE ARM ARCHITECTURE REFERENCE MANUAL IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE.

4. No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the ARM tradename, in connection with the use of the ARM Architecture Reference Manual or any products based thereon. Nothing in Clause 1 shall be construed as authority for you to make any representations on behalf of ARM Limited in respect of the ARM Architecture Reference Manual or any products based thereon.

Copyright © 2006 ARM Limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

# Contents ARM Architecture Reference Manual Debug supplement

# Preface

| Conventions     | <br> |

|-----------------|------|

| Further reading | <br> |

|                 |      |

| Chapter 1 | Introduction |          |

|-----------|--------------|----------|

|           | 11           | Overview |

| 1.1 | Overview             | 1-2 |

|-----|----------------------|-----|

| 1.2 | Debug                | 1-3 |

| 1.3 | Performance counters | 1-5 |

| 1.4 | Trace                | 1-6 |

| 1.5 | Register interfaces  | 1-7 |

| 1.5 | Register interfaces  |     |

# Chapter 2 Debug Events

| Overview                       | . 2-2                                                                                                        |

|--------------------------------|--------------------------------------------------------------------------------------------------------------|

| Invasive debug authentication  | . 2-4                                                                                                        |

| Software Debug events          | . 2-6                                                                                                        |

| Halting Debug events           | 2-18                                                                                                         |

| Generation of Debug events     | 2-20                                                                                                         |

| Debug event priority and order | 2-23                                                                                                         |

|                                | Invasive debug authentication<br>Software Debug events<br>Halting Debug events<br>Generation of Debug events |

| Chapter 3 | Debug Exceptions |                                                            |         |  |

|-----------|------------------|------------------------------------------------------------|---------|--|

|           | 3.1              | Overview                                                   | 3-2     |  |

|           | 3.2              | Effects of Debug Exceptions on CP15 registers and the WFAR | 3-4     |  |

| Chapter 4 | Debu             | ug State                                                   |         |  |

|           | 4.1              | Overview                                                   | 4-2     |  |

|           | 4.2              | Entering Debug state                                       | 4-3     |  |

|           | 4.3              | Behavior of the PC and CPSR in Debug state                 | 4-7     |  |

|           | 4.4              | Executing instructions in Debug state                      | 4-9     |  |

|           | 4.5              | Privilege in Debug state                                   | 4-13    |  |

|           | 4.6              | Behavior of non-invasive debug in Debug state              |         |  |

|           | 4.7              | Exceptions in Debug state                                  |         |  |

|           | 4.8              | Leaving Debug state                                        | 4-21    |  |

| Chapter 5 | Debu             | ug Register Interfaces                                     |         |  |

|           | 5.1              | About the Debug Register Interface                         | 5-2     |  |

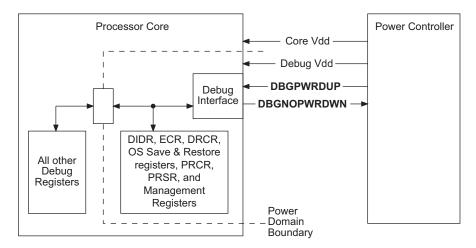

|           | 5.2              | Reset and Power-down support                               | 5-6     |  |

|           | 5.3              | Debug Register Map                                         | 5-13    |  |

|           | 5.4              | Synchronization of debug register updates                  | 5-18    |  |

|           | 5.5              | Access permissions                                         | 5-20    |  |

|           | 5.6              | Coprocessor interface                                      |         |  |

|           | 5.7              | The Memory-mapped and recommended external debug interface | es 5-34 |  |

| Chapter 6 | Reco             | ommended External Debug Interface                          |         |  |

|           | 6.1              | System integration signals                                 |         |  |

|           | 6.2              | Recommended debug slave port                               | 6-10    |  |

| Chapter 7 | Debu             | ug Requirements on Memory Systems                          |         |  |

|           | 7.1              | About debug requirements on memory systems                 | 7-2     |  |

|           | 7.2              | Recommended access to specific CP15 registers              | 7-3     |  |

|           | 7.3              | Debug state Cache/MMU Control Registers                    | 7-4     |  |

| Chapter 8 | Non-             | -invasive debug                                            |         |  |

|           | 8.1              | About non-invasive debug                                   |         |  |

|           | 8.2              | Program counter sampling register                          | 8-3     |  |

|           | 8.3              | Non-invasive debug authentication                          | 8-4     |  |

| Chapter 9 |                  | e-based Performance Counters                               |         |  |

|           | 9.1              | About core-based performance counters                      |         |  |

|           | 9.2              | Status in the ARM architecture                             | -       |  |

|           | 9.3              | Accuracy of performance counters                           |         |  |

|           | 0 1              | Behavior on overflow                                       | 9-6     |  |

|           | 9.4              |                                                            |         |  |

|           | 9.5              | Interaction with Security Extensions                       |         |  |

|           | -                |                                                            | 9-8     |  |

| 9.8  | Register map       | 9-10 |

|------|--------------------|------|

| 9.9  | Access permissions | 9-12 |

| 9.10 | Event numbers      | 9-13 |

# Chapter 10 Debug Register Reference

| 10.1 | Identification registers                    | . 10-3 |

|------|---------------------------------------------|--------|

| 10.2 | Control and status registers                | . 10-8 |

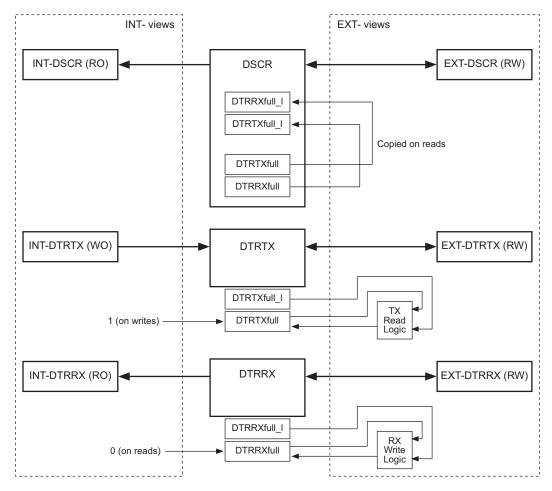

| 10.3 | Instruction and data transfer registers     | 10-32  |

| 10.4 | Breakpoint and watchpoint registers         | 10-39  |

| 10.5 | Operating-system save and restore registers | 10-58  |

| 10.6 | Memory system control registers             | 10-61  |

| 10.7 | Management registers                        | 10-69  |

| 10.8 | Core-based performance counters registers   | 10-80  |

|      |                                             |        |

## Glossary

Contents

# Preface

This preface introduces the ARM Architecture Reference Manual, Debug supplement. It contains the following sections:

- About this manual on page x

- Conventions on page xii

- Further reading on page xiii

- *Feedback* on page xiv.

# About this manual

The purpose of this manual is to describe the ARM Debug architecture. It is a supplement to the ARM Architecture Reference Manual (ARM DDI 0100, the ARM ARM), and is intended to be used with it.

It is assumed that the reader is familiar with:

- the ARM programmer's model, described in Part A Chapter 2 of the ARM Architecture Reference Manual

- the memory system architecture support, described in Part B of the ARM Architecture Reference Manual.

This manual is described in the following sections:

- Intended audience

- Using this manual.

#### Intended audience

This book is written for all developers designing:

- ARM processors

- hardware using ARM processors

- software for systems using ARM processors.

#### Using this manual

This manual is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an introduction to the purpose of the ARM Debug Architecture, and an overview of how this purpose is achieved.

#### Chapter 2 Debug Events

Read this chapter for information about what Debug events are, and how a processor responds to them.

#### Chapter 3 Debug Exceptions

Read this chapter for information about Debug Exceptions.

#### Chapter 4 Debug State

Read this chapter for information about Debug State.

#### Chapter 5 Debug Register Interfaces

Read this chapter for information about the Debug Register Interfaces.

#### Chapter 6 Recommended External Debug Interface

Read this chapter for details of the recommended external debug interface.

#### Chapter 7 Debug Requirements on Memory Systems

Read this chapter for details of the requirements placed on memory systems by debug.

#### Chapter 8 Non-invasive debug

Read this chapter for information about non-invasive debug.

#### **Chapter 9** Core-based Performance Counters

Read this chapter for information about core-based performance counters.

#### Chapter 10 Debug Register Reference

Read this chapter for reference information about the debug registers.

# Conventions

Conventions that this manual can use are described in:

- Typographic

- Signals.

## Typographic

| typewriter     | Is used for assembler syntax descriptions, pseudo-code descriptions of instruction and source code examples.                                                                                                                                                               |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                | The typewriter font is also used in the main text for instruction mnemonics and for hexadecimal numbers.                                                                                                                                                                   |  |

| italic         | Highlights important notes, introduces special terminology, and denotes internal cross-references and citations.                                                                                                                                                           |  |

| bold           | Is used for emphasis in descriptive lists and elsewhere, where appropriate.                                                                                                                                                                                                |  |

| SMALL CAPITALS | Are used for a few terms that have specific technical meanings. Their meanings can be found in the <i>Glossary</i> .                                                                                                                                                       |  |

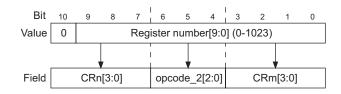

| < and >        | <ul> <li>Angle brackets enclose replaceable terms for assembler syntax where they appear<br/>in code or code fragments. They appear in normal font in running text. For example:</li> <li>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd></li> </ul> |  |

|                | • The Opcode_2 value selects which register is accessed.                                                                                                                                                                                                                   |  |

## Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means HIGH for active-HIGH signals and LOW for active-LOW signals. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower-case n | Denotes an active-LOW signal.                                                                                                                                           |

| Prefix DBG   | Denotes debug signals.                                                                                                                                                  |

# **Further reading**

This section lists publications that provide additional information on the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda, and the ARM Frequently Asked Questions.

#### **ARM** publications

This architecture specification is a supplement to, and must be read in conjunction with, the *ARM Architecture Reference Manual*, ARM DDI 0100.

The following documents contain additional information that is relevant to the information given in this specification, or complement the information given here:

- ARM Architecture Reference Manual Security Extensions Supplement, ARM DDI 0309

- ARM Debug Interface v5 Architecture Specification, ARM IHI 0031

- CoreSight Architecture Specification, ARM IHI 0029

- Embedded Trace Macrocell Architecture Specification, ARM IHI 0014.

#### Other publications

This section lists relevant documents published by third parties:

- EEE 1149.1-1990 IEEE Standard Test Access Port and Boundary Scan Architecture (JTAG).

- JEP106M, Standard Manufacture's Identification Code, JEDEC Solid State Technology Association.

# Feedback

ARM Limited welcomes feedback on its documentation.

#### Feedback on this manual

If you have any comments on this manual, send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

# Chapter 1 Introduction

This chapter introduces the ARM Debug Architecture. It contains the following sections:

- Overview on page 1-2

- Debug on page 1-3

- *Performance counters* on page 1-5

- Trace on page 1-6

- *Register interfaces* on page 1-7.

# 1.1 Overview

ARMv6 was the first version of the ARM architecture to include debug provisions. The introduction of the ARM Architecture Security Extensions extended the ARMv6 Debug Architecture:

- ARMv6 systems without Security Extensions implement v6 debug

- ARMv6 systems with Security Extensions implement v6.1 debug.

ARMv7 introduces additional extensions to support developments in the debug environment.

The main change in the debug environment is the emergence of new forms of external debug interface. Although ARMv6 did not require a particular debug interface, it was designed with the JTAG scan-chain model in mind. JTAG remains an important and widely used interface. However, systems such as the ARM CoreSight architecture require changes in the debug interface. For more information about the CoreSight architecture see the *CoreSight Architecture Specification*. Some of the aims of the CoreSight architecture, such as a more system-centric view of debug, and improved debug of powered-down systems, are addressed in the ARMv7 core debug architecture.

Another important aspect of v6 Debug is the optional trace extension. This is implemented by an Embedded Trace Macrocell (ETM) compliant to ETMv3. This optional extension is retained in ARMv7, and the first version of the ETM architecture for ARMv7 implementations is ETMv3.3.

ARMv7 debug also introduces an architecture extension to provide core-based performance counters.

Table 1-1 shows the main components of ARMv7 debug, and where they are described.

| Component            | Status   | Reference                                           |  |

|----------------------|----------|-----------------------------------------------------|--|

| Debug                | Required | Chapter 2 Debug Events                              |  |

|                      |          | Chapter 3 Debug Exceptions                          |  |

|                      |          | Chapter 4 Debug State                               |  |

|                      |          | Chapter 5 Debug Register Interfaces                 |  |

| Performance counters | Optional | Chapter 9 Core-based Performance Counters           |  |

| Trace                | Optional | Embedded Trace Macrocell Architecture Specification |  |

#### Table 1-1 ARMv7 Debug sub-architectures

ARM processors implement two types of debug support:

**Invasive debug** All debug features that allow modification of the processor state.

**Non-invasive debug** All debug features that allow data and program flow observation, especially trace support.

# 1.2 Debug

The debug component of the ARM Debug Architecture is primarily intended for run-control debugging. Versions 6 and 7 of the architecture (ARMv6 and ARMv7) provide a software interface that includes:

- a Debug Identification Register (DIDR)

- status and control registers, including the Debug Status and Control Register (DSCR)

- hardware breakpoint and watchpoint support

- a Debug Communications Channel (DCC).

The ARMv7 software interface also includes reset, Power-down and Operating System support features.

The debug architecture also requires an external debug interface that supports access to the programmers' model.

The programmers' model can be used to manage and control Debug events. Watchpoints and breakpoints are two examples of Debug events. Debug events are described in Chapter 2 *Debug Events*.

You can configure the core through the DSCR into one of two Debug-modes:

#### **Monitor Debug-mode**

This causes a Debug Exception to occur as a result of a Debug event. Debug Exceptions are serviced through the same exception vectors as the Prefetch and Data Aborts, depending on whether they relate to instruction execution or data access.

Debug Exceptions are described in Chapter 3 Debug Exceptions.

#### Halting Debug-mode

This allows the system to enter a special Debug state when a Debug event occurs. When the system is in Debug state, the processor core ceases to execute instructions from the program counter location, but is instead controlled through the external debug interface and the *Instruction Transfer Register* (ITR) in particular. This allows an external agent, such as a debugger, to interrogate processor context, and control all subsequent instruction execution. Because the processor is stopped, it ignores the external system and cannot service interrupts.

Debug state is described in Chapter 4 Debug State.

A debug solution can use a mixture of the two methods, for example to support an OS or RTOS with both:

- Running System Debug (RSD) using Monitor Debug-mode

- Halting Debug-mode support available as a fallback for system failure and boot time debug.

The ability to switch between these two Debug-modes is fully supported by the architecture.

You can program the *Vector Catch Register* (VCR) to trap many exceptions. Trapped exceptions cause a Debug event. Untrapped exceptions cause a normal exception in the execution flow.

When both Debug-modes are disabled, debug is restricted to simple monitor solutions. These are usually ROM or Flash-based. Such a monitor might use standard system features, such as a UART or Ethernet connection, to communicate with a debug host. Alternatively, it might use the DCC as an out-of-band communications channel to the host. This minimizes its requirement on system resources.

This forms the basis of the Debug Programmer's Model (DPM) for ARMv6 and ARMv7.

#### 1.2.1 Security Extensions and debug

Security Extensions debug allows you to disable invasive debug and non-invasive debug independently in either:

- all Secure modes

- only in Secure Privileged modes.

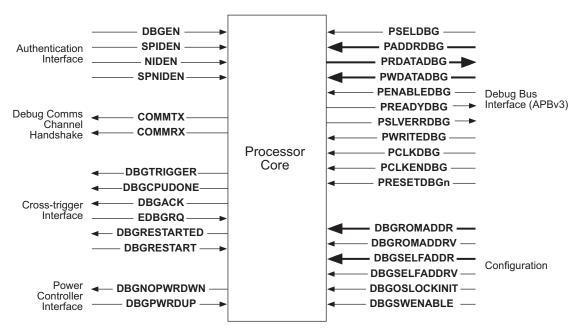

This is controlled by four input signals and two control bits in the Secure Debug Enable Register:

- the *Debug Enable* signal, **DBGEN**

- the Non-Invasive Debug Enable signal, NIDEN

- the Secure Privileged Invasive Debug Enable signal, SPIDEN

- the Secure Privileged Non-Invasive Debug Enable signal, SPNIDEN

- the Secure User Invasive Debug Enable bit, SUIDEN

- the Secure User Non-invasive Debug Enable bit, SUNIDEN.

For more information, see:

- *Invasive debug authentication* on page 2-4

- Non-invasive debug authentication on page 8-4

- the ARM Architecture Reference Manual Security Extensions Supplement, for details of the Secure Debug Enable Register

- *Authentication signals* on page 6-3 for details of the **DBGEN**, **NIDEN**, **SPIDEN** and **SPNIDEN** signals.

# 1.3 Performance counters

Performance Counters were implemented in several processors before ARMv7, however, before ARMv7 they did not form part of the architecture. The form described here follows those implementations with minor modifications to allow for potential future expansion.

The basic form consists of:

- A cycle counter, with the ability to count cycles or every sixty-fourth cycle.

- A number of performance counters whose events can be programmed. Previous implementations have provided up to four counters, but architecturally space is provided for up to 31 counters allowing for additional expansion (up to 31). The actual number of counters is IMPLEMENTATION DEFINED, and an identification mechanism is provided.

- Controls for enabling and resetting performance counters, to flag overflows and to enable interrupts on overflow. The cycle counter can be independently enabled from the rest of the performance counters.

The set of events that can be monitored split into those that are likely to be consistent across many micro-architectures and the rest, that are likely to be implementation specific. As a result, this architecture defines a core set of events to be used across many micro-architectures, together with a large space reserved for IMPLEMENTATION DEFINED events. The full set of events for any given implementation is IMPLEMENTATION DEFINED. There is no requirement to implement any of the core set of events, but the numbers allocated for the core set of events must not be used except as defined.

# 1.4 Trace

Trace support is an architecture extension typically implemented using an *Embedded Trace Macrocell* (ETM). The ETM constructs a real-time trace stream corresponding to the operation of the processor. It is IMPLEMENTATION DEFINED whether the trace stream is stored locally in an Embedded Trace Buffer (ETB) for independent download and analysis, or whether it is exported directly through a trace port to a *Trace Port Analyzer* (TPA) and its associated host based trace debug tools.

Use of the ETM is non-invasive. Development tools can connect to the ETM, configure it, capture trace and download the trace without affecting the operation of the processor in any way. The ETM architecture extension provides an enhanced level of run-time system observation and debug granularity. It is particularly useful in cases where:

- Stopping the core affects the behavior of the system.

- There is insufficient state visible in a system by the time a problem is detected to be able to determine its cause. Trace provides a mechanism for system logging and back tracing of faults.

Trace might also be used to perform analysis of code running on the processor, such as performance analysis or code coverage.

The ETM architecture is documented separately. Licensees and third-party tools vendors should contact ARM Limited to ensure that they have the latest version. The ETM architecture specifies the following:

- the ETM programmers' model

- permitted trace protocol formats

- the physical trace port connector.

The ETM architecture version is defined with a major part and a minor part, in the form ETMvX.Y where X is the major version number and Y is the minor version number. The first ETM version that aligns with ARMv7 is ETMv3.3.

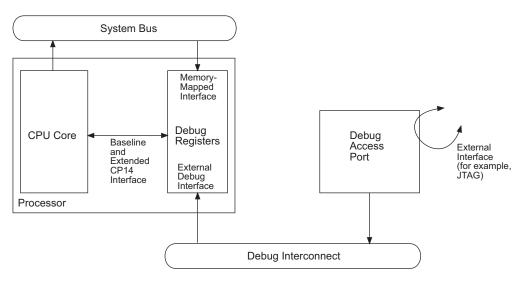

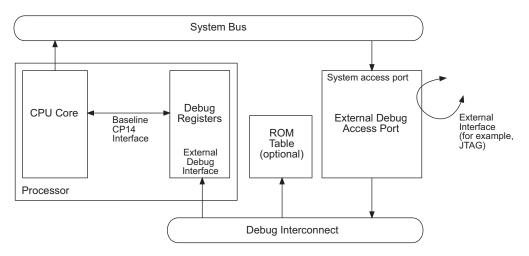

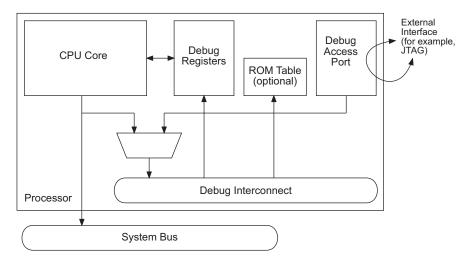

# 1.5 Register interfaces

This section gives a brief description of the different debug register interfaces defined by ARMv7. The most important distinction is between:

- the external debug interface, that defines how an external debugger can access the ARMv7 debug resources

- the processor interface, that describes how an ARMv7 processor core can access its own debug resources.

ARMv7 recommends an external debug interface based on the *ARM Debug Interface v5 Architecture Specification* (ADIv5). The most significant difference between ADIv5 and the interface recommended by ARMv6 is that ADIv5 supports debug over power-down of the processor core.

Although the ADIv5 interface is not required for compliance with the ARMv7 architecture, ARM's RealView tools require this interface to be implemented.

ADIv5 supports both a JTAG wire interface and a low pin-count *Serial Wire* interface. ARM's RealView tools support either wire interface.

An ADIv5 interface allows a debug object, such as an ARMv7 processor, to abstract a set of resources as a memory-mapped peripheral. Accesses to debug resources are made as 32-bit read/write transfers. Power-down is supported by introducing the abstraction that accesses to certain resources can return an error response when they are unavailable, just as a memory-mapped peripheral can return a slave-generated error response in exceptional circumstances.

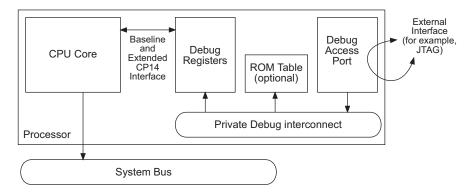

The ARMv7 Debug Architecture requires software executing on the processor to be able to access all debug registers. To provide access to a particular basic subset of debug registers ARMv7 requires that the Baseline Coprocessor 14 (CP14) Interface is implemented, see *Baseline CP14 interface* on page 5-24. In order to provide access to the rest of the debug registers ARMv7 allows one of two options:

- An Extended CP14 Interface. This is similar to the requirement of the ARMv6 architecture.

- A Memory-mapped interface.

An implementation can include both of these options.

ARMv7 does not allow all combinations of debug, ETM, and performance monitor interfaces. There are three options for ARMv7 implementations, shown as options A, B, and C in Table 1-2 on page 1-8.

The ETM architecture provides the same implementation options as ARMv7 Debug. It is optional whether Trace registers are implemented but if they are implemented, the interface to them must be as shown in Table 1-2 on page 1-8.

| Option | Processor interface to debug registers           | Processor interface to trace registers | Processor interface to performance monitor |

|--------|--------------------------------------------------|----------------------------------------|--------------------------------------------|

| А      | Baseline CP14 + Extended CP14                    | CP14                                   | CP15                                       |

| В      | Baseline CP14 + Memory-mapped                    | Memory-mapped                          | CP15                                       |

| С      | Baseline CP14 + Extended CP14 +<br>Memory-mapped | CP14 +<br>Memory-mapped                | CP15                                       |

Table 1-2 Options for interfacing to debug in ARMv7

# Chapter 2 **Debug Events**

This chapter contains the following sections:

- Overview on page 2-2

- *Invasive debug authentication* on page 2-4

- Software Debug events on page 2-6

- *Halting Debug events* on page 2-18

- *Generation of Debug events* on page 2-20

- Debug event priority and order on page 2-23.

## 2.1 Overview

A Debug event can be either:

- A Software Debug event, see *Software Debug events* on page 2-6

- A Hardware Debug event, see *Halting Debug events* on page 2-18.

A processor responds to a Debug event in one of the following ways:

- ignores the Debug event

- takes a Debug Exception, see Chapter 3 Debug Exceptions

- enters Debug State, see Chapter 4 Debug State.

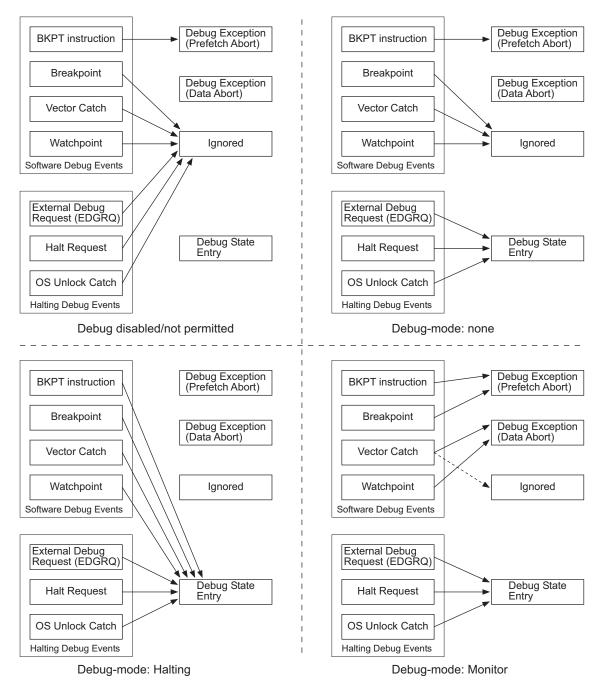

The response depends on the configuration. This is shown in Table 2-1, and in Figure 2-1 on page 2-3.

| Configuration                               |                          | Behavior                        | Debug mede                                                     |                                   |                                       |

|---------------------------------------------|--------------------------|---------------------------------|----------------------------------------------------------------|-----------------------------------|---------------------------------------|

| Invasive<br>debug<br>permitted <sup>a</sup> | DSCR[15:14] <sup>b</sup> | BKPT<br>instruction             | Other Software<br>Debug event                                  | Halting Debug<br>event            | Debug-mode<br>selected and<br>enabled |

| No                                          | bxx <sup>c</sup>         | Debug<br>exception <sup>d</sup> | Ignore                                                         | Ignore <sup>e</sup>               | Disabled, not permitted               |

| Yes                                         | b00                      | Debug<br>exception <sup>d</sup> | Ignore                                                         | Debug state<br>entry <sup>f</sup> | None                                  |

| Yes                                         | bx1                      | Debug state<br>entry            | Debug state entry                                              | Debug state<br>entry              | Halting                               |

| Yes                                         | b10                      | Debug<br>exception              | Debug exception or<br>Ignore, but see<br>footnote <sup>g</sup> | Debug state<br>entry <sup>f</sup> | Monitor                               |

#### Table 2-1 Processor behavior on Debug events

a. See Invasive debug authentication on page 2-4.

b. See Halting Debug-mode enable, bit [14] on page 10-15 and Monitor Debug-mode enable, bit [15] on page 10-15.

c. The value of DSCR[15:14] is ignored when invasive debug is not permitted. If DBGEN is LOW these bits read as zero.

d. When debug is disabled or not permitted, the BKPT instruction generates a Debug exception rather than being ignored. The DSCR, IFSR and IFAR are set to 1 as if a BKPT Instruction Debug Exception occurred. See *Effects of Debug Exceptions on CP15 registers and the WFAR* on page 3-4.

e. The processor might enter Debug State later, see Halting Debug events on page 2-18.

- f. In ARMv6, these entries are IMPLEMENTATION DEFINED, see the ARM Architecture Reference Manual.

- g. Be careful when programming Debug events when Monitor Debug-mode is selected and enabled, because certain conditions can lead to UNPREDICTABLE behavior, see *unpredictable behavior on Software Debug events* on page 2-14.

Figure 2-1 Processor behavior on Debug events

# 2.2 Invasive debug authentication

Invasive debug can be enabled or disabled. If it is disabled the processor ignores all debug events except BKPT Instruction. This means that debug events other than BKPT Instruction do not cause the processor to enter Debug state or to take a debug exception.

In addition, if a processor implements the Security Extensions, invasive debug can be permitted or not permitted. If invasive debug is not permitted, the processor again ignores all debug events except BKPT Instruction.

The difference between enabled and permitted is that permitted debug operation depends on the security state and the operating mode of the processor. The alternatives for when Invasive debug is permitted are:

- in all processor modes, in both Secure and Nonsecure worlds

- only in Nonsecure world

- in Nonsecure world and Secure User mode.

The external debug interface signals that control the enabling and permitting of Debug events are **DBGEN** and **SPIDEN**. SPIDEN is only implemented on processors that implement Security Extensions. See *Authentication signals* on page 6-3.

If **DBGEN** is LOW, all invasive debug is disabled.

On processors that do not implement Security Extensions, if **DBGEN** is HIGH, invasive debug is enabled and permitted in all modes, see Table 2-2.

| DBGEN | Modes in which Invasive debug is permitted |

|-------|--------------------------------------------|

| LOW   | None                                       |

| HIGH  | All modes                                  |

#### Table 2-2 Invasive debug authentication, Security Extensions not implemented

On processors that implement Security Extensions, if both **DBGEN** and **SPIDEN** are HIGH, invasive debug is enabled and permitted in all modes and in both Secure and Nonsecure worlds. If **DBGEN** is HIGH and **SPIDEN** is LOW:

- Invasive debug is enabled and permitted in the Nonsecure world.

- Invasive debug is not permitted in Secure privileged modes.

- Whether invasive debug is permitted in Secure User mode depends on the value of the SUIDEN bit in the Secure Debug Enable (SDE) Register. See the *ARM Architecture Reference Manual Security Extensions Supplement* for details of the Secure Debug Enable Register.

This is shown in Table 2-3 on page 2-5.

| DBGEN | SPIDEN | SUIDEN | Modes in which invasive debug is permitted         |  |

|-------|--------|--------|----------------------------------------------------|--|

| LOW   | Х      | Х      | None                                               |  |

| HIGH  | LOW    | 0      | All modes in Nonsecure world                       |  |

| HIGH  | LOW    | 1      | All modes in Nonsecure world, and Secure User mode |  |

| HIGH  | HIGH   | Х      | All modes in all worlds                            |  |

#### Table 2-3 Invasive debug authentication, Security Extensions implemented

#### —— Note ———

If you only enable invasive debug when the processor is in a Nonsecure mode this only protects your secure processing from direct observation or invasion by an untrusted debugger. System designers must be aware that such configurations might still allow attacks such as denial of service attacks. For example:

- The processor can be forced into Debug state from a Nonsecure mode, preventing processing of secure operations.

- The Interrupts disable bit in the Debug Status and Control Register can be used to prevent servicing of secure interrupts.

ARM Limited recommends that you disable invasive debug in all modes where you are concerned about such attacks.

## 2.3 Software Debug events

A Software Debug event can be any of the following:

- A Watchpoint Debug event, see Watchpoint Debug events

- A Breakpoint Debug event, see *Breakpoint Debug events* on page 2-10

- A BKPT Instruction Debug event, see *BKPT Instruction Debug events* on page 2-12

- A Vector Catch Debug event, see *Vector Catch Debug events* on page 2-13.

If Monitor Debug-mode is selected and enabled, the behavior of certain types of Software Debug events is noted in the following sections as UNPREDICTABLE. See *unpredictable behavior on Software Debug events* on page 2-14 for more information.

#### 2.3.1 Watchpoint Debug events

Watchpoint Debug events are controlled by pairs of registers referred to as Watchpoint Register Pairs (WRPs). An implementation may contain many WRPs. The first two WRPs are identified as WRP0 and WRP1, and this numbering pattern continues for additional WRPs. WRPn refers to any particular pair. WRPn consists of two registers:

- a Watchpoint Control Register, WCRn

- a Watchpoint Value Register, WVRn.

For a given Watchpoint Register Pair, WRPn, a Watchpoint Debug event occurs when all of the following are true:

- The *Data Virtual Address* (DVA) matches the value in WVRn. See *Memory addresses* on page 2-13 for a definition of the DVA.

- At the time when the watchpoint is evaluated, all the conditions of WCRn match.

- The watchpoint is enabled.

- If linking is enabled in WCRn, the linked Context ID matching Breakpoint Register Pair (BRP) must meet the following conditions:

- the BRP is enabled

- the value held in the BRP matches the Context ID in CP15 register 13.

See Breakpoint Debug events on page 2-10 for more information about BRPs.

• The instruction that initiated the memory access is committed for execution. Watchpoint Debug events are only generated if the instruction passes its condition code.

All instructions that the *ARM Architecture Reference Manual* defines as memory access instructions can generate Watchpoint Debug events.

It is IMPLEMENTATION DEFINED whether either or both of the memory hint instructions, PLD and PLI, generate Watchpoint Debug events. When Watchpoint Debug event generation by either or both of the PLD and PLI instructions is implemented, the behavior must be:

- if PLI is implemented, no watchpoint is generated in a situation where the instruction would generate a prefetch abort, if it was a real fetch rather than a hint

- If PLD is implemented, no watchpoint is generated in a situation where the instruction would generate a Data Abort, if it was a real data access rather than a hint

- in all other situations a Watchpoint Debug event is generated.

It is IMPLEMENTATION DEFINED whether the following cache maintenance operations generate Watchpoint Debug events:

- clean the data cache by modified virtual address (MVA)

- invalidate the data cache by MVA

- invalidate the instruction cache by MVA

- clean and invalidate the data cache by MVA.

— Note —

When Watchpoint Debug event generation by these cache maintenance operations is implemented, these operations must generate Watchpoint Debug events on a DVA match, regardless of whether the data is stored in any cache.

For regular data accesses, the Watchpoint Debug event generation includes a comparison of the WCR contents with the size of access. For the purpose of this comparison, the sizes of these operations are IMPLEMENTATION DEFINED:

- memory hints, PLD and PLI

- cache maintenance operations.

Watchpoint Debug events can be Precise or Imprecise:

- Precise Watchpoint Debug events act like a precise Data Abort exception on the data access instruction itself

- Imprecise Watchpoint Debug events act like an exception that cancels a later instruction.

For more information see Precise and Imprecise Watchpoint Debug events on page 2-8.

For the ordering of debug events, the ARMv7 architecture requires that:

- Regardless of the actual ordering of memory accesses, Watchpoint Debug events must be taken in program order. See *Debug event priority and order* on page 2-23.

- Watchpoint Debug events must behave as if they were evaluated before the memory access is observed, regardless of whether the Watchpoint Debug event is precise or imprecise. See *Generation of Debug events* on page 2-20.

#### Precise and Imprecise Watchpoint Debug events

ARMv7 allows watchpoints to be either *precise* or *imprecise*. An implementation can implement precise watchpoints, imprecise watchpoints, or both. It is IMPLEMENTATION DEFINED under what circumstances a watchpoint is precise or imprecise.

ARMv6 only allows imprecise watchpoints.

#### Precise Watchpoint Debug events

A Precise Watchpoint Debug event has the same behavior as a precise Data Abort:

- If Monitor Debug-mode is enabled, R14\_abt is set to the address of the watchpointed exception + 8.

- The Debug event occurs before any following instructions or exceptions have altered the state of the processor.

- The value in the base register for the memory access is not updated.

—— Note ——

The Base Updated Abort Model is not permitted in ARMv7.

- If the instruction was a register load, the data returned is marked as invalid. If the instruction was a single register load, the destination is not updated. If the instruction loaded multiple registers, the values in the destination registers, other than the PC and base register, are UNPREDICTABLE.

- If the instruction is a coprocessor load, the values left in the coprocessor register are UNPREDICTABLE.

- If the instruction is a store, the content of the memory location written to is unchanged.

On a Precise Watchpoint Debug event, the DSCR[5:2] Method of Debug Entry bits are set to Precise Watchpoint Occurred.

If a Precise Watchpoint Debug event is signalled by a memory operation other than the first operation of an instruction that causes multiple operations, such as the LDM and LDC instructions, to Device or Strongly Ordered memory, the memory access rules may not be maintained.

For example, if the second memory operation of an STM instruction signals a Precise Watchpoint Debug event, then when the instruction is re-tried following processing of the Debug event, the first memory operation would be repeated. This behavior is not normally permitted for Device or Strongly Ordered memory.

To avoid this circumstance, debuggers should not set watchpoints on addresses within regions of Device or Strongly Ordered memory which may be accessed in this way. The address masking features of watchpoints may be used to set a watchpoint on an entire region, thereby ensuring the Precise Watchpoint Debug event is taken on the first operation of such an instruction.

#### Imprecise Watchpoint Debug events

An Imprecise Watchpoint Debug event has similar, but not identical, behavior to an imprecise Data Abort. Its behavior is:

- The state of the processor on the imprecise watchpoint exception must be such that the processor can return to the instruction cancelled by the Debug event.

- If Monitor Debug-mode is enabled, R14\_abt is set to the address of the instruction to return to + 8.

- The watchpointed instruction *must* have completed, and other instructions that followed it, in program order, might have completed. For more information see *Recognizing Imprecise Watchpoint Debug events*.

- The watchpoint *must* be taken before any exceptions that occur in program order after the watchpoint is triggered.

- All the registers written by the watchpointed instruction are updated.

- Any memory accessed by the watchpointed instruction is updated.

An imprecise watchpoint is not an External Abort. An imprecise watchpoint:

- is not affected by the EA bit in the Secure Configuration Register (SCR)

- is not ignored when the A flag, bit [8] of the CPSR, is set to 1.

An imprecise watchpoint is also more constrained than an imprecise Data Abort, because it must be possible to return to the program that caused the watchpoint.

On an Imprecise Watchpoint Debug event, the DSCR[5:2] Method of Debug Entry bits are set to Imprecise Watchpoint Occurred.

#### **Recognizing Imprecise Watchpoint Debug events**

When an instruction that consists of multiple memory operations is accessing Device or Strongly Ordered memory, and an Imprecise Watchpoint Debug event is signalled by a memory operation other than the first operation of the instruction, the Debug event *must not* cause Debug state entry or a Debug Exception until all the operations have completed. This ensures the memory access rules for Device and Strongly Ordered memory are preserved.

Examples of instructions that cause multiple memory operations are the LDM and LDC instructions.

– Note –

To understand why the architecture does not allow the Imprecise Watchpoint Debug event to be taken before the watchpointed instruction completes, consider an LDM instruction accessing Device or Strongly Ordered memory, with an Imprecise Watchpoint Debug event signalled after the first word of memory is accessed. If the Debug event was taken immediately, the LDM would be re-executed on return from the event handler. This would cause a new access to the first word of memory, breaking the rule that, for Device or Strongly Ordered memory, each memory operation of an instruction is issued precisely once.

#### 2.3.2 Breakpoint Debug events

Breakpoint Debug events are controlled by pairs of registers referred to as *Breakpoint Register Pairs* (BRPs). An implementation may contain many BRPs. The first two BRPs are identified as BRP0 and BRP1, and this numbering pattern continues for additional BRPs. BRPn refers to any particular pair. BRPn consists of two registers:

- a Breakpoint Control Register, BCRn

- a Breakpoint Value Register, BVRn.

For a given Breakpoint Register Pair, BRPn, a Breakpoint Debug event occurs when:

- BCRn is programmed for linked or unlinked *Instruction Virtual Address* (IVA) match or mis-match. See *Memory addresses* on page 2-13 for a definition of the IVA.

- The IVA of an instruction is compared with the BVRn value:

- for a match, if BCRn is programmed for matches

- for a mis-match, if BCRn is programmed for mis-matches.

——Note —

For more information on address matching and mis-matching, see *Variable length instruction sets* on page 2-11 and *Byte address select, bits* [8:5] on page 10-41.

- At the time when the breakpoint is evaluated, all the conditions specified in BCRn match.

- The breakpoint is enabled.

- If BCRn is programmed for linked Context ID match and, at the time the breakpoint is evaluated:

- the linked BRP indicated by BCRn, BRPm, is enabled

- the value held in BVRm matches the Context ID held in CP15 register 13.

- The instruction is committed for execution. The Debug event is generated whether the instruction passes or fails its condition code.

A Breakpoint Debug event also occurs when:

- BCRn is programmed for unlinked Context ID match.

- The Context ID, in CP15 register 13, matches the BVRn value.

- At the same time as the breakpoint is evaluated, all the conditions specified in BCRn match.

- The breakpoint is enabled.

- The instruction is committed for execution. The Debug event is generated whether the instruction passes or fails its condition code.

If Monitor Debug-mode is selected and enabled then the behavior is UNPREDICTABLE if both of the following are true:

- BCRn is programmed for linked or unlinked IVA mismatch, or BCRn is programmed for unlinked Context ID match.

- BCRn is programmed to generate Debug Events in a privileged mode or in any mode.

Breakpoint Debug events are precise. That is, the Debug event acts like an exception that cancels the breakpointed instruction. Breakpoint Debug events must be evaluated before the instruction is executed. See *Generation of Debug events* on page 2-20.

For more information, see *Breakpoint Value Registers (BVRn)* on page 10-39 and *Breakpoint Control Registers (BCRn)* on page 10-40.

#### Variable length instruction sets

In the ARMv7 Architecture Specification:

- a variable length instruction set is one where instructions comprise one or more units of memory, each of a fixed size.

- a fixed length instruction set is one where instructions are always a single unit of memory of a fixed size.

Thumb-2, Thumb-2EE and Java byte codes are examples of variable length instruction sets. In Thumb-2 and Thumb-2EE, an instruction comprises one or two halfwords. In Java, an instruction comprises one or more bytes.

In the Thumb instruction set, the BL instruction consists of two halfwords:

- On processors that do not implement Thumb-2 instructions, implementations can choose to execute the two halfwords separately. In these cases Thumb is considered as a fixed length instruction set

- Alternatively, in an implementation where the Thumb BL instruction is executed as a single instruction, Thumb is considered as a variable length instruction set.

The distinction between these two implementations of the Thumb instruction set is whether the second half of the BL instruction can be considered as a valid target for an exception return. In other words, Thumb is implemented as a variable length instruction set if an exception can be taken between executing the two halves of a BL instruction.

ARM instructions are all a fixed size, and therefore ARM is fixed length instruction set.

In ARMv7, a BRP configured such that a match occurs on an address other than the first unit of the instruction does not cause the instruction to generate a Breakpoint Debug event. For example, on a Thumb-2 instruction, a BRP that matches the second halfword of the instruction will not cause the instruction to generate a Breakpoint Debug event.

Instructions in a fixed length instruction set consist of a single unit, which is therefore the first unit of the instruction. For instructions in a variable length instruction set consisting of more than one unit, the first unit of the instruction is defined as the unit of the instruction with the lowest address in memory.

In ARMv6 the behavior of breakpoints that match on an instruction memory unit other than the first one is IMPLEMENTATION DEFINED. However, ARMv6 specifies that, for the Java instruction set, breakpoints matching on operands do not cause the instruction to be breakpointed. A Breakpoint Debug event is only generated if the BRP is configured to match the opcode. The opcode is always the first memory unit of the instruction.

In all cases, a debugger must configure the BRP such that it matches on all bytes of the first unit of the instruction, otherwise the generation of Breakpoint Debug events is UNPREDICTABLE.

On a ARMv6 architecture processor that does not implement Thumb-2 instructions and that allows an exception to be taken between executing the two halves of a Thumb BL instruction, a Debugger must treat the Thumb BL as two instructions, and therefore set breakpoints on both halves of the instruction. This might require two BRPs.

#### — Note ——

To ensure compatibility across ARMv6 implementations, a debugger can always treat BL as two instructions when debugging code on an ARMv6 processor that does not implement Thumb-2 instructions.

#### For example:

- On an ARMv7 processor:

- To breakpoint on a 32-bit Thumb-2 instruction starting at address 0x8000, a Debugger must set BVRn = 0x8000 and BCRn[8:5] = b0011. These are the settings for breakpointing on any Thumb-2 instruction, including a BL.

- To breakpoint on a 32-bit Thumb-2 instruction starting at address 0x8002, a Debugger must set BVRn = 0x8000 and BCRn[8:5] = b1100.

- To breakpoint on an ARM instruction starting at address 0x8004, a Debugger must set BVRn = 0x8004 and BCRn[8:5] = b1111.

- On an ARMv6 processor that does not implement Thumb-2:

- To breakpoint on a Thumb BL instruction at address 0xC120, a Debugger must set BVRn = 0xC120 and BCRn[8:5] = b1111.

- To breakpoint on a Thumb BL instruction at address 0xC122, a Debugger must set BVRn = 0xC120, BVRm = 0xC124, BCRn[8:5] = b1100 and BCRm[8:5] = b0011.

#### 2.3.3 BKPT Instruction Debug events

A BKPT Instruction Debug event occurs when a BKPT instruction is committed for execution. BKPT is an unconditional instruction.

BKPT Instruction Debug events are precise. That is, the Debug event acts like an exception that cancels the BKPT instruction.

See the *ARM Architecture Reference Manual* for details of the BKPT instruction and its encodings in the ARM and Thumb instruction sets.

#### 2.3.4 Vector Catch Debug events

Vector Catch Debug events are controlled by the Vector Catch Register (VCR).

A Vector Catch Debug event occurs when:

- The IVA of an instruction matches a vector location address for the current security world. See *Memory addresses* for a definition of the IVA.

- At the same time as the vector catch is evaluated, the corresponding bit of the VCR is set to 1, indicating vector catch enabled.

- The instruction is committed for execution. The Debug event is generated whether the instruction passes or fails its condition code.

Vector Catch Debug events must be evaluated before the instruction is executed. The vector catch behaves exactly like a BRPn set with BVRn[31:2] set to the top 30 bits of the exception vector address, and BCRn[8:5], the Byte Address Select field, set to b1111 and BCRn programmed for unlinked IVA match.

—— Note ———

Under this model, any instruction prefetched from an exception vector address that is committed for execution can trigger a Vector Catch Debug event, not just those due to exception entries.

Instruction fetches from non word-aligned addresses within the 4-bytes of the exception vector address also trigger vector catches. For example, a Thumb instruction fetch from the second half-word of the address can trigger a vector catch.

However, unlike breakpoints, if the vector catch address matches a unit of an instruction in a variable length instruction set that is not the first unit of the instruction, vector catch generation is UNPREDICTABLE. See *Variable length instruction sets* on page 2-11 for more information on breakpoint generation and variable length instruction sets.

If Monitor Debug-mode is selected and enabled, and the vector is either the Prefetch abort vector or the Data Abort vector, the Debug event is ignored.

Vector Catch Debug events are precise. That is, the Debug event acts like an exception that cancels the instruction at the caught vector. Vector Catch Debug events must be evaluated before the instruction is executed. See *Generation of Debug events* on page 2-20.

For more information, see Vector Catch Register (VCR) on page 10-54.

#### 2.3.5 Memory addresses

On processors that implement the *Virtual Memory System Architecture* (VMSA), and also implement the *Fast Context Switch Extension* (FCSE):

• It is IMPLEMENTATION DEFINED whether the *Instruction Virtual Address* (IVA) used in generating Breakpoint Debug events is the *Modified Virtual Address* (MVA) or *Virtual Address* (VA) of the instruction.

- It is IMPLEMENTATION DEFINED whether the *Data Virtual Address* (DVA) used in generating Watchpoint Debug events is the MVA or VA of the data access.

- The IVA used in generating Vector Catch Debug events is always the VA of the instruction.

- The *Watchpoint Fault Address Register* (WFAR) reads a VA plus an offset dependent on the processor state.

- The *Program Counter Sampling Register* (PCSR) reads a VA plus an offset dependent on the processor state.

— Note ———

The use of the FCSE is deprecated in ARMv7.

On processors that implement the VMSA, and do not implement the FCSE:

- The IVA used in generating Breakpoint Debug events is the VA of the instruction.

- The DVA used in generating Watchpoint Debug events is the VA of the data access.

- The IVA used in generating Vector Catch Debug events is the VA of the instruction.

- The WFAR reads a VA plus an offset dependent on the processor state.

- The PCSR reads a VA plus an offset dependent on the processor state.

On processors that implement the *Protected Memory System Architecture* (PMSA), all addresses are *Physical Addresses* (PAs):

- The IVA used in generating Breakpoint Debug events is the PA of the instruction.

- The DVA used in generating Watchpoint Debug events is the PA of the data access.

- The IVA used in generating Vector Catch Debug events is the PA of the instruction.

- The WFAR reads a PA plus an offset dependent on the processor state.

- The PCSR reads a PA plus an offset dependent on the processor state.

For more information about the WFAR, see *Effects of Debug Exceptions on CP15 registers and the WFAR* on page 3-4, *The effect of entering Debug state on CP15 registers and the WFAR* on page 4-4, and *Watchpoint Fault Address Register (WFAR)* on page 10-22.

For more information about the PCSR, see *Program counter sampling register* on page 8-3 and *Program Counter Sampling Register (PSCR)* on page 10-31.

#### 2.3.6 UNPREDICTABLE behavior on Software Debug events

Vector Catch Debug events on the Prefetch abort and Data Abort vectors are ignored if Monitor Debug-mode is configured, because they would lead to an unrecoverable state.

ARM Limited recommends that VCR[28,27,12,11,4,3] are always programmed as zero when Monitor Debug-mode is configured, see *Vector Catch Register (VCR)* on page 10-54.

Vector Catch Debug events on the Secure Monitor Call vector are not ignored. However, VCR[10] should normally also be programmed as zero; see *Monitor Debug-mode vector catch on Secure Monitor Call* on page 2-17.

In ARMv6 the following events are ignored if Monitor Debug-mode is configured, because they can lead to an unrecoverable state:

- Unlinked Context ID Breakpoint Debug events, if the processor is running in a privileged mode.

- Breakpoint Debug events with BCR[22:21] = b10, if the processor is running in a privileged mode.

In ARMv7, debuggers must avoid these cases by restricting the programming of the BCR if Monitor Debug-mode is enabled and selected. This means that the allowed values of the Privileged Mode control bits, bits [2:1], of BCRn must be restricted in the following cases:

- if BCRn[22:20] = b010, selecting an unlinked Context ID breakpoint

- If BCRn[22:20] = b100 or b101, selecting an IVA mismatch breakpoint.

For these cases, BCRn[2:1] must be programmed to one of:

- b00, selecting match only in User, Supervisor or System Mode

- b10, selecting match only in User Mode.

See *Debug exceptions in abort handlers* for additional points that must be considered before using the b00 setting.

— Caution ———

The following values must not be selected for BCRn[2:1]:

- b01, match in any privileged mode

- b11, match in any mode.

For details of programming the BCR see Breakpoint Control Registers (BCRn) on page 10-40.

If these restrictions are not followed, the processor behavior on a resulting Debug event is UNPREDICTABLE. The processor can enter an unrecoverable state, because taking the Debug Exception does not take the processor out of the state in which the Debug event occurs.

## Debug exceptions in abort handlers

The previous section indicated that, in ARMv7, a debugger might set BCR[2:1] to b00, match in User, Supervisor and System Modes, to avoid the possibility of reaching an unrecoverable state in the unlinked Context ID and IVA mismatch breakpoint cases when Monitor Debug-mode is selected. However, BCR[2:1] must only be programmed to b00 if you are confident that the abort handler will not switch to one of these modes before saving context that may be corrupted by a additional Debug event. The context that might be corrupted by such an event includes R14\_abt, SPSR\_abt, IFAR, DFAR, and DFSR.

It is unlikely that an abort handler would switch to User Mode to process an abort before saving these registers, so setting BCR[2:1] to b10, match only in User Mode, is safer

Also, take care when setting a Breakpoint or BKPT Instruction Debug event inside a Prefetch abort or Data Abort handler, or when setting a Watchpoint Debug event on a data address that might be accessed by any of these handlers.

In general, the user must only set Breakpoint or BKPT Instruction Debug events inside an abort handler at a point after the context that would be corrupted by a Debug event has been saved. Breakpoint Debug events in code that may be run by an abort handler can be avoided by setting BCR[2:1] to b00 or b01, as appropriate.

Watchpoint Debug events in abort handlers can be avoided by setting WCR[2:1] for the watchpoint to b10, match only non-privileged accesses, if the code being debugged is not running in a privileged mode.

Failure to follow these guidelines may lead to Debug events occurring before the handler is able to save the context of the abort causing the context to be overwritten, resulting in UNPREDICTABLE software behavior. The context that might be corrupted by such events includes R14\_abt, SPSR\_abt, IFAR, DFAR, and DFSR.

## Debug events in the debug monitor

Because Debug Exceptions are overlaid on top of the Data Abort and Prefetch abort exceptions, the precautions outlined in the section *Debug exceptions in abort handlers* on page 2-15 also apply to debug monitors. The suggested settings for breakpoints and watchpoints that can avoid taking Debug Exceptions within a Data Abort handler can be used to avoid taking Debug Exceptions in the debug monitor.

In addition, particularly on ARMv7 processors that do not implement the Extended CP14 Interface, and particularly those that implement Precise Watchpoint Debug events, when Monitor Debug-mode is enabled debuggers must avoid:

- setting Watchpoint Debug events on the addresses of debug registers

- setting Breakpoint and Vector Catch Debug events on the addresses of instruction within the debug monitor.

In particular, it is unwise to set a watchpoint on the address of the Watchpoint Control Register (WCR) for that watchpoint, or to set a breakpoint on the address of an instruction that disables the breakpoint.

As noted in section Generation of Debug events on page 2-20:

- a write to the WCR for a watchpoint set on the address of that WCR, to disable that watchpoint will trigger the watchpoint

- an instruction that disables a breakpoint on that instruction will trigger the breakpoint.

In the first of these cases:

- if watchpoints are imprecise, the write to the WCR still takes place and the watchpoint is disabled. The debug software must then deal with the re-entrant Debug Exception.

- if watchpoints are precise the value in the WCR after the watchpoint is signaled is unchanged, and the Debug event is left enabled.

In the breakpoint case, the Debug Exception will be taken before the Debug event is disabled.

In both the watchpoint and the breakpoint case it might be impossible to recover.

## Monitor Debug-mode vector catch on Secure Monitor Call

Debuggers must also be cautious about programming a Vector Catch Debug event on the Secure Monitor Call (SMC) vector when Monitor Debug-mode is enabled. If such an event is programmed, the following sequence can occur:

1. Nonsecure code executes an SMC instruction.

– Note ——

- 2. The processor takes the SMC exception, branching to the Monitor vector in Monitor Mode. SCR[0] = 1, indicating the SMC originated in the Nonsecure world.

- 3. The Vector Catch Debug event is taken. Although SCR[0] = 1, the processor is in the Secure World because it is in Monitor Mode.

- 4. The processor jumps to the Secure Prefetch abort vector, and sets SCR[0] = 0.

Aborts taken in Secure World cause SCR[0] to be set to 0.

5. The abort handler at the Secure Prefetch abort handler can tell a Vector Catch Debug event occurred, and can determine the address of the SMC instruction from R14\_mon. However, it cannot determine whether that is a Secure or Nonsecure address.

Therefore, ARM Limited advises you not to program a Vector Catch Debug event on the SMC vector when Monitor Debug-mode is enabled.

— Note — —

This is not a security issue, because the sequence given here can only occur if **SPIDEN** is HIGH.

# 2.4 Halting Debug events

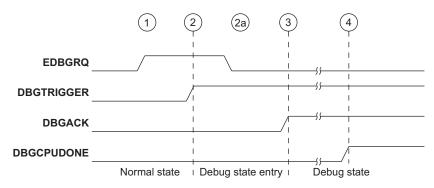

Halting Debug events are caused by the external debug interface requesting that the processor enters Debug state. The three types of Halting Debug event are:

• Activation of the External Debug Request signal, **EDBGRQ**.

This signal can be driven by, for example:

- an external agent such as a cross-triggering unit

- an ETM.

See EDBGRQ, DBGTRIGGER, DBGCPUDONE and DBGACK on page 6-4.

• A Halt Request Debug event. This occurs following receipt of a Halt Request command.

The Halt Request command is activated by a debugger writing 1 to the Halt Request bit of the Debug Run Control Register (DRCR). The processor debug control logic holds the request until the processor enters Debug state.

See Halt Request, bit [0] on page 10-23.

- An OS Unlock Catch Debug event. This occurs when both of the following are true:

- the OS Unlock Catch is enabled in the Event Catch Register

- the OS Lock transitions from being locked to being unlocked.

The event is held by the debug control logic until the processor enters Debug state.

See OS Unlock Catch, bit [0] on page 10-57 and OS Lock Access Register (OSLAR) on page 10-58 for details.

If debug is disabled when one of these events is detected, the request is ignored and no Halting Debug event occurs. Debug is disabled when the external debug interface signal **DBGEN** is LOW.

If **DBGEN** is HIGH, meaning that debug is enabled, and a Halting Debug event occurs when debug is not permitted, the Halting Debug event is pended. This means that the processor enters Debug state when it transitions to a security world or processor mode where debug is permitted.

While a Halting Debug event is pended:

- For External Debug requests, the requestor holds **EBDGRQ** HIGH until the core enters Debug state.

- For the other Halting Debug events the event is pended internally until the processor enters a security world or processor mode where debug is permitted. However, if **DBGEN** goes LOW before the processor enters the world or mode where debug is permitted, it is UNPREDICTABLE whether the processor keeps the event pended. If the debug logic is reset before the processor enters the permitted world or mode, the processor must remove the pending Halting Debug event.

If a Halting Debug event occurs when debug is enabled and permitted, or debug becomes enabled and permitted whilst a Halting Debug event is pending, it is guaranteed that Debug state is entered by the end of the next Instruction Synchronization Barrier (ISB) operation, exception entry, or exception return.

In v6 Debug and v6.1 Debug:

- if you are using the recommended ARM Debug Interface v4.0, the Halt Request command is issued by placing the HALT instruction in the IR register and taking the Debug Test Access Port State Machine (DBGTAPSM) through the Run-Test/Idle state

- the OS Unlock Catch Debug event is not supported.

In v6 Debug it is IMPLEMENTATION DEFINED whether Halting Debug events cause entry to Debug state when Halting Debug-mode is not configured and enabled

# 2.5 Generation of Debug events

The generation of Breakpoint and Watchpoint Debug events can be dependent on the context of the processor, including:

- the current processor mode

- the contents of the Context ID register

- the Secure world setting, if the processor implements Security Extensions.

The generation of Debug events is also dependent on the state of the debug logic:

- Breakpoint Debug events are dependent on the contents of the relevant Breakpoint Register Pair (BRP)

- Watchpoint Debug events are dependent on the contents of the relevant Watchpoint Register Pair (WRP)

- Linked Breakpoint or Watchpoint Debug events are dependent on the settings of a second BRP

- Vector Catch Debug events are dependent on the settings in the Vector Catch Register (VCR)

- OS Unlock Catch Debug events are dependent on the setting of the Event Catch Register (ECR).

In addition, as shown in Table 2-1 on page 2-2, the generation of Debug events is dependent on:

- the settings of the authentication signals, see *Authentication signals* on page 6-3

- the values in the Debug Status and Control Register (DSCR), see *Halting Debug-mode enable*, *bit* [14] on page 10-15, and *Monitor Debug-mode enable*, *bit* [15] on page 10-15.

The following events are guaranteed to take effect on the Debug event generation logic by the end of the next Instruction Synchronization Barrier (ISB) operation, exception entry, or exception return:

- Context changing operations, including:

- mode changes

- writes to the Context ID register

- Secure world changes.

- Operations that change the state of the Debug event generation logic, including:

- writes to BRP registers, for Breakpoint Debug events, or linked Breakpoint or Watchpoint Debug events

- writes to WRP registers, for Watchpoint Debug events

- writes to the VCR register, for Vector Catch Debug events

- writes to the ECR, for OS Unlock Catch Debug events

- changes to the authentication signals

- writes to the DSCR register.

Exception return sequences are usually also context changing operations, and hence the context change operation is guaranteed to take effect on the breakpoint matching logic by the end of that exception return sequence.

If you require a change in the Debug event generation logic to complete before a particular event or piece of code is debugged then you must ensure there is an explicit synchronization operation after the change in the Debug settings. In the absence of an explicit synchronization operation, the changes take effect as operations drain down the pipeline. This might be acceptable in some situations, if you require only that the debug changes take effect within a number of instructions.

An explicit synchronization operation is one of:

- an exception entry

- a return from exception

- an Instruction Synchronization Barrier (ISB) instruction.

Between a context change operation and the end of the next explicit synchronization operation it is UNPREDICTABLE whether the processing of a Debug event will depend the old or the new context.

Between operations that change the state of the Debug event generation logic and the end of the next ISB, exception entry or exception return, it is UNPREDICTABLE whether Debug event generation depends on the old or the new settings.

#### – Note –––––

The rules for how a write to a debug register through a Memory-mapped interface has side-effects, for example, the enabling or disabling of a Debug event, are defined by the memory ordering model of the ARM Architecture. See *Synchronization of debug register updates* on page 5-18 and the ARM Architecture Reference Manual for more information.

It is not a requirement of this architecture that such changes take effect on instruction fetches from the memory system, or on memory accesses made by the processor, at the same point as they take effect on the debug logic. The only architectural requirement is that such a change executed before an Instruction Synchronization Barrier (ISB) operation must be visible to both the memory system and the debug logic for all instructions executed after the ISB operation. This requirement is described earlier in this section.

Watchpoint Debug events must be evaluated before a memory access operation is observed. Breakpoint and Vector Catch Debug events must be evaluated before the instruction is executed, that is, before the instruction has any effect on the architectural state of the processor. As a result, if the instruction is one that modifies the context in which Debug events are evaluated, the Debug event must be evaluated in terms of the context before the memory access operation is observed or the instruction executes. For example:

• In an ARMv7 implementation that uses the Memory-mapped interface, if the Watchpoint Control Register (WCR) is located in Device or Strongly Ordered memory, a write to the WCR to enable a watchpoint on a Data Virtual Address (DVA) of the WCR itself must not trigger the watchpoint.

\_\_\_\_\_Note \_\_\_\_\_

If the WCR is located in Normal memory, the Memory Ordering Model allows for the write to happen out-of-order, and possibly to be repeated. In this case there is a possibility that the write to the WCR can trigger a watchpoint on this instruction.

Conversely, a write to the WCR to disable the same watchpoint must trigger the watchpoint if the WCR is located in Device or Strongly Ordered memory. For more information see *Debug events in the debug monitor* on page 2-16.

• An instruction that writes to a Breakpoint Control Register (BCR) or Vector Catch Register (VCR) to enable a Debug event on the Instruction Virtual Address (IVA) of the instruction itself *must not* trigger the Debug event.

Conversely, a write to the BCR or VCR to disable the same Debug event must trigger the Debug event.

# 2.6 Debug event priority and order

Table 2-4 shows where Debug events come in the ARM exception priority model.

| Priority order | Exception source                   | Debug event                                        |

|----------------|------------------------------------|----------------------------------------------------|

| Highest        | Reset                              | Not applicable                                     |

|                | Precise Data Abort                 | Watchpoints, precise or imprecise                  |

|                | FIQ                                | Not applicable                                     |

|                | IRQ                                | Not applicable                                     |

|                | Imprecise Abort                    | Not applicable                                     |

|                | Prefetch abort                     | Breakpoints, Vector Catch and Halting Debug events |

| Lowest         | Undefined Instruction, SVC and SMC | BKPT Instruction.                                  |

## Table 2-4 Position of Debug events in the ARM exception priority model

Table 2-4 shows that: