## Arm<sup>®</sup> Architecture Reference Manual Supplement Armv8, for the Armv8-R AArch32 architecture profile

### Arm Architecture Reference Manual Supplement Armv8, for the Armv8-R AArch32 architecture profile

Copyright © 2016-2017, 2020 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

|                  |       |                  | Change History      |

|------------------|-------|------------------|---------------------|

| Date             | Issue | Confidentiality  | Change              |

| 12 Aug 2016      | A.a   | Confidential     | LAC release         |

| 31 Mar 2017      | A.b   | Non-Confidential | EAC release         |

| 06 November 2020 | A.c   | Non-Confidential | Updated EAC release |

|                  |       |                  |                     |

112.0

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. You must follow the Arm's trademark usage guidelines http://www.arm.com/company/policies/trademarks.

Copyright © 2016-2017, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

#### (LES-PRE-20349 version 21.0)

In this document, where the term Arm is used to refer to the company it means "Arm or any of its affiliates as appropriate".

#### — Note —

The term Arm can refer to versions of the Arm architecture, for example Armv8 refers to version 8 of the Arm architecture. The context makes it clear when the term is used in this way.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product. The information in this manual is at EAC quality, which means that all features of the specification are described in the manual.

#### Web Address

http://www.arm.com

## Contents Arm Architecture Reference Manual Supplement Armv8, for the Armv8-R AArch32 architecture profile

|            |                              | Preface       x         About this supplement       x         Using this book       xi         Conventions       xii         Additional reading       xiii         Feedback       xiv                                     |   |

|------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Part A     |                              | Introduction and Architecture Overview                                                                                                                                                                                    |   |

| Chapter A1 | A1.1<br>A1.2<br>A1.3<br>A1.4 | Architecture OverviewAbout the Armv8 architecture and architecture profilesA1-18The Armv8-R AArch32 architecture profileA1-19Supported extensions in Armv8-R AArch32A1-20Changes between Armv7-R and Armv8-R AArch32A1-21 |   |

| Part B     |                              | Differences in the Armv8-R Architecture from Armv8-A                                                                                                                                                                      | 4 |

| Chapter B1 | B1.1<br>B1.2<br>B1.3         | <b>Differences between the Armv8-A and Armv8-R AArch32 Profiles</b><br>Differences from the Armv8-A AArch32 application level architecture                                                                                |   |

## Part C Armv8-R Protected Memory System Architecture

| Chapter C1 |              | Protected Memory System Architecture                   |        |

|------------|--------------|--------------------------------------------------------|--------|

|            | C1.1         | About PMSAv8-32                                        |        |

|            | C1.2         | Protection region attributes and access permissions    |        |

|            | C1.3         | Default memory maps and Background region checks       |        |

|            | C1.4<br>C1.5 | Memory protection<br>PMSAv8-32 implications for caches |        |

|            |              |                                                        |        |

| Part D     |              | Armv8-R Instructions                                   |        |

| Chapter D1 |              | Armv8-R Instruction Set                                |        |

|            | D1.1         | Armv8-R base instructions                              |        |

|            | D1.2         | Armv8-R Advanced SIMD and floating-point instructions  |        |

|            | D1.3<br>D1.4 | Single-precision only floating-point implementations   |        |

|            | D1.4         |                                                        | D1 00  |

| Chapter D2 |              | Description of Redefined and New Instructions          | D0 50  |

|            | D2.1<br>D2.2 | Redefined instructions                                 |        |

|            | D2.2         |                                                        | D2-05  |

| Part E     |              | Armv8-R System Registers and System Instru             | ctions |

| Chapter E1 |              | Armv8-R System Registers and System Instructions       |        |

| -          | E1.1         | Armv8-R System register list                           |        |

|            | E1.2         | Armv8-R System instructions                            | E1-76  |

| Chapter E2 |              | Description of the Redefined or New System Registers   |        |

|            | E2.1         | Redefined System registers                             |        |

|            | E2.2         | New System registers                                   | E2-153 |

| Part F     |              | Differences in Armv8-R Debug from Armv8-A              |        |

| Chapter F1 |              | Differences in Armv8-R Debug from Armv8-A              |        |

|            | F1.1         | Differences from Armv8-A invasive debug                | F1-186 |

|            | F1.2         | Differences from Armv8-A non-invasive debug            |        |

|            | F1.3         | Differences from Armv8-A external debug                | F1-188 |

| Part G     |              | Armv8-R External Debug Registers                       |        |

| Chapter G1 |              | Armv8-R External Debug Registers                       |        |

| ·          | G1.1         | Armv8-R external debug register list                   | G1-194 |

| Chapter G2 |              | Description of the Redefined External Debug Registers  |        |

| -          | G2.1         | Redefined external debug registers                     | G2-198 |

| Part H     |              | Architectural Pseudocode for Armv8-R AArch             | 32     |

| Chapter H1 |              | Armv8-R AArch32 Pseudocode                             |        |

| •          | H1.1         | Pseudocode limitations                                 | H1-230 |

|            | H1.2         | Pseudocode for AArch32 operation                       |        |

|            | H1.3         | Shared pseudocode                                      | H1-289 |

# Part I Appendixes Appendix I1 Armv8-R AArch32 CONSTRAINED UNPREDICTABLE behaviors

I1.1 Reserved values in System registers and memory attribute settings ...... 11-356

## Preface

This preface introduces the Arm<sup>®</sup> Architecture Reference Manual Supplement Armv8, for the Armv8-R AArch32 architecture profile. It contains the following sections:

- *About this supplement* on page x.

- Using this book on page xi.

- Conventions on page xii.

- *Additional reading* on page xiii.

- *Feedback* on page xiv.

## About this supplement

This supplement describes the changes that are introduced by the Armv8-R AArch32 architecture. For a summary of these changes, see *The Armv8-R AArch32 architecture profile* on page A1-19.

The supplement must be read with the most recent issue of the *Arm*<sup>®</sup> *Architecture Reference Manual Armv8, for Armv8-A architecture profile.* Together, that manual and this supplement provide a full description of the Armv8-R AArch32 architecture.

This manual is organized into parts as described in Using this book on page xi.

### Using this book

The purpose of this book is to describe the changes that are introduced by the Armv8-R AArch32 architecture. It describes the Armv8-R AArch32 profile in terms of how it differs from the Armv8-A profile.

This book is a supplement to the Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile (ARM DDI 0487), and is intended to be used with it. There might be inconsistencies between this supplement and the Armv8-A Architecture Reference Manual due to some late-breaking changes. Therefore, the Armv8-A Architecture Reference Manual is the definitive source of information about Armv8-A.

It is assumed that the reader is familiar with the Armv8-A and Armv8-R architectures.

The information in this book is organized into parts, as described in this section:

| Part A     | Provides an introduction to the Armv8-R architecture.                                           |  |  |

|------------|-------------------------------------------------------------------------------------------------|--|--|

| Part B     | Describes the non-debug features in which the Armv8-R profile differs from the Armv8-A profile. |  |  |

| Part C     | Describes the Armv8-R Protected Memory System Architecture (PMSAv8-32).                         |  |  |

| Part D     | Describes the Armv8-R instruction set.                                                          |  |  |

| Part E     | Describes the Armv8-R System registers and System instructions.                                 |  |  |

| Part F     | Describes the debug features in which the Armv8-R profile differs from the Armv8-A profile.     |  |  |

| Part G     | Describes the Armv8-R debug registers.                                                          |  |  |

| Part H     | Describes the Armv8-R pseudocode.                                                               |  |  |

| Appendixes | Provides additional information.                                                                |  |  |

## Conventions

The following sections describe conventions that this book can use:

- Typographic conventions.

- Signals.

•

- Numbers.

- Pseudocode descriptions.

#### Typographic conventions

The following table describes the typographic conventions:

#### Typographic conventions

| Style                | Purpose                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| italic               | Introduces spec                                                                                                                                                                                                          | Introduces special terminology, and denotes citations.                                                                                                                                                                                                                                                                                        |  |  |

| bold                 | Denotes signal                                                                                                                                                                                                           | names, and is used for terms in descriptive lists, where appropriate.                                                                                                                                                                                                                                                                         |  |  |

| monospace            | Also used in the                                                                                                                                                                                                         | Used for assembler syntax descriptions, pseudocode, and source code examples.<br>Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.                                                                                     |  |  |

| SMALL CAPITALS       |                                                                                                                                                                                                                          | Used for a few terms that have specific technical meanings, and are included in the <i>Glossary</i> in the <i>Arm</i> <sup>®</sup> <i>Architecture Reference Manual Armv8, for Armv8-A architecture profile.</i>                                                                                                                              |  |  |

| Colored text Signals | <ul> <li>A cross-r<br/>page, for</li> <li>A link, to</li> </ul>                                                                                                                                                          | This can be:<br>for example https://developer.arm.com.<br>eference, that includes the page number of the referenced information if it is not on the current<br>example, <i>Pseudocode descriptions</i> .<br>a chapter or appendix, or to a glossary entry, or to the section of the document that defines the<br>erm, for example Chapter A1. |  |  |

|                      | In general this spe<br>recommendations.                                                                                                                                                                                  | cification does not define processor signals, but it does include some signal examples and                                                                                                                                                                                                                                                    |  |  |

|                      | The signal conven                                                                                                                                                                                                        | tions are:                                                                                                                                                                                                                                                                                                                                    |  |  |

|                      | Signal level       The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:         •       HIGH for active-HIGH signals.         •       LOW for active-LOW signals. |                                                                                                                                                                                                                                                                                                                                               |  |  |

| Numbers              | Lowercase n                                                                                                                                                                                                              | At the start or end of a signal name denotes an active-LOW signal.                                                                                                                                                                                                                                                                            |  |  |

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

#### **Pseudocode descriptions**

This book uses a form of pseudocode to provide precise descriptions of the specified functionality.

### Additional reading

This section lists relevant publications from Arm and third parties.

See Developer, https://developer.arm.com, for access to Arm documentation.

#### Arm publications

- Arm<sup>®</sup> Architecture Reference Manual, Armv7-A and Armv7-R edition (ARM DDI 0406).

- Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile (ARM DDI 0487).

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (ARM IHI 0029).

- Arm® Embedded Trace Macrocell Architecture Specification, ETMv4 (ARM IHI 0064).

- Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0 (ARM IHI 0069).

#### Other publications

• JEDEC Solid State Technology Association, Standard Manufacturer's Identification Code, JEP106.

## Feedback

Arm welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title, Arm<sup>®</sup> Architecture Reference Manual Supplement Armv8, for the Armv8-R AArch32 architecture profile.

- The number, ARM DDI 0568A.c.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

—— Note —

Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

## Part A Introduction and Architecture Overview

## Chapter A1 Architecture Overview

This chapter introduces the Armv8 architecture, the architecture profiles it defines, and the Armv8-R AArch32 profile that this manual defines. It contains the following sections:

- *About the Armv8 architecture and architecture profiles* on page A1-18.

- *The Armv8-R AArch32 architecture profile* on page A1-19.

- Supported extensions in Armv8-R AArch32 on page A1-20.

- Changes between Armv7-R and Armv8-R AArch32 on page A1-21.

### A1.1 About the Armv8 architecture and architecture profiles

The Arm architecture that this Architecture Reference Manual describes, defines the behavior of an abstract machine, referred to as a *processing element* (PE). Implementations that are compliant with the Arm architecture must conform to the described behavior of the PE. This manual does not describe how to build an implementation of the PE, nor does it limit the scope of such implementations beyond the defined behaviors.

Except where the architecture specifies differently, the programmer-visible behavior of an implementation that is compliant with the Arm architecture must be the same as a simple sequential execution of the program on the PE. This programmer-visible behavior does not include the execution time of the program.

The Arm Architecture Reference Manual also describes rules for software to use the PE.

The Arm architecture includes definitions of:

- An associated debug architecture.

- Associated trace architectures, which define trace macrocells that implementers can implement with the associated processor hardware. For more information, see the *Embedded Trace Macrocell Architecture Specification*.

The Arm architecture is a *Reduced Instruction Set Computer* (RISC) architecture with the following RISC architecture features:

- A large uniform register file.

- A *load/store* architecture, where data-processing operations only operate on register contents, not directly on memory contents.

- Simple addressing modes, with all *load/store* addresses determined from register contents and instruction fields only.

Armv8 defines three architecture profiles:

- A Application profile:

- Supports a *Virtual Memory System Architecture* (VMSA) based on a *Memory Management Unit* (MMU).

- Supports the A64, A32, and T32 instruction sets.

- **R** Real-time profile, described in this manual:

- Supports a *Protected Memory System Architecture* (PMSAv8-32) based on a *Memory Protection Unit* (MPU).

- Supports the A32 and T32 instruction sets.

- M Microcontroller profile:

- Implements a programmers' model that is designed for low-latency interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high-level languages.

- Supports a PMSA based on an MPU.

- Supports a variant of the T32 instruction set.

This Architecture Reference Manual Supplement:

- Describes the Armv8-R profile in terms of how it differs from the Armv8-A profile. If a definition is not mentioned in this Supplement, the definition in the *Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile* applies.

- Does not describe details of other profiles but assumes knowledge of the Armv8-A profile.

- Describes differences between the Armv7-R and Armv8-R profiles.

## A1.2 The Armv8-R AArch32 architecture profile

The main features of the Armv8-R AArch32 profile are:

- One Execution state, AArch32.

- The A32 and T32 instruction sets, which are compatible with earlier versions of the Arm architecture.

- The *Protected Memory System Architecture* (PMSA) that defines memory ordering and memory management with a single 32-bit *physical address* (PA) space. The Armv8-R PMSA is not compatible with the Armv7-R architecture.

- A programmers' model and its interfaces to System registers that control most PE and memory system features and provide status information.

- Support for Advanced SIMD and floating-point instructions.

- The Armv8-R virtualization model.

- The Armv8 Debug architecture that provides software access to debug features.

## A1.3 Supported extensions in Armv8-R AArch32

#### A1.3.1 Security Extensions

Armv8-R only supports a single Security state, Non-secure.

#### A1.3.2 Armv8.x extensions for the Armv8-A profile

Armv8-R does not support any of the Armv8.x extensions.

#### A1.3.3 Advanced SIMD and floating-point extensions

Both the Advanced SIMD and floating-point instructions are OPTIONAL. When they are implemented, they must conform to the Armv8-A AArch32 specifications.

The inclusion of double-precision floating-point processing is also OPTIONAL. When only the single-precision encoding format is implemented and Advanced SIMD is not implemented, the floating-point implementation must be a D16 implementation.

For more information, see *Advanced SIMD and floating-point support* on page B1-26 and *Single-precision only floating-point implementations* on page D1-54.

## A1.4 Changes between Armv7-R and Armv8-R AArch32

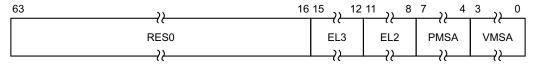

- The architecture is described in terms of the Armv8 Exception levels. Armv8-R implementations support EL0, EL1, and EL2.

- Armv8-R supports virtualization, which provides:

- Support for the EL2 Exception level.

- A second MPU that provides stage 1 memory protection for memory accesses from EL2 and optionally provides stage 2 memory protection for accesses from EL1 and EL0. These protection stages act as address translation regimes in the Armv8-R AArch32 profile.

- A redefined PMSA, PMSAv8, provides:

- A new model for defining protection regions, using a pair of 32-bit addresses to define the region.

- An increase of the minimum protection region size from 32 bytes to 64 bytes.

- No support for subregions or overlapping regions.

- There is no CPACR.D32DIS control in Armv8-R floating-point implementations.

- Armv8-R supports only a trivial Jazelle implementation.

- Divide by zero trapping is not supported in hardware.

Architecture Overview A1.4 Changes between Armv7-R and Armv8-R AArch32

## Part B Differences in the Armv8-R Architecture from Armv8-A

## Chapter B1 Differences between the Armv8-A and Armv8-R AArch32 Profiles

This chapter describes the Armv8-R AArch32 profile. It contains the following sections:

- Differences from the Armv8-A AArch32 application level architecture on page B1-26.

- Differences from the Armv8-A AArch32 instruction sets on page B1-27.

- Differences from the Armv8-A AArch32 system level architecture on page B1-28.

### B1.1 Differences from the Armv8-A AArch32 application level architecture

#### B1.1.1 Advanced SIMD and floating-point support

In addition to the Advanced SIMD and floating-point support in Armv8-A, Armv8-R AArch32 also supports single-precision floating-point implementations without Advanced SIMD.

If an implementation supports only single-precision floating-point operations and does not support Advanced SIMD, then it must implement only 16 double-precision registers, D0-D15, that is, it must be a D16 implementation.

See also Armv8-R Advanced SIMD and floating-point instructions on page D1-53 and Single-precision only floating-point implementations on page D1-54.

Table B1-1 shows the field values that are permitted in Armv8-R in addition to the values that are permitted in Armv8-A.

| Field         | Value | Description                                                                               |

|---------------|-------|-------------------------------------------------------------------------------------------|

| MVFR0.FPDP    | 0000  | No double-precision support.                                                              |

| MVFR0.SIMDReg | 0001  | 16x 64-bit register SIMD&FP register file.                                                |

| MVFR1.FPHP    | 0001  | Support for half-precision to and from single-precision conversion (no double-precision). |

| MVFR1.SIMDHP  | 0000  | No Advanced SIMD                                                                          |

| MVFR1.SIMDSP  | 0000  | No Advanced SIMD                                                                          |

| MVFR1.SIMDInt | 0000  | No Advanced SIMD                                                                          |

| MVFR1.SIMDLS  | 0000  | No Advanced SIMD                                                                          |

#### Table B1-1 Advanced SIMD and floating-point ID field values additionally permitted in Armv8-R

The Armv8-A definitions of HCPTR.TASE, NSACR, and CPACR apply for all implementations, including D16.

#### B1.1.2 Differences from the Armv8-A AArch32 application level programmers' model

The following are the differences from the Armv8-A profile as it is described in chapter *The AArch32 Application Level Programmers' Model* in the *Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

- Armv8-R only supports a single Security state.

- Armv8-R implementations cannot include EL3.

- EL2 is required in Armv8-R.

- Exception levels in Armv8-R are based on the Armv8-A AArch32 PE modes. Hyp mode provides the EL2 functionality.

- Armv8-R supports the A32 and T32 instruction sets with some modifications, see Part D Armv8-R Instructions.

#### B1.1.3 Differences from the Armv8-A AArch32 application level memory model

Armv8-R redefines DMB and DSB, and defines a new instruction, DFB.

Armv8-R relaxes the ordering requirements for DMB and DSB by enforcing ordering only in terms of certain Exception level criteria:

- Accesses from EL1 and EL0 are ordered only with respect to accesses using the same VMID.

- Accesses from EL2 are ordered only with respect to other accesses from EL2.

All other memory barrier requirements are unchanged. See *Memory barriers* in the *Arm*<sup>®</sup> *Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

### B1.2 Differences from the Armv8-A AArch32 instruction sets

See Chapter D1 Armv8-R Instruction Set.

### B1.3 Differences from the Armv8-A AArch32 system level architecture

#### B1.3.1 Differences from the Armv8-A AArch32 system level programmers' model

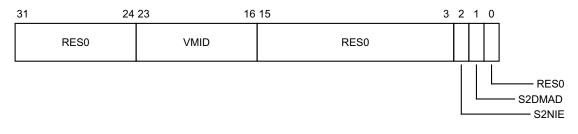

#### Virtualization

Armv8-R includes a modified form of the Armv8-A AArch32 virtualization scheme. In common with AArch32 state in Armv8-A, EL2 in Armv8-R AArch32 supports virtualization and adds Hyp mode to the implemented PE modes. The relationship between Hyp mode and the other implemented PE modes is the same as for an Armv8-A AArch32 implementation that does not include EL3. See *Memory protection units (MPUs)* on page C1-32.

#### GIC

A Generic Interrupt Controller (GIC) implemented with an Armv8-R PE must not implement LPI support.

#### B1.3.2 Differences from the Armv8-A AArch32 system level memory model

#### Address space

Armv8-R uses a 32-bit address space with a flat mapping from the *virtual address* (VA) used by the PE to the *physical address* (PA).

#### Address translation

In Armv8-R, address translation is the process of flat-mapping a VA to a PA and determining the access permissions and memory attributes of the target PA.

#### System register support for IMPLEMENTATION DEFINED memory features

The type, presence, and accessibility of *tightly-coupled memory* (TCM) to EL1 and EL0 or just EL2 is IMPLEMENTATION DEFINED.

#### B1.3.3 The Armv8-R Protected Memory System Architecture, PMSAv8

This Supplement defines PMSAv8. See Chapter C1 Protected Memory System Architecture.

## Part C Armv8-R Protected Memory System Architecture

## Chapter C1 Protected Memory System Architecture

This chapter provides a system-level view of the memory system architecture for an Armv8-R implementation, the *Protected Memory System Architecture* (PMSAv8-32). It contains the following sections:

- *About PMSAv8-32* on page C1-32.

- Protection region attributes and access permissions on page C1-35.

- Default memory maps and Background region checks on page C1-38.

- *Memory protection* on page C1-40.

- *PMSAv8-32 implications for caches* on page C1-44.

### C1.1 About PMSAv8-32

An Arm PMSA is based on a *Memory Protection Unit* (MPU) that provides a memory protection scheme. The PMSA uses a flat mapping between the *virtual address* (VA) accessed by the PE and the 32-bit *physical address* (PA) accessed in the memory system. That is, for all accesses, the VA is the same as the PA, see *Address translation and translation regimes in PMSAv8-32* on page C1-33.

PMSAv8-32 only supports a unified memory protection scheme. It does not support separate instruction and data regions in the address map. PMSAv8-32 is not backwards-compatible with PMSAv7 or earlier Arm PMSAs.

For general information about the Arm memory model, see chapters *The AArch32 Application Level Memory Model* and *The AArch32 System Level Memory Model* in the *Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

#### C1.1.1 Protection regions

An MPU defines protection regions in the 4GB address map. A protection region is a contiguous memory region for which the MPU defines the memory attributes, for example the memory type and the access permissions.

Protection regions:

- Are defined by a pair of a Base Address Register and a Limit Address Register, see *Memory protection units* (*MPUs*).

- Have a minimum size of 64 bytes.

- Have a maximum size of the entire address map, 4GB.

- Must not overlap.

- Do not need to be contiguous.

The definition of a protection region specifies the start and the end of the region, the access permissions to the region, and the memory attributes for the region. For more information, see *Memory protection* on page C1-40.

#### C1.1.2 Memory protection units (MPUs)

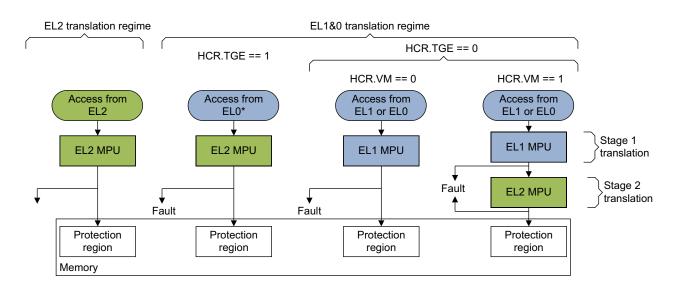

PMSAv8-32 defines two MPUs:

#### EL1 MPU

Defines the protection regions for accesses from EL1 and from EL0.

#### EL2 MPU

Defines the protection regions for accesses from EL2.

When the value of HCR.VM is 1 and for accesses from EL1 and from EL0, the EL2 MPU uses these protection regions to modify the access permissions and memory attributes that are assigned by the EL1 MPU.

See *Protection region attributes and access permissions* on page C1-35. For an address that does not match any defined protection region, PMSAv8-32 defines Background regions and default memory maps. See *Default memory maps and Background region checks* on page C1-38.

An PMSAv8-32 implementation can provide a virtualization scheme in which a single PE supports multiple guest environments under the control of a single hypervisor that executes at EL2, where executing at EL2 means executing in Hyp mode. Typically, an operating system executing at EL1 programs the EL1 MPU to define the memory map for its own operation and for applications it runs at EL0. A hypervisor executing at EL2 programs the EL2 MPU to define the memory map for its own operation and to modify the access permission and memory attribute assignments that are performed by the EL1&0 stage 1 translation.

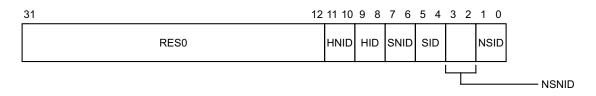

#### C1.1.3 Address translation and translation regimes in PMSAv8-32

In Armv8-R:

- Address translation describes the process of flat mapping the *virtual address* (VA) used by the PE to the *physical address* (PA) accessed in the memory system and determining the access permissions and memory attributes of the target PA.

- A *translation regime* maps a VA to a PA, using one or two stages of address translation to assign the access permissions and memory attributes of the target PA. When two translation stages are used, the intermediate address is treated as an *intermediate physical address* (IPA).

— Note -

These definitions provide consistency between the Armv8-A and Armv8-R descriptions of the memory model.

PMSAv8-32 defines the following translation regimes:

#### EL1&0 translation regime

This assigns the access permissions and memory attributes for any access from EL1 or EL0.

This translation regime has one or two stages of translation:

- All accesses from EL1 or EL0 are translated by the EL1 MPU if it is enabled. This translation is a stage 1 translation.

- When the value of HCR.VM is 1, the access is also translated by the EL2 MPU. This translation is a stage 2 translation, and can modify the access permissions and memory attributes that are assigned by the stage 1 translation.

For the EL1&0 stage 1 translation, ADDRESS is in protection region n if:

PRBAR<n>.BASE:'000000' <= ADDRESS <= PRLAR<n>.LIMIT:'111111'

#### EL2 translation regime

This assigns the access permissions and memory attributes for any access from EL2.

This translation regime has a single stage of translation, stage 1, that is performed by the EL2 MPU.

For the EL2 stage 1 translation, ADDRESS is in protection region *n* if:

HPRBAR<n>.BASE:'000000' <= ADDRESS <= HPRLAR<n>.LIMIT:'111111'

The attributes for a protection region are defined by the combination of:

- The values that are programmed into the Base Address Register and Limit Address Register pair that define the protection region.

- A Memory Attributes Indirection register that is indexed by those values.

#### Figure C1-1 shows how memory accesses are handled when both MPUs are enabled.

- Controlled from EL2

- Controlled from EL1

- \* Access from EL1 is not allowed when HCR.TGE==1

#### Figure C1-1 PMSAv8-32 memory access permission and attribute control

For other scenarios, see *Effect of enabling one or both MPUs on attribute assignment and fault generation* on page C1-40.

### C1.2 Protection region attributes and access permissions

The protection region attribute fields control the memory type, Cacheability, and Shareability of the region. Armv8-R uses the same memory types and memory attributes as Armv8-A.

The Armv8-R identification scheme is based on the scheme that is used by VMSAv8-32 when using the Long-descriptor translation table format. See VMSAv8-32 Long-descriptor format memory region attributes in the Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile.

The memory attributes and access permissions for a protection region are defined by entries in:

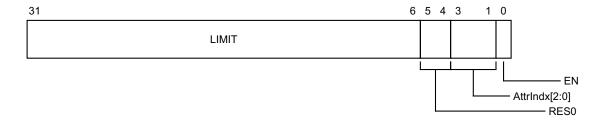

- The PRBAR and PRLAR, or HPRBAR and HPRLAR, that define the region.

- The MAIR<m>.Attr<n> or HMAIR<m>.Attr<n> field that is indexed by PRLAR.AttrIndx or HPRLAR.AttrIndx, respectively. In Armv8-R, the PE always behaves as if the value of TTBCR.EAE were 1 even though the encoding space that TTBCR uses in Armv8-A is unallocated in Armv8-R. For information about the behavior when TTBCR.EAE is 1, see the Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile.

See also Assignment model of memory attributes and access permissions.

For the EL1&0 translation regime, when both MPUs are enabled and the value of HCR.VM is 1, the stage 1 memory attribute and access permission assignments are combined with the stage 2 assignments as described in *Combining attributes* on page C1-36.

#### C1.2.1 Assignment model of memory attributes and access permissions

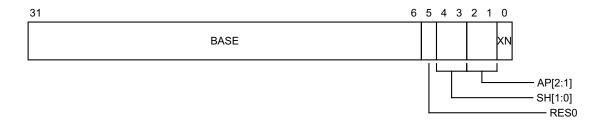

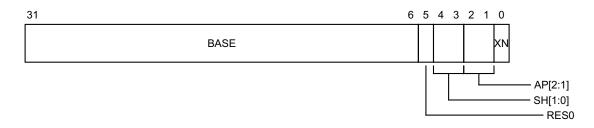

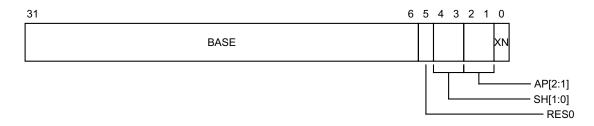

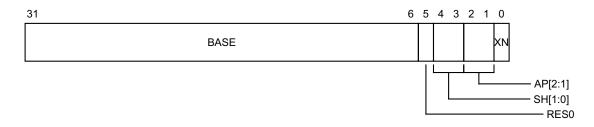

#### PRBAR.SH, HPRBAR.SH

Defines the Shareability, for a Normal memory protection region. For any type of Device memory, and for Normal Inner Non-cacheable, Outer Non-cacheable memory, the value of the SH[1:0] field is IGNORED.

#### PRBAR.AP[2:1], HPRBAR.AP[2:1]

Defines the Access permissions. For encoding information, see the register description.

#### PRBAR.XN, HPRBAR.XN

Defines the Execute-never attribute for the region. For encoding information, see the register description.

**XN** == 1 The region is Execute-never.

PMSAv8-32 makes no distinction between Privileged execute-never (PXN) and Unprivileged execute-never (UXN).

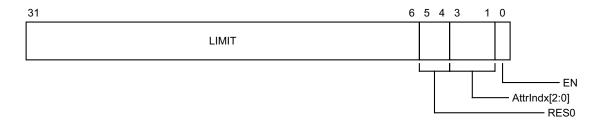

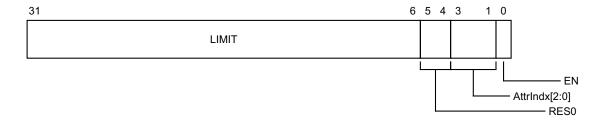

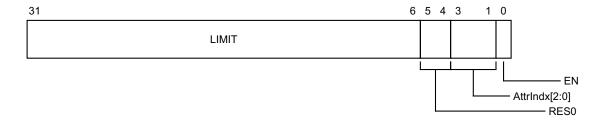

#### PRLAR.AttrIndx, HPRLAR.AttrIndx

Indexes an Attr<*n*> field in MAIR<*m*> or HMAIR<*m*>, as follows:

- AttrIndx[2] indicates the MAIR register to be used:

- AttrIndx[2] == 0 Use MAIR0 or HMAIR0.

- AttrIndx[2] == 1 Use MAIR1 or HMAIR1.

- AttrIndx[2:0] indicates the required Attr field, Attr < n >, where n = AttrIndx[2:0].

#### MAIR<*m*>.Attr<*n*>, HMAIR<*m*>.Attr<*n*>

#### Defines:

- The memory type, Normal memory, or a type of Device memory.

- For Normal memory:

- The Inner Cacheability and Outer Cacheability attributes, each of which is one of Non-cacheable, Write-Through Cacheable, or Write-Back Cacheable.

- For Write-Through Cacheable and Write-Back Cacheable regions, the Read-Allocate and Write-Allocate policy hints, each of which is Allocate or Do not allocate.

#### C1.2.2 Combining attributes

For the EL1&0 translation regime, when both MPUs are enabled and the value of HCR.VM is 1, the stage 1 and stage 2 attributes and access permissions are combined as follows:

- If the stage 1 access permissions indicate that an access is not permitted, a stage 1 Permission fault is generated regardless of the stage 2 permissions.

- If the stage 1 access permissions indicate that an access is permitted but the stage 2 access permissions indicate that it is not permitted, a stage 2 Permission fault is generated.

- If an access is permitted by both the stage 1 and the stage 2 access permissions, the memory attributes are combined as shown in Table C1-1, Table C1-2, and Table C1-3 on page C1-37.

| Rule                                                                                    | If the memory type assigned by either stage is: | The resultant memory type is: |

|-----------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------|

| Device has precedence over<br>Normal                                                    | Any Device memory type                          | A Device memory type          |

| non-Gathering has precedence over Gathering                                             | A Device-nGxx memory type                       | A Device-nGxx memory type     |

| non-Reordering has precedence<br>over Reordering                                        | A Device-nGnRx memory type                      | A Device-nGnRx memory type    |

| No Early Write<br>Acknowledgement has<br>precedence over Early Write<br>Acknowledgement | The Device-nGnRnE memory type                   | The Device-nGnRnE memory type |

Table C1-1 Combining the stage 1 and stage 2 memory type assignments

Regardless of any Shareability attribute that results from the combinations that are described in Table C1-3 on page C1-37:

- Any location for which the resultant memory type is any type of Device memory is always treated as Outer Shareable.

- Any location for which the resultant memory type is Normal Inner Non-cacheable, Outer Non-cacheable is always treated as Outer Shareable.

Table C1-2 shows the assignments at each stage of translation are combined to create the resultant Cacheability attribute. These rules apply independently for the Inner Cacheability and Outer Cacheability attributes.

|  | Table C1-2 Comb | bining Cacheability | v assignments t | for Normal memory |

|--|-----------------|---------------------|-----------------|-------------------|

|--|-----------------|---------------------|-----------------|-------------------|

| Stage 1 assignment                    | Stage 2 assignment                    | Resultant Cacheability  |

|---------------------------------------|---------------------------------------|-------------------------|

| Non-cacheable                         | Any                                   | Non-cacheable           |

| Any                                   | Non-cacheable                         | Non-cacheable           |

| Write-Through Cacheable               | Write-Through or Write-Back Cacheable | Write-Through Cacheable |

| Write-Through or Write-Back Cacheable | Write-Through Cacheable               | Write-Through Cacheable |

| Write-Back Cacheable                  | Write-Back Cacheable                  | Write-Back Cacheable    |

A protection region is treated as Outer Shareable, regardless of any Shareability assignments at either stage of translation if:

The resultant memory type attribute, as described in Table C1-1, is any type of Device memory.

The resultant memory type attribute, as described in Table C1-1, is Normal memory, and the resultant Cacheability, as described in Table C1-2, is Inner Non-cacheable, Outer Non-cacheable.

For a protection region with a resultant memory type attribute of Normal that is not Inner Non-cacheable, Outer Non-cacheable, Table C1-3 shows how the Shareability attribute is obtained from the assignment at each stage of translation.

|                    |                    | Non-cacheable memory   |

|--------------------|--------------------|------------------------|

| Stage 1 assignment | Stage 2 assignment | Resultant Shareability |

| Outer Shareable    | Any                | Outer Shareable        |

| Inner Shareable    | Outer Shareable    | Outer Shareable        |

| Inner Shareable    | Inner Shareable    | Inner Shareable        |

| Inner Shareable    | Non-shareable      | Inner Shareable        |

| Non-shareable      | Outer Shareable    | Outer Shareable        |

| Non-shareable      | Inner Shareable    | Inner Shareable        |

| Non-shareable      | Non-shareable      | Non-shareable          |

## Table C1-3 Combining Shareability assignments for Normal not Inner Non-cacheable, Outer Non-cacheable memory

•

### C1.3 Default memory maps and Background region checks

Each PMSAv8-32 MPU has an associated default memory map which is used when the MPU is not enabled.

When the MPU is enabled and Background region checking is enabled, privileged accesses that do not hit defined protection regions undergo a second check.

- For the EL1 MPU, Background region checking is enabled for privileged access when the value of SCTLR.BR is 1.

- For the EL2 MPU, Background region checking is enabled for accesses from EL2 when the value of HSCTLR.BR is 1.

For details, see Effect of enabling one or both MPUs on attribute assignment and fault generation on page C1-40.

#### C1.3.1 EL1 MPU default memory map

Table C1-4 and Table C1-5 describe the default memory map defined for the EL1 MPU. When the value of HCR.DC is 0, Background region checking by the EL1 MPU also uses this memory map.

#### Table C1-4 Instruction accesses and EL1 Background region checks

| Address range           | SCTLR.I == 0                        | SCTLR.I == 1                                      | XN                  |

|-------------------------|-------------------------------------|---------------------------------------------------|---------------------|

| 0x00000000 — 0x7FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Through Cacheable | Execution permitted |

| 0x80000000 — 0xFFFFFFFF | Not applicable                      | Not applicable                                    | Execute-never       |

#### Table C1-5 Data accesses and EL1 Background region checks

| Address range           | SCTLR.C == 0                        | SCTLR.C == 1                                                      |

|-------------------------|-------------------------------------|-------------------------------------------------------------------|

| 0x00000000 — 0x3FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Back, Write-Allocate<br>Cacheable |

| 0x40000000 — 0x5FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Through Cacheable                 |

| 0x60000000 — 0x7FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Shareable,<br>Non-cacheable                               |

| 0x80000000 - 0xBFFFFFFF | Device-nGnRE                        | Device-nGnRE                                                      |

| 0xC0000000 – 0xFFFFFFFF | Device-nGnRnE                       | Device-nGnRnE                                                     |

When the value of HCR.DC is 1, the Background region and the Default memory map produce accesses with the following attributes:

- Normal memory.

- Non-shareable.

- Inner Write-Back Read-Allocate, Write-Allocate Cacheable.

- Outer Write-Back Read-Allocate, Write-Allocate Cacheable.

- Execution permitted.

#### C1.3.2 EL2 MPU default memory map

Table C1-6 and Table C1-7 describe the default memory map defined for the EL2 MPU. Background region checking by the EL2 MPU also uses this memory map.

| HSCTLR.I == 0                       | HSCTLR.I == 1                                     | XN                                                          |

|-------------------------------------|---------------------------------------------------|-------------------------------------------------------------|

| Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Through Cacheable | Execution permitted                                         |

| Not applicable                      | Not applicable                                    | Execute-never                                               |

|                                     | Normal, Shareable,<br>Non-cacheable               | Normal, Shareable,<br>Non-cacheable Write-Through Cacheable |

#### Table C1-6 Instruction accesses and EL2 Background region checks

#### Table C1-7 Data accesses and EL2 Background region checks

| Address range           | HSCTLR.C == 1                       | HSCTLR.C == 1                                                     |

|-------------------------|-------------------------------------|-------------------------------------------------------------------|

| 0x00000000 — 0x3FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Back, Write-Allocate<br>Cacheable |

| 0x40000000 — 0x5FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Non-shareable,<br>Write-Through Cacheable                 |

| 0x60000000 — 0x7FFFFFFF | Normal, Shareable,<br>Non-cacheable | Normal, Shareable,<br>Non-cacheable                               |

| 0x80000000 — 0xBFFFFFFF | Device-nGnRE                        | Device-nGnRE                                                      |

| 0xC0000000 — 0xFFFFFFFF | Device-nGnRnE                       | Device-nGnRnE                                                     |

## C1.4 Memory protection

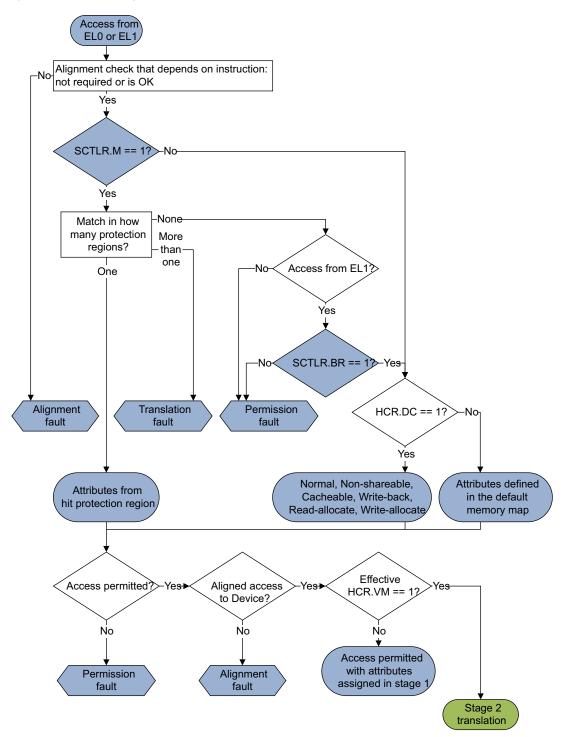

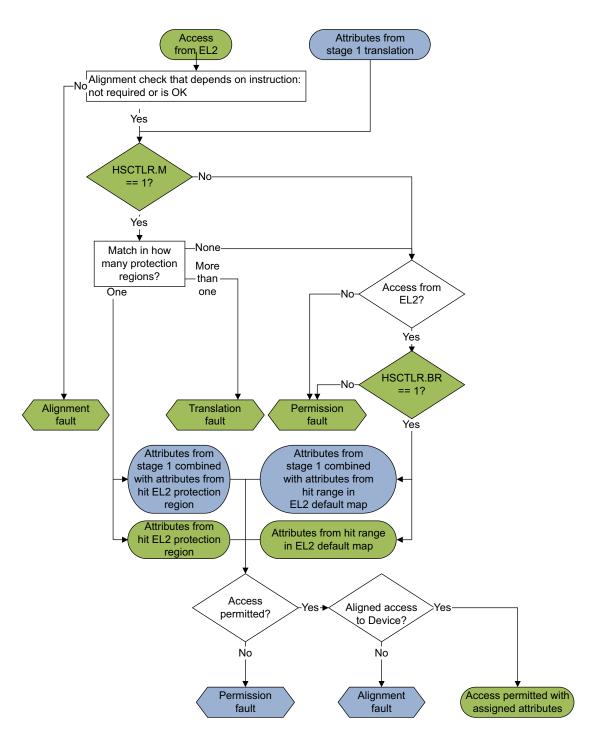

An MPU checks whether the address used by a memory access matches a defined protection region. It uses the properties that are defined for that region or for the Background region to determine whether the access is permitted and if it is permitted, how it must behave.

- The EL1 MPU is enabled when the value of SCTLR.M is 1.

- The EL2 MPU is enabled when the value of HSCTLR.M is 1.

Each MPU provides two mechanisms for defining its own protection regions by:

- Using indirect accesses, where:

- PRSELR/HPRSELR is programmed to specify the required protection region.

- PRBAR/HPRBAR and PRLAR/HPRLAR are programmed to specify the address range and attributes for that region.

- Directly specifying the address range and attributes for the first 32 regions using PRBAR<n>/HPRBAR<n> and PRLAR<n>/HPRLAR<n>.

For the EL2 protection regions, HPRENR provides direct access to the region enable for regions 0-31.

#### C1.4.1 Effect of enabling one or both MPUs on attribute assignment and fault generation

For accesses that fault:

- MPU-generated faults follow the PMSAv8-32 Long-descriptor format and are reported in the same way as VMSAv8-32 faults.

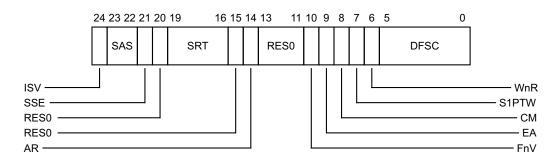

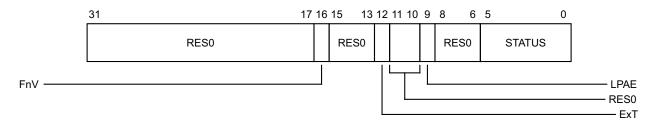

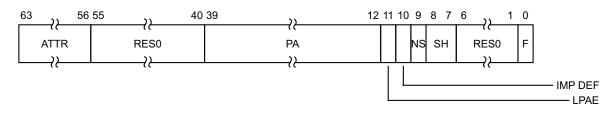

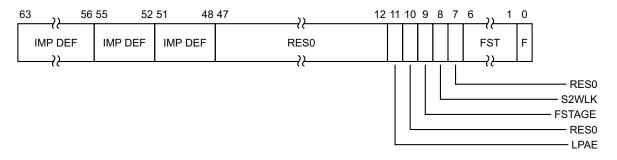

- All MPU faults are treated as level 0 faults. For translation operations, PMSA contexts return the 64-bit PAR format. The PAR format discards the least significant bits but the translation query uses the entire input address. For more information, see the *Types of MMU faults* section in the *The AArch32 Virtual Memory System Architecture* chapter of the *Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile*. For fault status codes, see DFSR, IFSR, and HSR.

- If the value of EDSCR.HDD is 1, stage 2 faults in Debug state are reported as Debug events at EL1. See *Behavior in Debug state* on page F1-189.

For an access that does not fault:

#### When both the EL1 MPU and the EL2 MPU are enabled:

- For an EL2 access (an access from Hyp mode), the EL2 MPU configuration settings determine the access permissions and memory attributes.

- For EL1 and EL0 accesses, the EL1 MPU configuration settings determine the stage 1 access permissions and memory attributes. If the *Effective value* of HCR.VM is 1, those access permissions and memory attributes are then modified by the EL2 MPU, as described in *Combining attributes* on page C1-36.

#### When the EL1 MPU is disabled and the EL2 MPU is enabled:

- For an EL2 access (an access from Hyp mode), the EL2 MPU configuration settings determine the access permissions and memory attributes.

- For an EL1 or EL0 access, the EL1 Background region settings determine the stage 1 access permissions and memory attributes. If the *Effective value* of HCR.VM is 1, those access permissions and memory attributes are then modified by the EL2 MPU, as described in *Combining attributes* on page C1-36.

#### When the EL1 MPU is enabled but the EL2 MPU is disabled:

For an EL2 access (an access from Hyp mode), the EL2 Background region settings determine the access permissions and memory attributes.

For EL1 and EL0 accesses, the EL1 MPU configuration settings determine the access permissions and memory attributes. If the *Effective value* of HCR.VM is 1, those access permissions and memory attributes are then combined with the EL2 Background region settings, as described in *Combining attributes* on page C1-36.

#### When both the EL1 MPU and the EL2 MPU are disabled:

•

- For an EL2 access (an access from Hyp mode), the EL2 Background region settings determine the stage 1 access permissions and memory attributes.

- For an EL1 or EL0 access, the EL1 Background region settings determine the access permissions and memory attributes. If the *Effective value* of HCR.VM is 1, those access permissions and memory attributes are then modified by the EL2 Background region settings, as described in *Combining attributes* on page C1-36.

Figure C1-2 shows the stage 1 translation for EL1 and EL0 accesses.

Figure C1-2 Stage 1 translation for EL1 and EL0 accesses

Figure C1-3 shows the stage 2 translation for EL1 and EL0 and stage 1 translation for EL2 accesses.

Figure C1-3 Stage 2 translation for EL1 and EL0, stage 1 translation for EL2 accesses

Combining is trivial if the EL1 MPU check resulted in attributes from the EL1 Background region because the two Background regions are identical when both of them are enabled.

## C1.5 PMSAv8-32 implications for caches

Enabling or reconfiguring the MPU, or reprogramming any protection regions, can result in new and different memory attributes for a previously accessed or speculatively accessed address. In this situation, the rules for *Mismatched memory attributes* apply. See the *Mismatched memory attributes* section in the *The AArch32 Virtual Memory System Architecture* chapter of the *Arm*<sup>®</sup> *Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

#### C1.5.1 Cache line length

A PMSAv8-32 MPU permits the definition of protection regions that might be smaller than a cache line in the implementation. Therefore, the following rules apply:

- If the MPU is configured such that multiple differing attributes apply to a single cache line, then for any access to that cache line the rules for mismatched memory attributes apply. See the *Memory region attributes* section in the *The AArch32 Virtual Memory System Architecture* chapter of the *Arm*<sup>®</sup> *Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

- Marking any part of a cache line as Write-Back permits the entire line to be treated as Write-Back.

# Part D Armv8-R Instructions

## Chapter D1 Armv8-R Instruction Set

This chapter describes the T32 and A32 instruction sets of the Armv8-R profile. It contains the following sections:

- *Armv8-R base instructions* on page D1-48.

- Armv8-R Advanced SIMD and floating-point instructions on page D1-53.

- Single-precision only floating-point implementations on page D1-54.

- Instruction encodings on page D1-56.

## D1.1 Armv8-R base instructions

Table D1-1 summarizes the instructions that are new in the Armv8-R AArch32 profile or redefined from Armv8-A. For instructions that are unchanged with respect to Armv8-A, see the *Arm® Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

|                              |                                      | Table D1-1 Armv8-R base instruction                 |

|------------------------------|--------------------------------------|-----------------------------------------------------|

| Instruction                  | Status with<br>respect to<br>Armv8-A | Notes                                               |

| ADC                          | Unchanged                            |                                                     |

| ADD                          | Unchanged                            |                                                     |

| ADR                          | Unchanged                            |                                                     |

| AESD, AESE, AESIMC,<br>AESMC | Unchanged                            |                                                     |

| AND                          | Unchanged                            |                                                     |

| ASR                          | Unchanged                            |                                                     |

| В                            | Unchanged                            |                                                     |

| BFC                          | Unchanged                            |                                                     |

| BFI                          | Unchanged                            |                                                     |

| BIC                          | Unchanged                            |                                                     |

| ВКРТ                         | Unchanged                            |                                                     |

| BL, BLX, BX, BXJ             | Unchanged                            |                                                     |

| CBNZ<br>CBZ                  | Unchanged                            |                                                     |

| CDP<br>CDP2                  | Unchanged                            |                                                     |

| CLREX                        | Unchanged                            |                                                     |

| CLZ                          | Unchanged                            |                                                     |

| CMN                          | Unchanged                            |                                                     |

| СМР                          | Unchanged                            |                                                     |

| CPS, CPSID, CPSIE            | Unchanged                            |                                                     |

| CRC32, CRC32C                | Unchanged                            |                                                     |

| DBG                          | Unchanged                            |                                                     |

| DCPS1, DCPS2                 | Unchanged                            |                                                     |

| DCPS3                        | Unused                               |                                                     |

| DFB on page D2-66            | New                                  |                                                     |

| DMB on page D2-59            | Redefined                            | Differences from the Armv8-A AArch32                |

| DSB on page D2-62            | Redefined                            | <i>application level architecture</i> on page B1-26 |

|                              |                                      |                                                     |

#### Table D1-1 Armv8-R base instructions

| Instruction                                                                             | Status with<br>respect to<br>Armv8-A | Notes |

|-----------------------------------------------------------------------------------------|--------------------------------------|-------|

| EOR                                                                                     | Unchanged                            |       |

| ERET                                                                                    | Unchanged                            |       |

| HLT                                                                                     | Unchanged                            |       |

| HVC                                                                                     | Unchanged                            |       |

| ISB                                                                                     | Unchanged                            |       |

| IT                                                                                      | Unchanged                            |       |

| LDA, LDAB, LDAEX,<br>LDAEXB, LDAEXD,<br>LDAEXH, LDAH                                    | Unchanged                            |       |

| LDC, LDC2                                                                               | Unchanged                            |       |

| LDM, LDMIA, LDMFD,<br>LDMDA, LDMFA, LDMDB,<br>LDMEA, LDMIB, LDMED                       | Unchanged                            |       |

| LDR, LDRB, LDRBT, LDRD                                                                  | Unchanged                            |       |

| LDREX, LDREXB, LDREXD,<br>LDREXH, LDRH, LDRHT,<br>LDRSB, LDRSBT, LDRSH,<br>LDRSHT, LDRT | Unchanged                            |       |

| LSL                                                                                     | Unchanged                            |       |

| LSR                                                                                     | Unchanged                            |       |

| MCR, MCR2, MCRR, MCRR2                                                                  | Unchanged                            |       |

| MLA                                                                                     | Unchanged                            |       |

| MLS                                                                                     | Unchanged                            |       |

| MOV                                                                                     | Unchanged                            |       |

| MOVT                                                                                    | Unchanged                            |       |

| MRC, MRC2, MRRC, MRRC2                                                                  | Unchanged                            |       |

| MRS                                                                                     | Unchanged                            |       |

| MSR                                                                                     | Unchanged                            |       |

| MUL                                                                                     | Unchanged                            |       |

| MVN                                                                                     | Unchanged                            |       |

| NOP                                                                                     | Unchanged                            |       |

| ORN                                                                                     | Unchanged                            |       |

| ORR                                                                                     | Unchanged                            |       |

| PKHBT, PKHTB                                                                            | Unchanged                            |       |

|                                                                                         |                                      |       |

| Instruction                                        | Status with<br>respect to<br>Armv8-A | Notes |

|----------------------------------------------------|--------------------------------------|-------|

| PLD                                                | Unchanged                            |       |

| PLI                                                | Unchanged                            |       |

| POP                                                | Unchanged                            |       |

| PUSH                                               | Unchanged                            |       |

| QADD, QADD16, QADD8,<br>QASX, QDADD                | Unchanged                            |       |

| QDSUB, QSAX, QSUB,<br>QSUB16, QSUB8                | Unchanged                            |       |

| RBIT                                               | Unchanged                            |       |

| REV, REV16, REVSH                                  | Unchanged                            |       |

| RFE, RFEDA, RFEDB,<br>RFEIA, RFEIB                 | Unchanged                            |       |

| ROR                                                | Unchanged                            |       |

| RRX                                                | Unchanged                            |       |

| RSB                                                | Unchanged                            |       |

| RSC                                                | Unchanged                            |       |

| SADD16, SADD8                                      | Unchanged                            |       |

| SASX                                               | Unchanged                            |       |

| SBC                                                | Unchanged                            |       |

| SBFX                                               | Unchanged                            |       |

| SDIV                                               | Unchanged                            |       |

| SEL                                                | Unchanged                            |       |

| SETEND                                             | Unchanged                            |       |

| SEV                                                | Unchanged                            |       |

| SEVL                                               | Unchanged                            |       |

| SHA1C, SHA1M, SHA1P,<br>SHA1H, SHA1SU0,<br>SHA1SU1 | Unchanged                            |       |

| SHA256H, SHA256H2,<br>SHA256SU0, SHA256SU1         | Unchanged                            |       |

| SHADD16, SHADD8                                    | Unchanged                            |       |

| SHASX                                              | Unchanged                            |       |

| SHSAX                                              | Unchanged                            |       |

| Instruction                                                                                                                                         | Status with<br>respect to<br>Armv8-A | Notes |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|

| SHSUB16, SHSUB8                                                                                                                                     | Unchanged                            |       |

| SMC                                                                                                                                                 | Unused                               |       |

| SMLABB, SMLABT,<br>SMLATB, SMLATT, SMLAD,<br>SMLADX, SMLAL, SMLALS,<br>SMLALBB, SMLALBT,<br>SMLALTB, SMLALTT,<br>SMLALD, SMLALDX,<br>SMLAWB, SMLAWT | Unchanged                            |       |

| SMLSD, SMLSDX, SMLSLD,<br>SMLSLDX, SMMLA,<br>SMMLAR                                                                                                 | Unchanged                            |       |

| SMMLS, SMMLSR                                                                                                                                       | Unchanged                            |       |

| SMMUL, SMMULR, SMUAD,<br>SMUADX, SMULBB,<br>SMULBT, SMULTB,<br>SMULTT, SMULL, SMULLS,<br>SMULWB, SMULWT                                             | Unchanged                            |       |

| SMUSD, SMUSDX                                                                                                                                       | Unchanged                            |       |

| SRS, SRSDA, SRSDB,<br>SRSIA, SRSIB                                                                                                                  | Unchanged                            |       |

| SSAT, SSAT16                                                                                                                                        | Unchanged                            |       |

| SSAX                                                                                                                                                | Unchanged                            |       |

| SSUB16, SSUB8                                                                                                                                       | Unchanged                            |       |

| STC, STC2                                                                                                                                           | Unchanged                            |       |

| STL, STLB, STLH                                                                                                                                     | Unchanged                            |       |

| STRL, STRLB, STRLH                                                                                                                                  | Unchanged                            |       |

| STM, STMIA, STMEA,<br>STMDA, STMED, STMDB,<br>STMFD, STMIB, STMFA                                                                                   | Unchanged                            |       |

| STR, STRB, STRBT, STRD,<br>STRH, STRHT, STRT                                                                                                        | Unchanged                            |       |

| STRLEX, STRLEXB,<br>STRLEXH, STRLEXD                                                                                                                | Unchanged                            |       |

| SUB                                                                                                                                                 | Unchanged                            |       |

| SVC                                                                                                                                                 | Unchanged                            |       |

|                                                                                                                                                     | Unchanged                            |       |

| Instruction     | Status with<br>respect to<br>Armv8-A | Notes |

|-----------------|--------------------------------------|-------|

| TBB, TBH        | Unchanged                            |       |

| TEQ             | Unchanged                            |       |

| TST             | Unchanged                            |       |

| UADD16, UADD8   | Unchanged                            |       |

| UASX            | Unchanged                            |       |

| UBFX            | Unchanged                            |       |

| UDF             | Unchanged                            |       |

| UDIV            | Unchanged                            |       |

| UHADD16, UHADD8 | Unchanged                            |       |

| UHASX           | Unchanged                            |       |

| UHSAX           | Unchanged                            |       |

| UHSUB16, UHSUB8 | Unchanged                            |       |

| UMAAL           | Unchanged                            |       |

| UMLAL           | Unchanged                            |       |

| UMULL           | Unchanged                            |       |

| UQADD16, UQADD8 | Unchanged                            |       |

| UQASX           | Unchanged                            |       |

| UQSAX           | Unchanged                            |       |

| UQSUB16, UQSUB8 | Unchanged                            |       |

| USAD8           | Unchanged                            |       |

| USADA8          | Unchanged                            |       |

| USAT, USAT16    | Unchanged                            |       |

| USAX            | Unchanged                            |       |

| USUB16, USUB8   | Unchanged                            |       |

| UXTAB, UXTAB16  | Unchanged                            |       |

| UXTAH           | Unchanged                            |       |

| UXTB, UXTB16    | Unchanged                            |       |

| UXTH            | Unchanged                            |       |

| WFE             | Unchanged                            |       |

| WFI             | Unchanged                            |       |

| YIELD           | Unchanged                            |       |

## D1.2 Armv8-R Advanced SIMD and floating-point instructions

The Armv8-R AArch32 profile supports Advanced SIMD and floating-point operations. For the instruction descriptions, see the *Arm<sup>®</sup> Architecture Reference Manual Armv8, for Armv8-A architecture profile.*

Armv8-R can optionally support single-precision floating-point operations without Advanced SIMD.

See also Advanced SIMD and floating-point support on page B1-26 and Single-precision only floating-point implementations on page D1-54.

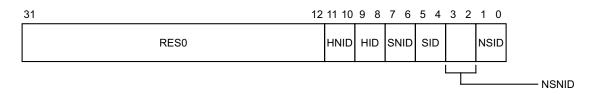

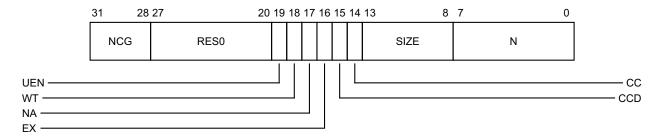

## D1.3 Single-precision only floating-point implementations