# Arm<sup>®</sup> Base System Architecture 1.1 Platform Design Document Non-confidential

Arm Base System Architecture

# Contents

|    | Release information<br>Arm Non-Confidential Document License ("License")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| At | Terms and abbreviations<br>References<br>Rules-based writing<br>Content item identifiers<br>Content item rendering<br>Content item classes<br>Progressive terminology commitment<br>Feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>11</b><br>11<br>12<br>13<br>13<br>13<br>13<br>13<br>14<br>15                                                |  |

| 1  | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                                                                             |  |

| 2  | Introduction2.1Approach and scope2.2How to interpret this document2.3Design patterns2.3.1Non-secure operating systems2.3.2Hypervisors2.3.3Platform security functionality2.3.4Memory partitioning2.3.5Peripheral subsystems                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>17</b><br>17<br>18<br>19<br>19<br>20<br>21<br>22<br>22                                                      |  |

| 3  | Base System Architecture         3.1       Approach         3.2       Scope         3.3       PE Architecture         3.3.1       Operating system         3.3.2       Hypervisor         3.3.3       Platform security functionality         3.3.4       PE Architecture - Future Requirements         3.4       Memory map         3.4.1       Operating system         3.4.2       Platform security functionality         3.5       Interrupt controller         3.5.1       Operating system         3.5.2       Platform firmware         3.6       PPI assignments         3.7       System MMU and device assignment         3.7.1       Operating system         3.7.2       Hypervisor | 23<br>23<br>23<br>25<br>25<br>26<br>26<br>26<br>26<br>26<br>27<br>27<br>27<br>27<br>29<br>29<br>30<br>31<br>31 |  |

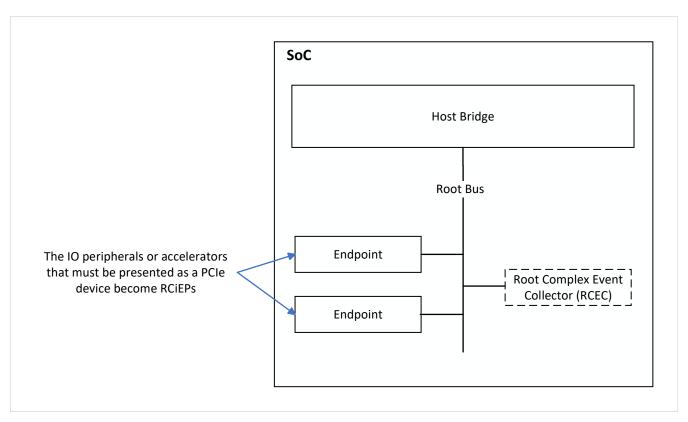

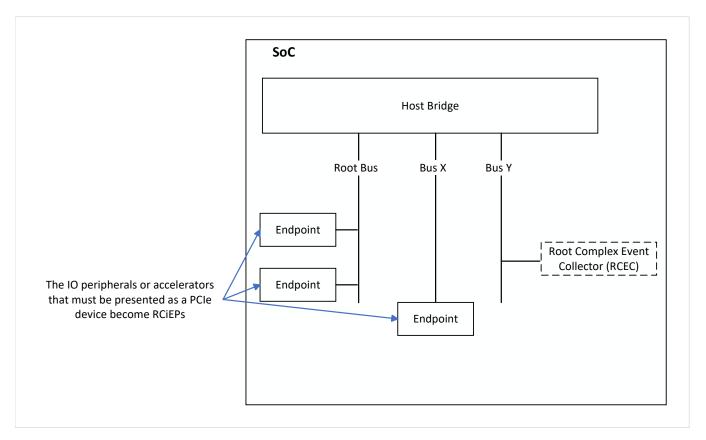

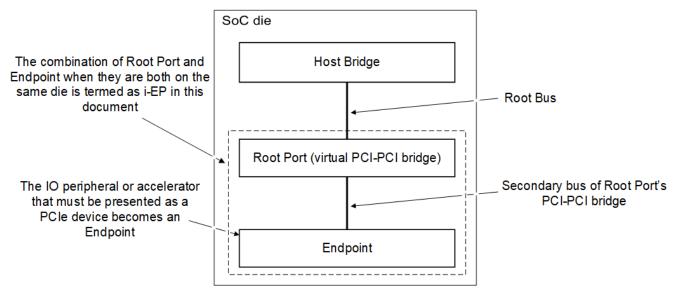

|    | <ul> <li>3.7.3 System MMU and device assignment - Future requirements</li> <li>3.8 Clock and timer subsystem <ul> <li>3.8.1 Operating system</li> </ul> </li> <li>3.9 Wakeup semantics</li> <li>3.10 Power state semantics</li> <li>3.11 Watchdogs</li> <li>3.12 Peripheral subsystems <ul> <li>3.12.1 Platform security functionality</li> <li>3.12.2 PCIe integration</li> </ul> </li> <li>3.13 Presenting an on-chip peripheral as PCIe device <ul> <li>3.13.1 Option 1: Root Complex Integrated Endpoint (RCiEP)</li> </ul> </li> </ul>                                                                                                                                                      | 32<br>33<br>34<br>35<br>39<br>39<br>40<br>40<br>40<br>40                                                       |  |

|   | <ul> <li>3.13.2 Option 2: Integrated Endpoint (i-EP)</li> <li>3.13.3 Option 1 and Option 2: A comparison</li> <li>3.14 Base System Architecture - checklist</li> <li>3.14.1 BSA Level 1 checklist</li> <li>3.14.2 BSA Future Level checklist</li> </ul>                                                                                                                                          | 43<br>44<br>45<br>45<br>48                                                             |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| A | Heterogenous systems<br>A.1 Implementation, identification, and revision differences                                                                                                                                                                                                                                                                                                             | <b>50</b><br>50                                                                        |

| В | Generic UARTB.1AboutB.2Generic UART register frameB.3InterruptsB.4Control and setupB.5Operation                                                                                                                                                                                                                                                                                                  | <b>52</b><br>52<br>52<br>54<br>54<br>54                                                |

| С | Generic Watchdog         C.1       About         C.2       Watchdog operation         C.3       Register summary         C.4       Register descriptions         C.4.1       Watchdog Control and Status Register         C.4.2       Watchdog Interface Identification Register                                                                                                                 | <b>55</b><br>55<br>56<br>58<br>58<br>58<br>58                                          |

| D | SMMUv3 integration                                                                                                                                                                                                                                                                                                                                                                               | 59                                                                                     |

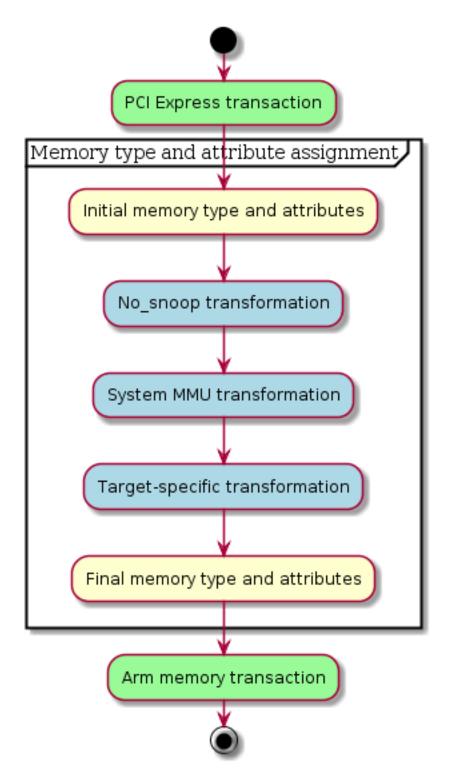

| E | PCI Express integrationE.1Configuration spaceE.2PCI Express memory spaceE.3PCI Express device view of memoryE.4Message Signaled InterruptsE.5GICv3 support for MSI(-X)E.6Legacy interruptsE.7System MMU and Device AssignmentE.8I/O CoherencyE.8.1Memory type and attribute assignmentE.9Legacy I/OE.10Integrated end pointsE.11Peer-to-peerE.12PASID supportE.13PCIe Precision Time Measurement | 60<br>62<br>63<br>63<br>64<br>64<br>64<br>65<br>65<br>65<br>68<br>68<br>68<br>69<br>69 |

| F | RCiEPF.1Rules for RCiEPF.2RCiEP capabilities and registersF.3Register bit field rules for the RCiEP optionF.3.1PCI Express Capabilities RegisterF.3.2Device Capabilities RegisterF.3.3Device Control RegisterF.3.4Device capabilities 2 RegisterF.3.5Device control 2 RegisterF.3.6Power Management Capabilities RegisterF.3.7Power Management Control/Status RegisterF.3.8Data Register         | 70<br>71<br>73<br>74<br>74<br>74<br>75<br>75<br>75<br>75<br>75                         |

| G | I-EP                                                                                                                                                                                                                                                                                                                                                                                             | 77                                                                                     |

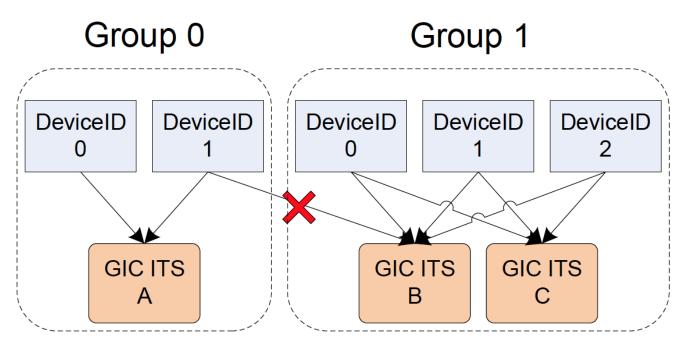

| <ul> <li>G.2 I-EP capabilities and registers</li> <li>G.2.1 Supported Link Speed Declaration in Link Capabilities 2</li> <li>G.3. Register bit field rules for the i-EP option</li> <li>G.3.1 Type 1 header registers</li> <li>G.3.2 Power Management Capabilities Register</li> <li>G.3.3 Power Management Capabilities Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Slot Capabilities Register</li> <li>G.3.6 Slot Control Register</li> <li>G.3.8 I-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.21 Margining Lane Control Register</li> <li>G.3.21 Margining Port Capabilities Register</li> <li>G.3.21 Margining Port Capabilities Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.24 LEP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H.2 Generation and ITS groups</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.3 Examples of ITS groups from firmware data</li> <li>H.4 DeviceID generation and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | pported Link Špeed Declaration in Link Capabilities 2 81<br>bit field rules for the i-EP option 83<br>wer Management Capabilities Register 83<br>the Capabilities Register 83<br>the Capabilities Register 84<br>to Control Register 84<br>to Control Register 84<br>P option: Rules for PCI Express Capabilities Register 84<br>vice Capabilities Register 84<br>vice Capabilities Register 85<br>vice Capabilities Register 85<br>vice Capabilities Register 85<br>vice Capabilities Register 85<br>vice Capabilities 2 Register 85<br>vice Capabilities 2 Register 85<br>vice Control Register 85<br>vice Control Register 85<br>vice Control 2 Register 90<br>vis Control 2 Register 92<br>regining Port Capabilities Register 93<br>of GT/s Status Register 93<br>of GT/s Status Register 93<br>of GT/s Status Register 93<br>vertion and ITS groups 94<br>GT/s Register 94<br>vration and ITS groups 95<br>s ckground 96<br>vis 95<br>s ckground 96<br>vis 100<br>GICv2m architecture 94<br>verture 9 |    | G.1 Rules for i-EP                                                   | 77  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------|-----|

| <ul> <li>G.3 Register bit field rules for the I-EP option</li> <li>G.3.1 Type 1 header registers</li> <li>G.3.2 Power Management Control/Status Register</li> <li>G.3.3 Power Management Control/Status Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Stol Capabilities Register</li> <li>G.3.6 Stol Control Register</li> <li>G.3.7 Stol Status Register</li> <li>G.3.8 I-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.12 Lowice Control 2 Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.16 Link Control 2 Register</li> <li>G.3.17 Link Status Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.20 Link Control 3 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.24 I-EP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H.1 TIS groups</li> <li>H.1 TIS groups</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.3 System description of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> 1 GCV2m Architecture <ol> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>SPI allocation</li> <li>SPI allocation</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | it field rules for the I-EP option 83<br>se 1 header registers 83<br>wer Management Control/Status Register 83<br>ta Register 83<br>ta Capabilities Register 84<br>th Control Register 84<br>th Control Register 84<br>th Control Register 84<br>to Control Register 84<br>vice Capabilities Register 84<br>vice Capabilities Register 85<br>vice Capabilities Register 85<br>vice Control Register 90<br>vice Control Register 92<br>vice Control Register 93<br>virgining Lane Status Register 93<br>virgining Lane Status Register 93<br>virgining Lane Status Register 94<br>da Link Feature Capabilities and Data Link Feature Status 94<br>dT/s Registers and Lane Error Status Register 94<br>viter 95<br>s ckground 96<br>virgin on DeviceID and ITS groups from firmware data 98<br>virgin on DeviceID and ITS groups from firmware data 98<br>virgin on Lane 26<br>virgin on Lane 95<br>virgin on Lane 26<br>virgin on Lane 95<br>virgin 05<br>virgin 05<br>virgin 05<br>virgin 05<br>vir                                                                                        |    | G.2 I-EP capabilities and registers                                  | 78  |

| <ul> <li>G.3.1 Type 1 header registers</li> <li>G.3.2 Power Management Capabilities Register</li> <li>G.3.3 Power Management Control/Status Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Slot Capabilities Register</li> <li>G.3.6 Slot Control Register</li> <li>G.3.7 Slot Status Register</li> <li>G.3.8 LEP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control 2 Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.24 LEP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H.1 11 Background</li> <li>H.1.2 Rules</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Generation of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> I GCV2m Architecture <ol> <li>Background</li> <li>About the Glov2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation<td>be 1 header registers 83 wer Management Capabilities Register 83 wer Management Control/Status Register 83 ta Register 84 to Capabilities Register 84 P option: Rules for PCI Express Capabilities Register 84 wice Capabilities Register 84 wice Capabilities Register 85 wice Cantrol Register 85 wice Capabilities Register 85 wice Control Register 85 wice Control Register 85 wice Control Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Control Register 95 wice Cont</td><td></td><td>G.2.1 Supported Link Speed Declaration in Link Capabilities 2</td><td>81</td></li></ol> | be 1 header registers 83 wer Management Capabilities Register 83 wer Management Control/Status Register 83 ta Register 84 to Capabilities Register 84 P option: Rules for PCI Express Capabilities Register 84 wice Capabilities Register 84 wice Capabilities Register 85 wice Cantrol Register 85 wice Capabilities Register 85 wice Control Register 85 wice Control Register 85 wice Control Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Control Register 95 wice Cont                                                                                                                                                                                                                                                                                                                                                    |    | G.2.1 Supported Link Speed Declaration in Link Capabilities 2        | 81  |

| <ul> <li>G.3.1 Type 1 header registers</li> <li>G.3.2 Power Management Capabilities Register</li> <li>G.3.3 Power Management Control/Status Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Slot Capabilities Register</li> <li>G.3.6 Slot Control Register</li> <li>G.3.7 Slot Status Register</li> <li>G.3.8 LEP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control 2 Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.24 LEP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H.1 11 Background</li> <li>H.1.2 Rules</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Generation of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> I GCV2m Architecture <ol> <li>Background</li> <li>About the Glov2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation<td>be 1 header registers 83 wer Management Capabilities Register 83 wer Management Control/Status Register 83 ta Register 84 to Capabilities Register 84 P option: Rules for PCI Express Capabilities Register 84 wice Capabilities Register 84 wice Capabilities Register 85 wice Cantrol Register 85 wice Capabilities Register 85 wice Control Register 85 wice Control Register 85 wice Control Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Control Register 95 wice Cont</td><td></td><td>G.3 Register bit field rules for the i-EP option</td><td>83</td></li></ol>              | be 1 header registers 83 wer Management Capabilities Register 83 wer Management Control/Status Register 83 ta Register 84 to Capabilities Register 84 P option: Rules for PCI Express Capabilities Register 84 wice Capabilities Register 84 wice Capabilities Register 85 wice Cantrol Register 85 wice Capabilities Register 85 wice Control Register 85 wice Control Register 85 wice Control Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Capabilities Register 85 wice Control Register 95 wice Cont                                                                                                                                                                                                                                                                                                                                                    |    | G.3 Register bit field rules for the i-EP option                     | 83  |

| <ul> <li>G.3.2 Power Management Capabilities Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Stot Capabilities Register</li> <li>G.3.6 Stot Capabilities Register</li> <li>G.3.7 Stot Status Register</li> <li>G.3.8 i-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.12 Device Control 2 Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control 2 Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.21 Margining Lane Control Register</li> <li>G.3.21 Margining Lane Control Register</li> <li>G.3.21 Margining Lane Control Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16 o GT/S Status Register</li> <li>G.3.24 i-EP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 InGT/s Registers and Lane Error Status Register</li> <li>H.11 TIS groups</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.1.1 Background</li> <li>H.2.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.2 Rules</li> <li>H.3 System description of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> I GICV2m Architecture <ol> <li>Background</li> <li>About the GICV2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>GICV2 programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | wer Management Capabilities Register83wer Management Control/Status Register83at Register83at Capabilities Register84at Control Register84t Status Register84Vice Capabilities Register84vice Capabilities Register84vice Capabilities Register84vice Control Register84vice Control Register85vice Control Register86k Capabilities Register86k Capabilities Register88k Control Register89k Status Register89k Status Register90k Status Register90k Status Register91k Control Register92ne Equalization Control Register92ne Equalization Control Register93y oftin's Status Register93y oftin's Status Register93y oftin's Rules for 16.0 GT/s Lane Equalization Control Register94GT/s Registers and Lane Error Status Register95s ckground95les95s ckground96les97secription of DeviceID and ITS groups from firmware data98if or Multer90gift of Lewices90if of Lewices90if of Multer90if of Multer910granming101granming101granming101wertion an ITS groups95k form hot-plugg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | G.3.1 Type 1 header registers                                        | 83  |

| <ul> <li>G.3.3 Power Management Control/Status Register</li> <li>G.3.4 Data Register</li> <li>G.3.5 Stot Capabilities Register</li> <li>G.3.6 Stot Control Register</li> <li>G.3.7 Stot Status Register</li> <li>G.3.8 i-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.16 Link Status Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.24 i-EP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 InGT/s Registers and Lane Error Status Register</li> <li>G.3.26 Dig Cir/s Registers and Lane Error Status Register</li> <li>H.1 11 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Generation of DeviceID values</li> <li>H.2.4 Rules</li> <li>H.1.3 Examples of ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> I GICV2m Architecture <ol> <li>Background</li> <li>About the GICV2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>GICV2 programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | wer Management Control/Status Register83ta Register83ta Register84to Capabilities Register84to Carbilities Register84to Status Register84vice Capabilities Register84vice Capabilities Register84vice Capabilities Register84vice Capabilities 2 Register86ki Capabilities 2 Register86ki Capabilities 2 Register86ki Carbol 2 Register88ki Carbol 2 Register88ki Carbol 2 Register89ki Capabilities 2 Register89ki Capabilities 2 Register89ki Carbol 2 Register89ki Carbol 2 Register90ki Carbol 2 Register90ki Carbol 2 Register91ki Control 2 Register92re Equalization Control Register92regining Lane Control Register and Margining Lane Status Register93register Segister93P option: Rules for 16.0 GT/s Lane Equalization Control Register94ration and ITS groups95s chycound95les95amples of ITS groups95s chycound96les97specificit of DeviceID and ITS groups from firmware data98if for heigher and bar IIS groups from firmware data98if on not-plugged devices99tecture100ration nice100ration nice100ration of DeviceID and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                                                      | 83  |

| <ul> <li>G.3.4 Data Register</li> <li>G.3.5 Slot Capabilities Register</li> <li>G.3.6 Slot Control Register</li> <li>G.3.8 Slot Status Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Capabilities Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.20 Link Control 3 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.25 Data Link Feature Capabilities and Lane Equalization Control Register</li> <li>G.3.25 Link Strutus and Lane Error Status Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.25 Link Grupps</li> <li>H.1 TS groups</li> <li>H.1 TS groups</li> <li>H.1 TS groups</li> <li>H.1.1 Background</li> <li>H.2 Rules</li> <li>H.2 Generation of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> 1 GICV2m Architecture <ol> <li>Background</li> <li>About the GICv2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>GICv2 programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ta Register83at Capabilities Register84t Control Register84t Status Register84P option: Rules for PCI Express Capabilities Register84wice Capabilities Register84wice Capabilities Register85wice Capabilities Register85wice Control Register86k Capabilities Register86k Capabilities Register88k Control Register89k Capabilities 2 Register89k Capabilities 2 Register90k Status Register90k Status Register91k Control 2 Register92ne Equalization Control Register92ne Equalization Control Register92ne Equalization Control Register93argining Port Capabilities Register93argining Port Capabilities Register93o GT/S Status Register93o J S Status Register94varion and ITS groups95s ckground95les95scription of DeviceID and ITS groups from firmware data98of GlCv2m architecture90nd100GlCv2m architecture100no100no100terture100no100terture100no100no101gramming101gramming101terture101terture101terture <t< td=""><td></td><td>- · · ·</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | - · · ·                                                              |     |

| <ul> <li>G.3.5 Slot Capabilities Register</li> <li>G.3.6 Slot Control Register</li> <li>G.3.8 i-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.9 Device Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities 2 Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.18 Link Control 3 Register</li> <li>G.3.18 Link Control 3 Register</li> <li>G.3.20 Link Control 3 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.26 16GT/s Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H. 11 TS groups</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Generation of DeviceID values</li> <li>H.2.1 Background</li> <li>H.2.2 Rules</li> <li>H.3 Exsten description of DeviceID and ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> 1 GICV2m Architecture <ol> <li>About the GlCv2m architecture</li> <li>Sevently</li> </ol> 1 A Virtualization 1.6 GlCv2 programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | th Capabilities Register84th Control Register84Vice Capabilities Register84P option: Rules for PCI Express Capabilities Register84Vice Capabilities Register84vice Control Register85vice Control 2 Register85vice Control 2 Register88k Capabilities Register88k Capabilities Register88k Capabilities Register88k Capabilities 2 Register89k Capabilities 2 Register90k Status Register90k Status 2 Register91k Capabilities 2 Register92k Control 2 Register92k Control 2 Register92k Control 3 Register92k Control 3 Register92k Control 3 Register930 GT/s Status Register930 GT/s Status Register930 GT/s Status Register930 GT/s Status Register94GT/s Registers and Lane Equalization Control Register94Fration and ITS groups95s ckground96les95s chycincul 0 DeviceID and ITS groups from firmware data98for hot-pluged devices99tecture100ion100ion100ion100ion101gramming101gramming101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | · ·                                                                  |     |

| <ul> <li>G.3.6 Slot Control Register</li> <li>G.3.7 Slot Status Register</li> <li>G.3.8 i-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.10 Device Capabilities Register</li> <li>G.3.11 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.16 Link Capabilities Register</li> <li>G.3.17 Link Status 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.18 Link Control 2 Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.20 Link Control 3 Register</li> <li>G.3.21 Margining Lane Control Register and Margining Lane Status Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.24 i-EP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H DeviceID generation and ITS groups</li> <li>H.1 ITS groups</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.2 Generation of DeviceID values</li> <li>H.2 Rules</li> <li>H.3 Examples of ITS groups</li> <li>H.2 Background</li> <li>H.2 Rules</li> <li>H.3 Examples of ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> 1 GICV2m Architecture <ol> <li>Redigned devices</li> </ol> 1 GICV2m Architecture <ol> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>GICV2 programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | at Control Register84t Status Register84t Status Register84vice Capabilities Register84vice Capabilities Register85vice Capabilities 2 Register85vice Capabilities 2 Register88k Capabilities 2 Register89k Capabilities 2 Register90k Status Register91k Control Register92k Control Register92k Capabilities 2 Register91k Control Register92k Control 2 Register92k Control Register92k Control Register92k Control Register93ortic Capabilities Register93ortic S Status Register93s s s95s dyround95les95s dyround95les97secription of DeviceID and ITS groups from firmware data98ir form hot-plugged devices99tecture100nof100ion101gramming101gramming101gramming101gramming10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | -                                                                    |     |

| <ul> <li>G.3.7 Slot Status Register</li> <li>G.3.8 i-EP option: Rules for PCI Express Capabilities Register</li> <li>G.3.10 Device Control Register</li> <li>G.3.11 Device Capabilities Register</li> <li>G.3.12 Device Control Register</li> <li>G.3.13 Link Capabilities Register</li> <li>G.3.14 Link Control Register</li> <li>G.3.15 Link Status Register</li> <li>G.3.16 Link Capabilities 2 Register</li> <li>G.3.16 Link Control 2 Register</li> <li>G.3.16 Link Control 2 Register</li> <li>G.3.19 Lane Equalization Control Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.20 Link Control 2 Register</li> <li>G.3.21 Margining Lane Control Register</li> <li>G.3.22 Margining Port Capabilities Register</li> <li>G.3.23 16.0 GT/s Status Register</li> <li>G.3.24 1-EP option: Rules for 16.0 GT/s Lane Equalization Control Register</li> <li>G.3.25 Data Link Feature Capabilities and Data Link Feature Status</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>G.3.26 16GT/s Registers and Lane Error Status Register</li> <li>H.1 TS groups</li> <li>H.1.1 Background</li> <li>H.1.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Rules</li> <li>H.1.3 Examples of ITS groups</li> <li>H.2 Rules</li> <li>H.2.1 Background</li> <li>H.2.2 Rules</li> <li>H.2 Background</li> <li>H.2.2 Rules</li> <li>H.3 Examples of ITS groups from firmware data</li> <li>H.4 DeviceIDs from hot-plugged devices</li> </ul> I GICV2m Architecture <ol> <li>About the GICv2m architecture</li> <li>Security</li> <li>Virtualization</li> <li>SPI allocation</li> <li>GICV2 programming</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | at Status Register       84         P option: Rules for PCI Express Capabilities Register       84         wice Capabilities Register       85         wice Capabilities Register       85         wice Control 2 Register       86         k Capabilities Register       88         k Control Register       88         k Control Register       89         k Control Register       90         k Status Register       90         k Capabilities 2 Register       90         k Control 2 Register       92         k Control 3 Register       92         argining Lane Control Register and Margining Lane Status Register       93         voltar Equalization Control Register       93         P option: Rules for 16.0 GT/s Lane Equalization Control Register       94         Partion and ITS groups       95         s (kground       95         les       95         amples of ITS groups       96         n of DeviceID and ITS groups from firmware data       98         s from hot-plugged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                                                      | 84  |