# Realm Management Monitor specification

| Document number            | DEN0137                 |

|----------------------------|-------------------------|

| Document quality           | EAC                     |

| Document version           | 1.0-eac3                |

| Document confidentiality   | Non-confidential        |

| Document build information | 1b76d699 doctool 0.53.0 |

Copyright © 2022-2023 Arm Limited or its affiliates. All rights reserved.

## **Realm Management Monitor specification**

#### **Release information**

#### 1.0-eac3 (20-07-2023)

#### Clarifications

- Clarify which bits of command input / output values should / must be zero (FENIMORE-674)

- Explain distinction between concrete and abstract types (FENIMORE-693)

- Clarify return value from RSI\_IPA\_STATE\_SET when stopping at first DESTROYED entry (FENIMORE-699) [I<sub>GXDDX</sub>]

#### Defects

- PSCI\_SYSTEM\_{OFF,RESET}: change Realm state to SYSTEM\_OFF (FENIMORE-694)

- RMI\_REC\_CREATE: update RIM only if runnable flag is set (FENIMORE-697)

- RMI\_REALM\_CREATE: fix list of measured parameters (FENIMORE-695)

- Remove members from RmmSystemRegisters (FENIMORE-700)

- State saved / restored depends on architecture features supported by the platform, so defining this type as an empty placeholder

- Avoid use of reserved ASL v1 keyword "entry" in MRS (FENIMORE-702)

- RmiRecEntry -> RmiRecEnter

- RmiRecEntryFlags -> RmiRecEnterFlags

- RmiRecRun::entry -> RmiRecRun::enter

- RmmRttWalkResult::entry -> RmmRttWalkResult::rtte

- RSI\_IPA\_STATE\_SET: prohibit RSI\_DESTROYED input value (FENIMORE-705)

- RMI\_PSCI\_COMPLETE: PSCI\_CPU\_ON: fix copy of context\_id to target CPU X0 (FENIMORE-703)

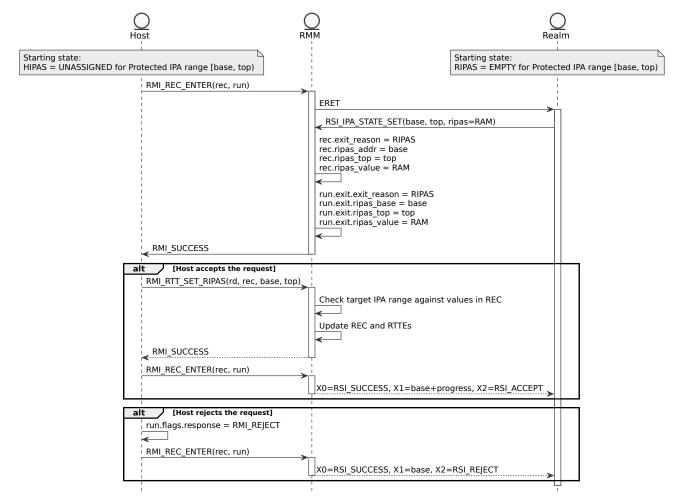

- Allow Host to reject request to change RIPAS to RAM (FENIMORE-661)

- Allow Host to reject PSCI\_CPU\_ON request via RMI\_PSCI\_COMPLETE (FENIMORE-706)

#### Relaxations

- Permit folding of level 2 RTT to create level 1 block mapping (FENIMORE-608)

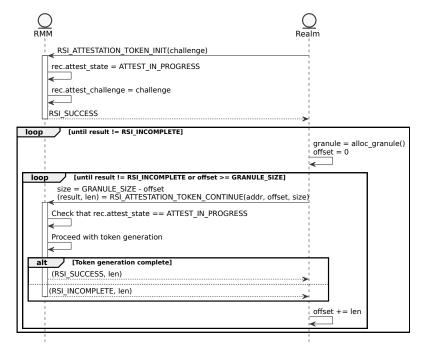

- Remove restriction that attestation token size must not exceed 4KB (FENIMORE-691)

#### 1.0-eac2 (07-06-2023)

#### Clarifications

- Remove reference to triggering ERROR\_INPUT by setting MBZ bit to 1 (FENIMORE-675)

- Clarify constraints on output values in case of command failure [R<sub>TFZMS</sub>] (FENIMORE-676)

- Clarify encoding of RmiRealmParams::sve\_sz (FENIMORE-684)

- Clarify set of SMCCC interfaces available to a Realm [R<sub>NPLKX</sub>] (FENIMORE-685)

#### Defects

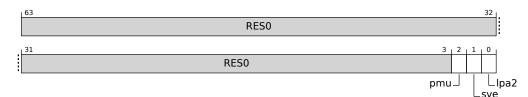

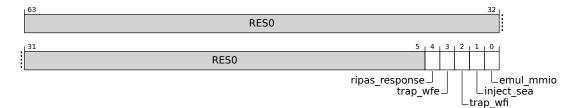

- Replace PMU fields in RmiRecExit with single bit indicating the PMU overflow status [R<sub>WXTZF</sub>] (FENIMORE-679)

- RMI\_PSCI\_COMPLETE: failure condition should compare against MPIDR, not RD address (FENIMORE-681)

- RMI\_REC\_CREATE: remove params\_valid failure condition (FENIMORE-686)

- RMI\_RTT\_{INIT,SET}\_RIPAS: check alignment of "top" input value (FENIMORE-687)

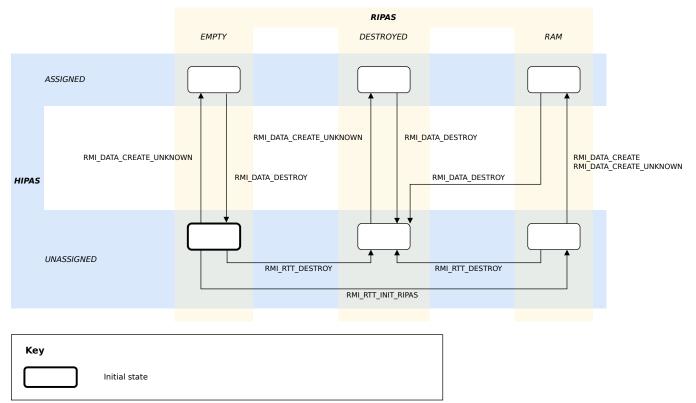

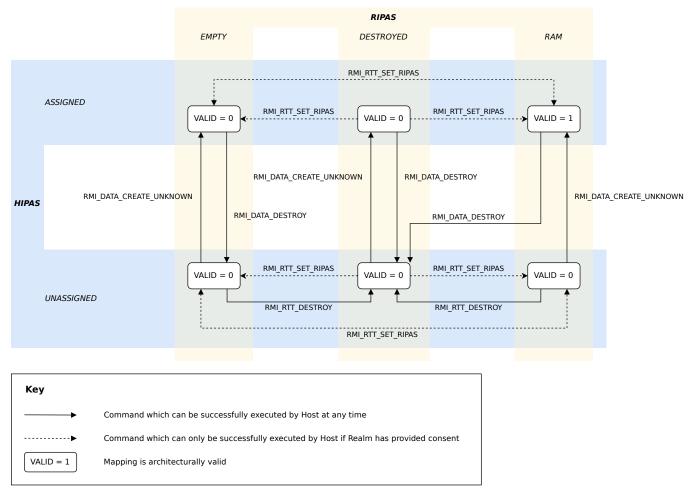

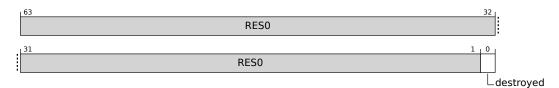

- Reduce coupling between HIPAS and RIPAS (FENIMORE-680)

- Replace HIPAS=DESTROYED with RIPAS=DESTROYED

- Remove RmiRttEntryState::RMI\_DESTROYED

- Change encoding of RmiRttEntryState::RMI\_TABLE

- Add RmiRipas::RMI\_DESTROYED

- Add RsiRipas::RSI\_DESTROYED

- RMI\_DATA\_CREATE\_UNKNOWN: remove pre-condition that RIPAS=RAM

- RMI\_DATA\_DESTROY:

- \* In all cases, post-condition now states that HIPAS=UNASSIGNED

- \* If pre-condition was RIPAS=RAM, post-condition states that RIPAS=DESTROYED

- RMI\_RTT\_DESTROY:

- \* Remove post-condition that HIPAS=DESTROYED

- \* Add post-condition that state of parent RTTE is UNASSIGNED

- \* Add post-condition that RIPAS=DESTROYED

- RMI\_RTT\_SET\_IPA\_STATE: stop at first DESTROYED entry if "destroyed" flag is set

- RSI\_IPA\_STATE\_SET: add "destroyed" flag

- Clarify distinction between "RTT folding" [D<sub>QPXCP</sub>] and "RTT destruction" [D<sub>VXRZW</sub>]

- RMI\_RTT\_INIT\_RIPAS: success conditions should be bounded by walk\_top, not top

#### Relaxations

• RSI\_REALM\_CONFIG: provide Realm hash algorithm (FENIMORE-678)

#### 1.0-eac1 (31-03-2023)

#### Clarifications

- Unused bits of RmiRecEntry::gicv3\_hcr are SBZ [I<sub>SMHXB</sub>] (FENIMORE-666)

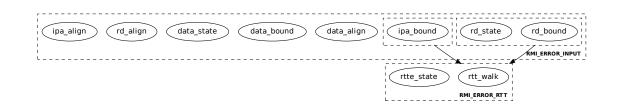

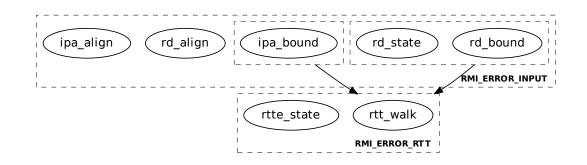

- RMI\_REC\_ENTER: all RMI\_ERROR\_INPUT failure conditions precede all RMI\_ERROR\_REC failure conditions (FENIMORE-668)

- Avoid use of raw Xn values in command conditions where possible (FENIMORE-671)

- Clarify definition of REC exit due to (Non-)emulatable Data Abort [D<sub>CYRMT</sub>, D<sub>MTZMC</sub>] (FENIMORE-673)

#### Defects

- RMI\_RTT\_INIT\_RIPAS: take account of "top" IPA value when calculating RIM contribution (FENIMORE-662)

- RttSkipEntriesWithRipas: fix inverted logic (FENIMORE-663)

- RMI\_RTT\_SET\_RIPAS: on success, modify IPA range [base, walk\_top) (FENIMORE-669)

- RMI\_RTT\_{INIT,SET}\_RIPAS: remove redundant failure conditions (FENIMORE-670)

- Clarify HIPAS=DESTROYED implies RIPAS=UNDEFINED [R<sub>JYDRL</sub>] (FENIMORE-672)

#### Relaxations

• RSI\_HOST\_CALL: relax alignment requirement from 4KB to 256B

#### 1.0-eac0 (31-01-2023)

#### Clarifications

None

#### Defects

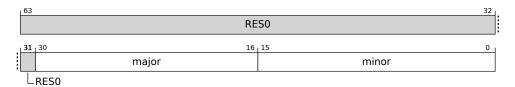

- RmiRealmParams: reduce width of integer attributes (FENIMORE-647)

- RSI\_IPA\_STATE\_SET: replace (base, size) with (base, top) (FENIMORE-656)

- RMI\_RTT\_INIT\_RIPAS, RMI\_RTT\_SET\_RIPAS: allow single command to modify multiple RTT entries (FENIMORE-656)

#### Relaxations

• RMI\_RTT\_SET\_RIPAS: remove "ripas" input value (FENIMORE-659)

## 1.0-bet2 (16-12-2022)

#### Clarifications

- Flows: update RMI\_REC\_ENTRY to take a single 'run' input value

- Clarify meaning of "TTD" [I<sub>YMNSR</sub>] (FENIMORE-641)

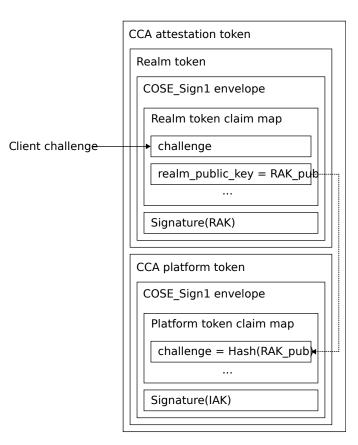

- Fix typo in reference to "CCA platform token claim map"  $[I_{FJKFY}]$  (FENIMORE-647)

- Fix reference to "RME system architecture spec" (FENIMORE-648)

- Flows: remove stale reference to parameters passed to RMI\_DATA\_CREATE (FENIMORE-649)

- Improve definition and constistency of usage of the term "REC" (FENIMORE-650)

- Where referring to the RMM data structure "REC object" is now used

- Clarify description of properties of Realm IPA space [I<sub>TPGKW</sub>] (FENIMORE-639)

- Replace "permitted, under control of host" with statements which refer to particular HIPAS values.

- Add "Protected IPA, HIPAS=DESTROYED" row, thereby removing contradictory statements regarding SEA taken to Realm, previously in "Protected IPA, RIPAS=EMPTY".

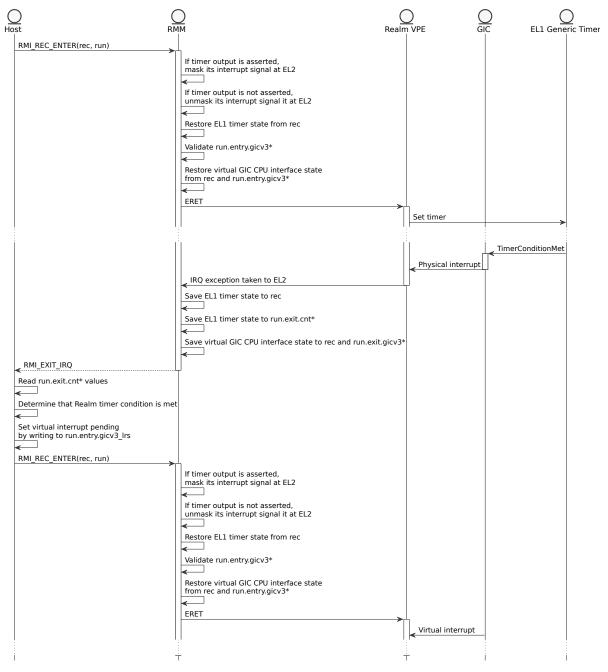

- On assertion of an EL1 timer, the RMM guarantees a REC exit, not only a Realm exit (FENIMORE-651)

- RMI\_RTT\_FOLD: preserve RIPAS value if IPA is Protected (FENIMORE-638)

#### Defects

- Attestation: wrap sub-tokens in byte stream (FENIMORE-643)

- RMI\_DATA\_DESTROY, RMI\_RTT\_{DESTROY,FOLD}: return PA of destroyed object (FENIMORE-563)

- RMI\_REALM\_DESTROY, RMI\_REC\_DESTROY, RMI\_REC\_ENTER, RMI\_RTT\_DESTROY, RMI\_RTT\_FOLD, RMI\_RTT\_SET\_RIPAS: Remove RMI\_ERROR\_IN\_USE (FENIMORE-588)

- RMI\_DATA\_CREATE, RMI\_DATA\_CREATE\_UNKNOWN, RMI\_REC\_CREATE, RMI\_RTT\_CREATE: pass RD pointer in X1 (FENIMORE-655)

- Replace RmiRealmParams::features\_0 with discrete fields (FENIMORE-655)

- RMI\_DATA\_CREATE(\_UNKNOWN): require RIPAS=RAM (FENIMORE-645)

- Apply "must / should be zero" consistently (FENIMORE-619)

- In command inputs, unused bits are SBZ

- In command outputs, unused bits are MBZ

#### Relaxations

- RSI\_HOST\_CALL: expand set of GPRs to X0-X30 (FENIMORE-607)

- This enables the RMM to support any calling convention.

- RMI\_DATA\_DESTROY, RMI\_RTT\_DESTROY, RMI\_RTT\_UNMAP\_UNPROTECTED: return IPA of next live RTT entry (FENIMORE-563)

#### 1.0-bet1 (31-10-2022)

#### Clarifications

- Rename HIPAS VALID\_NS -> UNASSIGNED (FENIMORE-631)

- SEA injection is independent of whether Host emulates MMIO (FENIMORE-632)

- In RIPAS change flow, permit Host to apply the change to zero or more pages of the target IPA region (FENIMORE-633)

- Flows: replace HVC with Host call (FENIMORE-611)

- Clarify behavior of VmidIsValid() function (FENIMORE-630)

- Qualify "all other exit fields are zero" statements [R<sub>GTJRP</sub>, R<sub>LRCFP</sub>] (FENIMORE-634)

GIC, timer and PMU fields are valid on every REC exit.

#### Defects

- Change size of RsiHostCall type to 256 bytes (FENIMORE-629)

- Correct the set of ESR\_EL2 fields which are returned to the Host on REC exit due to Data abort [R<sub>RYVFL</sub>]

- On all Data Aborts, add FnV.

- On Emulatable Data Aborts, add SF.

- On Non-emulatable Data Abort at an Unprotected IPA, add IL.

#### Relaxations

None

## Arm Non-Confidential Document Licence ("Licence")

This Licence is a legal agreement between you and Arm Limited ("**Arm**") for the use of Arm's intellectual property (including, without limitation, any copyright) embodied in the document accompanying this Licence ("**Document**"). Arm licenses its intellectual property in the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence.

"**Subsidiary**" means any company the majority of whose voting shares is now or hereafter owner or controlled, directly or indirectly, by you. A company shall be a Subsidiary only for the period during which such control exists.

This Document is **NON-CONFIDENTIAL** and any use by you and your Subsidiaries ("Licensee") is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to Licensee under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

# Licensee hereby agrees that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, Licensee acquires no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by Licensee or by Arm. Without prejudice to any of its other rights, if Licensee is in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to Licensee. Licensee may terminate this Licence at any time. Upon termination of this Licence by Licensee or by Arm, Licensee shall stop using the Document and destroy all copies of the Document in its possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

Any breach of this Licence by a Subsidiary shall entitle Arm to terminate this Licence as if you were the party in breach. Any termination of this Licence shall be effective in respect of all Subsidiaries. Any rights granted to any Subsidiary hereunder shall automatically terminate upon such Subsidiary ceasing to be a Subsidiary.

The Document consists solely of commercial items. Licensee shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

This Licence may be translated into other languages for convenience, and Licensee agrees that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with ® or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may

be the trademarks of their respective owners. No licence, express, implied or otherwise, is granted to Licensee under this Licence, to use the Arm trade marks in connection with the Document or any products based thereon. Visit Arm's website at http://www.arm.com/company/policies/trademarks for more information about Arm's trademarks.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © 2022-2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-21585 version 4.0

# Contents Realm Management Monitor specification

|         | Realm Management Monitor specification       ii         Release information       iii         Arm Non Confidential Decument Linease ("Linease")       iii |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Arm Non-Confidential Document Licence ("Licence")                                                                                                         |

| Preface |                                                                                                                                                           |

|         | Conventions                                                                                                                                               |

|         | Typographical conventions                                                                                                                                 |

|         | Numbers                                                                                                                                                   |

|         | Pseudocode descriptions                                                                                                                                   |

|         | Addresses                                                                                                                                                 |

|         | Rules-based writing                                                                                                                                       |

|         | Content item identifiers                                                                                                                                  |

|         | Content item rendering                                                                                                                                    |

|         | Content item classes                                                                                                                                      |

|         | Additional reading                                                                                                                                        |

|         | Feedback                                                                                                                                                  |

|         | Feedback on this book                                                                                                                                     |

|         | Open issues                                                                                                                                               |

## Part A Architecture

| Chapter A1 | Overview  |                                     |    |

|------------|-----------|-------------------------------------|----|

| •          | A1.1 Co   | nfidential computing                | 24 |

|            | A1.2 Sv   | stem software components            | 25 |

|            | •         | alm Management Monitor              |    |

| Chapter A2 | Concepts  |                                     |    |

| •          | -         | alm                                 | 28 |

|            | A2.1.1    | l Overview                          | 28 |

|            | A2.1.2    | 2 Realm execution environment       | 28 |

|            | A2.1.3    | B Realm attributes                  | 29 |

|            | A2.1.4    | 4 Realm liveness                    | 30 |

|            | A2.1.5    |                                     | 31 |

|            | A2.1.6    | ,                                   | 32 |

|            | A2.1.7    | •                                   | 32 |

|            | A2.2 Gr   |                                     | 33 |

|            | A2.2.1    | Granule attributes                  | 33 |

|            | A2.2.2    |                                     | 34 |

|            | A2.2.3    | •                                   | 34 |

|            | A2.2.4    | ,                                   | 36 |

|            |           | ealm Execution Context              | 38 |

|            | A2.3.1    |                                     | 38 |

|            | A2.3.2    |                                     | 38 |

|            | A2.3.3    |                                     | 39 |

|            | A2.3.4    |                                     | 40 |

|            | / L.O.    |                                     | 10 |

| Chapter A3 | Realm cre | ation                               |    |

| •          | A3.1 Re   | alm feature discovery and selection | 43 |

|            |           | ,                                   | -  |

|            |           |                                     |    |

|            |                              | A3.1.1                                                                                                                                                                                                                                | Realm hash algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43                                                                                                                         |

|------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|            |                              | A3.1.2                                                                                                                                                                                                                                | Realm LPA2 and IPA width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                                                                                         |

|            |                              | A3.1.3                                                                                                                                                                                                                                | Realm support for Scalable Vector Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44                                                                                                                         |

|            |                              | A3.1.4                                                                                                                                                                                                                                | Realm support for self-hosted debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                                                                         |

|            |                              | A3.1.5                                                                                                                                                                                                                                | Realm support for Performance Monitors Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                                         |

|            |                              | A3.1.6                                                                                                                                                                                                                                | Realm support for Activity Monitors Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                                                                                                                         |

|            |                              | A3.1.7                                                                                                                                                                                                                                | Realm support for Statistical Profiling Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                                         |

|            |                              | A3.1.8                                                                                                                                                                                                                                | Realm support for Trace Buffer Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                         |

| Oberter Ad | Deel                         |                                                                                                                                                                                                                                       | ation model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| Chapter A4 |                              |                                                                                                                                                                                                                                       | ption model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                                                                         |

|            | A4.1                         |                                                                                                                                                                                                                                       | ption model overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                                                                                                         |

|            | A4.2                         |                                                                                                                                                                                                                                       | entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                                         |

|            |                              | A4.2.1                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                                                                         |

|            |                              | A4.2.2                                                                                                                                                                                                                                | General purpose registers restored on REC entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                                                                         |

|            |                              | A4.2.3                                                                                                                                                                                                                                | REC entry following REC exit due to Data Abort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                                         |

|            | A4.3                         |                                                                                                                                                                                                                                       | exit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                                                         |

|            |                              | A4.3.1                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52                                                                                                                         |

|            |                              | A4.3.2                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                                         |

|            |                              | A4.3.3                                                                                                                                                                                                                                | General purpose registers saved on REC exit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                                                                                         |

|            |                              | A4.3.4                                                                                                                                                                                                                                | REC exit due to synchronous exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                                                                                         |

|            |                              | A4.3.5                                                                                                                                                                                                                                | REC exit due to IRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                                                                                         |

|            |                              | A4.3.6                                                                                                                                                                                                                                | REC exit due to FIQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                                                                         |

|            |                              | A4.3.7                                                                                                                                                                                                                                | REC exit due to PSCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58                                                                                                                         |

|            |                              | A4.3.8                                                                                                                                                                                                                                | REC exit due to RIPAS change pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59                                                                                                                         |

|            |                              | A4.3.9                                                                                                                                                                                                                                | REC exit due to Host call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                                                                         |

|            |                              | A4.3.10                                                                                                                                                                                                                               | REC exit due to SError                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                                                                         |

|            | A4.4                         |                                                                                                                                                                                                                                       | ated Data Aborts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                         |

|            | A4.5                         | Host                                                                                                                                                                                                                                  | call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                                                                         |

|            |                              |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| Chapter A5 | Real                         | m mem                                                                                                                                                                                                                                 | ory management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| Chapter A5 | <b>Real</b><br>A5.1          |                                                                                                                                                                                                                                       | ory management n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                                                                         |

| Chapter A5 |                              | Realı                                                                                                                                                                                                                                 | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63                                                                                                                   |

| Chapter A5 | A5.1                         | Realı                                                                                                                                                                                                                                 | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

| Chapter A5 | A5.1                         | Realı<br>Realı                                                                                                                                                                                                                        | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                                                         |

| Chapter A5 | A5.1                         | Realı<br>Realı<br>A5.2.1                                                                                                                                                                                                              | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63                                                                                                                   |

| Chapter A5 | A5.1                         | Realı<br>Realı<br>A5.2.1<br>A5.2.2                                                                                                                                                                                                    | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>63<br>64                                                                                                       |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4                                                                                                                                                                                | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>63<br>64<br>64                                                                                                 |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5                                                                                                                                                                      | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>63<br>64<br>64<br>64                                                                                           |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6                                                                                                                                                  | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>64                                                                                           |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7                                                                                                                                                  | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66                                                                                     |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6                                                                                                                                                  | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66                                                                               |

| Chapter A5 | A5.1<br>A5.2                 | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9                                                                                                                              | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>67                                                                         |

| Chapter A5 | A5.1                         | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9<br>Host                                                                                                                      | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>67<br>68                                                                   |

| Chapter A5 | A5.1<br>A5.2                 | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9<br>Host<br>A5.3.1                                                                                                            | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>67<br>68<br>68                                                             |

| Chapter A5 | A5.1<br>A5.2                 | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9<br>Host<br>A5.3.1<br>A5.3.2                                                                                                  | n memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>66<br>67<br>68<br>68<br>69                                                 |

| Chapter A5 | A5.1<br>A5.2                 | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9<br>Host<br>A5.3.1<br>A5.3.2<br>A5.3.3                                                                                        | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>66<br>67<br>68<br>68<br>69<br>70                                           |

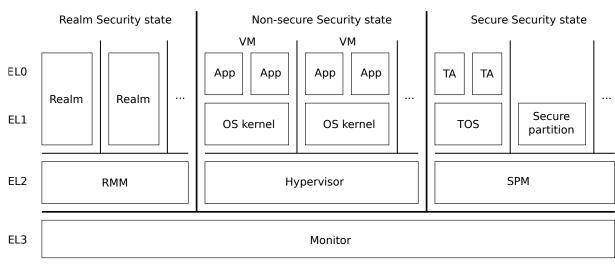

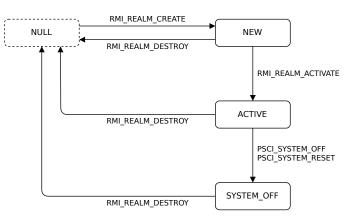

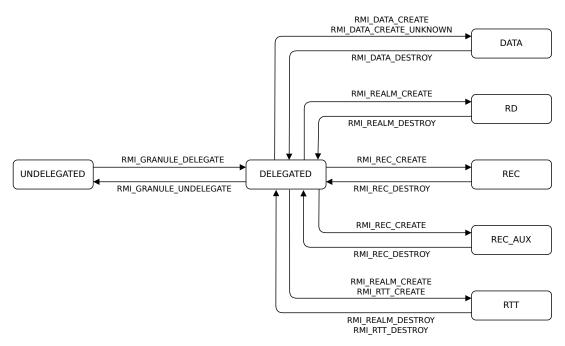

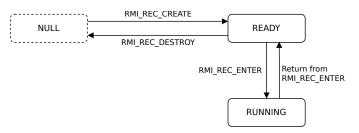

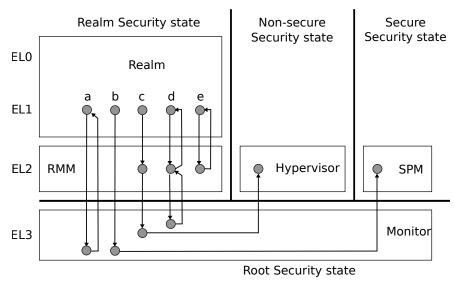

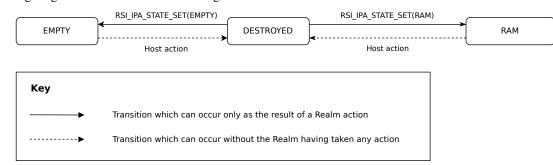

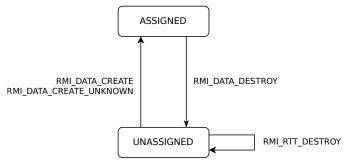

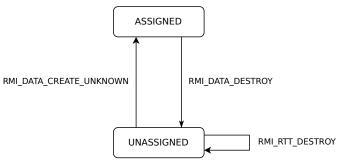

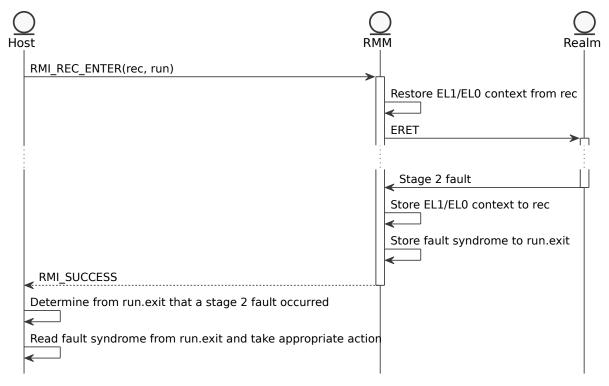

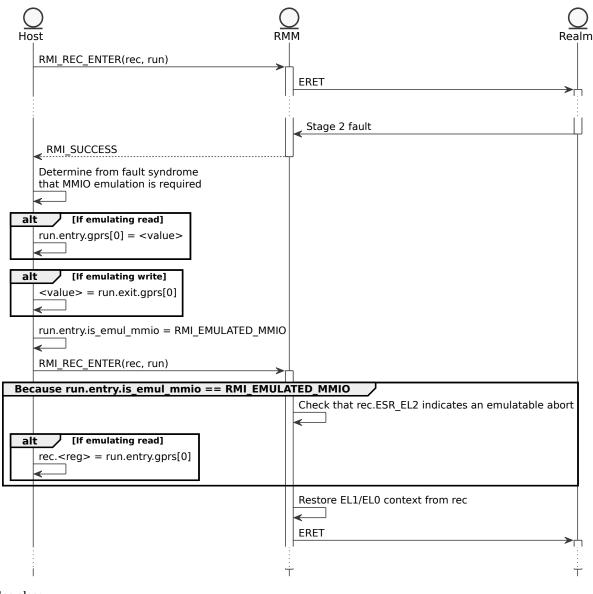

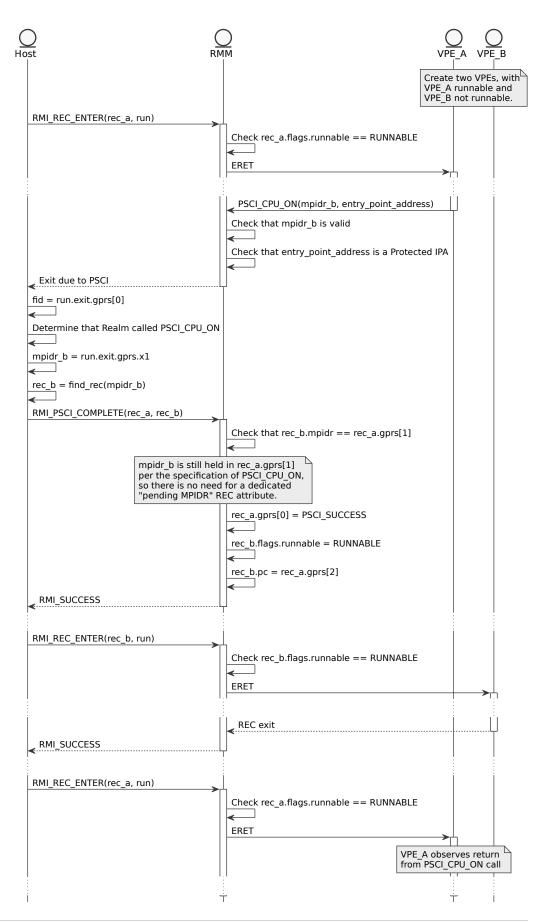

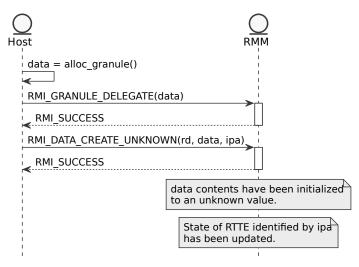

| Chapter A5 | A5.1<br>A5.2                 | Reali<br>Reali<br>A5.2.1<br>A5.2.2<br>A5.2.3<br>A5.2.4<br>A5.2.5<br>A5.2.6<br>A5.2.7<br>A5.2.8<br>A5.2.9<br>Host<br>A5.3.1<br>A5.3.2<br>A5.3.3<br>A5.3.4                                                                              | m memory management overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63<br>63<br>64<br>64<br>64<br>66<br>66<br>66<br>67<br>68<br>68<br>68<br>69<br>70<br>71                                     |