## ARM<sup>®</sup> Generic Interrupt Controller Architecture version 1.0

# Architecture Specification

Copyright © 2008 ARM Limited. All rights reserved. ARM IHI 0048A

## **ARM Generic Interrupt Controller**

Copyright © 2008 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

| Change | History |

|--------|---------|

| onunge | matory  |

| Date              | Issue | Confidentiality                      | Change                        |

|-------------------|-------|--------------------------------------|-------------------------------|

| 23 September 2008 | А     | Non-Confidential Unrestricted Access | First release for version 1.0 |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\bowtie}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

- Subject to the provisions of Clauses 2 and 3, ARM hereby grants to you a perpetual, non-exclusive, non-transferable, royalty free, worldwide licence to use and copy the ARM Generic Interrupt Controller (GIC) Architecture Specification ("Specification") for the purpose of developing, having developed, manufacturing, having manufactured, offering to sell, selling, supplying or otherwise distributing products which comply with the Specification and which contain at least one processor core which has either been (i) developed by or for ARM or (ii) developed under licence from ARM.

- 2. THE ARM GIC ARCHITECTURE SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE.

- 3. No licence, express, implied or otherwise, is granted to you, under the provisions of Clause 1, to use the ARM tradename in connection with the ARM GIC Architecture Specification or any products based thereon. Nothing in Clause 1 shall be construed as authority for you to make any representations on behalf of ARM in respect of the ARM GIC Architecture Specification.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

Copyright © 2008 ARM Limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

This document is Non-Confidential. The right to use, copy and disclose this document is subject to the licence set out above.

Unrestricted Access is an ARM internal classification.

## Contents ARM Generic Interrupt Controller Architecture Specification

|           |         | About this specification                            |      |

|-----------|---------|-----------------------------------------------------|------|

|           |         | Further reading                                     | ix   |

| Chapter 1 | Introd  | uction                                              |      |

|           | 1.1     | About the Generic Interrupt Controller architecture | 1-2  |

|           | 1.2     | Security Extensions support                         | 1-3  |

|           | 1.3     | Terminology                                         |      |

| Chapter 2 | GIC Pa  | artitioning                                         |      |

| •         | 2.1     | About GIC partitioning                              | 2-2  |

|           | 2.2     | The Distributor                                     |      |

|           | 2.3     | CPU interfaces                                      | 2-6  |

| Chapter 3 | Interru | upt Handling and Prioritization                     |      |

| -         | 3.1     | About interrupt handling and prioritization         | 3-2  |

|           | 3.2     | General handling of interrupts                      |      |

|           | 3.3     | Interrupt prioritization                            | 3-12 |

|            | 3.4<br>3.5<br>3.6 | The effect of the Security Extensions on interrupt handling3-15The effect of the Security Extensions on interrupt prioritization3-18Pseudocode details of interrupt handling and prioritization3-25 |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4  | Prog              | rammers Model                                                                                                                                                                                       |

| •          | 4.1               | About the programmers model 4-2                                                                                                                                                                     |

|            | 4.2               | Effect of the Security Extensions on the programmers model 4-7                                                                                                                                      |

|            | 4.3               | Distributor register descriptions 4-11                                                                                                                                                              |

|            | 4.4               | CPU interface register descriptions 4-46                                                                                                                                                            |

| Appendix A | Pseu              | docode Index                                                                                                                                                                                        |

|            | A.1               | Index of pseudocode functions A-2                                                                                                                                                                   |

| Appendix B | Softw             | vare Examples for the GIC                                                                                                                                                                           |

|            | B.1               | Use of identification registers B-2                                                                                                                                                                 |

|            | B.2               | Initialization after reset or power on B-3                                                                                                                                                          |

|            | B.3               | Processor response to an initial interrupt B-6                                                                                                                                                      |

|            | B.4               | Preemptive processing B-9                                                                                                                                                                           |

|            | B.5               | Generating a software interrupt B-12                                                                                                                                                                |

|            | B.6               | Changing a CPU interface interrupt priority mask B-13                                                                                                                                               |

|            | B.7               | Changing the priority of an interrupt B-14                                                                                                                                                          |

|            | B.8               | Changing the processor targets of an interrupt B-15                                                                                                                                                 |

|            | B.9               | Disabling a peripheral interrupt B-16                                                                                                                                                               |

|            | B.10              | Changing the security configuration of an interrupt B-17                                                                                                                                            |

|            | B.11              | Disabling a CPU interface on the GIC B-19                                                                                                                                                           |

|            | B.12              | Message passing between processors B-20                                                                                                                                                             |

|            | B.13              | Example of using the binary point B-21                                                                                                                                                              |

| Appendix C | •                 | ster Shortform Names                                                                                                                                                                                |

|            | C.1               | Register name aliases C-2                                                                                                                                                                           |

|            | C.2               | Index of architectural shortform names C-4                                                                                                                                                          |

|            |                   |                                                                                                                                                                                                     |

### Glossary

## Preface

This preface summarizes the contents of this specification and lists the conventions it uses. It contains the following sections:

- About this specification on page vi

- Conventions on page viii

- *Further reading* on page ix

- *Feedback* on page x.

### About this specification

This is version 1.0 of the Architecture Specification for the ARM Generic Interrupt Controller (GIC).

Throughout this document, references to *the GIC* or *a GIC* refer to a device that implements this GIC architecture. Unless the context makes it clear that a reference is to an IMPLEMENTATION DEFINED feature of the device, these references describe the requirements of this specification.

#### Intended audience

The specification is written for users that want to design, implement, or program the GIC in a range of ARM-compliant implementations from simple uniprocessor implementations to complex multiprocessor systems.

The specification assumes that users have some experience of ARM products. It does not assume experience of the GIC.

#### Using this specification

This specification is organized into the following chapters:

#### **Chapter 1** Introduction

Read this for an overview of the GIC, and information about the terminology used in this document.

#### Chapter 2 GIC Partitioning

Read this for a description of the major interfaces and components of the GIC. The chapter also describes how they operate.

#### Chapter 3 Interrupt Handling and Prioritization

Read this for a description of the requirements for interrupt handling, and the interrupt priority scheme for a GIC.

#### **Chapter 4** Programmers Model

Read this for a description of the Distributor and CPU interface registers.

#### Appendix A Pseudocode Index

Read this for an index to the pseudocode functions defined in this specification.

#### Appendix B Software Examples for the GIC

Read this for a description of non-architectural, non-prescriptive, methods of using the GIC, and of how the GIC manages interrupts.

#### Appendix C Register Shortform Names

Read this for a description of relationship between the architectural shortform names of the registers described in this specification and their legacy shortform aliases, and for an alphabetic index of the architectural shortform names.

*Glossary* Read the Glossary for definitions of terms used in this document.

### Conventions

The following sections describe conventions that this book can use:

- General typographic conventions

- Signals

- Numbers

- Pseudocode descriptions.

#### General typographic conventions

| monospace      | Used for assembler syntax descriptions, pseudocode, and source code examples.                                                                                                  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                | Also used in the main text for instruction mnemonics and for references to other<br>items appearing in assembler syntax descriptions, pseudocode, and source code<br>examples. |  |  |

| italic         | Highlights important notes, introduces special terminology, and denotes internal cross-references and citations.                                                               |  |  |

| bold           | Denotes signal names and is used for terms in descriptive lists, where appropriate.                                                                                            |  |  |

| SMALL CAPITALS | Used for a few terms that have specific technical meanings, that are included in the Glossary.                                                                                 |  |  |

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | • HIGH for active-HIGH signals                                                                              |

|              | • LOW for active-LOW signals.                                                                               |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

#### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x and written in a monospace font.

#### **Pseudocode descriptions**

This specification uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monspace font, and follows the conventions described in the *ARM Architecture Reference Manual*, *ARMv7-A and ARMv7-R edition*.

## **Further reading**

This section lists publications by ARM and by third parties.

See http://infocenter.arm.com/ for access to ARM documentation.

### **ARM** publications

This specification contains information that is specific to the GIC. See the following documents for other relevant information:

• ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406).

### **External publications**

This section lists relevant documents published by third parties:

• JEP106M, Standard Manufacture's Identification Code, JEDEC Solid State Technology Association.

## Feedback

ARM welcomes feedback on this documentation.

#### Feedback on this specification

If you have any comments or suggestions about this documentation, contact your supplier and give:

- the document title

- the document number

- an explanation with as much information as you can provide.

ARM also welcomes general suggestions for additions and improvements.

## Chapter 1 Introduction

This chapter gives an overview of the GIC and information about the terminology used in this document. It contains the following sections:

- About the Generic Interrupt Controller architecture on page 1-2

- Security Extensions support on page 1-3

- *Terminology* on page 1-4.

## **1.1** About the Generic Interrupt Controller architecture

The Generic Interrupt Controller (GIC) architecture defines:

- the architectural requirements for handling all interrupt sources for any processor associated with a GIC

- a common interrupt controller programming interface applicable to uniprocessor or multiprocessor systems.

#### —Note —

The architecture describes a GIC designed for use with one or more processors that comply with the ARM A and R architecture profiles. However the GIC architecture does not place any restrictions on the processors used with an implementation of the GIC.

The GIC is a centralized resource for supporting and managing interrupts in a system that includes at least one processor. It provides:

- registers for managing interrupt sources, interrupt behavior, and interrupt routing to one or more processors

- support for:

- the ARM architecture Security Extensions

- enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt sources

- generating software interrupts

- interrupt masking and prioritization

- uniprocessor and multiprocessor environments.

The GIC takes interrupts asserted at the system level and signals them to each connected processor as appropriate. If the GIC implements the Security Extensions it can implement two interrupt requests to a connected processor. The architecture identifies these two requests as IRQ and FIQ.

#### — Note ——

In many implementations the IRQ and FIQ interrupt requests correspond to the IRQ and FIQ asynchronous exceptions that are supported by all variants of the ARM architecture except the *Microcontroller profile* (M-profile). For more information about IRQ, FIQ, and asynchronous exceptions, see the *ARM Architecture Reference Manual*, *ARMv7-A and ARMv7-R edition*.

#### 1.1.1 GIC architecture specification version

This specification describes version 1.0 of the GIC architecture. Some products have been implemented using preliminary versions of this specification and might not fully comply with this specification.

The GIC architecture specification version is independent of the *rxpx* version, or major and minor revision description, used for product releases.

## 1.2 Security Extensions support

The ARM GIC architecture Security Extensions support:

- configuring each interrupt as either Secure or Non-secure

- signalling Secure interrupts to the target processor using either the IRQ or the FIQ exception request

- a unified scheme for handling the priority of Secure and Non-secure interrupts

- optional lockdown of the configuration of some Secure interrupts.

In an implementation that includes the Security Extensions:

- System software individually defines each implemented interrupt as either Secure or Non-secure.

- The behavior of processor accesses to registers in the GIC depends on whether the access is Secure or Non-secure, see *Processor security state and Secure and Non-secure GIC accesses* on page 1-5.

Except where this document explicitly indicates otherwise, when accessing GIC registers:

- a Non-secure read of a register field holding state information for a Secure interrupt returns zero

- the GIC ignores any Non-secure write to a register field holding state information for a Secure interrupt.

Non-secure accesses can only read or set information corresponding to Non-secure interrupts. Secure accesses can read or set information corresponding to both Non-secure and Secure interrupts.

- A Non-secure interrupt signals an IRQ interrupt request to a target processor.

- A Secure interrupt can signal either an IRQ or an FIQ interrupt request to a target processor.

## 1.3 Terminology

The following sections define architectural terms used in this specification:

- Interrupt states

- Interrupt types

- Models for handling interrupts on page 1-5

- Spurious interrupts on page 1-5

- Processor security state and Secure and Non-secure GIC accesses on page 1-5

- Banking on page 1-6.

#### 1.3.1 Interrupt states

The following states apply at the interface between the GIC and each processor supported in the system:

| Inactive           | An interrupt that is not active or pending.                                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pending            | An interrupt from a source to the GIC that is recognized as asserted in hardware or generated by software and is waiting to be serviced by a target processor. |

| Active             | An interrupt from a source to the GIC that has been acknowledged by a processor, and is being serviced but has not completed.                                  |

| Active and pending | A processor is servicing the interrupt and the GIC has a pending interrupt from the same source.                                                               |

#### 1.3.2 Interrupt types

A device that implements this GIC architecture can manage the following types of interrupt:

**Peripheral interrupt** This is an interrupt asserted by a signal to the GIC. The GIC architecture defines the following types of peripheral interrupt:

#### Private peripheral interrupt (PPI)

This is a peripheral interrupt that is specific to a single processor.

#### Shared peripheral interrupt (SPI)

This is a peripheral interrupt that the Distributor can route to any combination of processors.

Each peripheral interrupt is either:

#### **Edge-triggered**

This is an interrupt that is asserted on detection of a rising edge of an interrupt signal and then, regardless of the state of the signal, remains asserted until it is cleared by the conditions defined by this specification.

#### Level-sensitive

This is an interrupt that is asserted whenever the interrupt signal level is HIGH, and deasserted whenever the level is LOW.

— Note —

While a level-sensitive interrupt is asserted its state in the GIC is pending, or active and pending. If the peripheral deasserts the interrupt signal for any reason the GIC removes the pending state from the interrupt. For more information see *Interrupt handling state machine* on page 3-10.

#### Software-generated interrupt (SGI)

This is an interrupt generated by software writing to a specific register in the GIC. The system uses SGIs for interprocessor communication.

A software interrupt has edge-triggered properties. The software triggering of the interrupt is equivalent to the edge transition of the interrupt signal on a peripheral input.

#### 1.3.3 Models for handling interrupts

In a multiprocessor implementation, there are two models for handling interrupts:

- **1-N model** Only one processor handles this interrupt. The system must implement a mechanism to determine which processor handles an interrupt that is programmed to target more than one processor.

- **N-N model** All processors receive the interrupt independently. When a processor acknowledges the interrupt, the interrupt pending state is cleared only for that processor. The interrupt remains pending for the other processors.

#### 1.3.4 Spurious interrupts

It is possible that an interrupt that the GIC has signaled to a processor is no longer required. If this happens, when the processor acknowledges the interrupt, the GIC returns a special Interrupt ID that identifies the interrupt as a *spurious interrupt*. This can happen because:

- the state of the interrupt has changed

- software has re-programmed the GIC to change the processing requirements for the interrupt

- the interrupt is handled using the 1-N model and another processor has acknowledged the interrupt.

#### 1.3.5 Processor security state and Secure and Non-secure GIC accesses

A processor that implements the ARM Security Extensions has a security state, either Secure or Non-secure:

- a processor in Non-secure state can make only Non-secure accesses to a GIC

- a processor in Secure state can make both Secure and Non-secure accesses to a GIC

- software running in Non-secure state is described as Non-secure software

- software running in Secure state is described as Secure software.

For more information about the implementation of the Security Extensions on a processor see the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

A multiprocessor system with a GIC that implements the Security Extensions might include one or more processors that do not implement the Security Extensions. Such a processor is implemented so that either:

- it makes only Secure accesses to the GIC, meaning any software running on the processor is Secure software that can only make Secure accesses to the GIC

- it makes only Non-secure accesses to the GIC, meaning any software running on the processor is Non-secure software.

#### 1.3.6 Banking

#### Interrupt banking

In a multiprocessor implementation, for PPIs and SGIs, the GIC can have multiple interrupts with the same interrupt ID. Such an interrupt is called a *banked interrupt*, and is identified uniquely by the combination of its interrupt ID and its associated CPU interface. For more information see *Interrupt IDs* on page 2-4.

#### **Register banking**

Register banking refers to implementing multiple copies of a register at the same address. This occurs:

- in a multiprocessor implementation, for some registers corresponding to banked interrupts

- in a GIC that implements the Security Extensions, to provide separate Secure and Non-secure copies of some registers.

For more information see Register banking on page 4-5.

## Chapter 2 GIC Partitioning

This chapter describes the architectural partitioning of the GIC. It contains the following sections:

- *About GIC partitioning* on page 2-2

- The Distributor on page 2-4

- *CPU interfaces* on page 2-6.

## 2.1 About GIC partitioning

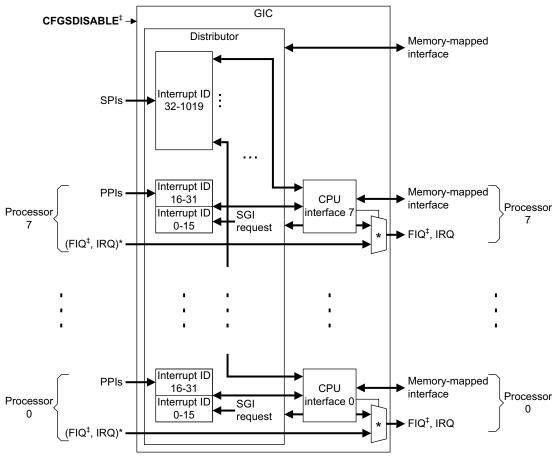

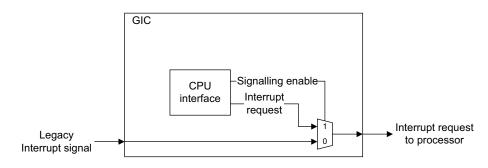

This GIC architecture splits logically into a Distributor block and one or more CPU interface blocks, as Figure 2-1 on page 2-3 shows:

| Distributor    | This performs interrupt prioritization and distribution to the CPU interfaces that connect to the processors in the system. |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| CPU interfaces | Each CPU interface performs priority masking and preemption handling for a connected processor in the system.               |

Each block provides part of the GIC programmers model, and the programmers model is generally the same for each implemented CPU interface. This model supports implementation of the GIC in uniprocessing or multiprocessing environments.

\_\_\_\_\_ Note \_\_\_\_\_

- The split of the GIC into the Distributor and CPU interface blocks is an architectural abstraction. It is IMPLEMENTATION DEFINED whether these blocks are implemented separately or combined.

- In a GIC that implements the Security Extensions in a multiprocessor system, a CPU interface can be implemented so that it receives:

- both Secure and Non-secure accesses

- only Secure accesses

- only Non-secure accesses.

A GIC can implement up to eight CPU interfaces, numbered from 0-7.

‡ Only if Security Extensions are implemented

\* Optional input and bypass multiplexer, see text

## 2.2 The Distributor

The Distributor centralizes all interrupt sources, determines the priority of each interrupt, and for each CPU interface dispatches the interrupt with the highest priority to the interface for priority masking and preemption handling.

The Distributor provides a programming interface for:

- globally enabling the forwarding of interrupts to the CPU interfaces

- enabling or disabling each interrupt

- setting the priority level of each interrupt

- setting the target processor list of each interrupt

- setting each peripheral interrupt to be level-sensitive or edge-triggered

- if the GIC implements the Security Extensions, setting each interrupt as either Secure or Non-secure

- sending an SGI to one or more target processors.

In addition, the Distributor provides:

- visibility of the state of each interrupt

- a mechanism for software to set or clear the pending state of a peripheral interrupt.

#### 2.2.1 Interrupt IDs

Interrupts from sources are identified using *ID numbers*. Each CPU interface can see up to 1020 interrupts. Because of banking of SPIs and PPIs this means the distributor supports up to 1244 interrupts.

The GIC assigns interrupt ID numbers ID0-ID1019 as follows:

- Interrupt numbers ID32-ID1019 are used for SPIs.

- Interrupt numbers ID0-ID31 are used for interrupts that are private to a CPU interface, and are banked in the Distributor,

A banked interrupt is one where the Distributor can have multiple interrupts with the same ID. A banked interrupt is identified uniquely by its ID number and its associated CPU interface number. Of the banked interrupt IDs:

- ID0-ID15 are used for SGIs

- ID16-ID31 are used for PPIs

In a multiprocessor system:

- A PPI is signalled to a particular CPU interface, and is private to that interface. In prioritizing

interrupts for a CPU interface the distributor considers only the PPIs signalled to that interface.

- Each connected processor issues an SGI by writing to the ICDSGIR in the Distributor, see Software Generated Interrupt Register (ICDSGIR) on page 4-39. Each SGI can target multiple processors. In the distributor and in a targeted processor, an SGI is identified uniquely by the combination of its interrupt number, ID0-ID15, and the processor source ID, CPUID0-CPUID7, of the processor that issued the SGI. Banking SGIs means the GIC can handle multiple software interrupts simultaneously without resource conflicts.

The Distributor ignores any write to the ICDSGIR that is not from a processor that is connected to one of the CPU interfaces. How the Distributor determines the processor source ID of a processor writing to the ICDSGIR is IMPLEMENTATION DEFINED.

In a uniprocessor system, there is no distinction between shared and private interrupts, because all interrupts are visible to the processor. In this case the processor source ID value is 0.

• Interrupt numbers ID1020-ID1023 are reserved for special purposes, see *Special interrupt numbers* on page 3-11.

System software sets the priority of each interrupt independent of its interrupt number.

In any system that implements the Security Extensions, to support a consistent model for message passing between processors, ARM strongly recommends that all processors reserve:

- ID0-ID7 for Non-secure interrupts

- ID8-ID15 for Secure interrupts.

For more information about message passing see Message passing between processors on page B-20.

## 2.3 CPU interfaces

Each CPU interface block provides the interface for a processor that operates with the GIC. Each CPU interface provides a programming interface for:

- enabling the signalling of interrupt requests by the CPU interface

- acknowledging an interrupt

- indicating completion of the processing of an interrupt

- setting an interrupt priority mask for the processor

- defining the preemption policy for the processor

- determining the highest priority pending interrupt for the processor.

When enabled, a CPU interface takes the highest priority pending interrupt for its connected processor and determines whether the interrupt has sufficient priority for it to signal the interrupt request to the processor. To determine whether to signal the interrupt request to the processor the CPU interface considers the interrupt priority mask and the preemption settings for the processor. At any time, the connected processor can read the priority of its highest priority active interrupt from a CPU interface register.

The mechanism for signaling an interrupt to the processor is IMPLEMENTATION DEFINED.

#### — Note —

On ARM processor implementations, the traditional mechanism for signalling an interrupt request is by asserting **nIRQ** or **nFIQ**.

The processor acknowledges the interrupt request by reading the CPU interface Interrupt Acknowledge register. The CPU interface returns one of:

- The ID number of the highest priority pending interrupt, if that interrupt is of sufficient priority to generate an interrupt exception on the processor. This is the normal response to an interrupt acknowledge.

- Exceptionally, an ID number that indicates a spurious interrupt.

When the processor acknowledges the interrupt at the CPU interface, the Distributor changes the status of the interrupt from pending to either active, or active and pending. At this point the CPU interface can signal another interrupt to the processor, to preempt interrupts that are active on the processor. If there is no pending interrupt with sufficient priority for signalling to the processor, the interface deasserts the interrupt request signal to the processor.

When the interrupt handler on the processor has completed the processing of an interrupt, it writes to the CPU interface to indicate interrupt completion. When this happens, the distributor changes the status of the interrupt either:

- from active to inactive

- from active and pending to pending.

## Chapter 3 Interrupt Handling and Prioritization

This chapter describes the requirements for interrupt handling and prioritization in the GIC. It contains the following sections:

- About interrupt handling and prioritization on page 3-2

- General handling of interrupts on page 3-5

- Interrupt prioritization on page 3-12

- The effect of the Security Extensions on interrupt handling on page 3-15

- The effect of the Security Extensions on interrupt prioritization on page 3-18

- Pseudocode details of interrupt handling and prioritization on page 3-25.

## 3.1 About interrupt handling and prioritization

The following subsections give more information about the interrupts supported by a GIC, and how a connected processor must determine the range of interrupt IDs supported by the GIC:

- Handling different interrupt types in a multiprocessor system on page 3-3

- *Identifying the supported interrupts* on page 3-3.

The remainder of the chapter describes interrupt handling and prioritization.

Interrupt handling describes:

- how the GIC recognizes interrupts

- how software can program the GIC to configure and control interrupts

- the state machine the GIC maintains for each interrupt on each CPU interface

- how the exception model of a processor interacts with the GIC.

Prioritization describes:

- the configuration and control of interrupt priority

- the order of execution of pending interrupts

- the determination of when interrupts are visible to a target processor, including:

- interrupt priority masking

- interrupt grouping

- preemption of an active interrupt.

The GIC architecture supports uniprocessor and multiprocessor systems. In either a uniprocessor or a multiprocessor system, a GIC can implement the ARM Security Extensions. A GIC that implements the Security Extensions:

- recognizes that a connected processor that implements the Security Extensions makes either Secure accesses or Non-secure accesses to the GIC registers

- supports:

- the configuration of interrupts as either Secure or Non-secure

- the handling of Secure and Non-secure interrupts.

- in a multiprocessor system, might implement the Security Extensions on only some of its CPU interfaces.

Support for Secure and Non-secure interrupts makes interrupt handling and prioritization more complex. This chapter describes interrupt handling and prioritization in a GIC that does not implement the Security Extensions, and then describes the effect of the Security Extensions, in the following sections:

- *General handling of interrupts* on page 3-5

- Interrupt prioritization on page 3-12

- The effect of the Security Extensions on interrupt handling on page 3-15

- The effect of the Security Extensions on interrupt prioritization on page 3-18

- *Pseudocode details of interrupt handling and prioritization* on page 3-25.

#### 3.1.1 Handling different interrupt types in a multiprocessor system

A GIC supports peripheral interrupts and software-generated interrupts, see Interrupt types on page 1-4.

In a multiprocessor implementation the GIC handles:

- software generated interrupts (SGIs) using an N-N model

- peripheral (hardware) interrupts using a 1-N model.

See Models for handling interrupts on page 1-5 for definitions of the two models.

#### 3.1.2 Identifying the supported interrupts

The GIC architecture defines different ID values for the different types of interrupt, see *Interrupt IDs* on page 2-4. However, there is no requirement for the GIC to implement a continuous block of interrupt IDs for any interrupt type.

— Note –

ARM strongly recommends that implemented interrupts are grouped to use the lowest ID numbers and as small a range of interrupt IDs as possible, because this reduces the number of registers that must be implemented, and that discovery routines must check.

To correctly handle interrupts, software must know what interrupt IDs are supported by the GIC. Software can use the ICDISERs to discover this information, see *Interrupt Set-Enable Registers (ICDISERn)* on page 4-19. If the processor implements the Security Extensions, Secure software determines which interrupts are visible to Non-secure software. The Non-secure software must know which interrupts it can see, and might use this discovery process to find this information.

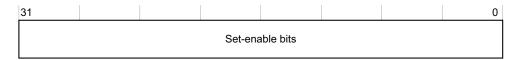

ICDISER0 provides the Set-enables bits for:

- SGIs, using interrupt IDs 15-0, corresponding to register bits [15:0]

- PPIs, using interrupt IDs 31-16, corresponding to register bits [31:16].

The remaining ICDISERs, from ICDISER1, provide the Set-enable bits for the SPIs, starting at interrupt ID 32.

If an interrupt is:

- not supported, the Set-enable bit corresponding to its interrupt ID is RAZ/WI

- supported and permanently enabled, the Set-enable bit corresponding to its interrupt ID is RAO/WI.

Software discovers which interrupts are supported as follows:

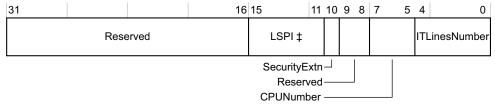

- Read the ICDICTR, see *Interrupt Controller Type Register (ICDICTR)* on page 4-14. The ITLinesNumber field identifies the number of implemented ICDISERs, and therefore the maximum number of SPIs that might be supported.

- Write 0 to the ICDDCR.Enable bit, to disable forwarding of interrupts to CPU interfaces, see *Distributor Control Register (ICDDCR)* on page 4-12.

— Note —

When ICDDCR.Enable is set to 0 the GIC ignores the state of peripheral signals. This means it might miss edge-triggered interrupts.

- For each implemented ICDISER, starting with ICDISER0:

- Write 0xFFFFFFF to the ICDISER.

- Read the value of the ICDISER. Bits that read as 1 correspond to supported interrupt IDs.

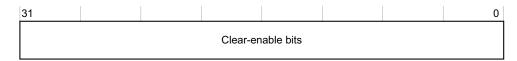

Software uses the ICDICERs to discover which interrupts are permanently enabled, see *Interrupt Clear-Enable Registers (ICDICERn)* on page 4-21. It does this discovery as follows. For each implemented ICDICER, starting with ICDICER0:

- Write 0xFFFFFFFF to the ICDICER. This disables all interrupts that can be disabled.

- Read the value of the ICDICER. Bits that read as 1 correspond to interrupts that are permanently enabled.

- Write 1 to any bits in the ICDICER that correspond to interrupts that must be re-enabled.

The GIC implements the same number of ICDISERs and ICDICERs.

When software has completed its discovery, it writes 1 to the ICDDCR.Enable bit, to enable forwarding of interrupts to CPU interfaces.

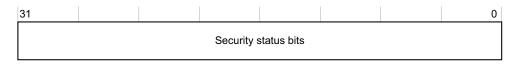

If the GIC implements the Security Extensions, software can use Secure accesses to:

- discover all the supported interrupt IDs.

- write to the ICDISRs, to configure interrupts as Secure or Non-secure, see *Interrupt Security Registers (ICDISRn)* on page 4-17.

Software using Non-secure accesses can discover only the interrupts that are configured as Non-secure.

If Secure software changes the security configuration of any interrupts after Non-secure software has discovered its supported interrupts, it must communicate the effect of those changes to the Non-secure software.

## 3.2 General handling of interrupts

The Distributor maintains a state machine for each supported interrupt on each CPU interface. *Interrupt handling state machine* on page 3-10 describes this state machine and its state transitions. The possible states of an interrupt are:

- inactive

- pending

- active

- active and pending.

When the GIC recognizes an interrupt request, it marks its state as *pending*. Regenerating a pending interrupt does not affect the state of the interrupt.

The GIC operates on interrupts as follows:

– Note –

- 1. The GIC determines whether each interrupt is enabled. An interrupt that is not enabled has no further effect on the GIC.

- 2. For each enabled interrupt that is pending, the Distributor determines the targeted processor or processors.

- 3. For each processor, the Distributor determines the highest priority pending interrupt, based on the priority information it holds for each interrupt, and forwards the interrupt to the CPU interface.

- 4. The CPU interface compares the interrupt priority with the current interrupt priority for the processor, determined by a combination of the Priority Mask Register, the current preemption settings, and the highest priority active interrupt for the processor. If the interrupt has sufficient priority, the GIC signals an interrupt exception request to the processor.

Throughout this document, an interrupt is described as having *sufficient priority* if its priority value, compared with the Priority Mask Register value, the preemption settings for the interface, and the priority of the highest priority active interrupt on the processor, mean that the CPU interface must signal the interrupt request to the processor.

- 5. When the processor takes the interrupt exception, it reads the ICCIAR in its CPU interface to acknowledge the interrupt, see *Interrupt Acknowledge Register (ICCIAR)* on page 4-56. This read returns an Interrupt ID that the processor uses to select the correct interrupt handler. When it recognizes this read, the GIC changes the state of the interrupt:

- if the pending state of the interrupt persists when the interrupt becomes active, or if the interrupt is generated again, from pending to active and pending.

- otherwise, from pending to active

——Note —

- A level-sensitive peripheral interrupt persists when it is acknowledged by the processor, because the interrupt signal to the GIC remains asserted until the interrupt service routine (ISR) running on the processor accesses the peripheral asserting the signal.

- In a multiprocessor implementation, the GIC handles:

- SGIs using an N-N model, where the acknowledgement of an interrupt by one processor has no effect on the state of the interrupt on other CPU interfaces

- peripheral interrupts using a 1-N model, where the acknowledgement of an interrupt by one processor removes the pending status of the interrupt on any other targeted processors, see *Implications of the 1-N model* on page 3-8.

- 6. When the processor has completed handling the interrupt, it signals this completion by writing to the ICCEOIR in the GIC, see *End of Interrupt Register (ICCEOIR)* on page 4-59.

The GIC requires the order of completion of interrupts by a particular processor to be the reverse of the order of acknowledgement, so the last interrupt acknowledged must be the first interrupt completed.

When the processor writes to the ICCEOIR, the GIC changes the state of the interrupt, for the corresponding CPU interface, either:

- from active to inactive

- from active and pending to pending.

If there is no pending interrupt of sufficient priority for the CPU interface to signal it to the processor, the interface deasserts the interrupt exception request to the processor.

A CPU interface never signals to the connected processor any interrupt that is active and pending. It only signals interrupts that are pending and have sufficient priority:

- for SPIs, this means the interface never signals any interrupt that is active and pending on any CPU interface

- for SGIs, the interface never signals any interrupt that is active and pending on this interface, but does not consider whether the interrupt is active and pending on any other interface

- any PPI is private to this interface and the interface does not signal it if it is active and pending.

For more information about the steps in this process see:

- *Interrupt prioritization* on page 3-12,

- for a GIC that implements the Security Extensions:

- The effect of the Security Extensions on interrupt handling on page 3-15

- The effect of the Security Extensions on interrupt prioritization on page 3-18.

#### 3.2.1 Interrupt controls in the GIC

The following sections describe the interrupt controls in the GIC:

- Interrupt enables

- Setting and clearing pending state of an interrupt

- Finding the active or pending state of an interrupt on page 3-8

- *Generating an SGI* on page 3-8.

#### Interrupt enables

For peripheral interrupts, a processor:

- enables an interrupt by writing to the appropriate ICDISER bit, see *Interrupt Set-Enable Registers* (*ICDISERn*) on page 4-19

- disables an interrupt by writing to the appropriate ICDICER bit, see *Interrupt Clear-Enable Registers* (*ICDICERn*) on page 4-21.

Whether SGIs are permanently enabled, or can be enabled and disabled by writes to the ICDISER and ICDICER, is IMPLEMENTATION DEFINED.

Writes to the ICDISERs and ICDICERs control whether the Distributor forwards interrupts to the CPU interfaces. Disabling an interrupt by writing to the appropriate ICDICER does not prevent that interrupt from changing state, for example becoming pending.

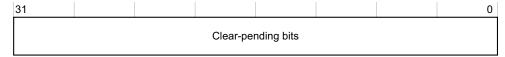

#### Setting and clearing pending state of an interrupt

For peripheral interrupts, a processor can:

- set the pending state by writing to the appropriate ICDISPR bit, see *Interrupt Set-Pending Registers* (*ICDISPRn*) on page 4-23

- clear the pending state by writing to the appropriate ICDICPR bit, see *Interrupt Clear-Pending Registers (ICDICPRn)* on page 4-26.

For a level-sensitive interrupt:

- If the hardware signal of an interrupt is asserted when a processor writes to the corresponding ICDICPR bit then the write to the register has no effect on the pending state of the interrupt.

- If a processor writes a 1 to an ICDISPR bit then the corresponding interrupt becomes pending regardless of the state of the hardware signal of that interrupt, and remains pending regardless of the assertion or deassertion of the signal.

For more information about the control of the pending state of a level-sensitive interrupt see *Control of the pending status of level-sensitive interrupts* on page 4-28.

For SGIs, the GIC ignores writes to the corresponding ICDISPR and ICDISCR bits. A processor cannot change the state of a software-generated interrupt by writing to these registers.

#### Finding the active or pending state of an interrupt

A processor can find:

- the pending state of an interrupt by reading the corresponding ICDISPR or ICDICPR bit

- the active state of an interrupt by reading the corresponding ICDABR bit, see *Active Bit Registers* (*ICDABRn*) on page 4-29.

The corresponding register bit is 1 if the interrupt is pending or active. If an interrupt is pending and active the corresponding bit is 1 in both registers.

For an SGI, the corresponding ICDISPR and ICDICPR bits RAO if there is a pending interrupt from at least one generating processor that targets the processor reading the ICDISPR or ICDICPR.

#### **Generating an SGI**

A processor generates an SGI by writing to an ICDSGIR, see *Software Generated Interrupt Register* (*ICDSGIR*) on page 4-39. An SGI can target multiple processors, and the ICDSGIR write specifies the target processor list. The ICDSGIR includes optimization for:

- interrupting only the processor that writes to the ICDSGIR

- interrupting all processors other than the one that writes to the ICDSGIR.

SGIs from different processors use the same interrupt IDs. Therefore, any target processor can receive SGIs with the same interrupt ID from different processors. On the CPU interface of the target processor, the pending status of each of these interrupts is independent of the pending status of any other interrupt, but only one interrupt with this ID can be active. Reading the ICCIAR for an SGI returns both the interrupt ID and the CPU ID of the processor that generated the interrupt, uniquely identifying the interrupt.

In a multiprocessor implementation, the interrupt priority of each SGI interrupt ID is defined independently for each CPU interface, see *Interrupt Priority Registers (ICDIPRn)* on page 4-31. This means that, for each CPU interface, all SGIs with a particular interrupt ID that are pending on that interface have the same priority and must be handled serially. How the CPU interface serializes these SGIs is IMPLEMENTATION DEFINED.

#### 3.2.2 Implications of the 1-N model

In a multiprocessor implementation, the GIC uses a 1-N model to handle peripheral interrupts that target more than one processor. This means that when the GIC recognizes an interrupt acknowledge from one of the target processors it clears the pending state of the interrupt on all the other targeted processors. This model means an interrupt can be handled by the first available processor. However, the interrupt might generate an interrupt exception on more than one of the targeted processors, for example if two of the targeted processors recognize the interrupt exception request from the GIC at similar times.

When multiple target processors attempt to acknowledge the interrupt, the following can occur:

• A processor reads the ICCIAR and obtains the interrupt ID of the interrupt to be serviced, see *Interrupt Acknowledge Register (ICCIAR)* on page 4-56. More than one target processor might have obtained this interrupt ID, if the processors read their ICCIARs at very similar times. The system

might require software on the target processors to ensure that only one processor runs its interrupt service routine. A typical mechanism to achieve this is implementing a lock on the *interrupt service routine* (ISR), in shared memory. This might operate as follows:

- each target processor that obtains the interrupt ID from its read of the ICCIAR runs a semaphore routine, attempting to obtain a lock on the ISR corresponding to the specified ID value

- if a processor fails to obtain the lock it does no further processing of the interrupt, but writes the interrupt ID to its ICCEOIR, see *End of Interrupt Register (ICCEOIR)* on page 4-59

- the processor that obtains the lock handles the interrupt and then writes the interrupt ID to its ICCEOIR.

- A processor reads the ICCIAR and obtains the interrupt ID 1023, indicating a spurious interrupt. The processor can return from its interrupt service routine without writing to its ICCEOIR.

The spurious interrupt ID indicates that the original interrupt is no longer pending, typically because another target processor is handling it.

#### – Note –

- A GIC implementation might ensure that only one processor can make a 1-N interrupt active, removing the need for a lock on the ISR. This is not required by the architecture, and generic GIC code must not rely on this behavior.

- For any processor, if an interrupt is active and pending, the GIC does not signal an interrupt exception request for this interrupt to any processor until the active status is cleared.

#### 3.2.3 Interrupt handling state machine

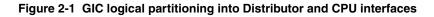

The distributor maintains a state machine for each supported interrupt on each CPU interface. Figure 3-1 shows an instance of this state machine, and the possible state transitions.

#### Figure 3-1 Interrupt handling state machine

#### — Note ———

SGIs are generated only by writes to an ICDSGIR. Peripheral interrupts are generated by either a peripheral indicating it requires service, or by a write to an ICDISPR.

When the Distributor and CPU interfaces are enabled, the conditions that cause each of the state transitions are as follows:

#### Transition A1 or A2, add pending status

For an SGI:

- Occurs on a write to an ICDSGIR that specifies the processor as a target.

- If the GIC implements the Security Extensions and the write to the ICDSGIR is Secure, the transition occurs only if the security configuration of the specified SGI, for the appropriate CPU interface, corresponds to the ICDSGIR.SATT bit value.

For an SPI or PPI, occurs if either:

- a peripheral asserts an interrupt signal

- software writes to an ICDISPR.

#### Transition B1 or B2, remove pending status

Not applicable to SGIs:

- a pending SGI must transition through the active state, or reset, to remove its pending status.

- an active and pending SGI must transition through the pending state, or reset, to remove its pending status.

For an SPI or PPI, occurs if either:

- the level-sensitive interrupt is pending only because of the assertion of an input signal, and that signal is deasserted

- the interrupt is pending only because of the assertion of an edge-triggered interrupt signal, or a write to an ICDISPR, and software writes to the corresponding ICDICPR.

- **Transition C** If the interrupt is enabled and of sufficient priority to be signalled to the processor, occurs when software reads from the ICCIAR.

- **Transition D** For an SGI, occurs if the associated SGI is enabled and the Distributor forwards it to the CPU interface at the same time that the processor reads the ICCIAR to acknowledge a previous instance of the SGI. Whether this transition occurs depends on the timing of the read of the ICCIAR relative to the reforwarding of the SGI.

For an SPI or PPI:

- Occurs if all the following apply:

- The interrupt is enabled.

- Software reads from the ICCIAR. This read adds the active state to the interrupt.

- For a level-sensitive interrupt, the interrupt signal remains asserted. This is usually the case, because the peripheral does not deassert the interrupt until the processor has serviced the interrupt.

- For an edge-triggered interrupt, whether this transition occurs depends on the timing of the read of the ICCIAR relative to the detection of the reassertion of the interrupt. Otherwise the read of the ICCIAR causes transition C, possibly followed by transition A2.

#### Transition E1 or E2, remove active status

Occurs when software writes to the ICCEOIR.

#### 3.2.4 Special interrupt numbers

The GIC architecture reserves interrupt ID numbers 1020-1023 for special purposes. In a GIC that does not implement the Security Extensions, the only one of these used is ID 1023. This value is returned to a processor, in response to an interrupt acknowledge, if there is no pending interrupt with sufficient priority for it to be signalled to the processor, It is described as a response to a *spurious interrupt*.

— Note ——

A race condition can cause a spurious interrupt. For example, a spurious interrupt can occur if a processor writes a 1 to a field in an ICDICER that corresponds to a pending interrupt after the CPU interface has signalled the interrupt to the processor and the processor has recognized the interrupt, but before the processor has read from the ICCIAR.

For more information about the special interrupt numbers see *Special interrupt numbers when the Security Extensions are implemented* on page 3-16.

## 3.3 Interrupt prioritization

This section describes interrupt prioritization in the GIC architecture. It includes the following subsections:

- Preemption on page 3-13

- Priority masking on page 3-13

- Priority grouping on page 3-14

- Interrupt generation on page 3-14.

Software configures interrupt prioritization in the GIC by assigning a priority value to each interrupt source. Priority values are 8-bit unsigned binary. A GIC supports a minimum of 16 and a maximum of 256 priority levels. If the GIC implements fewer than 256 priority levels, low-order bits of the priority fields are RAZ/WI, This means that the number of implemented priority field bits is IMPLEMENTATION DEFINED in the range 4-8, as Table 3-1 shows.

| Implemented priority bits | Possible priority field values       | Number of priority levels |

|---------------------------|--------------------------------------|---------------------------|

| [7:0]                     | 0x00-0xFF (0-255), all values        | 256                       |

| [7:1]                     | 0x00-0xFE, (0-254), even values only | 128                       |

| [7:2]                     | 0x00-0xFC (0-252), in steps of 4     | 64                        |

| [7:3]                     | 0x00-0xF8 (0-248), in steps of 8     | 32                        |

| [7:4]                     | 0x00-0xF0 (0-240), in steps of 16    | 16                        |

#### Table 3-1 Effect of not implementing some LS priority field bits

In the GIC prioritization scheme, lower numbers have higher priority, that is, the lower the assigned priority value the higher the priority of the interrupt. The highest interrupt priority always has priority field value 0, and the lowest value depends on the number of implemented priority levels, as Table 3-1 shows.

The ICDIPRs hold the priority value for each supported interrupt, see *Interrupt Priority Registers* (*ICDIPRn*) on page 4-31. To determine the number of priority bits implemented write 0xFF to an ICDIPR priority field and read back the value stored.

#### — Note ———

ARM recommends that, before checking the priority range in this way

- for a peripheral interrupt, software first disables the interrupt

- for an SGI. software first checks that the interrupt is inactive.

An implementation might reserve an interrupt for a particular purpose and assign a fixed priority to that interrupt, meaning the priority value for that interrupt is read-only.

This model aligns with the priority grouping mechanism described in *Priority grouping* on page 3-14.

If, on a particular CPU interface, multiple pending interrupts have the same priority, and have sufficient priority that the interface must signal them to the processor, it is IMPLEMENTATION DEFINED how the interface selects which interrupt to signal.

When an interrupt is active on a CPU interface, the GIC might signal a higher-priority interrupt on that CPU interface, see *Preemption*.

Software sets the priority of each interrupt in the appropriate ICDIPR, see *Interrupt Priority Registers* (*ICDIPRn*) on page 4-31. It is IMPLEMENTATION DEFINED whether a write to the ICDIPR changes the priority of any active interrupt.

#### 3.3.1 Preemption

A CPU interface supports forwarding of higher priority pending interrupts to a target processor before an active interrupt completes. A pending interrupt is only forwarded if it has a higher priority than all of:

- the priority of the highest priority active interrupt on the target processor, the *running priority* for the processor, see *Running Priority Register (ICCRPR)* on page 4-61

- the priority mask, see *Priority masking*

- the priority group, see *Priority grouping* on page 3-14.

Preemption occurs at the time when the processor acknowledges the new interrupt, and starts to service it in preference to the previously active interrupt or the currently running process. When this occurs, the initial active interrupt is said to have been *preempted*. Starting to service an interrupt while another interrupt is still active is sometimes described as *interrupt nesting*.

— Note —

For a processor that complies with the ARM architecture:

- The value of the I or F bit in the CPSR determines whether the processor responds to the signalled interrupt by starting the interrupt acknowledge procedure.

- When processing a preempting interrupt, the processor must save and later restore the context of the previously active ISR.

For more information, see the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

#### 3.3.2 Priority masking

The ICCPMR for a CPU interface defines a priority threshold for the target processor, see *Interrupt Priority Mask Register (ICCPMR)* on page 4-52. The GIC only signals pending interrupts with a higher priority than this threshold value to the target processor. A value of zero, the register reset value, masks all interrupts to the associated processor.

The GIC always masks an interrupt that has the largest supported priority field value. This provides an additional means of preventing an interrupt being signalled to any processor.

#### — Note —

Writing 255 to the ICCPMR always sets it to the largest supported priority field value. Table 3-1 on page 3-12 shows how the largest supported field value varies with the number of implemented priority bits.

#### 3.3.3 Priority grouping

Priority grouping splits each priority value into two fields, the *group priority* and the *subpriority* fields. The GIC uses the group priority field to determine whether a pending interrupt has sufficient priority to preempt a currently active interrupt.

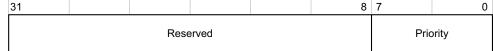

The binary point field in the ICCBPR controls the split of the priority bits into the two parts. This 3-bit field specifies how many of the least significant bits of the 8-bit interrupt priority field are excluded from the group priority field, as Table 3-2 shows.

| Binary point value | Interrupt priority field [7:0] |                   |                         |  |

|--------------------|--------------------------------|-------------------|-------------------------|--|

|                    | Group priority field           | Subpriority field | Field with binary point |  |

| 0                  | [7:1]                          | [0]               | ggggggg.s               |  |

| 1                  | [7:2]                          | [1:0]             | gggggg.ss               |  |

| 2                  | [7:3]                          | [2:0]             | ggggg.sss               |  |

| 3                  | [7:4]                          | [3:0]             | gggg.ssss               |  |

| 4                  | [7:5]                          | [4:0]             | ggg.sssss               |  |

| 5                  | [7:6]                          | [5:0]             | gg.ssssss               |  |

| 6                  | [7]                            | [6:0]             | g.8888888               |  |

| 7                  | No preemption                  | [7:0]             | .SSSS SSSS              |  |

#### Table 3-2 Priority grouping by binary point

The minimum binary point value supported is IMPLEMENTATION DEFINED in the range 0-3.

For more information about the ICCBPR see Binary Point Register (ICCBPR) on page 4-54.

Where multiple pending interrupts share the same group priority, the GIC uses the subpriority field to resolve the priority within a group. Where two or more pending interrupts in a group have the same subpriority, how the GIC selects between the interrupts is IMPLEMENTATION DEFINED.

#### 3.3.4 Interrupt generation

The pseudocode in *Exception generation pseudocode, without the Security Extensions* on page 3-27 describes the generation of interrupts by the GIC.

# 3.4 The effect of the Security Extensions on interrupt handling

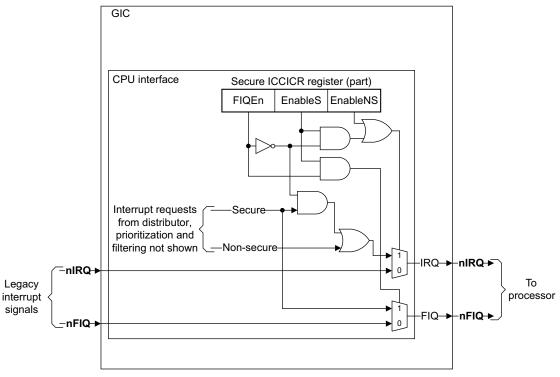

If a GIC CPU interface implements the Security Extensions, it provides two interrupt output signals, IRQ and FIQ:

- The CPU interface always uses the IRQ exception request for Non-secure interrupts

- Software can configure the CPU interface to use either IRQ or FIQ exception requests for Secure interrupts.

#### -Note -

In a GIC that does not support the Security Extensions, each CPU interface implements only a single port for signalling interrupts to a target processor. The alternatives for providing GIC interrupt routing for both IRQ and FIQ exception requests in a processor environment that does not include the Security Extensions are:

- Implement two instances of the GIC, without the Security Extensions. One instance routes FIQs and the other instance routes IRQs.

- Implement a single GIC that implements the Security Extensions, and implements the CPU interface to the processor so that all accesses appear to the GIC as Secure accesses. In an implementation of this model, software configures an interrupt as Secure to assign it to the generation of FIQ exception requests to the processor.

The remainder of this section describes a GIC that implements the Security Extensions.

### 3.4.1 Security Extensions support

Software can detect support for the Security Extensions by reading the ICDICTR.SecurityExtn bit, see *Interrupt Controller Type Register (ICDICTR)* on page 4-14.

Secure software makes Secure writes to the ICDISRs to configure each interrupt as Secure or Non-secure, see *Interrupt Security Registers (ICDISRn)* on page 4-17.

In addition:

- The banking of registers provides independent control of Secure and Non-secure interrupts, see *Effect* of the Security Extensions on the programmers model on page 4-7.

- The Secure copy of the ICCICR has additional fields to control the processing of Secure and Non-secure interrupts, see *CPU Interface Control Register (ICCICR)* on page 4-47. These fields are:

- the SBPR bit, that affects the preemption of Non-secure interrupts, see *Control of preemption* by Non-secure interrupts on page 3-22

- the FIQEn bit, that controls whether the interface signals Secure interrupts to the processor using the IRQ or FIQ interrupt exception requests

- the AckCtl bit, that affects the acknowledgment of Non-secure interrupts, see *Effect of the* Security Extensions on interrupt acknowledgement on page 3-16

- the EnableNS bit, that controls whether Non-secure interrupts are signaled to the processor, and is an alias of the Enable bit in the Non-secure ICCICR.

- The Non-secure copy of the ICCBPR is aliased as the ICCABPR, see *Aliased Binary Point Register* (*ICCABPR*) on page 4-62. This is a Secure register, meaning it is only accessible by Secure accesses.

#### 3.4.2 Special interrupt numbers when the Security Extensions are implemented

*Special interrupt numbers* on page 3-11 describes the use of interrupt ID 1023 to indicate a *spurious interrupt*. The full list of the interrupt ID numbers the GIC architecture reserves for special purposes is as follows:

1020-1021 Reserved.

**1022** Used only if the GIC implements the Security Extensions.

– Note –

The GIC returns this value to a processor in response to an interrupt acknowledge only when all of the following apply:

- the interrupt acknowledge is a Secure read

- the highest priority pending interrupt is Non-secure

- the AckCtl bit in the Secure ICCICR is set to 0

- the priority of the interrupt is sufficient for it to be signalled to the processor.

Interrupt ID 1022 informs Secure software that there is a Non-secure interrupt of sufficient priority to be signalled to the processor, that must be handled by Non-secure software. In this situation the Secure software might alter its schedule to permit Non-secure software to handle the interrupt, to minimize the interrupt latency.

**1023** This value is returned to a processor, in response to an interrupt acknowledge, if there is no pending interrupt with sufficient priority for it to be signalled to the processor.

On a processor that implements the Security Extensions, Secure software treats values of 1022 and 1023 as spurious interrupts.

### 3.4.3 Effect of the Security Extensions on interrupt acknowledgement

When a processor takes an interrupt, it acknowledges the interrupt by reading the ICCIAR, see *General handling of interrupts* on page 3-5. A read of the ICCIAR always acknowledges the highest priority pending interrupt for the processor performing the read.

If the highest priority pending interrupt is a Secure interrupt, the processor must make a Secure read of the ICCIAR to acknowledge it.

By default, the processor must make a Non-secure read of the ICCIAR to acknowledge a Non-secure interrupt. If he AckCtl bit in the Secure ICCICR is set to 1 the processor can make a Secure read of the ICCIAR to acknowledge a Non-secure interrupt.

If the read of the ICCIAR does not match the security of the interrupt, taking account of the AckCtl bit value for a Non-secure interrupt, the ICCIAR read does not acknowledge any interrupt and returns the value:

- 1022 for a Secure read when the highest priority interrupt is Non-secure

- 1023 for a Non-secure read when the highest priority interrupt is Secure.

See Effect of the Security Extensions on reads of the ICCIAR on page 4-58 for more information.

# 3.5 The effect of the Security Extensions on interrupt prioritization

If the GIC supports the Security Extensions:

- Secure software must program the ICDISRs to configure each supported interrupt as either Secure or Non-secure, see *Interrupt Security Registers (ICDISRn)* on page 4-17

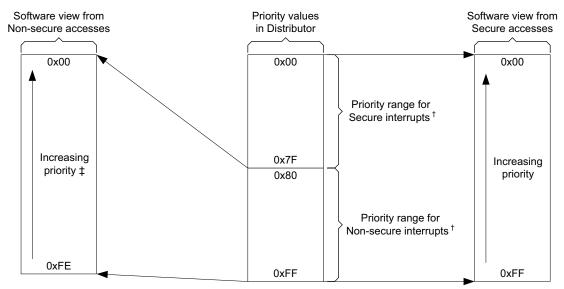

- the GIC provides Secure and Non-secure views of the interrupt priority settings

- the minimum number of priority values supported increases from 16 to 32.

— Note –

Non-secure accesses can see only half of the supported priority values. Therefore, if the GIC implements 32 priority values, Non-secure accesses see only 16 priority values.

#### 3.5.1 Software views of interrupt priority

When a processor reads the priority value of an interrupt, the GIC returns either the Secure or the Non-secure view of that value, depending on whether the access is Secure or Non-secure. This section describes the two views of interrupt priority, and the relationship between them.

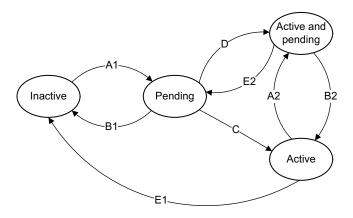

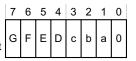

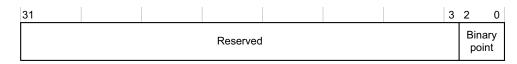

For a Secure access, the GIC implements a minimum of 32 and a maximum of 256 priority levels. This means it implements 5-8 bits of the 8-bit priority value fields. Unimplemented low-order bits of the priority fields are RAZ/WI, Figure 3-2 shows the Secure view of a priority value field for a Secure interrupt.

#### Figure 3-2 Secure view of the priority field for a Secure interrupt

In this view:

- bits H-D are the bits that the GIC must implement

- bits c-a are the bits the GIC might implement, that are RAZ/WI if not implemented.

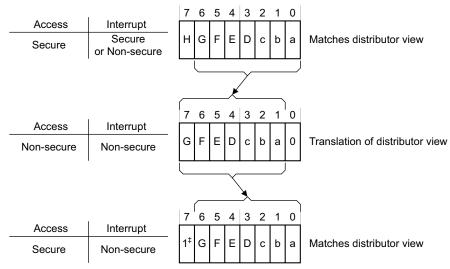

A Non-secure access can only see a priority value field that corresponds to a Non-secure access. For a Non-secure access, the GIC supports half the priority levels it supports for a Secure access. Figure 3-3 shows the Non-secure view of a priority value field for a Non-secure interrupt.

Non-secure view, priority value field for Non-secure interrupt

In this view:

- bits G-D are the bits that the GIC must implement

- bits c-a are the bits the GIC might implement, that are RAZ/WI if not implemented

- bit [0] is RAZ/WI.

The Non-secure view of a priority value does not show how the value is stored in the Distributor. Taking the value from a Non-secure write to a priority field, before storing the value the Distributor:

- right-shifts the value by one bit

- sets bit [7] of the value to 1.

This translation means the priority value for the Non-secure interrupt is in the top half of the possible value range, meaning the interrupt priority is in the bottom half of the priority range.

A Secure read of the priority value for a Non-secure interrupt returns the value stored in the distributor. Figure 3-4 shows this Secure view of the priority value field for a Non-secure interrupt that has had its priority value field set by a Non-secure access, or has had a priority value with bit [7] == 1 set by a Secure access:

|                                                                                                        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|

| Secure read,<br>priority value field for Non-secure interrupt,<br>with value set by a Non-secure write | 1 | G | F | E | D | с | b | а |

#### Figure 3-4 Secure read of the priority field for a Non-secure interrupt

A Secure write to the priority value field for a Non-secure interrupt can set bit [7] to 0, but see *Recommendations for managing priority values* on page 3-22. If a Secure write sets bit [7] to 0:

- A Non-secure read returns the value 0bGFEDcba0.

- A Non-secure write can change the value of the field, but only to a value that has bit [7] set to 1 in the distributor view of the field.

- Note –

This behavior of Non-secure accesses applies only to the Priority value fields in the ICDIPR, see *Interrupt Priority Registers (ICDIPRn)* on page 4-31:

- if the Priority field in the ICCPMR holds a value with bit [7] == 0, then the field is RAZ/WI to Non-secure accesses, see *Interrupt Priority Mask Register (ICCPMR)* on page 4-52

- if the Priority field in the ICCRPR holds a value with bit [7] == 0, then the field is RAZ to Non-secure reads, see *Running Priority Register (ICCRPR)* on page 4-61.

Figure 3-5 on page 3-20 shows the relationship between the views of the Priority value fields.

‡ If the priority value was set by a Non-secure write, bit [7] is set to 1 in the Distributor, and a Secure read sees this value. A Secure write to the field can set this bit to 0, see text for how this affects Non-secure accesses to the field.

The priority field for a Secure interrupt is RAZ/WI to Non-secure accesses.

#### Figure 3-5 Relationship between Secure and Non-secure views of interrupt priority fields

Figure 3-6 on page 3-21 shows how the software views of the interrupt priorities, from Secure and Non-secure accesses, relate to the priority values held in the Distributor, and the interrupt value that are visible to Secure and Non-secure accesses. This is for a GIC that implements the maximum range of priority values.

‡ All priority values are even (bit [0] == 0) in the view from Non-secure accesses

† Ranges recommended by ARM for normal use, see text for more information

#### Figure 3-6 Software views of the priorities of Non-secure and Secure interrupts

Table 3-3 shows how the number of priority value bits implemented by the GIC affects the Secure and Non-secure views of interrupt priority.

| Possible priority field values      |                                                                                                             |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| Secure view                         | Non-secure view                                                                                             |  |  |

| 0xFF-0x00 (255-0), all values       | 0xFE-0x00 (254-0), even values only                                                                         |  |  |

| 0xFE-0x00 (254-0), even values only | 0xFC-0x00 (252-0), in steps of 4                                                                            |  |  |

| 0xFC-0x00 (252-0), in steps of 4    | 0xF8-0x00 (248-0), in steps of 8                                                                            |  |  |

| 0xF8-0x00 (248-0), in steps of 8    | 0xF0-0x00 (240-0), in steps of 16                                                                           |  |  |

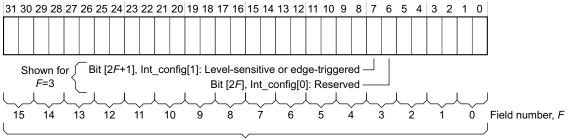

|                                     | Secure view0xFF-0x00 (255-0), all values0xFE-0x00 (254-0), even values only0xFC-0x00 (252-0), in steps of 4 |  |  |