# Arm® Architecture Reference Manual Supplement Memory System Resource Partitioning and Monitoring (MPAM), for Armv8-A

# Arm Architecture Reference Manual Supplement Memory System Resource Partitioning and Monitoring (MPAM), for Armv8-A

Copyright © 2018-2019 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

The following releases of this document have been made.

Release history

| Date             | Issue | Confidentiality  | Change              |

|------------------|-------|------------------|---------------------|

| 30 October, 2018 | A.a   | Non-Confidential | EAC release         |

| 05 July, 2019    | A.b   | Non-Confidential | Updated EAC release |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". Arm PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. You must follow the Arm's trademark usage guidelines http://www.arm.com/company/policies/trademarks.

Copyright © 2018-2019 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

In this document, where the term Arm is used to refer to the company it means "Arm or any of its subsidiaries as appropriate".

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

# **Product Status**

The information in this document is final, that is for a developed product.

### Web Address

http://www.arm.com

# Contents

|              |     | Ргетасе                                   |      |

|--------------|-----|-------------------------------------------|------|

|              |     | About this book                           |      |

|              |     | Using this book                           | x    |

|              |     | Conventions                               | xii  |

|              |     | Additional reading                        | xiv  |

|              |     | Feedback                                  | X\   |

| Chapter 1    |     | Introduction                              |      |

| -            | 1.1 | Overview                                  | 1-18 |

|              | 1.2 | Memory-system resource partitioning       | 1-19 |

|              | 1.3 | Memory-system resource usage monitoring   | 1-20 |

|              | 1.4 | Memory-system components                  |      |

|              | 1.5 | Implementation flexibility                |      |

|              | 1.6 | Example uses                              |      |

| Chapter 2    |     | MPAM and Arm Memory-System Architecture   |      |

| •            | 2.1 | MPAM and Arm memory-system architecture   | 2-26 |

| Chapter 3    |     | ID Types, Properties, and Spaces          |      |

| •            | 3.1 | Introduction                              | 3-28 |

|              | 3.2 | ID types and properties                   |      |

|              | 3.3 | PARTID spaces and properties              |      |

|              | 3.4 | Communication of MPAM information to MSCs |      |

|              | 3.5 | MPAM_NS                                   |      |

| Chapter 4    |     | MSC Propagation of MPAM Information       |      |

| -            | 4.1 | Introduction                              | 4-34 |

|              | 4.2 | Requesting master components              | 4-35 |

|              | 4.3 | Terminating slave components              | 4-36 |

|              | 4.4 | Intermediate slave-master components      | 4-37 |

|              | 4.5 | Request buffering                         | 4-38 |

|              | 4.6 | Cache memory                              | 4-39 |

| Chapter 5    |     | System Model                              |      |

| <del>-</del> | 5.1 | Introduction                              | 5-42 |

|              | 5.2 | System-level field widths                 | 5-44 |

|              | 5.3 | PE behavior                               |      |

|              | 5.4 | Other requesters with MPAM                | 5-46 |

|              |     |                                           |      |

|            | 5.5  | Requesters without MPAM support                                   | 5-47   |

|------------|------|-------------------------------------------------------------------|--------|

|            | 5.6  | Model of a resource partitioning control                          | 5-48   |

|            | 5.7  | Interconnect behavior                                             | 5-49   |

|            | 5.8  | Cache behavior                                                    |        |

|            | 5.9  | Memory-channel controller behavior                                |        |

| Chapter 6  |      | PE Generation of MPAM Information                                 |        |

|            | 6.1  | Introduction                                                      | 6-54   |

|            | 6.2  | Discovering MPAM                                                  |        |

|            | 6.3  | MPAM System registers                                             |        |

|            | 6.4  | Instruction, data, translation table walk, and other accesses     |        |

|            | 6.5  | Security                                                          |        |

|            |      | PARTID virtualization                                             |        |

|            | 6.6  |                                                                   |        |

|            | 6.7  | MPAM AArch32 interoperability                                     |        |

|            | 6.8  | Support for nested virtualization                                 |        |

|            | 6.9  | MPAM errors and default ID generation                             | 6-70   |

| Chapter 7  |      | System Registers                                                  |        |

|            | 7.1  | Overview                                                          |        |

|            | 7.2  | Synchronization of system register changes                        | 7-73   |

|            | 7.3  | Summary of system registers                                       | 7-74   |

|            | 7.4  | System register descriptions                                      |        |

|            | 7.5  | MPAM enable                                                       |        |

|            | 7.6  | Lower-EL MPAM register access trapping                            |        |

|            | 7.7  | Reset                                                             |        |

|            | 7.8  | Unimplemented exception levels                                    | -      |

| Chapter 8  |      | MPAM in MSCs                                                      |        |

| Onapter 0  | 8.1  | Introduction                                                      | 0 110  |

|            | 8.2  | Resource controls                                                 |        |

|            | -    |                                                                   |        |

|            | 8.3  | Security in MSCs                                                  |        |

|            | 8.4  | Virtualization support in system MSCs                             |        |

|            | 8.5  | PE with integrated MSCs                                           |        |

|            | 8.6  | System-wide PARTID and PMG widths                                 |        |

|            | 8.7  | MPAM interrupts                                                   | 8-124  |

| Chapter 9  |      | Resource Partitioning Controls                                    |        |

| -          | 9.1  | Introduction                                                      | 9-128  |

|            | 9.2  | Partition resources                                               | 9-129  |

|            | 9.3  | Standard partitioning control interfaces                          | 9-130  |

|            | 9.4  | Vendor or implementation-specific partitioning control interfaces |        |

|            | 9.5  | Measurements for controlling resource usage                       |        |

|            | 9.6  | PARTID narrowing                                                  |        |

|            | 9.7  | System reset of MPAM controls in MSCs                             |        |

|            | 9.8  | About the fixed-point fractional format                           |        |

| Chapter 10 |      | Resource Monitors                                                 |        |

| Chapter 10 | 40.4 |                                                                   | 40.440 |

|            | 10.1 | Introduction                                                      |        |

|            | 10.2 | MPAM resource monitors                                            |        |

|            | 10.3 | Common features                                                   |        |

|            | 10.4 | Monitor configuration                                             | 10-151 |

| Chapter 11 |      | Memory-Mapped Registers                                           |        |

|            | 11.1 | Overview of MMRs                                                  |        |

|            | 11.2 | Summary of memory-mapped registers                                | 11-159 |

|            | 11.3 | Memory-mapped ID register description                             |        |

|            | 11.4 | Memory-mapped partitioning configuration registers                |        |

|            | 11.5 | Memory-mapped monitoring configuration registers                  |        |

|            |      |                                                                   |        |

|            | 11.6 | Memory-mapped control and status registers             | 11-235 |

|------------|------|--------------------------------------------------------|--------|

| Chapter 12 | 12.1 | Errors in MSCs                                         | 12-242 |

|            | 12.2 | Error conditions in accessing memory-mapped registers  |        |

|            | 12.3 | Overwritten error status                               |        |

|            | 12.4 | Behavior of configuration reads and writes with errors | 12-247 |

| Chapter 13 |      | Armv8 Pseudocode                                       |        |

| -          | 13.1 | Shared pseudocode                                      | 13-250 |

| Appendix A | 4    | Generic Resource Controls                              |        |

|            | A.1  | Introduction                                           | A-258  |

|            | A.2  | Portion resource controls                              | A-259  |

|            | A.3  | Maximum-usage resource controls                        | A-260  |

|            | A.4  | Proportional resource allocation facilities            | A-261  |

|            | A.5  | Combining resource controls                            | A-263  |

| Appendix E | 3    | MSC Firmware Data                                      |        |

| • •        | B.1  | Introduction                                           | B-266  |

|            | B.2  | Partitioning-control parameters                        |        |

|            | B.3  | Performance-monitoring parameters                      |        |

|            |      | Glossary                                               |        |

# **Preface**

This preface introduces the MPAM Extension Architecture Specification v1.0. It contains the following sections:

- About this book on page x.

- Using this book on page xi.

- Conventions on page xiii.

- Additional reading on page xiv.

- Feedback on page xv.

# About this book

This book is the Architecture Specification for the MPAM Extension Architecture Specification v1.0.

It specifies System registers and behaviors for generation of MPAM information in processing elements (PEs). It also specifies memory-mapped registers and standard types of resource control interfaces for Memory-System Components (MSCs). It also covers resource usage monitors for measuring usage by software.

Together, these facilities permit software both to observe memory-system usage and to allocate resources to software by running that software in a memory-system partition.

This document defines the MPAM Extension version 1.0. This MPAM extension is an optional extension to Armv8.2 and later versions. This document covers only the AArch64 Execution state. However, see *MPAM AArch32 interoperability* on page 6-66 for interoperation with AArch32.

This document primarily describes hardware architecture. As such, it does not usually include information on either the software needed to control these facilities or the ways to implement effective controls of the memory system using the parameters defined by this architecture. This document gives no guidance as to which of the optional features to implement at which of the MSCs.

# Intended audience

This document targets the following audience:

Hardware and software developers interested in the MPAM hardware architecture.

# Using this book

This book is organized into the following chapters:

Readers new to MPAM should first read Chapters 1 to 5.

Readers interested in MPAM generation behavior in the PE should read Chapters 6 and 7.

Readers interested in MPAM resource controls and memory-system component behaviors should read Chapters 8, 9, 11, 12, and Appendices A and B.

Readers interested in MPAM resource usage monitoring should read Chapters 10, 11, and 12.

Readers interested in pseudocode definition, refer to the "Arm® Architecture Reference Manual".

# Chapter 1 Introduction

Read this chapter for an introduction to the MPAM extension.

# Chapter 2 MPAM and Arm Memory-System Architecture

Read this chapter for a description of MPAM and Arm Memory-System Architecture.

## Chapter 3 ID Types, Properties, and Spaces

Read this chapter for a description of ID Types, Properties, and Spaces.

# Chapter 4 MSC Propagation of MPAM Information

Read this chapter for a description of MSC Propagation of MPAM Information.

# Chapter 5 System Model

Read this chapter for a description of the System model.

# Chapter 6 PE Generation of MPAM Information

Read this chapter for a description of PE Generation of MPAM Information.

# Chapter 7 System Registers

Read this chapter for a description of the System registers.

# Chapter 8 MPAM in MSCs

Read this chapter for a description of MPAM in MSCs.

# Chapter 9 Resource Partitioning Controls

Read this chapter for a description of Memory-System Partitioning.

# Chapter 10 Resource Monitors

Read this chapter for a description of Performance Monitoring Groups.

## Chapter 11 Memory-Mapped Registers

Read this chapter for a description of Memory-Mapped Registers.

# Chapter 12 Errors in MSCs

Read this chapter for a description of Errors in MSCs.

# Chapter 13 Armv8 Pseudocode

Read this chapter for the pseudocode definitions that describe various features of the MPAM Architecture.

# Appendix A Generic Resource Controls

Read this appendix for a description of Generic Resource Controls.

# Appendix B MSC Firmware Data

Read this appendix for a description of MSC Firmware Data.

| n | cc |  |

|---|----|--|

|   |    |  |

| ( | Read this glossary for definitions of some of the terms that are used in this manual. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning. |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | Note                                                                                                                                                                                                                         |

|   | Arm publishes a single glossary that relates to most Arm products, see the Arm Glossary                                                                                                                                      |

| ] | http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html. A definition in the                                                                                                                                    |

| , | glossary in this book might be more detailed than the corresponding definition in the Arm Glossary                                                                                                                           |

# **Conventions**

The following sections describe conventions that this book can use:

- Typographic conventions.

- Signals.

- Numbers.

- Pseudocode descriptions.

# Typographic conventions

The typographical conventions are:

*italic* Introduces special terminology, and denotes citations.

bold Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for a few terms that have specific technical meanings, and are included in the Glossary LINK.

Colored text Indicates a link. This can be:

- A URL, for example http://infocenter.arm.com.

- A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, *Pseudocode descriptions*.

- A link to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term.

# **Signals**

In general this specification does not define processor signals, but it does include some signal examples and recommendations.

The signal conventions are:

# Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

# **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

# Pseudocode descriptions

This book uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font, and is described in Appendix C *Pseudocode Definition*.

# **Additional reading**

This section lists relevant publications from Arm and third parties.

See the Infocenter http://infocenter.arm.com, for access to Arm documentation.

# **Arm publications**

This book contains information that is specific to this product. See the following documents for other relevant information:

- Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile (ARM DDI 0487)

- Armv8.1 Extensions (ARM DDI0557)

- Armv8.2 Extensions

- Armv8.3 Extensions (ARM-ECM-0454992)

- Armv8.4 Extensions (ARM-ECM-0629567)

- Arm CoreSight Architecture Specification v2.0 (ARM IHI029D)

# Other publications

The following books are referred to in this book, or provide more information:

"Heracles: Improving Resource Efficiency at Scale," David Lo, Liqun Cheng, Rama Govindaraju, Parthasarathy Ranganathan, Christos Kozyrakis, 42nd Annual International Symposium on Computer Architecture (ISCA), New York NY, ACM, 2015.

# **Feedback**

Arm welcomes feedback on its documentation.

# Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0598A.b.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

| Note                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader. |

| any document when viewed with any other 1 Dr. reader.                                                                                                           |

Preface Feedback

# Chapter 1 **Introduction**

This chapter contains the following sections:

- Overview on page 1-18.

- *Memory-system resource partitioning* on page 1-19.

- *Memory-system resource usage monitoring* on page 1-20.

- *Memory-system components* on page 1-21.

- *Implementation flexibility* on page 1-22.

- Example uses on page 1-23.

# 1.1 Overview

Some shared-memory computer systems run multiple applications or multiple virtual machines (VMs) concurrently. Such systems may have one or more of the following needs:

- Control the performance effects of misbehaving software on the performance of other software.

- Bound the performance impact on some software by any other software.

- Minimize the performance impact of some software on other software.

These scenarios are common in enterprise networking and server systems. The Memory System Resource Partitioning and Monitoring (MPAM) extension addresses these scenarios with two approaches that work together, under software control, to apportion the performance-giving resources of the memory system. The apportionment can be used to align the division of memory-system performance between software, to match higher-level goals for dividing the performance of the system between software environments.

These approaches are:

- Memory-system resource partitioning.

- Memory-system resource usage monitoring.

The main motivation of the extension is to make data centers less expensive. The extension can increase server utilization, so that fewer servers are needed for a given level of service. Utilization can be increased by controlling how much impact the best-effort jobs have on the tail latency of responses by web-facing jobs. See Heracles: Improving Resource Efficiency at Scale.

This MPAM Extension describes:

- A mechanism for attaching partition identifiers and a monitoring property, for executing software on an Arm

processing element (PE).

- Propagation of a Partition ID (PARTID) and Performance Monitoring Group (PMG) through the memory system.

- A framework for memory-system component controls that partition one or more of the performance resources of the component.

- Extension of the framework for MSCs to have performance monitoring that is sensitive to a combination of PARTID and PMG.

- Some implementation-independent, memory-mapped interfaces to memory-system component controls for performance resource controls most likely to be deployed in systems.

- Some implementation-independent memory-mapped interfaces to memory-system component resource monitoring that would likely be needed to monitor the partitioning of memory-system resources.

# 1.2 Memory-system resource partitioning

The performance of programs running on a computer system is affected by the memory-system performance, which is in part controlled by several resources in the memory system. In a memory system shared by multiple VMs, OSs, and applications, the resources available to one software environment may vary, depending on which other programs are also running. This is true because those other programs may consume more or less of an uncontrolled memory-system resource.

Memory-system resource partitioning provides controls on the limits and use of previously uncontrolled memory-system resources.

Shared, partitionable memory-system resources that can affect performance of a VM, OS, or application include:

- Shared caches, in which one application may displace the cached data of another application.

- Interconnect bandwidth, in which use by one application can interfere with use by another application due to contention for buffers, communication links, or other interconnect resources.

- Memory bandwidth, in which use by one application can interfere with the use by another application due to contention for DRAM bus bandwidth.

This list is not exhaustive. MPAM functionality can be extended through vendor and implementation-specific resource partitioning controls or resource-usage monitors.

Memory-system performance resource partitioning is performed by MPAM resource controls located within the MSCs. Each memory-system component may implement zero or more MPAM resource controls within that component.

An MPAM resource control uses the PARTID that is set for one or more software environments. A PARTID for the current software environment labels each memory system request. Each MPAM resource control has control settings for each PARTID. The PARTID in a request selects the control settings for that PARTID, which are then used to control the partitioning of the performance resources of that memory-system component.

# 1.3 Memory-system resource usage monitoring

Memory-system resource-usage monitoring measures memory-system resource usage. MSCs can have resource monitors. An MPAM monitor must be configured and enabled before it can be queried for resource-usage information. A monitor can be configured to be sensitive to a particular PARTID, or PARTID and PMG, and some monitors can be configured to certain subcategories of the resource (for example, the memory bandwidth used by writes that use a PARTID and PMG).

A monitor can measure resource usage or capacity usage, depending on the resource. For example, a cache can have monitors for cache storage that measure the usage of the cache by a PARTID and PMG.

Monitors can serve several purposes. A memory-system resource monitor might be used to find software environments to partition. Or, a monitor's reads might be used to tune the memory-system partitioning controls. A PMG value can be used to subdivide the software environments within a PARTID for finer-grained results, or to make measurements over prospective partitions.

# 1.4 Memory-system components

A Memory-System Component (MSC) is a function, unit, or design block in a memory system that can have partitionable resources. MSCs consist of all units that handle load or store requests issued by any MPAM master. These include cache memories, interconnects, Memory Management Units, memory channel controllers, queues, buffers, rate adaptors, and so on.

An MSC may be a part of another system component. For example, a PE may contain caches, which may contain MSCs

# 1.5 Implementation flexibility

Memory-system partitioning, monitoring capabilities, and certain implementation parameters must be discoverable by software, and they must be used by software to adapt to the system hardware. Discovery of MPAM memory-system component topology is expected to be by means of firmware data such as Device Tree or ACPI interface. MPAM controls and parameters of MSCs are discoverable in memory-mapped ID registers. Discovery of PE MPAM features and parameters is described in *Discovering MPAM* on page 6-55.

The width of memory-system partitioning and monitoring values communicated through the system can be sized to the needs of the system. The costs can thereby be adjusted to meet the market requirements.

This document defines standard interfaces to some resource partitioning and monitoring features of MSCs. It does so by defining ID registers that expose implementation parameters and options. It also defines configuration registers that allow standard programming of these features while giving substantial implementation flexibility. In addition, this document also defines a mechanism that permits IMPLEMENTATION DEFINED partitioning and monitoring features that may introduce partitioning or monitoring in new ways or of new resource types.

# 1.6 Example uses

This section is *informative*. It presents examples of partitioning uses that reduce memory-system interactions.

# 1.6.1 Separate systems combined

With faster processors, it is often less expensive to integrate into a single computer system the functions previously performed by two or more systems. If any of these previously separate systems was real-time or otherwise performance-sensitive, it may be necessary to isolate the performance of that function from others in the integrated system.

Memory system performance can be monitored, and the measured usage can guide optimization of system partitioning.

Partitioning is often statically determined by the system developer. Partitions may be given non-shared resource allocations to improve real-time predictability. The number of partitions required could be small, similar to the number of previously separate systems.

# 1.6.2 Foreground and background job optimization

When foreground and background jobs are run on the same system, the foreground job's response time should not be compromised, and the background job's throughput should be optimized. The performance of the foreground and background jobs can be monitored, and the resource allocations can be changed dynamically to track system loading while optimizing foreground response time and background throughput.

An example of this approach is proposed in *Heracles: Improving Resource Efficiency at Scale*. This paper describes a system that requires only two partitions, one for web-facing applications and another for best-effort applications. The Heracles approach measures the service-level objective of tail latency for web service and adjusts the division of resources between the two partitions. Resource-usage monitoring is also used to tune resource allocation for particular resources.

# 1.6.3 Service-level provisioning in multi-tenant VM servers

When a server runs multiple VMs for different users, it is necessary to prevent one VM from using more resource than it has paid for and thereby prevent other tenants from being able to use the resource they have paid for. MPAM partitions provide a means to regulate the memory-system resources used by a VM.

While there need only be a few service levels provisioned onto a server, each VM needs a separate PARTID so that resource-usage controls can be separately responsive to the resource demands of that VM.

Introduction

1.6 Example uses

This chapter contains the following sections:

• MPAM and Arm memory-system architecture on page 2-26

# 2.1 MPAM and Arm memory-system architecture

This section is normative.

MPAM partitioning of memory-system performance resources must not affect the correctness of any memory behavior specified in the *Arm Architecture Reference Manual*. The Arm v8 memory model, as specified in that manual, must be followed in all of its particulars, including requirements for observation, coherence, caching, order, atomicity, endianess, alignment, memory types, and any other requirements defined in the Arm ARM v8 memory model. Furthermore, these requirements must also be met:

- For single-PE and multiple-PE environments.

- For MPAM information that is the same as, or different from, multiple requests by a single requestor or by multiple requestors.

- For all MPAM memory-system component resource controls and configurations.

- When MPAM information stored with data accessed from caches is the same as, or different from, MPAM information in requests that access that data.

A Speculative access (either an instruction prefetch or an early data read) may be generated at any time, based on MPAM System register configuration that might change before the access would be architecturally executed. MPAM does not impose any limit on such speculation – neither a data dependency on the MPAMn\_ELx registers nor a control dependency on the System register synchronization, other than the limits on use of System register values in the *Arm Architecture Reference Manual*.

2-26

# Chapter 3 **ID Types, Properties, and Spaces**

This chapter contains the following sections:

- *Introduction* on page 3-28.

- *ID types and properties* on page 3-29.

- *PARTID spaces and properties* on page 3-30.

- Communication of MPAM information to MSCs on page 3-31.

- *MPAM\_NS* on page 3-32.

# 3.1 Introduction

This chapter is normative.

MPAM operation is based on the MPAM information that masters include with requests made to the memory system. This chapter defines the components of that MPAM information bundle, which consists of:

- PARTID

- PMG

- MPAM\_NS

# 3.2 ID types and properties

MPAM has a single ID type, the Partition ID (PARTID). The architectural maximum width of a PARTID field is 16 bits.

PARTIDs have a single property, the Performance Monitoring Group (PMG). The architectural maximum width of a PMG field is 8 bits.

# 3.3 PARTID spaces and properties

MPAM PARTIDs have up to four PARTID spaces:

- Secure physical PARTID space. This space is accessed when a PE is executing in the Secure state.

- Non-secure physical PARTID space. This space is accessed when a PE is executing in the Non-secure state.

- Non-secure virtual PARTID space. This space exists only when the virtualization option is implemented and enabled for the current EL, and only within a PE that is executing in the Non-secure state.

- Secure virtual PARTID space. This space exists only when the virtualization option is implemented and enabled for the current EL, and only within a PE that is executing in the Secure state.

Each PARTID space has a maximum PARTID set by the implementation of the device. The range of valid PARTIDs is 0 to the maximum PARTID, inclusive. The maximum values of a PARTID implemented by a PE and by different MSCs need not be the same. Software should avoid using PARTIDs that exceed the smallest maximum of any MSCs accessed, because the behavior of an MSC accessed with an out-of-range PARTID is not well-defined.

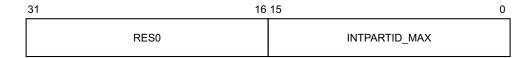

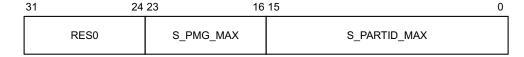

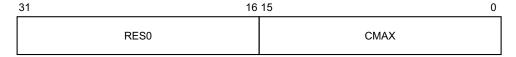

Each MSC has an MPAM identification register with which to discover the width of PARTID implemented. The maximum Non-secure PARTID supported by an MSC is indicated in its MPAMF\_IDR.PARTID\_MAX. The maximum secure PARTID supported by an MSC is indicated in its MPAMF\_SIDR.PARTID\_MAX. The maximum PARTID supported by a PE is indicated in MPAMIDR EL1.PARTID MAX.

## 3.3.1 Default PARTID

Each MPAM PARTID space has a default value, which is PARTID 0 in that PARTID space.

The default physical PARTID must be generated when MPAM PARTID generation is disabled by MPAMEN == 0. This PARTID space is selected according to the current Security state; it is either the secure physical PARTID space or the Non-secure physical PARTID space.

MPAM PARTID generation is permitted to produce the default PARTID when the generation encounters an error.

# 3.3.2 Default PMG

The default PMG must be generated when MPAMEN == 0.

It is CONSTRAINED UNPREDICTABLE whether MPAM PMG generation produces the PMG value from the MPAMn ELx register field or from the default PMG in either of two cases:

- When the PMG generation encounters an error, such as out-of-range PMG.

- When a default PARTID is generated due to a PARTID generation error.

In other cases, when MPAMEN == 1, the PMG must be the PMG value from the MPAMn\_ELx register field.

The PARTID and PMG error conditions in a PE are described in *MPAM errors and default ID generation* on page 6-70.

System designers can also choose to output the default IDs on requests generated by masters that do not support MPAM.

# 3.4 Communication of MPAM information to MSCs

The representation of the MPAM information bundle on system interfaces is IMPLEMENTATION DEFINED.

If the system implements security, interfaces must be able to communicate a PARTID that is in either the Secure or the Non-secure PARTID space with each memory-system request.

# 3.5 MPAM\_NS

MPAM\_NS indicates the MPAM security space of the PARTID in the MPAM information bundle. In a PE, it is not stored in a register; it comes from the Security state. The pseudocode function, IsSecure(), computes the current Security state. See Table 6-5 on page 6-60 for combinations of MPAM\_NS and NS bits.

# Chapter 4 **MSC Propagation of MPAM Information**

This chapter contains the following sections:

- *Introduction* on page 4-34

- Requesting master components on page 4-35

- *Terminating slave components* on page 4-36

- Intermediate slave-master components on page 4-37

- Request buffering on page 4-38

- *Cache memory* on page 4-39

# 4.1 Introduction

This section is *normative*.

MSC propagation of MPAM information includes the storage and transmission of:

- PARTID (PARTID spaces and properties on page 3-30).

- PMG (Chapter 10 Resource Monitors).

- MPAM\_NS (MPAM\_NS on page 3-32).

An MSC must implement at least one of the following categories of MPAM propagation behavior, and it might implement several of these behaviors.

# 4.2 Requesting master components

Requesting masters must label all requests to downstream MSCs with MPAM information.

A requesting master must have a device-appropriate means of setting the MPAM information in the request:

- The PE must use the scheme described in Chapter 6 PE Generation of MPAM Information.

- This architecture does not specify a mechanism for determining the MPAM information for requests from a non-PE master. Arm recommends that non-PE masters needing to use MPAM facilities specify a mechanism for determining the PARTID, PMG, and MPAM NS of requests.

- SMMU architecture version 3.2 specifies MPAM information generation on memory system accesses translated by the SMMU and accesses originated by the SMMU to its tables in memory.

- GIC architecture version v3/v4 specifies MPAM information generation on memory system accesses

originated by the GIC to its tables in memory.

If a requesting master does not support MPAM, the system must arrange to supply a value for MPAM information required for the interface. If no other mechanism is available, these values must be driven to a default value (in the Non-secure physical PARTID space or in the secure physical PARTID space).

See also Requesters without MPAM support on page 5-47.

# 4.3 Terminating slave components

A terminating slave receives requests from upstream masters but does not communicate the requests to a downstream slave. Instead, the terminating slave services the requests. A terminating slave does not forward MPAM information from a request. A terminating MSC is the edge of MPAM in a system.

A DRAM controller is a terminating slave, even though it communicates with DRAM devices to complete the request. The DRAM devices do not support MPAM communication, so MPAM information is not forwarded to them. This might also happen elsewhere in a system where there is no downstream slave that has MPAM support.

# 4.4 Intermediate slave-master components

Intermediate MSCs have both one or more slave interfaces and one or more master interfaces.

An intermediate component can route a request from an upstream master to one of its downstream master ports. When routing a request from upstream to downstream, the intermediate component passes the MPAM information unaltered to the downstream master port.

An intermediate component might terminate a request from upstream locally without propagating the request to a downstream master port if the request is serviced locally.

# 4.5 Request buffering

Requests can be buffered in any MSC. A request that is buffered must retain its MPAM information.

# 4.6 Cache memory

A cache line must store the MPAM information of the request that caused its allocation. See *Cache behavior* on page 5-50 for requirements on cache memory behavior.

MSC Propagation of MPAM Information 4.6 Cache memory

# Chapter 5 System Model

This chapter contains the following sections:

- *Introduction* on page 5-42.

- System-level field widths on page 5-44.

- *PE behavior* on page 5-45.

- Other requesters with MPAM on page 5-46.

- Requesters without MPAM support on page 5-47.

- *Model of a resource partitioning control* on page 5-48.

- *Interconnect behavior* on page 5-49.

- Cache behavior on page 5-50.

- *Memory-channel controller behavior* on page 5-52.

#### 5.1 Introduction

This section describes a model of system behavior that can support the MPAM features. In particular, the behavior of masters, interconnects, caches, and memory controllers is described.

In this system model, a request:

- Begins at a requester (master), such as a PE, I/O master, DMA controller, or graphics processor:

- MPAM information (PARTID, PMG, and MPAM NS) is transported with every request.

- Traverses non-cache nodes that might be a transport component (such as an interconnect), a bus resizer, or an asynchronous bridge.

- Might reach an MSC that contains or is a cache:

- Caches sometimes generate a response (cache hit) and sometimes pass the request on (cache miss).

- Caches could also allocate entries based on the request.

- Caches must store the MPAM PARTID, PMG, and MPAM NS associated with an allocation:

- Needed for cache-storage usage monitoring.

- Used during eviction to another cache.

- Cache eviction must attach MPAM fields to the eviction request. The source for MPAM information on an eviction may depend on whether the eviction is to memory or to another cache. See *Eviction* on page 5-50 and *Optional cache behaviors* on page 5-51.

- Might proceed from a cache to a transport component, and to other caches or a memory-channel controller.

- Might result in a memory controller or other terminating slave device responding to a request it receives.

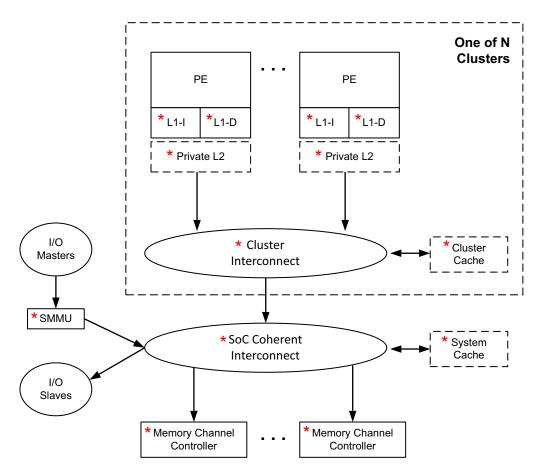

Figure 5-1 on page 5-43 shows a simplified system model for the downstream flow, in the direction of requests from masters to slaves. In this figure, all objects implement an MSC except the PEs, I/O Masters, and I/O Slaves. PEs generate MPAM information from MPAM state in their System registers. I/O masters typically get their MPAM information when their requests pass through an SMMU.

The interconnects in Figure 5-1 on page 5-43 can represent bus, crossbar, packet, or other interconnect technologies.

An MSC responds to the MPAM information that arrives as part of a request. If the MSC implements partitioning controls, those controls find partitioning settings by the PARTID in the MPAM information of the request, and they use those settings to control the allocation of a controlled resource.

For caches, a cache line (which has an address) is always associated with the PARTID that allocated the line – or the PARTID that allocated the line into an inner cache that has now been evicted to the current cache. The inner cache PARTID must be preserved when the line is evicted to an outer cache.

An address may be accessed by multiple PARTIDs.

A cache must store the PARTIDs of the lines it contains, so that it can measure and control the cache lines used by a PARTID, and so that it can provide the PARTID to downstream MSCs when the line is evicted.

<sup>\*</sup> Memory-System Component (MSC) that might contain MPAM resource controls

Figure 5-1 MPAM system model (downstream flow)

# 5.2 System-level field widths

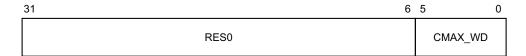

Arm recommends that a system be configured to support a common size for the PARTID and PMG fields of MPAM. Mismatched sizes make it difficult for software to use anything but the smallest of implemented widths.

#### 5.3 PE behavior

Processing elements (PEs) issue memory-system requests. PEs must implement the MPAMn\_ELx registers (page 7-71) and their behaviors to generate the PARTID and PMG fields of memory-system requests.

See Chapter 6 PE Generation of MPAM Information.

#### 5.3.1 PARTID generation

When a PE generates a memory-system request, it must label the request with the PARTID from the MPAMn\_ELx register for the current Exception level. MPAM NS must be set to the current execution Security state.

If the MPAM Virtualization Extension is implemented and enabled for the current Exception level, the PARTID from the MPAMn\_ELx register must be mapped through the virtual partition mapping registers (*System register descriptions* on page 7-75) to produce a physical PARTID.

#### 5.3.2 Information flow

When a PE with MPAM support issues a request to the rest of the system, it labels those commands with the PARTID and PMG supplied by software in the MPAMn\_ELx register in effect (and if MPAM1\_EL1 or MPAM0\_EL1 with virtual PARTID mapping is enabled, with the virtual PARTID mapped to a physical PARTID).

In addition to the PARTID and PMG, the request must also have the MPAM\_NS bit to indicate whether the PARTID is to be interpreted as in the Secure PARTID space or the Non-secure PARTID space.

#### 5.3.3 Resource partitioning

If a PE contains internal memory-system partitioning controls, it must have memory-mapped registers (Chapter 9 *Resource Partitioning Controls*) to identify and configure those features.

The PE could include caches. The included caches could implement memory-system partitioning, such as cache-capacity partitioning controls. The cache behavior in *Cache behavior* on page 5-50 must apply to included cache functionality.

An MSC within a PE could have priority partitioning. This generates a priority or QoS value for the downstream traffic from that MSC, effectively giving priority or QoS values tied to the software environment that generated that traffic.

#### 5.3.4 Resource-usage monitoring

A PE may have internal resource monitors that can measure the use by a PARTID and PMG of an MPAM resource (Chapter 10 Resource Monitors).

If a PE contains such features, they must have memory-mapped registers (Chapter 10 Resource Monitors) to identify and configure those features.

# 5.4 Other requesters with MPAM

Other requesters that support MPAM, such as a DMA controller, must issue requests to the system that have the MPAM fields. Non-PE masters can have schemes different from those implemented in PEs for associating MPAM information with requests. These other schemes are not documented herein.

# 5.5 Requesters without MPAM support

A requester that does not implement support for MPAM must use a system-specific means to provide MPAM information to MSCs that support MPAM.

Some examples of requester devices that might not implement support for MPAM include:

- Legacy DMA controller.

- Third-party peripheral IP.

- CoreSight DMA components, such as ETR.

- Older devices which cannot be economically upgraded to include MPAM support.

Some options for adding MPAM information to requests include:

- The MPAM information could be tied off to the default PARTID and PMG values (*Default PARTID* on page 3-30) and MPAM NS set as appropriate for the device.

- The MPAM information could be provided by a System Memory Management Unit (SMMU) that supports

adding MPAM information according to the stream and substream of the request.

- The MPAM information could be in added by a bus bridge or other system component that handles the requester's memory-system traffic.

Other implementations are permitted.

## 5.6 Model of a resource partitioning control

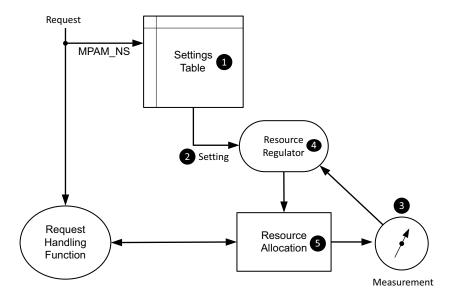

A general model of a resource partitioning controller within an MSC is shown in Figure 5-2. This model shows a resource partitioning model that measures resource usage by the partition and that controls resource usage by comparing the measured usage with the control settings for that partition.

Figure 5-2 Model of MPAM resource partitioning controller

In Figure 5-2, a request arrives from an upstream master to an MSC that implements MPAM partitioning control. The request is handled as follows:

- The PARTID and MPAM\_NS values of the incoming request are used to index into a Settings Table of partition-control settings. (There is one settings table per implemented resource control.)

- The table entry for that PARTID specifies its partition-control setting, which is passed to a Resource Regulator.

- 3. Conformance of the resource with the setting may require Measurement of how the resource is being used by the partition.

- The Measurement feeds back to the Resource Regulator, where it is compared with the Setting and used to make a decision about Resource Allocation.

In Figure 5-2, items 1, 2, 3, and 4 are added to the original memory system when MPAM is implemented, although in some MSCs there may be sufficient measurement hardware already in place. Item 1, the Settings Table, is the heart of an MPAM MSC.

All of the above is separate from normal request-handling by the MSC.

When doing cache-way partitioning, a significant part of the above mechanism can be eliminated. It is not necessary to make measurements. The cache ways that can be allocated into are known.

The upside of cache-way partitioning is that it is simple and cheap. The downside is that caches do not have many ways, so fine-grained control is not possible. In addition, resources can be strained if one or more ways are allocated to only one partition, without sharing.

### 5.7 Interconnect behavior

Interconnects connect requesters to targets, and they must transport MPAM information fields from requester to target.

Interconnects may support the MPAM control features, such as priority partitioning. Support for MPAM is discoverable in ID registers and firmware data.

Some interconnect devices may include cache functionality, in which case the cache behavior in *Cache behavior* on page 5-50 applies.

#### 5.8 Cache behavior

A cache must associate the MPAM information of the request that allocated a cache line with any data stored in the cache line. This stored MPAM information is a property of the data.

The term "data" in this section is intended to indicate the content stored in the cache. It is not intended to indicate any restriction on the applicability of this section based on the purpose of the cache or of its content.

The MPAM information on a request to the cache from an upstream master is used for the following purposes:

- Source for the MPAM information associated with data when the data is allocated into the cache and is stored

in association with the data while the data resides in the cache.

- Optionally updating the stored MPAM information of the cached data on a store hit (*Write hits may update the MPAM information of a cache line* on page 5-51).

- Providing MPAM information for downstream requests to fulfill the incoming request such as a read from downstream on a cache miss that fetches data into the cache.

- Optionally (*Eviction*), providing MPAM information for downstream requests generated by evict or clean operations when this cache is the last level of cache upstream of main memory.

- Selecting settings of partitioning controls implemented in the cache.

- Tracking resource usage needed by partitions for a control implementation.

- Performing accounting, if necessary, to track resource usage for resource usage monitors, if implemented.

- Triggering and filtering resource monitors, if implemented, for events triggered by requests from upstream masters.

The stored MPAM information is used by MPAM for the following purposes:

- Providing the MPAM information for downstream requests generated by evict or clean operations, when this

cache is not the last level of cache.

- Optionally (*Eviction*) providing MPAM information for downstream requests generated by evict or clean

operations, when this cache is the last level of cache.

- Triggering and filtering resource monitors by MPAM PARTID and PMG, if implemented for events triggered

by internal and downstream requests.

- Tracking resource usage by partitions, as needed by a partitioning control implementation.

#### 5.8.1 Eviction

When a cache line is evicted to another cache, the evicting cache must produce the MPAM information that was used in the request that originally allocated the cache line.

A system cache (last-level cache) may produce the MPAM information of the request that caused the eviction in its request to a memory-channel controller, or the cache may produce the stored MPAM information associated with the evicted line.

#### 5.8.2 Cache partitioning

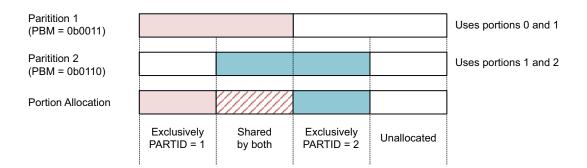

A cache may optionally implement cache-partitioning resource controls, such as a cache-portion partitioning control.

The cache-portion partitioning control (*Cache-portion partitioning* on page 9-130) was conceived for use on large, multi-way associative caches, but cache-portion partitioning can be implemented on caches that are not set-associative. For example, a single entry or group of entries may be a cache portion in a fully-associative cache.

The cache maximum-capacity partitioning control (*Cache maximum-capacity partitioning* on page 9-131) was conceived for use on caches that do not support cache-portion partitioning or that have insufficient portions to meet the needs of the planned use.

Both types of cache partitioning may be used together in a cache memory component. This may be useful, for example, when the cache has insufficient portions to give adequate control for a planned use.

#### 5.8.3 Resource monitoring

A cache may implement cache-storage usage monitoring (*Cache-storage usage monitor* on page 10-148). For a monitored PARTID, the monitor gives the total cache storage used by the PARTID.

#### 5.8.4 Optional cache behaviors

The following cache behaviors are permitted but not required.

#### Write hits may update the MPAM information of a cache line

On a write hit to cached data that has different request MPAM information than the stored MPAM information associated with the data, the stored MPAM information is permitted to be updated to the request MPAM information.

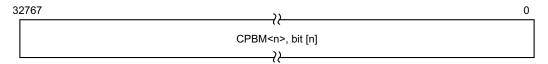

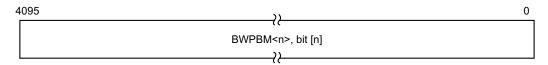

It is possible that a change in the PART\_ID of the data (without moving the data) leaves the data in a portion of the cache that the new PARTID does not have permission to allocate. This can occur if the Cache Portion Bit Map (CPBM) bit for that portion is not set in the CPBM for the new PARTID. The optional behavior in this subsection does not change the location within the cache, even if the new partition for the data does not have a CPBM bit that allows allocation in this portion of the cache. Updating the location within the cache is a second optional behavior that is covered in the next subsection.

# Write hits that update the PARTID of a cache line may move that line to a different portion

A write hit to cached data is permitted to change the portion of the cache capacity allocated to the data, if (i) the PARTID of the cache data is updated due to the write hit, and (ii) the portion of capacity where the data currently resides is not in the new PARTID's cache portion bitmap.

# 5.9 Memory-channel controller behavior

This section is informative.

A memory-channel controller may implement MPAM features. Some of the features that may be helpful in a memory-channel controller are:

- Memory-bandwidth minimum and maximum partitioning (Memory-bandwidth minimum and maximum partitioning on page 9-133).

- Memory-bandwidth portion partitioning (Memory-bandwidth portion partitioning on page 9-133).

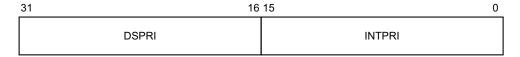

- Priority partitioning (internal) (*Priority partitioning* on page 9-136).

- Memory-bandwidth usage monitors (*Memory-bandwidth usage monitors* on page 10-147).

# Chapter 6 **PE Generation of MPAM Information**

This chapter contains the following sections:

- *Introduction* on page 6-54.

- *Discovering MPAM* on page 6-55.

- *MPAM System registers* on page 6-56.

- Instruction, data, translation table walk, and other accesses on page 6-59.

- Security on page 6-60.

- *PARTID virtualization* on page 6-61.

- MPAM AArch32 interoperability on page 6-66.

- Support for nested virtualization on page 6-67.

- MPAM errors and default ID generation on page 6-70.

#### 6.1 Introduction

This introduction is informative. Other sections and subsections are normative unless marked as informative.

In a PE, the generation of PARTID, PMG, and MPAM\_NS labels for memory-system requests is controlled by software running at the current EL or higher. The set of MPAM information for:

- An application running at EL0 is controlled from EL1.

- An OS or guest OS running at EL1 is controlled from EL1 or EL2, according to settings controlled at EL2 and EL3

- A hypervisor or host OS running at EL2 is controlled from EL2 or EL3, according to settings controlled at EL3

- A guest hypervisor running at EL1 is controlled from EL1 or EL2, according to settings controlled at EL2 and EL3.

- Secure instances of all of the above.

- Monitor software running at EL3 is controlled only from EL3.

# 6.2 Discovering MPAM

This section is normative.

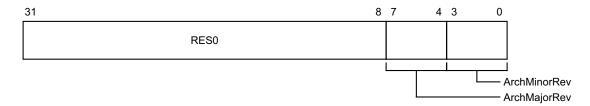

The presence of MPAM functionality in a PE is indicated by the ID\_AA64PFR0\_EL1[43:40] field (Table 6-1) being non-zero. The version of the MPAM Extension architecture is indicated in this field.

Table 6-1 MPAM ID\_AA64PFR0\_EL1[43:40] values

| ID_AA64PFR0_EL1[43:40] | MPAM Extension architecture version                           |  |

|------------------------|---------------------------------------------------------------|--|

| 0x0                    | MPAM Extension not present.                                   |  |

| 0x1                    | MPAM Extension is present with MPAM extension architecture 1. |  |

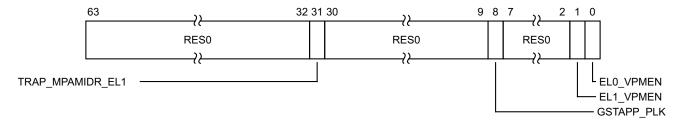

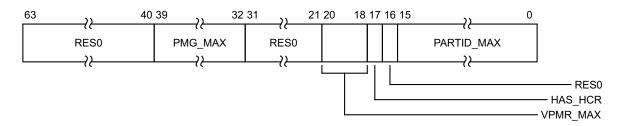

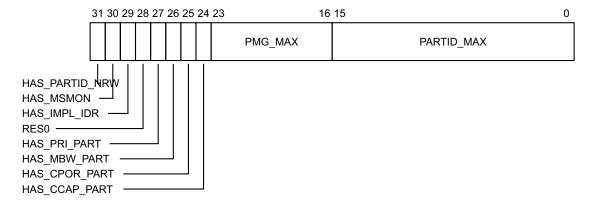

If the MPAM Extension is present, MPAMIDR\_EL1 specifies implementation properties, such as the largest PARTID usable and whether the virtualization features are supported.

# 6.3 MPAM System registers

This section is normative.

The MPAM PARTIDs are assigned to software by hypervisor and/or kernel software, and a PARTID, PMG, and MPAM\_NS are associated with all memory-system requests originated by the PE.

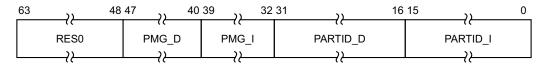

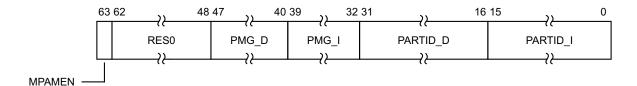

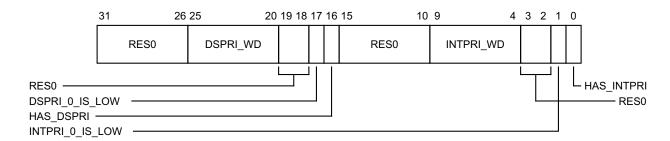

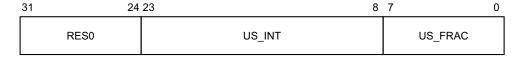

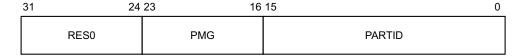

The MPAMn\_ELx System registers contain fields for two PARTIDs and the PMG property for each as shown in Table 6-2.

Table 6-2 MPAM System register PARTID and PMG fields

| Field Name | Description                           |  |

|------------|---------------------------------------|--|

| PARTID_D   | PARTID used for data requests.        |  |

| PARTID_I   | PARTID used for instruction requests. |  |

| PMG_D      | PMG property for PARTID_D.            |  |

| PMG_I      | PMG property for PARTID_I.            |  |

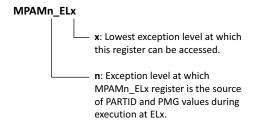

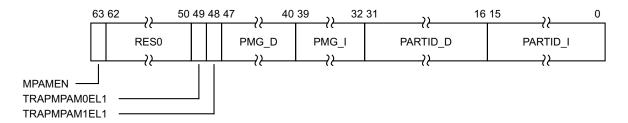

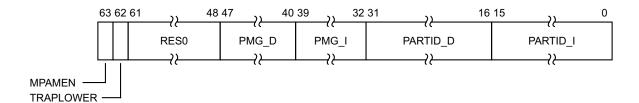

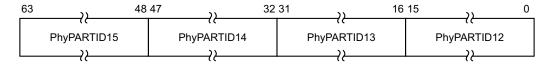

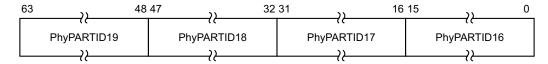

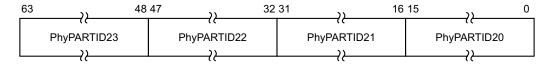

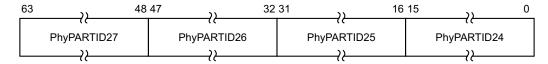

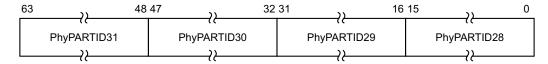

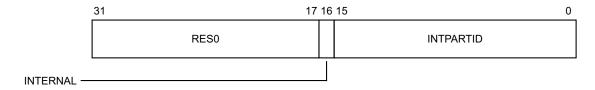

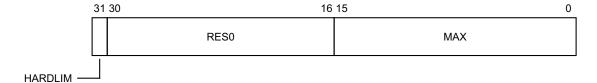

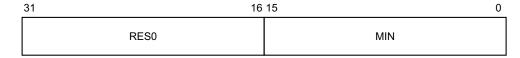

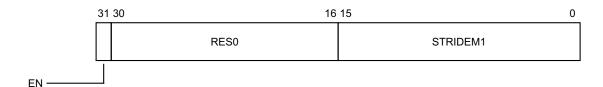

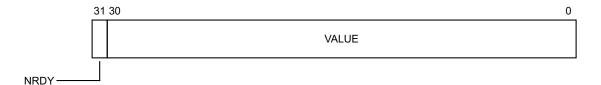

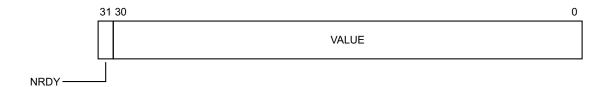

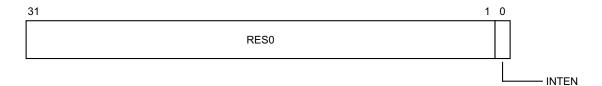

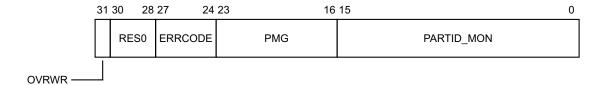

The MPAMn\_ELx System registers use the register-name syntax shown in Figure 6-1. These registers control MPAM PARTID and PMG, as shown in Table 6-3 on page 6-57 and *Summary of system registers* on page 7-74 and *System register descriptions* on page 7-75.

Figure 6-1 MPAM System register name syntax

Table 6-3 shows the PE MPAM System registers. The table does not include the following System registers: MPAMIDR EL1, MPAMVPMn EL2, MPAMVPMV EL2, MPAMHCR EL2.

Table 6-3 PE MPAM System registers

| System register | Controlled From   | Supplies PARTID and PMG when Executing In | Notes                                                                                                                                                                                                                                              |

|-----------------|-------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPAM0_EL1       | EL3<br>EL2<br>EL1 | EL0 (Applications)                        | With the virtualization option and MPAMHCR_EL2.EL0_VPMEN == 1, MPAM0_EL1 PARTIDs can be treated as virtual and mapped to a physical PARTID with virtualization option.                                                                             |

|                 |                   |                                           | Overridden by MPAM1_EL1 when MPAMHCR_EL2.GSTAPP_PLK is set.                                                                                                                                                                                        |

|                 |                   |                                           | MPAM0_EL1 may be controlled from only EL3 if MPAM3_EL3.TRAPLOWER == 1, from only EL2 or EL3 if MPAM3_EL3.TRAPLOWER == 0 and MPAMHCR_EL2.TRAPMPAM0EL1 == 1 or from EL1, EL2 or EL3 if MPAM3_EL3.TRAPLOWER == 0 and MPAMHCR_EL2.TRAPMPAM0EL1 == 0.   |

| MPAM1_EL1       | EL3               | EL1                                       | Overrides MPAM0_EL1 when                                                                                                                                                                                                                           |

|                 | EL2               | (Guest OS)                                | MPAMHCR_EL2.GSTAPP_PLK is set.                                                                                                                                                                                                                     |

|                 | EL1               |                                           | With the virtualization option and MPAMHCR_EL2.EL1_VPMEN == 1, MPAM1_EL1 PARTIDs are treated as virtual and mapped to a physical PARTID.                                                                                                           |

|                 |                   |                                           | MPAM1_EL1 may be controlled only from EL3 if MPAM3_EL3.TRAPLOWER == 1, only from EL2 or EL3 if MPAM3_EL3.TRAPLOWER == 0 and MPAMHCR_EL2.TRAPMPAM1EL1 == 1, or from EL1, EL2 or EL3 if MPAM3_EL3.TRAPLOWER == 0 and MPAMHCR_EL2.TRAPMPAM1_EL1 == 0. |

|                 |                   |                                           | When HCR_EL2.E2H == 1, accesses to MPAM1_EL1 through the MSR and MRS instructions are aliased to access MPAM2_EL2 instead.                                                                                                                         |

| MPAM2_EL2       | EL3               | EL2                                       | MPAM2_EL2 is controlled only from EL3 if                                                                                                                                                                                                           |

|                 | EL2               | (Hypervisor or host OS)                   | MPAM3_EL3.TRAPLOWER $\Longrightarrow$ 1, or from EL2 or EL3 if MPAM3_EL3.TRAPLOWER $\Longrightarrow$ 0.                                                                                                                                            |

| MPAM3_EL3       | EL3               | EL3                                       | MPAM3_EL3 is controlled only from EL3.                                                                                                                                                                                                             |

|                 |                   | (Monitor)                                 |                                                                                                                                                                                                                                                    |

| MPAM1_EL12      | EL2               | EL1                                       | Alias to MPAM1_EL1 for type 2 hypervisor host executing with HCR_EL2.E2H == 1.                                                                                                                                                                     |

Table 6-4 on page 6-58 shows the selection of MPAMn\_ELx System register for MPAM generation. All of the fields named are in MPAMHCR\_EL2:

- GSTAPP PLK is MPAMHCR EL2.GSTAPP PLK.

- EL0\_VPMEN is MPAMHCR\_EL2.EL0\_VPMEN.

- EL1\_VPMEN is MPAMHCR\_EL2.EL1\_VPMEN.

Table 6-4 Selection of MPAMn\_ELx System register for MPAM generation

| When current EL is:      | Use PARTID and PMG fields from | Perform MPAM virtual PARTID mapping |

|--------------------------|--------------------------------|-------------------------------------|

| EL0 with GSTAPP_PLK == 0 | MPAM0_EL1                      | If $EL0_VPMEN == 1$                 |

| EL0 with GSTAPP_PLK == 1 | MPAM1_EL1                      | If EL1_VPMEN == 1                   |

| EL1                      | MPAM1_EL1                      | If EL1_VPMEN == 1                   |

| EL2                      | MPAM2_EL2                      | Never                               |

| EL3                      | MPAM3_EL3                      | Never                               |

#### 6.4 Instruction, data, translation table walk, and other accesses

When a PE generates a memory-system request for an instruction access, the PARTID\_I field of an MPAMn\_ELx register is used, as shown in Table 6-4 on page 6-58. All translation table walk accesses for instructions use the same PARTID\_I field that their instruction accesses use.

When a PE generates a memory-system request for a data access, the PARTID\_D field of an MPAMn\_ELx register is used, as shown in Table 6-4 on page 6-58. All translation table walk accesses for data access use the same PARTID\_D field that their data accesses use.

PARTID\_D and PARTID\_I fields of an MPAMn\_ELx register may be set by software to the same or different PARTIDs. If PARTID\_D is used for an access, PMG\_D from the same register must also be used. If PARTID\_I is used for an access, PMG\_I from the same register must also be used.

#### 6.4.1 Load unprivileged and store unprivileged instructions

When executed at EL1 or at EL2 with EL2 Host (E2H), load unprivileged and store unprivileged instructions perform an access using permission-checking for an unprivileged access. These instructions do not change the MPAM labeling of the resulting memory-system requests from the labels that would be generated by other load or store instructions.

#### 6.4.2 Accesses by enhanced support for nested virtualization

The Armv8.4 [4] enhanced support for nested virtualization turns MRS and MSR instructions to certain EL2 registers from EL1 into accesses to a data structure in EL2 memory. As such, these accesses generate PARTID and PMG using MPAM2 EL2.PARTID D and MPAM2 EL2.PMG D, respectively.

See Support for nested virtualization on page 6-67.

#### 6.4.3 Accesses by statistical profiling extension

The Armv8.2 introduced the Statistical Profiling Extension (SPE). A PE with SPE can be configured to record statistically sampled events into a profiling buffer in memory. The buffer is accessed through the owning Exception level's translation regime.

MPAM PARTID, PMG, and MPAM\_NS for SPE writes to the profiling buffer must use the SPE's owning Exception level MPAM data access values.

For example, if the owning Exception level is EL2, the profiling buffer writes must be performed with MPAM2\_EL2.PARTID\_D, MPAM2\_EL2.PMG\_D, and MPAM\_NS reflecting the Security state of the owning Exception level.

## 6.5 Security

MPAM behavior in the PE and in MSCs is affected by the Security state. While the address spaces for Secure and Non-secure memory-system accesses are distinct, the memory-system resources are potentially shared in an implementation. For higher security, running Secure software with segregated resources can reduce the chances for side-channel attacks.

The generation of PARTID and PMG for a memory-system request is exactly the same at a Secure ELx as at a Non-secure ELx, for the same x. The difference is that requests at a Secure ELx are qualified with MPAM\_NS to indicate Secure or Non-secure PARTID space.

MPAM security behavior in MSCs is covered in Security in MSCs on page 8-120.

#### 6.5.1 Secure PARTID Space

In a PE, generation of Secure and Non-secure PARTIDs are governed by the following Secure MPAM PARTID space rules, described in *PARTID spaces and properties* on page 3-30:

- Secure PARTIDs are communicated with MPAM NS == 0.

- Non-secure PARTIDs are communicated with MPAM NS == 1.

- MPAM NS == 0 if the current Security state is Secure.

In Secure execution, the sourcing of PARTID and PMG in a PE are as described in this specification for Non-secure execution. The PARTID and PMG generation uses MPAMn\_ELx to source the labels for the request when executing at Exception level ELn. Non-secure and Secure PARTID generation is the same, including virtual-to-physical PARTID translation, if secure EL2 is present and enabled, and the MPAM virtualization feature is present and enabled for the MPAM0\_EL1 or MPAM1\_EL1 register used.

See also PARTID virtualization on page 6-61.

#### 6.5.2 Non-secure MPAM PARTID space

Non-secure MPAM PARTIDs are communicated with MPAM NS == 1.

Non-secure and Secure PARTID generation is the same, including virtual PARTID translation to physical PARTID if EL2 is present, the MPAM virtualization feature (MPAMIDR\_EL1.HAS\_HCR) is present, and virtual partition mapping is enabled for the MPAM0\_EL1 or MPAM1\_EL1 register used.

#### 6.5.3 Indication of Secure MPAM PARTID spaces

Secure MPAM PARTIDs are communicated with MPAM NS == 0.

MPAM\_NS is distinct from the NS signal, which indicates the accessed address space is Non-secure or Secure. Table 6-5 shows the meaning of combinations of MPAM\_NS and NS.

Table 6-5 Combinations of MPAM\_NS and NS

| MPAM_NS | NS | Meaning                                                                                                                                                                                                                                 |

|---------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0  | Secure. A Secure PARTID (from Secure Execution state) used with access to a secure location.                                                                                                                                            |

| 0       | 1  | Cross-state. A Secure PARTID (from Secure Execution state) used with access to a Non-secure location.                                                                                                                                   |

| 1       | 0  | Non-secure PARTID (from Non-secure Execution state) used with access to Secure location. This is illegal because the MPAM_NS == 1 implies a Non-secure Execution state, which must never access a location in the Secure address space. |

| 1       | 1  | Non-secure PARTID (from Non-secure Execution state) used with access to a Non-secure location.                                                                                                                                          |

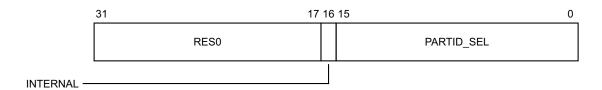

#### 6.6 PARTID virtualization

This introduction to MPAM virtualization support is informative, but subsections are individually marked as *normative* or *informative*.

The PARTID virtualization features described in this section are only available in a Security state in which all of the following conditions are met:

- EL2 is implemented and enabled in the Security state. See also *Unimplemented exception levels* on page 7-114.

- MPAM virtualization is supported, as indicated by MPAMIDR EL1.HAS HCR == 1.

The hardware and software involved in supporting MPAM virtualization includes:

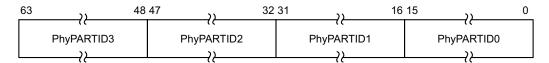

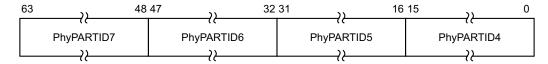

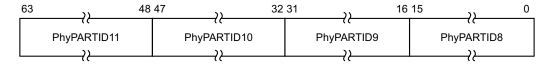

- Accesses made from EL1 to the MPAMIDR\_EL1 register are trapped to EL2 under control of the MPAMHCR\_EL2.TRAP\_MPAMIDR\_EL1 bit. This is done so that the hypervisor can emulate an MPAMIDR\_EL1 access and present an altered view of the register to the guest OS running at EL1. This altered view shows that the PARTID\_MAX field is a maximum that is equal to the largest virtual PARTID that the hypervisor has set up for the guest OS to use.

- Guest accesses to MPAM MSC control interfaces page-fault in the stage-2 page tables, thereby trapping to EL2 so that the virtual PARTID used can be access-controlled and mapped to the correct physical PARTID by the hypervisor. The hypervisor can give IPA mappings to an MSC's MPAM feature page that fault at stage 2 to produce this behavior.

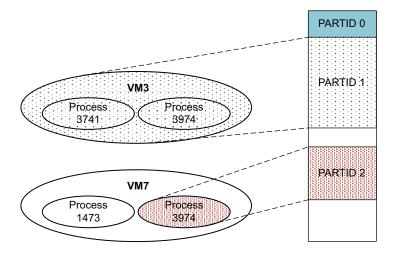

- Mapping of guest OS-assigned virtual PARTID values into the physical PARTID space when running guest applications at EL0 and the guest OS at EL1.

- Optionally, an invalid virtual PARTID (that is, one in which the valid bit, MPAMVPMV\_EL2, is 0) can cause

a default virtual PARTID to be used. See *PARTID space on error* on page 6-70.

- Support for type-2 hypervisors (for example, kvm) with the HCR\_EL2.E2H bit set when running the host OS in EL2 with hypervisor functionality. See Support for type-2 hypervisors on page 6-62.

These functions work together to give a guest OS the ability to control its virtual partitions and not trap to the hypervisor when context-switching between applications.

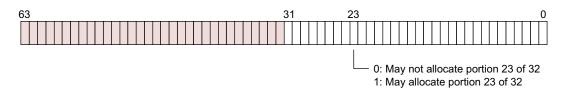

#### 6.6.1 MPAM virtual ID spaces

This section is normative.

MPAM virtual ID spaces only exist if the MPAM virtualization option is implemented, as indicated in MPAMIDR EL1.HAS HCR.