ARM<sup>®</sup> Reliability, Availability, and Serviceability (RAS) Specification ARMv8, for the ARMv8-A architecture profile

> Copyright © 2017 ARM Limited or its affiliates. All rights reserved. Document number: DDI 0587B.a

## ARM Reliability, Availability, and Serviceability (RAS) Specification

Copyright © 2017 ARM Limited or its affiliates. All rights Reserved.

#### **Release information**

The following changes have been made to this document.

| Date           | Issue | Confidentiality  | Change              |

|----------------|-------|------------------|---------------------|

| March 2017     | А     | Non-Confidential | First issue         |

| September 2017 | В     | Non-Confidential | EAC Release         |

| December 2017  | B.a   | Non-Confidential | Updated EAC Release |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names

mentioned in this document may be the trademarks of their respective owners. You must follow the Arm's trademark usage guidelines

http://www.arm.com/company/policies/trademarks.

Copyright © 2017 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

In this document, where the term ARM is used to refer to the company it means "Arm or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

### Web Address

http://www.arm.com

# Contents

| Pre | face  | •••••      |                                                                   | 7  |

|-----|-------|------------|-------------------------------------------------------------------|----|

|     | Refe  | rences     |                                                                   | 7  |

|     |       |            |                                                                   |    |

|     |       |            |                                                                   |    |

| 1   | Intro |            | 1                                                                 |    |

|     | 1.1   | <b>~ 1</b> | of errors                                                         |    |

|     | 1.2   | Techni     | iques for improving reliability, availability, and serviceability |    |

|     |       | 1.2.1      | Fault prevention and fault removal                                | 10 |

|     |       | 1.2.2      | Error handling and recovery                                       | 10 |

|     |       | 1.2.3      | Fault handling                                                    |    |

|     | 1.3   | Genera     | al taxonomy of errors                                             | 10 |

|     |       | 1.3.1      | Error detection                                                   | 10 |

|     |       | 1.3.2      | Error propagation                                                 | 11 |

|     |       | 1.3.3      | Infected, poisoned, containable, and uncontainable                | 11 |

|     | 1.4   | Fault h    | nandling                                                          | 11 |

| 2   | ARN   | Лу8.А F    | Crror Handling and Recovery Architecture                          | 12 |

| -   | 2.1   |            | omy of errors in the ARMv8-A architecture                         |    |

|     | 2.1   | 2.1.1      | Architectural error detection                                     |    |

|     |       | 2.1.1      | Error correction and deferment                                    |    |

|     |       | 2.1.2      | Architectural error propagation                                   |    |

|     |       | 2.1.3      | Architecturally infected, containable, and uncontainable          |    |

|     |       | 2.1.4      | Architecturally consumed errors                                   |    |

|     |       | 2.1.5      | Other errors                                                      |    |

|     | 2.2   |            | ating error exceptions                                            |    |

|     | 2.2   |            | ecord System register view                                        |    |

|     | 2.3   | 2.3.1      | Fields in VSESR_EL2, VDFSR, DISR(_EL1), and VDISR(_EL2)           |    |

|     | 2.4   |            | Synchronization Barrier                                           |    |

|     | 2.4   | 2.4.1      | ESB and Unrecoverable errors                                      |    |

|     |       | 2.4.1      | ESB and other containable errors                                  |    |

|     |       | 2.4.2      | ESB and other physical errors                                     |    |

|     |       | 2.4.3      | ESB and virtual errors                                            |    |

|     |       | 2.4.4      | ESD and virtual errors                                            |    |

|     | 2.5   |            | g external abort and SError interrupt exceptions to AArch64       |    |

|     | 2.5   | 2.5.1      | Target Exception level                                            |    |

|     |       | 2.5.1      | AArch64 syndrome registers on taking an error exception           |    |

|     |       | 2.5.2      | Multiple SError interrupts                                        |    |

|     | 2.6   |            | g external abort and SError interrupt exceptions to AArch32       |    |

|     | 2.0   | 2.6.1      | Target mode                                                       |    |

|     |       | 2.6.2      | AArch32 syndrome registers on taking an error exception           |    |

|     |       | 2.6.3      | Multiple SError interrupts                                        |    |

|     | 2.7   |            | l SError interrupts                                               |    |

|     |       |            |                                                                   |    |

| 3   | RAS   | •          | Architecture                                                      |    |

|     | 3.1   |            | ling errors                                                       |    |

|     |       | 3.1.1      | Detected uncorrected errors in data                               | 24 |

|     |       |            |                                                                   |    |

#### $\label{eq:armonic} \textbf{ARM} \circledast \textbf{Reliability, Availability, and Serviceability (RAS) Specification}$

|   |     | 3.1.2    | Corrected errors in data                                     |    |

|---|-----|----------|--------------------------------------------------------------|----|

|   |     | 3.1.3    | Other sources of error and warnings                          |    |

|   |     | 3.1.4    | Error types                                                  | 25 |

|   |     | 3.1.5    | Software faults                                              | 26 |

|   | 3.2 | Standar  | d error record                                               |    |

|   |     | 3.2.1    | Nodes                                                        |    |

|   |     | 3.2.2    | Multiple records per node                                    |    |

|   |     | 3.2.3    | Writing the error record                                     |    |

|   |     | 3.2.4    | Security and Virtualization                                  |    |

|   |     | 3.2.5    | Synchronization and error record accesses                    |    |

|   | 3.3 |          | ecovery interrupt                                            |    |

|   | 3.4 |          | andling interrupt                                            |    |

|   | 3.5 |          | l error signaling (external aborts)                          |    |

|   | 3.6 |          | d format Corrected error counter                             |    |

|   | 3.7 |          | covery and fault handling signaling                          |    |

|   | 3.8 | Error R  | ecovery reset                                                | 35 |

| 4 | RAS | Extensio | on Registers                                                 |    |

| - | 4.1 |          | y-mapped view                                                |    |

|   | 4.2 | •        | alues                                                        |    |

|   | 4.3 |          | to ERR< <i>n</i> >STATUS                                     |    |

|   | 4.4 |          | 54 System registers                                          |    |

|   |     | 4.4.1    | Register index                                               |    |

|   |     | 4.4.2    | DISR_EL1, Deferred Interrupt Status Register                 |    |

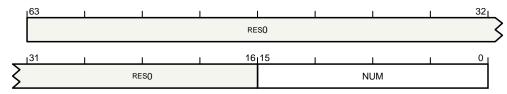

|   |     | 4.4.3    | ERRIDR_EL1, Error Record ID Register                         |    |

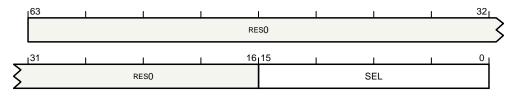

|   |     | 4.4.4    | ERRSELR_EL1, Error Record Select Register                    |    |

|   |     | 4.4.5    | ERXADDR_EL1, Selected Error Record Address Register          |    |

|   |     | 4.4.6    | ERXCTLR_EL1, Selected Error Record Control Register          |    |

|   |     | 4.4.7    | ERXFR_EL1, Selected Error Record Feature Register            |    |

|   |     | 4.4.8    | ERXMISCO_EL1, Selected Error Record Miscellaneous Register 0 |    |

|   |     | 4.4.9    | ERXMISC1_EL1, Selected Error Record Miscellaneous Register 1 |    |

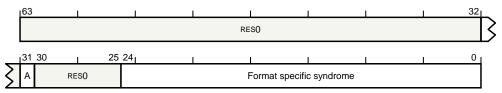

|   |     | 4.4.10   | ERXSTATUS_EL1, Selected Error Record Primary Status Register |    |

|   |     | 4.4.11   | VDISR_EL2, Virtual Deferred Interrupt Status Register        | 50 |

|   |     | 4.4.12   | VSESR_EL2, Virtual SError Exception Syndrome Register        | 53 |

|   | 4.5 | AArch3   | 32 System registers                                          | 55 |

|   |     | 4.5.1    | Register index                                               | 55 |

|   |     | 4.5.2    | DISR, Deferred Interrupt Status Register                     | 56 |

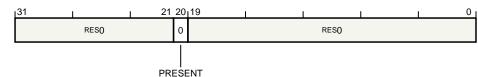

|   |     | 4.5.3    | ERRIDR, Error Record ID Register                             |    |

|   |     | 4.5.4    | ERRSELR, Error Record Select Register                        | 60 |

|   |     | 4.5.5    | ERXADDR, Selected Error Record Address Register              |    |

|   |     | 4.5.6    | ERXADDR2, Selected Error Record Address Register 2           | 63 |

|   |     | 4.5.7    | ERXCTLR, Selected Error Record Control Register              |    |

|   |     | 4.5.8    | ERXCTLR2, Selected Error Record Control Register 2           |    |

|   |     | 4.5.9    | ERXFR, Selected Error Record Feature Register                |    |

|   |     | 4.5.10   | ERXFR2, Selected Error Record Feature Register 2             |    |

|   |     | 4.5.11   | ERXMISC0, Selected Error Record Miscellaneous Register 0     |    |

|   |     | 4.5.12   | ERXMISC1, Selected Error Record Miscellaneous Register 1     |    |

|   |     | 4.5.13   | ERXMISC2, Selected Error Record Miscellaneous Register 2     |    |

|   |     | 4.5.14   | ERXMISC3, Selected Error Record Miscellaneous Register 3     |    |

|   |     | 4.5.15   | ERXSTATUS, Selected Error Record Primary Status Register     | 72 |

|     | 4.5.16   | VDFSR, Virtual SError Exception Syndrome Register                | 73  |

|-----|----------|------------------------------------------------------------------|-----|

|     | 4.5.17   | VDISR, Virtual Deferred Interrupt Status Register                |     |

| 4.6 | Error Re | ecord registers, including memory mapped view                    |     |

|     | 4.6.1    | Register index                                                   |     |

|     | 4.6.2    | ERR< <i>irq</i> >CR0, Error Interrupt Configuration Register 0   | 79  |

|     | 4.6.3    | ERR <irq>CR1, Error Interrupt Configuration Register 1</irq>     | 80  |

|     | 4.6.4    | ERR< <i>irq</i> >CR2, Error Interrupt Configuration Register 2   | 81  |

|     | 4.6.5    | ERR <n>ADDR, Error Record Address Register</n>                   |     |

|     | 4.6.6    | ERR <n>CTLR, Error Record Control Register</n>                   | 85  |

|     | 4.6.7    | ERR< <i>n</i> >FR, Error Record Feature Register                 |     |

|     | 4.6.8    | ERR< <i>n</i> >MISC0, Error Record Miscellaneous Register 0      | 93  |

|     | 4.6.9    | ERR <n>MISC1, Error Record Miscellaneous Register 1</n>          | 98  |

|     | 4.6.10   | ERR <n>STATUS, Error Record Primary Status Register</n>          | 99  |

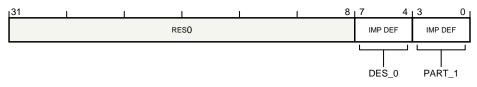

|     | 4.6.11   | ERRCIDR0, Component Identification Register 0                    |     |

|     | 4.6.12   | ERRCIDR1, Component Identification Register 1                    | 108 |

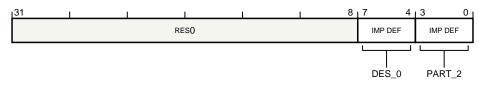

|     | 4.6.13   | ERRCIDR2, Component Identification Register 2                    | 109 |

|     | 4.6.14   | ERRCIDR3, Component Identification Register 3                    | 110 |

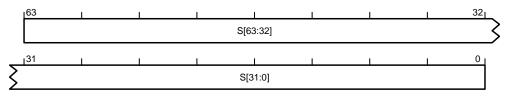

|     | 4.6.15   | ERRDEVAFF, Device Affinity Register                              | 111 |

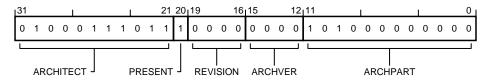

|     | 4.6.16   | ERRDEVARCH, Device Architecture Register                         | 114 |

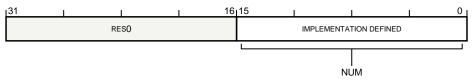

|     | 4.6.17   | ERRDEVID, Error Record Device ID Register                        | 116 |

|     | 4.6.18   | ERRGSR <n>, Error Group Status Register</n>                      |     |

|     | 4.6.19   | ERRIRQCR <n>, Generic Error Interrupt Configuration Register</n> | 118 |

|     | 4.6.20   | ERRIRQSR, Error Interrupt Status Register                        |     |

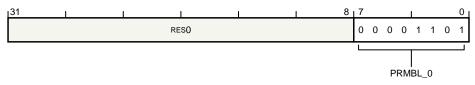

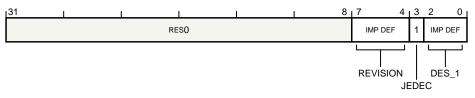

|     | 4.6.21   | ERRPIDR0, Peripheral Identification Register 0                   | 121 |

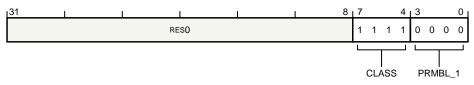

|     | 4.6.22   | ERRPIDR1, Peripheral Identification Register 1                   |     |

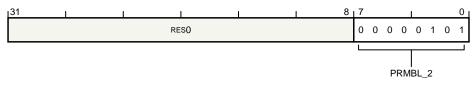

|     | 4.6.23   | ERRPIDR2, Peripheral Identification Register 2                   |     |

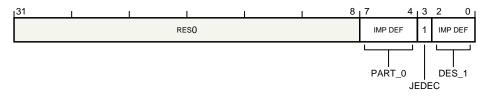

|     | 4.6.24   | ERRPIDR3, Peripheral Identification Register 3                   |     |

|     | 4.6.25   | ERRPIDR4, Peripheral Identification Register 4                   |     |

|     |          |                                                                  |     |

# Preface

This document describes the RAS Extension, and must be read in conjunction with the *ARM*<sup>®</sup> *Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.*

## References

This document refers to the following documents.

| Reference | Document number | Author | Document name                                                                              |

|-----------|-----------------|--------|--------------------------------------------------------------------------------------------|

| [1]       | ARM DDI 0487    | ARM    | ARM <sup>®</sup> Architecture Reference Manual, ARMv8, for<br>ARMv8-A architecture profile |

## Feedback

ARM welcomes feedback on its documentation.

If you have comments on the content of this specification, send an e-mail to errata@arm.com. Give:

- The title.

- The document and version number, ARM DDI 0587B.a.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# 1 Introduction

RAS are three aspects of the *dependability* of a system:

- Reliability, continuity of correct service.

- Availability, readiness for correct service.

- Serviceability, ability to undergo modifications and repairs.

RAS techniques reduce unplanned outages because:

- Transient errors can be detected and corrected before they cause application or system failure.

- Failing components can be identified and replaced.

- Failure can be predicted ahead-of-time to allow replacement during planned maintenance.

The RAS Extension is a mandatory extension to the ARMv8.2 architecture, and it is an optional extension to the ARMv8.0 and ARMv8.1 architectures.

ID\_AA64PFR0\_EL1.RAS in AArch64 state, and ID\_PFR0.RAS in AArch32 state, indicate whether the RAS Extension is implemented.

The RAS Extension introduces a new barrier instruction, the Error Synchronization Barrier (ESB), which is described in detail in the *ARM*<sup>®</sup> *Architecture Reference Manual*, *ARMv8*, *for ARMv8-A architecture profile*.

The RAS Extension also introduces a set of System and memory-mapped registers that are specific to the RAS architecture. These are described in detail in this specification.

In addition, the RAS Extension changes a limited number of fields in the following ARMv8-A System registers:

- In AArch64 state:

- HCR\_EL2.

- ID\_AA64MMFR1\_EL1.

- ID\_AA64PFR0\_EL1.

- ID\_MMFR4\_EL1.

- ID\_PFR0\_EL1.

- SCR\_EL3.

- ESR\_ELx.

- IFSR32\_EL2.

- In AArch32 state:

- HCR2.

- ID\_MMFR4.

- ID\_PFR0.

- SCR.

- DFSR.

- IFSR.

- HSR.

For details about these changes, see the *ARM*<sup>®</sup> *Architecture Reference Manual*, *ARMv8*, *for ARMv8-A architecture profile*.

Page 8

## 1.1 Types of errors

Correct service is delivered when the service implements the system function. This might encompass:

- Producing correct results.

- Producing results within the time allotted to the task.

- Not divulging secret or secure information.

For the purpose of describing the RAS Extension, deviation from correct service is defined using the following terms:

- A *failure* is the event of deviation from correct service. This includes data corruption, data loss, and service loss.

- An *error* is the deviation.

- A *fault* is the cause of the error.

Errors that are present but not detected are *latent* or *undetected* errors. A transaction carrying a latent error is *corrupted*. In a system with no error detection, all errors are latent errors and are *silently propagated* by components until either:

- They are masked and do not affect the outcome of the system:

- These are benign or false errors.

- They affect the service interface of the system and cause failure:

- These are silent data corruptions (SDC).

- The rate of such failures, measured as the number of failures per billion device-hours of operation, is called the SDC *Failure-in-Time* (FIT) rate.

The severity of a failure can range from minor to catastrophic:

- The harmful consequences of a *minor failure* are of a similar cost to the benefits provided by correct service delivery.

- The harmful consequences of a *catastrophic failure* are orders of magnitude, or even incommensurably, higher than the benefit provided by correct service delivery.

There are many sources of faults in a system, including both software and hardware faults:

- *Hardware faults* originate in, or affect, hardware.

- *Software faults* affect software, that is programs or data.

The RAS Extension primarily addresses errors produced from hardware faults. These fall into two main areas:

- Transient faults.

- Non-transient or *persistent faults*.

## 1.2 Techniques for improving reliability, availability, and serviceability

Each device sets its own targets for reliability, availability, and serviceability, and uses different techniques to achieve these targets, including:

- <u>Fault prevention and fault removal</u>.

- Error handling and recovery.

- Fault handling.

The RAS Extension does not prescribe the level of reliability, availability, and serviceability in any implementation, or which parts of the system include RAS.

## 1.2.1 Fault prevention and fault removal

<u>Fault prevention</u> and <u>fault removal</u> are two techniques for handling faults. Fault prevention and fault removal mechanisms are IMPLEMENTATION DEFINED.

Fault prevention techniques are outside the scope of the architecture.

The RAS Extension provides a common programmers' model and mechanisms for fault handling. A fault that is removed is a corrected error and might be recorded and generate a fault handling interrupt, but it is not propagated. This means that it is not consumed and does not signal an error exception.

## 1.2.2 Error handling and recovery

Error recovery is the process by which software and hardware minimize the impact of an uncorrected error by:

- Deferring an error from faults by not taking action immediately, but waiting for either:

- The fault to be masked later (fault removal).

- The error to be reported to a consumer of the error (this enables error recovery).

- Preventing further propagation of the error, that is *containing* the error.

- Reducing the severity of the error by invoking a *service failure mode*:

- These are detected uncorrected errors (DUE).

- The rate of such failures gives the DUE FIT rate.

- The type of service failure mode depends on what is acceptable to the service.

A software error recovery agent is invoked when hardware detects an error it cannot correct or remove.

An error recovery agent also provides information to the operator through error logs to improve serviceability, for example to help with the identification of *field replaceable units* (FRUs).

Error detection mechanisms are IMPLEMENTATION DEFINED. The RAS Extension provides a common programmers' model and mechanisms for error recovery.

## 1.2.3 Fault handling

Fault handling by software is the process by which software diagnoses and responds to faults to improve availability.

The RAS Extension provides mechanisms to allow the reporting of errors and warnings to a fault handling agent, and to provide information about the fault to the agent. The detailed nature of the fault handling agent is outside the scope of this architecture

Fault handling and error recovery might be independent agents.

## 1.3 General taxonomy of errors

## 1.3.1 Error detection

When a component accesses memory or other state, an error might be detected in that memory or state. The error might be corrected, deferred, or signaled to another component as a *detected* error.

## **1.3.2 Error propagation**

When an error is passed from a producer to a consumer, the producer *propagates* the error. If the error is received by the consumer as an undetected error, the error has been *silently propagated*.

In the simplest case, an error is propagated if a corrupt value is passed from producer to consumer. However, an error has also been propagated if:

- A transaction that would not have been permitted to occur had the fault not been activated passes from the producer to the consumer.

- A transaction does not occur that ought to have occurred.

- Modified data is lost or any other loss of coherency in a multiprocessor coherent system is observed.

In some cases, changing the timing and order of transactions is also considered propagation of an error.

### 1.3.3 Infected, poisoned, containable, and uncontainable

If an uncorrected error is consumed and updates the state of the component, then that state becomes *infected*. If the state is marked as being in error, meaning a subsequent read of the state will signal a detected error, the state is *poisoned*.

An undetected error is *uncontained* at the component that failed to detect it. A silently propagated error is uncontained at the component that silently propagated it.

A detected uncorrected error is *uncontainable* if it might be uncontained. A detected uncorrected error is *containable* if it is not uncontainable. If the component cannot determine whether a detected error is uncontainable or containable, it must treat it as uncontainable.

An error that is uncontainable at a component might still be containable at the system level.

----- Note -

Reporting an error as containable allows software to contain the error. It does not mean that hardware has contained the error.

## 1.4 Fault handling

The data recorded about the error is an *error record*. It is the responsibility of the error recovery and fault handling processes to collate the error record data and write it to an *error log*. See <u>Standard error record</u>.

ARM recommends that the error record identifies the component where the fault originated.

# 2 ARMv8-A Error Handling and Recovery Architecture

## 2.1 Taxonomy of errors in the ARMv8-A architecture

### 2.1.1 Architectural error detection

When a PE accesses memory or other state, an error might be detected in that memory or state, and corrected, deferred, or signaled to the PE as a detected error.

It is IMPLEMENTATION DEFINED whether an error detected by the consumer of a write from a PE is signaled to the PE and becomes a detected error that is consumed by the PE.

The component that detects an error is called a *node*. The nodes included as part of a processor, including an ARMv8-A PE, are IMPLEMENTATION DEFINED. An ARMv8-A PE implementing the RAS Extension must implement the System register interface to the IMPLEMENTATION DEFINED nodes of a PE. For more information, see <u>Nodes</u>.

The size of the Protection granule for any implemented error detection mechanism is IMPLEMENTATION DEFINED. A system might implement multiple error detection mechanisms with differing Protection granule sizes. The mechanism for clearing an error or poison from a Protection granule is IMPLEMENTATION DEFINED, and it is IMPLEMENTATION DEFINED whether any such mechanism exists.

---- Note -

For some systems, a single-copy atomic write of at least the whole Protection granule can reset the state of the granule and clear any error or poison. In other systems, a DC ZVA operation might also clear the error. However, the Protection granule might be larger than the DC ZVA block size and/or the largest single-copy atomic access that the PE can perform. These systems might require software to stop using the Protection granule, for example by not using the physical page containing the granule, until the system can be purged of errors, for example at a system reset. The architecture does not set any limit on the size of a Protection granule and it might be larger than a translation granule. Any mechanism for purging the system of errors is also IMPLEMENTATION DEFINED.

## 2.1.2 Error correction and deferment

If hardware can correct or defer a detected error, it must do so. The error is logged, and a fault handling interrupt is generated for fault handling purposes.

## 2.1.3 Architectural error propagation

For a PE, <u>Error propagation</u> applies to the propagation of detected errors between the general-purpose or SIMD&FP registers, and any program-visible architectural state of the PE, including:

- Other general-purpose and SIMD&FP registers.

- System registers.

- Special-purpose registers.

- PSTATE.

- Memory.

That is, the error is propagated by:

• A store of a corrupt value.

- A write of a corrupt value to a System register, Special-purpose register or PSTATE. Infecting a System register state might mean that the PE generates transactions that would not otherwise be permitted.

- Any operation that would not have been permitted to occur had the error not been activated, including:

- A load, translation table walk, or instruction fetch that would not have been permitted, including those from hardware speculation or prefetching.

- A store to an incorrect address or a store that would not have been made or not permitted.

- A direct or indirect write to a Special-purpose or System register that would not have been made or not permitted.

- Assertion of any signal, such as an interrupt, that would not have been asserted.

- Any operation not occurring that would have occurred had the error not been activated.

- Taking an imprecise exception.

- The PE discarding data that it holds in a modified state.

- Any other loss of uniprocessor semantics, ordering, or coherency.

The propagated error is silently propagated if it is not signaled to the consumer as a detected error.

The features that a PE includes to contain an error are IMPLEMENTATION DEFINED, and it is IMPLEMENTATION DEFINED whether an error can be signaled to the consumer as a detected error.

For example, an implementation might ensure that a corrupt value in a general-purpose or SIMD&FP register is not silently propagated, by signaling an error on any write of corrupt data to a memory location so that the memory location is poisoned.

### 2.1.4 Architecturally infected, containable, and uncontainable

<u>Infected</u>, <u>poisoned</u>, <u>containable</u>, <u>and uncontainable</u> apply to all program-visible architectural state of the PE, including general-purpose registers</u>, SIMD&FP registers, Special-purpose and System registers, PSTATE, and memory.

An error is uncontained by the PE if the error is silently propagated, unless it is contained because all of the following are true:

- The corrupt value is in the general-purpose or SIMD&FP registers.

- The error is only silently propagated by an instruction that occurs in program order after one of the following:

- Taking the External Abort or SError interrupt exception generated by the error.

- An Error Synchronization Barrier operation that synchronizes the error.

- The error is not silently propagated in any other way.

Architectural error propagation defines error propagation for a PE.

### 2.1.5 Architecturally consumed errors

For a PE, an error is architecturally consumed if any of the following are true:

- An instruction commits the corruption into the visible state of the PE.

- The error is on an instruction fetch and the instruction is committed for execution.

- The error is on a translation table walk for a committed load, store, or instruction fetch.

#### ARM® Reliability, Availability, and Serviceability (RAS) Specification

The PE must take action for a detected, architecturally consumed error, either by:

- Generating an error exception.

- Entering a failure mode.

### 2.1.6 Other errors

Errors from software faults are outside the scope of the RAS Extension error recovery architecture.

From within the processor itself, other errors might be detected. These are not errors detected by the architectural model of the PE and so are treated like errors detected by another component. An example of this is when the cache, not the PE, detects a tag RAM error. Other components might report errors to a PE using error recovery interrupts.

For implementations that include the Statistical Profiling Extension, the Statistical Profiling Extension behaves like a separate component.

## 2.2 Generating error exceptions

An error exception might be generated for an error that is corrected or deferred.

An error exception must be generated for all detected errors that are neither corrected nor deferred, and are signaled to and consumed by a PE as an External abort in response to:

- An architectural read from memory.

- A write to memory or a data cache maintenance operation. It is IMPLEMENTATION DEFINED whether an error detected by the consumer of a write from a PE:

- Is deferred to the consumer, for example, by poisoning the location.

- Is signaled to the PE as an External abort.

- Generates an error recovery interrupt.

It is IMPLEMENTATION DEFINED whether an error that is consumed by hardware speculation or prefetching by a PE, but that is not committed to the architecturally visible state of the PE, generates an External abort exception at the PE.

—— Note ——

An SError interrupt can also be generated for IMPLEMENTATION DEFINED causes.

An External abort must be taken as one of:

- A synchronous External abort exception.

- An asynchronous External abort that is taken as an *SError interrupt* exception.

It is IMPLEMENTATION DEFINED whether an External abort is taken synchronously or asynchronously for non-speculative:

- Instruction fetches.

- Instructions making explicit access to memory.

- Translation table walks.

- Hardware updates of translation tables.

All other External aborts must be taken asynchronously as an SError interrupt.

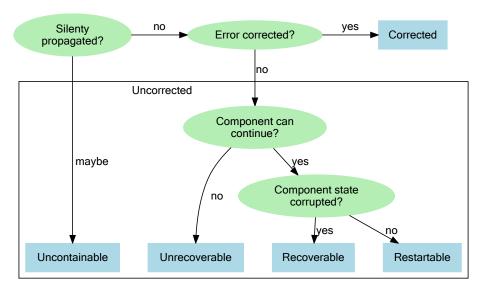

On each error exception, it is IMPLEMENTATION DEFINED whether the error has been contained or is *Uncontainable*. If the error has been contained, it is further IMPLEMENTATION DEFINED whether the state of the PE on taking the error exception is *Unrecoverable*, *Recoverable*, or *Restartable*:

#### **Uncontainable error (UC)**

The error is Uncontainable if the error has been, or might have been, silently propagated.

If the error cannot be isolated to an application or VM, or both, the system must be shut down by software to avoid catastrophic failure.

#### **Unrecoverable error (UEU)**

The state of the PE is Unrecoverable if all of the following are true:

- The error has not been silently propagated.

- The PE cannot recover execution from the preferred return address of the exception. This might be because of one of the following:

- The error has been architecturally consumed by the PE and infected the state of the PE general-purpose, SIMD&FP, and System registers.

- The exception is imprecise.

Either the application or the VM, or both, cannot continue and must be isolated by software.

#### **Recoverable error (UER)**

The state of the PE is Recoverable if all of the following are true:

- The error has not been silently propagated.

- The error has not been architecturally consumed by the PE. (The PE architectural state is not infected.)

- The exception is precise and PE can recover execution from the preferred return address of the

exception, if software locates and repairs the error.

The PE cannot make correct progress without either consuming the error or otherwise making the error unrecoverable. The error remains latent in the system.

If software cannot locate and repair the error, either the application or the VM, or both, must be isolated by software.

#### **Restartable error (UEO)**

The state of the PE is Restartable if all of the following are true:

- The error has not been silently propagated.

- The error has not been architecturally consumed by the PE. (The PE architectural state is not infected.)

- The exception is precise and PE can recover execution from the preferred return address of the

exception without any immediate action by software.

The PE can make progress. However, the error remains latent in the system.

Software might take action to locate and repair the error before it is consumed. The PE can be restarted by software without software taking any action to locate and repair the error.

This taxonomy is shown by Figure 1.

ARM® Reliability, Availability, and Serviceability (RAS) Specification

#### Figure 1: Taxonomy of consumed error types

It is IMPLEMENTATION DEFINED whether the severity of an asynchronous error and the state of the PE are reported when the asynchronous SError interrupt exception is taken. If the severity of an asynchronous error and the state of the PE are not reported, it is further IMPLEMENTATION DEFINED whether the error is reported as uncategorized or with an IMPLEMENTATION DEFINED syndrome. The severity of a synchronous error and the state of the PE are always reported when synchronous external abort exception is taken. See:

- AArch64 syndrome registers on taking an error exception.

- AArch32 syndrome registers on taking an error exception.

It is IMPLEMENTATION DEFINED whether IMPLEMENTATION DEFINED and uncategorized SError interrupts are edge-triggered or level-sensitive. Level-sensitive SError interrupts cannot be synchronized by an Error Synchronization Barrier.

The set of error types that can be reported by an implementation is IMPLEMENTATION DEFINED. An implementation can report:

- Any Restartable error as any of Recoverable, Unrecoverable, or Uncontainable.

- Any Recoverable error as either Unrecoverable or Uncontainable.

- Any Unrecoverable error as Uncontainable.

— Note –

If the state of the PE is reported as Recoverable, this does not mean that the error can be recovered from because the error in memory might be one which does not allow software to recover the operation. Rather, software *might* be able to recover if it can repair the error and continue.

## 2.3 Error record System register view

--- Note -

AArch64 Error record System registers are all registers with an ER\*\_EL1 mnemonic. AArch32 Error record System registers are all registers with an ER\* mnemonic. Both of these are defined in this specification.

Page 16

The number of error records that can be accessed through the System registers is IMPLEMENTATION DEFINED, and might be zero. The <u>ERRIDR EL1</u> and <u>ERRIDR</u> registers indicate the highest numbered index of the error records that can be accessed by System registers, plus one.

The error record System registers are described by:

- <u>AArch64 System registers</u>.

- AArch32 System registers.

The error record register contents are described by <u>Error Record registers, including memory mapped view</u>. To access an error record, software must:

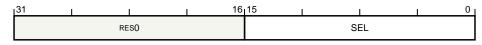

- Set the error selection register, <u>ERRSELR\_EL1.SEL</u> or <u>ERRSELR.SEL</u>, to the index of the record being accessed.

- Access the error record using the ERX\* System registers.

— Note -

See Synchronization and error record accesses.

The error records accessed through the System registers might be accessible only to the PE associated with those Systems registers, or they might be shared and therefore accessible to other PEs through either System registers or as a memory-mapped component.

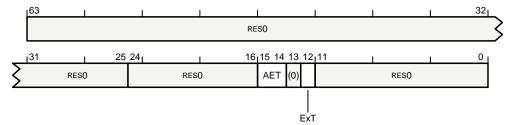

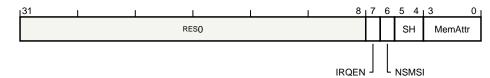

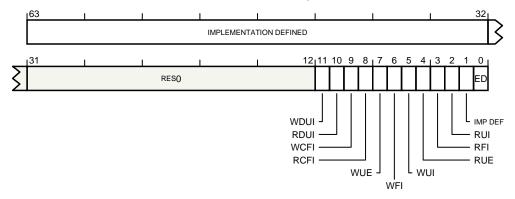

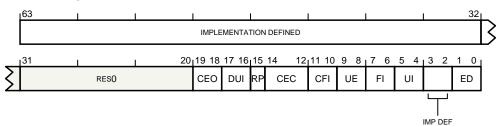

## 2.3.1 Fields in VSESR\_EL2, VDFSR, DISR(\_EL1), and VDISR(\_EL2)

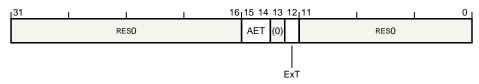

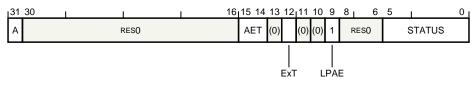

ESR\_ELx, HSR, DFSR, <u>VSESR\_EL2</u>, <u>VDFSR</u>, <u>DISR\_EL1</u>, <u>DISR</u>, <u>VDISR\_EL2</u>, and <u>VDISR</u> are error syndrome registers that are written with either a syndrome by hardware on taking or deferring a physical SError interrupt, or with a virtual syndrome value provided by software for a virtual SError interrupt, as applicable.

For a given implementation:

- If ESB never synchronizes any errors, then <u>DISR\_EL1.A</u> and <u>DISR.A</u> might be RES0.

- The error syndrome registers must be capable of storing any syndrome value that might be reported by hardware on taking a physical error exception.

- If any of ESR\_ELx[24:0], HSR[11:9], and DFSR[15:14,12] is not used and always set to zero by hardware on taking a physical SError interrupt exception or synchronous External Abort exception, it can be RES0 in that syndrome register.

- A bit that is not used and always set to zero or always set to one by hardware on taking a physical SError interrupt is permitted to be RES0 or RES1 respectively in the corresponding other syndrome registers. See <u>Table 1</u>.

| Bit that is permitted to be                         | If always set to zero or always set to one on taking an SError interrupt in all of |                        |                                 |  |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------|------------------------|---------------------------------|--|--|--|

| RESO or RES1                                        | $ESR_ELx[x], x \in [24:0]$                                                         | $HSR[x], x \in [11:9]$ | DFSR[ $x$ ], $x \in [15:14,12]$ |  |  |  |

| $\underline{\text{VSESR}}\underline{\text{EL2}}[x]$ | Yes                                                                                | -                      | Yes                             |  |  |  |

| $\underline{\text{VDISR}}\underline{\text{EL2}}[x]$ | Yes                                                                                | -                      | Yes                             |  |  |  |

| DISR_EL1[x]                                         | Yes                                                                                | -                      | -                               |  |  |  |

| $\underline{\text{VDFSR}}[x]$                       | -                                                                                  | -                      | Yes                             |  |  |  |

Table 1: Permitted relaxations for bits in error syndrome registers

| VDISR[x]                     | - | -   | Yes |

|------------------------------|---|-----|-----|

| $\underline{\text{DISR}}[x]$ | - | Yes | Yes |

## 2.4 Error Synchronization Barrier

The RAS Extension adds the Error Synchronization Barrier operation and the ESB instruction. For details and the encoding of ESB, see the *ARM*<sup>®</sup> *Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.*

In AArch32 state:

- ESB might update the <u>DISR</u> or <u>VDISR</u> registers.

- The <u>DISR</u> register can only be accessed at EL1 or above. If EL2 is implemented and HCR.AMO is set to 1, then reads and writes of <u>DISR</u> at Non-secure EL1 access <u>VDISR</u>.

In AArch64 state:

- ESB might update the <u>DISR\_EL1</u> or <u>VDISR\_EL2</u> registers.

- The <u>DISR\_EL1</u> register can only be accessed at EL1 or above. If EL2 is implemented and HCR\_EL2.AMO is set to 1, then reads and writes of <u>DISR\_EL1</u> at Non-secure EL1 access <u>VDISR\_EL2</u>.

Error Synchronization Barriers synchronize Unrecoverable errors, that is, containable errors that are architecturally consumed by the PE and not silently propagated.

All Unrecoverable errors must be synchronized by Error Synchronization Barriers.

## 2.4.1 ESB and Unrecoverable errors

For Unrecoverable errors, an ESB guarantees that:

- All Unrecoverable errors generated in program order before the ESB have pended a physical SError interrupt exception.

- If such a physical SError interrupt is pended by the ESB instruction, or was pending before the ESB instruction is executed:

- If the physical SError interrupt is unmasked at the current Exception level, it is taken before completion of the ESB instruction.

— Note —

- That is, the preferred return address of the exception is the ESB instruction address.

- The prioritization of this exception with respect to any other asynchronous exceptions that are pending and unmasked when the ESB instruction is executed is IMPLEMENTATION DEFINED.

- If the physical SError interrupt is masked at the current Exception level, then:

- The pending SError interrupt is cleared.

- The SError interrupt syndrome is recorded in <u>DISR\_EL1</u> or <u>DISR</u>.

- The <u>DISR\_EL1</u>.A or <u>DISR</u>.A field is set to 1 to indicate the SError interrupt was generated in program order before the ESB.

#### ARM® Reliability, Availability, and Serviceability (RAS) Specification

The Error Synchronization Barrier operation contains the error. See <u>Architecturally infected</u>, <u>containable</u>, <u>and uncontainable</u>.

ESB guarantees that all Unrecoverable SError interrupts that are generated in program order:

- Before the ESB, are either taken before or at the ESB, or recorded in the <u>DISR\_EL1</u> or <u>DISR</u> register by the ESB.

- After the ESB, are taken after the ESB and not recorded in <u>DISR\_EL1</u> or <u>DISR</u> by the ESB.

This includes Unrecoverable SError interrupts that are generated by instructions, translation table walks, hardware updates to the translation tables, and instruction fetches on the same PE.

If the Unrecoverable SError interrupt exception is:

- Taken, then the error is reported to software as Unrecoverable in the ESR\_ELx, DFSR or HSR syndrome register on taking the interrupt.

- Not taken, then the error is reported to software as Unrecoverable in the <u>DISR\_EL1</u> or <u>DISR</u> register.

### 2.4.2 ESB and other containable errors

For other types of containable error:

- A *Recoverable* error has not yet been consumed by the PE.

- *Restartable* and *Corrected* errors, and SError interrupts from reads by hardware speculation that do not corrupt the state of the PE, have not been consumed by the PE.

An unconsumed SError interrupt taken at the ESB or recorded in the <u>DISR\_EL1</u> or <u>DISR</u> register, might have been generated by hardware speculation of an instruction in program order after the Error Synchronization Barrier.

These SError interrupts are always precise.

## 2.4.3 ESB and other physical errors

For other errors, the following rules apply:

- Synchronous Abort exceptions are not synchronized by an Error Synchronization Barrier.

- Error recovery interrupts are asynchronous and are not synchronized by an Error Synchronization Barrier.

- It is IMPLEMENTATION DEFINED whether IMPLEMENTATION DEFINED and uncategorized SError interrupts are containable or Uncontainable, and whether they can be synchronized by an Error Synchronization Barrier.

- Uncontainable errors might not have been contained, and Uncontainable SError interrupts might be imprecise. An Uncontainable error might be taken at the ESB or recorded in the <u>DISR\_EL1</u> or <u>DISR</u> register by an ESB instruction, but this is not architecturally required.

## 2.4.4 ESB and virtual errors

If EL2 is implemented, then an ESB instruction executed at Non-secure EL0 or EL1 also synchronizes a pending virtual SError interrupt when any of:

- EL2 is using AArch64, HCR\_EL2.AMO is set to 1, and HCR\_EL2.TGE is set to 0.

- EL2 is using AArch32, HCR.AMO is set to 1, and HCR.TGE is set to 0.

In these cases, if a virtual SError interrupt is pending when the ESB instruction is executed:

- If the virtual SError interrupt is unmasked at the current Exception level, it is taken before the completion of the ESB instruction.

- If the virtual SError interrupt is masked at the current Exception level:

- HCR\_EL2.VSE or HCR.VA is cleared to 0.

- The virtual SError interrupt syndrome from <u>VSESR\_EL2</u> or <u>VDFSR</u> is recorded in <u>VDISR\_EL2</u> or <u>VDISR</u>, and <u>VDISR\_EL2</u>.A or <u>VDISR</u>.A is set to 1 to indicate the SError interrupt was pending prior to the execution of the ESB instruction.

— Note —

This happens in parallel with the Error Synchronization Barrier operation for physical SError interrupts.

#### 2.4.5 Extension for barrier at exception entry and exit

The ARMv8.2 IESB architectural feature adds a control bit to each SCTLR\_ELx register to insert an *implicit* Error Synchronization Barrier operation at exception entry and exception return. For the register field descriptions, see the *ARM*<sup>®</sup> *Architecture Reference Manual*, *ARMv8*, *for ARMv8-A architecture profile*.

For each Exception level, ELx, other than EL0, the implicit Error Synchronization Barrier after each exception or DCPSx instruction that is taken to ELx guarantees that Unrecoverable errors that are generated before the exception have pended an SError interrupt exception. If an Unrecoverable SError interrupt that can be synchronized is pended by, or was pending before the exception, then:

• If SError interrupts are unmasked at ELx, the SError interrupt is taken before the first instruction at ELx is executed.

----- Note -----

That is, the preferred return address for the SError interrupt is the original exception vector address.

• If SError interrupts are masked at ELx, the SError interrupt is pending.

The implicit Error Synchronization Barrier before an ERET or DRPS instruction executed at ELx guarantees that Unrecoverable errors that are generated before the return instruction have pended an SError interrupt exception. If an Unrecoverable SError interrupt is pended by, or was pending before the instruction, then:

- If SError interrupts are unmasked, the SError interrupt is taken before the return instruction.

- —— Note -

That is, the preferred return address for the SError interrupt is the address of the return instruction.

• If SError interrupts are masked, the SError interrupt is pending.

The implicit form of Error Synchronization Barrier:

- Must synchronize all Unrecoverable errors.

- Has no effect on <u>DISR\_EL1</u> or <u>VDISR\_EL2</u>.

- On taking an SError interrupt to ELy, reports that the error was generated by an implicit Error Synchronization Barrier in the ESR\_ELy.IESB bit.

- Guarantees that:

- All Unrecoverable errors generated in program order before the implicit barrier, are taken at the implicit barrier if the SError exception is unmasked.

No Unrecoverable errors generated in program order after the implicit barrier are reported in this way.

– Note –

The prioritization of asynchronous interrupts is IMPLEMENTATION DEFINED. This means that an implementation might choose to:

- Behave as if the SError interrupt was taken before the implicit Error Synchronization Barrier operation, if the interrupt was not masked.

- For the exception entry case, taking the SError interrupt in place of the exception. The syndrome

information for the SError interrupt (including the restart address and whether the PE state is

Restartable, Recoverable, or otherwise) must then apply to the instruction that generated the

exception.

- For the exception return case, the ESR\_ELy.IESB bit might be zero, but, otherwise the behavior is the same.

• Take another exception before the SError interrupt. In this case, the SError interrupt remains pending.

ARM recommends the SError interrupt is prioritized over other exceptions.

## 2.5 Taking external abort and SError interrupt exceptions to AArch64

## 2.5.1 Target Exception level

For SError interrupt and synchronous external abort exceptions taken to AArch64 state, the default target Exception level is:

- EL1, if taken from EL0 or EL1.

- EL2, if taken from EL2.

- EL3, if taken from EL3.

### However:

- If EL3 is implemented and SCR\_EL3.EA is set to 1, all SError interrupt and synchronous external abort exceptions are taken to EL3.

- Otherwise, if EL2 is implemented and the PE is in Non-secure state, then:

- If HCR\_EL2.AMO or HCR\_EL2.TGE is set to 1, all SError interrupts from EL0 and EL1 are taken to EL2.

- If HCR\_EL2.TEA or HCR\_EL2.TGE is set to 1, all synchronous external abort exceptions from EL0 and EL1 are taken to EL2.

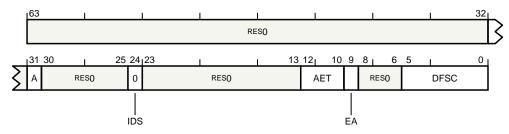

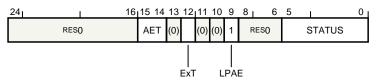

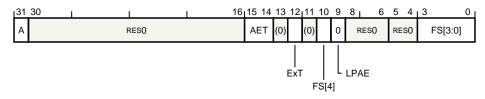

## 2.5.2 AArch64 syndrome registers on taking an error exception

On taking an SError interrupt or synchronous external abort exception to an Exception level using AArch64, the error syndrome is recorded in ESR\_ELx.

## 2.5.3 Multiple SError interrupts

An SError interrupt is asynchronous and might be masked by PSTATE.A. Therefore, multiple SError interrupt conditions might be pending together. The architecture does not define relative priorities for asynchronous exceptions.

It is IMPLEMENTATION DEFINED whether the multiple pending SError interrupt conditions are taken as a single SError interrupt exception.

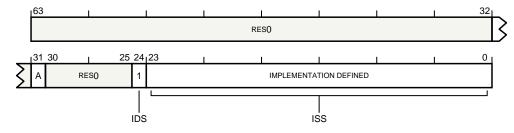

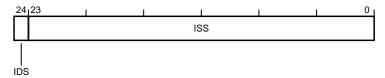

The value of ESR\_ELx is IMPLEMENTATION DEFINED if the multiple pending SError interrupt conditions that are taken as a single SError interrupt exception comprise a mix of:

- Pending IMPLEMENTATION DEFINED SError interrupt conditions that would be reported with ESR\_ELx.IDS == 1.

- Pending SError interrupt conditions that would be reported with ESR\_ELx.IDS == 0.

On taking an SError interrupt exception for one or more SError interrupt conditions:

- If one or more pending SError interrupt conditions are reported with ESR\_ELx.IDS == 1, then the syndrome recorded in ESR\_ELx.ISS is IMPLEMENTATION DEFINED.

- If all pending SError interrupt conditions are reported with ESR\_ELx.IDS == 0, then the combined effect of the errors on the state of the PE is reported in ESR\_ELx.AET.

Any pending SError interrupt conditions that are not taken with other SError interrupts as a single SError interrupt exception remain pending in ISR\_EL1 after the SError interrupt exception is taken.

An Error Synchronization Barrier operation requires that all Unrecoverable errors must be synchronized. If there are multiple requests outstanding, they are all synchronized by a single Error Synchronization Barrier operation.

## 2.6 Taking external abort and SError interrupt exceptions to AArch32

### 2.6.1 Target mode

For SError interrupt and synchronous external abort exceptions taken to AArch32 state, the default target mode is:

- Abort mode, if taken from EL0, EL1 or EL3, including from Secure Monitor mode.

- Hyp mode, if taken from EL2.

### However:

- If EL3 is implemented and using AArch32 and SCR.EA is set to 1:

- All SError interrupt and synchronous external Data Abort exceptions are taken to Secure Monitor mode, using vector offset 0x10.

- All synchronous external Prefetch Abort exceptions are taken to Secure Monitor mode, using vector offset 0x0C.

- Otherwise, if EL2 is implemented and using AArch32 and is in Non-secure state:

- If HCR.AMO or HCR.TGE is set to 1, all SError interrupts from EL0 and EL1 are taken to Hyp mode, using vector offset 0x14.

- If HCR.TEA or HCR.TGE is set to 1, all synchronous external abort exceptions from EL0 and EL1 are taken to Hyp mode, using vector offset 0x14.

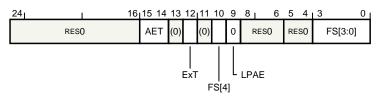

## 2.6.2 AArch32 syndrome registers on taking an error exception

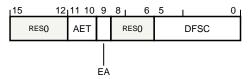

On taking an SError interrupt or synchronous external abort exception to an Exception level using AArch32, the error syndrome is recorded in:

- DFSR if an SError interrupt or synchronous Data Abort is taken to a PL1 mode.

- IFSR if a synchronous Prefetch Abort is taken to a PL1 mode.

• HSR if taken to Hyp mode.

### 2.6.3 Multiple SError interrupts

An SError interrupt is asynchronous and might be masked by CPSR.A. Therefore, multiple SError interrupt conditions might be pending together. The architecture does not define relative priorities for asynchronous exceptions.

It is IMPLEMENTATION DEFINED whether the multiple pending SError interrupt conditions are taken as a single SError interrupt exception.

On taking an SError interrupt exception, whether for one or more SError interrupt conditions, the combined effect of the errors on the state of the PE is reported in HSR.AET or DFSR.AET.

Any pending SError interrupt conditions that are not taken with other SError interrupts as a single SError interrupt exception remain pending in ISR after the SError interrupt exception is taken.

An Error Synchronization Barrier operation requires that all Unrecoverable errors must be synchronized. If there are multiple requests outstanding, they are all synchronized by a single Error Synchronization Barrier operation.

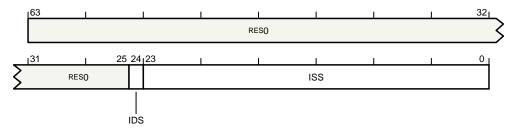

## 2.7 Virtual SError interrupts

When implemented, EL2 provides a virtual SError interrupt. The RAS Extension provides:

- Virtual syndrome registers to allow the ESR\_EL1 or DFSR value to be specified on taking a virtual SError interrupt. See <u>VSESR\_EL2</u> and <u>VDFSR</u>.

- Support for EL0 or EL1 to isolate a virtual SError interrupt as if it were a physical SError interrupt. See <u>ESB and virtual errors</u>.

# 3 RAS System Architecture

## 3.1 Recording errors

The component that detects an error is called a *node*. See <u>Nodes</u>.

When an error is detected by a node that supports fault reporting, it records the error and might generate a *fault handling interrupt* that is usually sent to an interrupt controller.

ARM recommends that nodes record all errors in *error records* to enable error recovery and fault handling. However, it is IMPLEMENTATION DEFINED whether:

- Errors are recorded by one or more of the following:

- The node that detects them.

- The master that consumes a signaled detected error. If only the master records the error, then syndrome information must be passed with the error to the master.

- A third party, that is a node whose purpose is to record errors for other nodes. Typically, such a

node contains either one record for each node for which it is recording an error, or it uses the

error record to identify the originating node.

- A master that consumes a signaled detected error records the consumed error.

- Errors are recorded by a node that merely propagates a signaled detected error from a different master to a different consumer.

- All corrected errors are recorded.

- Errors detected on hardware speculation are recorded.

An error record holds syndrome for the error. It contains:

- The status of the error.

- An address, if applicable.

- Optionally, counters for software to poll the rate of Corrected errors.

- Information to identify a FRU and locate the error within the FRU.

- This information is IMPLEMENTATION DEFINED.

- Other IMPLEMENTATION DEFINED information.

The Error Record registers might also contain control registers for error detection, correction and reporting at the node.

### 3.1.1 Detected uncorrected errors in data

Detected uncorrected errors are recorded and a fault handling interrupt is raised when the error is detected. ARM recommends that the hardware records enough information to allow fault analysis to find trends in the faults and allow identification of FRUs.

## 3.1.2 Corrected errors in data

ARM recommends that corrected errors are recorded by counting the individual errors. The fault handling process might compare the corrected error rate with a threshold value to determine whether to take action.

ARM recommends that hardware also records enough information to:

• Allow fault analysis to find trends in the faults. This information is IMPLEMENTATION DEFINED but might include the location of the data.

• Allow identification of a FRU.

The error is corrected and the corrected data passed on to the consumer.

It is IMPLEMENTATION DEFINED whether counting is done by software or hardware. <u>Standard format</u> <u>Corrected error counter</u> and <u>Corrected error counting</u> describe an optional standard hardware mechanism for counting errors.

### 3.1.3 Other sources of error and warnings

Other sources of error and warning are possible in a system. Within the ARMv8-A architecture these are signaled to a PE using an error recovery or fault handling interrupt.

### 3.1.4 Error types

For a <u>Standard error record</u>, the types of error that can be recorded are:

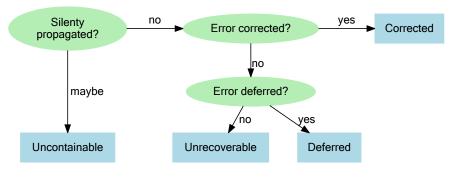

#### **Corrected error**

The error was detected and corrected. The error no longer infects the state of the node and has not been silently propagated. The node continues to operate.

#### **Deferred error**

The error was detected, was not corrected, and was deferred. The error has not been silently propagated. The error might be latent in the system. It is IMPLEMENTATION DEFINED whether the error continues to infect the state of the node or whether it has been deferred to the consumer. The node continues to operate. If the error might have been silently propagated, it must be reported as an Uncorrected error.

#### **Uncorrected error**

The error was detected and was not corrected or deferred. The error is latent in the system. An Uncorrected error can have sub-types. Two common sub-types are:

- *Unrecoverable*: The error has not been silently propagated.

- *Uncontainable*: The error might have been silently propagated. If the error cannot be isolated, the system must be shut down to avoid catastrophic failure.

The following two sections list additional sub-types.

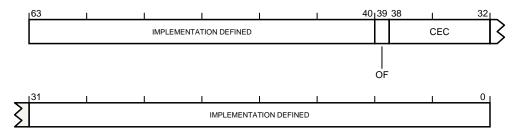

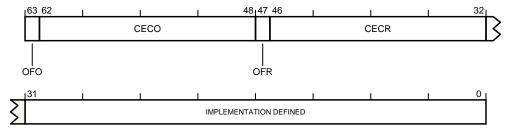

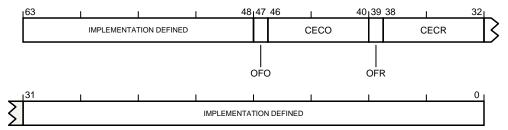

This taxonomy is shown by Figure 2.

#### Figure 2: Taxonomy of producer error types

#### Additional subtypes for an Uncorrected error produced at the node

For an error produced at the node, a node might additionally define the following subtypes:

#### Latent

The error has not been propagated. That is, the error was detected but not consumed, and was not recorded as a deferred error.

#### Signaled

The error has not been silently propagated. The error has been or might have been consumed, and was not recorded as a deferred error.

----- Note -

The producer does not know if a consumer has architecturally consumed the error. An error might be marked as latent if it has definitely not been propagated to any consumer, and signaled otherwise.

If these subtypes are implemented, then the Unrecoverable subtype further indicates that the node cannot continue operating.

ARM deprecates the implementation of the Latent and Signaled Uncorrected error types in the RAS system architecture.

#### Additional subtypes for an Uncorrected error consumed at the node

For an error consumed at the node, a node might additionally define the following subtypes:

#### Restartable

The error has not been silently propagated. The node has halted operation because it has consumed an error. The node does not rely on the corrupted data, so it can continue to operate without repairing the error.

#### Recoverable

The error has not been silently propagated. The node has halted operation. The node is reliant on consuming the corrupted data to continue. If software can locate and repair the error, the halted operation can continue.

If these subtypes are implemented, then the Unrecoverable subtype further indicates that the node cannot resume from its halted state.

ARM deprecates the implementation of the Restartable and Recoverable UE types for nodes other than consumer nodes with PE-like behavior. That is, nodes that process data that can support the concept of being restarted after halting because of an Uncorrected error.

### 3.1.5 Software faults

Software fault handling is outside the scope of the RAS Extension. ARM recommends that components raise an error recovery interrupt in response to a detected software fault.

## 3.2 Standard error record

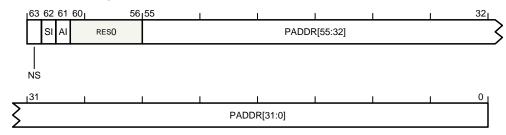

The RAS Extension defines a standard error record and a mechanism to access error records as System registers or as a memory-mapped component. The standard error record contains:

- The <u>ERR<n>CTLR</u> register to control common features, and an identification mechanism for these controls.

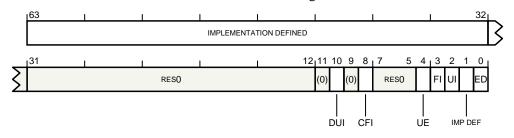

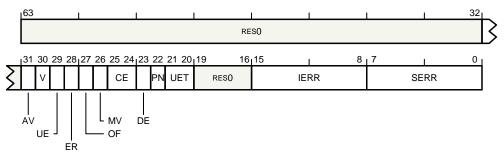

- A status register, <u>ERR<n>STATUS</u>, for common status fields, such as the type and coarse characterization of the error.

- An optional address register, <u>ERR<n>ADDR</u>.

- An identification register, <u>ERR<n>FR</u>, that describes the implemented features.

- IMPLEMENTATION DEFINED status registers, <u>ERR<n>MISC0</u> and <u>ERR<n>MISC1</u>. ARM recommends these are used for:

- Identifying a FRU.

- Locating the error within the FRU.

- Optional Corrected Error counters for software to poll the rate of Corrected errors.

An error record can also include additional IMPLEMENTATION DEFINED controls and identification registers.

Error records are accessed through groups of error records, corresponding to one or more nodes. This group might be sparse and error records that are not implemented in a group of error records have an ERR < n > FR register that reads as zero.

Error records can be accessed using System registers or as a memory-mapped component:

- <u>Error record System register view</u> defines an architectural format for a group of error records, accessed using System registers.

- <u>Memory-mapped view</u> defines a reusable format for a memory-mapped group of error records.

— Use of the reusable format is OPTIONAL.

Error records must be preserved over Error Recovery reset. This allows for a diagnosis after system failure.

#### 3.2.1 Nodes

The architecture defines the following common features for a node:

#### **Error detection and correction**

The level of error correction and detection implemented at a node is IMPLEMENTATION DEFINED. A node might include a control to disable error reporting and logging of detected errors, for example while software initializes the node. It is IMPLEMENTATION DEFINED whether the node fully disables error detection and correction when reporting and logging are disabled.

#### Fault handling interrupt

This is the asynchronous reporting of all or some detected errors by an interrupt, that is, all Corrected errors, Deferred errors, and Uncorrected errors. It is IMPLEMENTATION DEFINED whether a node provides a single control for all errors, or a first control for Corrected errors and a second control for all other detected errors.

See also Fault handling interrupt and RAS System Architecture.

#### **Corrected error counting**

It is IMPLEMENTATION DEFINED whether a node that implements error correction implements a counter for counting Corrected errors. Software might poll the error counter or initialize the counter with a threshold value and receive an interrupt when the counter overflows. A counter overflows when incrementing the counter results in unsigned integer overflow.

It is IMPLEMENTATION DEFINED which Corrected errors are counted.

It is IMPLEMENTATION DEFINED and might be UNPREDICTABLE whether Deferred and Uncorrected errors are counted by the Corrected error counter.

See also Standard format Corrected error counter.

#### In-band Uncorrected error signaling (external aborts)

This is the in-band signaling of detected Uncorrected errors to the consumer of the error. It is also referred to as an external abort. Corrected errors and Deferred errors are not reported by such means.

#### Uncorrected error recovery and handling interrupt

This is the asynchronous (out-of-band) reporting of detected Uncorrected errors by an interrupt. The interrupt can be used for error recovery, fault handling, or both. Corrected errors are not reported by this means. It is IMPLEMENTATION DEFINED whether the node provides a control to enable Deferred errors to be reported in this way. If the control is not provided, Deferred errors are not reported by this means.

The error recovery interrupt is generated even if the error syndrome is discarded because the error record already records a higher priority error.

#### Records

A node implements one or more records. When an error is detected, syndrome about the error is written to a record.

A node might implement some or all of these features, and, if implemented, might implement controls to enable or disable the features in <u>ERR<n>CTLR</u>.

For each node, it is IMPLEMENTATION DEFINED whether the fault and error reporting mechanisms apply to both reads and writes, or whether the mechanisms can be individually controlled for reads and writes.

### 3.2.2 Multiple records per node

Each node contains at least one error record. A node might implement multiple error records for one or more of the following purposes:

- To record different types of error in different records.

- To record errors from different sources in different records.

- To record multiple errors.

The multiple error records used by a single node are sequentially indexed. Each record other than the first record has an ERR < n > FR register that reads as zero, and the value in ERR < n > CTLR for each record other than the first record is RES0.

### 3.2.3 Writing the error record

When a new error is detected, the node:

- Modifies <u>ERR<n>STATUS</u>.{<u>CE</u>, <u>DE</u>, <u>UE</u>, <u>UET</u>} to indicate the type of the new detected error. See <u>Prioritizing errors</u>.

- Does one of the following:

- Overwrites the error record with the syndrome for the new error, if it is of a higher priority than the previous highest priority recorded error.

- Keeps the syndrome for the previous error, if the new error is of a lower priority than the

previous highest priority recorded error or if it has the same priority as the previous highest

priority recorded error.

- Counts the error, if it is a Corrected Error and a counter is implemented. It is IMPLEMENTATION DEFINED and might be UNPREDICTABLE whether Deferred and Uncorrected errors are counted by the Corrected error counter.

#### **Prioritizing errors**

The highest priority recorded error type is recorded in the <u>ERR<n>STATUS</u>. {<u>CE</u>, <u>DE</u>, <u>UE</u>, <u>UET</u>} fields, as shown in <u>Table 2</u>.

|              |         | ERR <n>STA</n> | TUS fields |         |                                                                     |          |

|--------------|---------|----------------|------------|---------|---------------------------------------------------------------------|----------|

| $\mathbf{V}$ | CE      | DE             | UE         | UET     | Highest priority error type                                         | Mnemonic |

| 0            | UNKNOWN | UNKNOWN        | UNKNOWN    | UNKNOWN | None                                                                | -        |

| 1            | 0b00    | 0              | 0          | UNKNOWN | _                                                                   |          |

| 1            | != 0b00 | 0              | 0          | UNKNOWN | Corrected error                                                     | CE       |

| 1            | Х       | 1              | 0          | UNKNOWN | Deferred error                                                      | DE       |

| 1            | Х       | Х              | 1          | 0b10    | <u>Uncorrected</u> : <u>Latent</u> or<br><u>Restartable</u> error   | UEO      |

| 1            | Х       | Х              | 1          | 0b11    | <u>Uncorrected</u> : <u>Signaled</u> or<br><u>Recoverable</u> error | UER      |

| 1            | Х       | Х              | 1          | 0b01    | Uncorrected: Unrecoverable<br>error                                 | UEU      |

| 1            | Х       | Х              | 1          | 0000    | <u>Uncorrected</u> : <u>Uncontainable</u><br>error                  | UC       |

Table 2: Encoding the highest priority error

Overwriting depends on the type of the previous highest priority error and on the type of the newly recorded error, as shown in Table 3.

In <u>Table 3</u>, the row and column headings use the mnemonics from <u>Table 2</u> and the following additional abbreviations are used:

- **K** Keep. Keep the previous error syndrome. It is IMPLEMENTATION DEFINED whether <u>ERR<n>STATUS.OF</u> is set to 1 or unchanged.

- **O** Overflow. Keep the previous error syndrome and set <u>ERR<n>STATUS.OF</u> to 1.

- W Overwrite. Record the new error syndrome. It is IMPLEMENTATION DEFINED whether <u>ERR<n>STATUS.OF</u> is set to 0 or unchanged.

- **CK** Count and keep. Count CE if a counter is implemented, and keep the previous error syndrome. If the counter overflows, or if no counter is implemented, it is IMPLEMENTATION DEFINED whether <u>ERR<n>STATUS.OF</u> is set to 1 or unchanged.

- **CWK** Count and overwrite or keep. The behavior is IMPLEMENTATION DEFINED and described by the value of <u>ERR<n>FR.CEO</u>:

- 0 Count CE if a counter is implemented. Keep the previous error syndrome. If the counter overflows, or if no counter is implemented, <u>ERR<n>STATUS.OF</u> is set to 1.

- 1 Count CE. If <u>ERR<n>STATUS.OF</u> == 1 before the CE is counted, keep the previous syndrome. Otherwise record the new error syndrome.

If the counter overflows, or if no counter is implemented, <u>ERR<n>STATUS.OF</u> is set to 1.

- **CW** Count and overwrite. Count CE if a counter is implemented, and overwrite. If a counter is implemented and the counter overflows, <u>ERR<n>STATUS.OF</u> is set to an UNKNOWN value. Otherwise, it is IMPLEMENTATION DEFINED whether <u>ERR<n>STATUS.OF</u> is set to 0 or unchanged.

- **WO** Overwrite and overflow. <u>ERR<n>STATUS.OF</u> is set to 1.

#### ARM® Reliability, Availability, and Serviceability (RAS) Specification

— Note –

One of <u>ERR<n>STATUS</u>.{<u>CE</u>, <u>DE</u>, <u>UE</u>} is set or modified even if the new error syndrome is discarded.

It is IMPLEMENTATION DEFINED and might be UNPREDICTABLE whether Deferred and Uncorrected errors are counted by the Corrected error counter. If counting a Deferred or Uncorrected error causes the counter to overflow, then <u>ERR<n>STATUS.OF</u> is set as it would be for a Corrected error that causes counter overflow. However, if the architecture requires that recording a Deferred or Uncorrected error sets the <u>ERR<n>STATUS.OF</u> flag, then this flag must be set even if the error is counted and the counter does not overflow.

| Previous   | New detected error type |    |     |     |     |    |

|------------|-------------------------|----|-----|-----|-----|----|

| error type | CE                      | DE | UEO | UER | UEU | UC |

| -          | CW                      | W  | W   | W   | W   | W  |

| СЕ         | CWK                     | W  | W   | W   | W   | W  |

| DE         | CK                      | 0  | W   | W   | W   | W  |

| UEO        | СК                      | Κ  | 0   | WO  | WO  | WO |

| UER        | СК                      | Κ  | 0   | 0   | WO  | WO |

| UEU        | СК                      | Κ  | 0   | 0   | 0   | WO |

| UC         | СК                      | Κ  | 0   | 0   | 0   | 0  |

Table 3: Rules for overwriting error records

#### Overwriting the error syndrome

When an old record is overwritten:

- Bits shown as X in <u>Table 2</u> for the new error are unchanged.

- The <u>ERR<n>STATUS</u>.{<u>ER</u>, <u>PN</u>, <u>IERR</u>, <u>SERR</u>} syndrome fields are written with the syndrome for the new error.

- If there is an address syndrome for the new error, <u>ERR<n>STATUS.AV</u> is set to 1 and the address is written to <u>ERR<n>ADDR</u>. Otherwise <u>ERR<n>STATUS.AV</u> is set to 0.

- If there is other miscellaneous syndrome for the new error, it is written to the <u>ERR<n>MISC0</u> or <u>ERR<n>MISC1</u> registers and <u>ERR<n>STATUS.MV</u> is set to 1.

- If there is no additional miscellaneous syndrome for the new error written to the <u>ERR<n>MISC0</u> or <u>ERR<n>MISC1</u> registers, then it is IMPLEMENTATION DEFINED whether <u>ERR<n>STATUS.MV</u> is set to 0 or unchanged.

- If software can determine from the <u>ERR<n>MISC0</u> and <u>ERR<n>MISC1</u> contents that the syndrome is not related to the highest priority error, the MV bit is unchanged.

- Otherwise the MV bit is cleared to zero.

- <u>ERR<n>STATUS.V</u> is set to 1.

#### Keeping the previous error syndrome

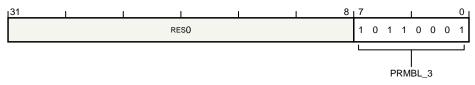

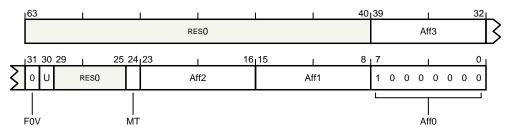

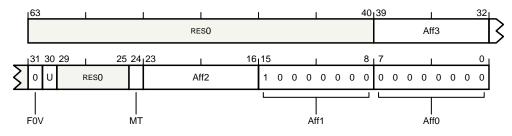

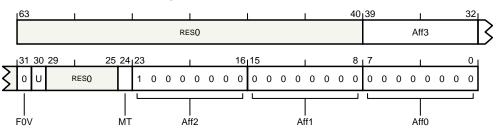

When an old record is kept: