# arm

## Arm<sup>®</sup> Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME), for Armv9-A

| Document number            | DDI0616                                  |

|----------------------------|------------------------------------------|

| Document quality           | EAC                                      |

| Document version           | A.a                                      |

| Document confidentiality   | Non-confidential                         |

| Document build information | a950072 Monday, 7 February 2022 at 11:07 |

Copyright © 2022 Arm Limited or its affiliates. All rights reserved.

## Arm® Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME), for Armv9-A

## **Release information**

## **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks

Copyright © 2022 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349 version 21.0

#### **Product Status**

The information in this document is final; that is, it is for a developed product.

The information in this Manual is at EAC quality, which means that:

- All features of the specification are described in the manual.

- Information can be used for software and hardware development.

## Arm<sup>®</sup> Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME), for Armv9-A

|            | Arm® Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME),                       |

|------------|-----------------------------------------------------------------------------------------------------------|

|            | for Armv9-A                                                                                               |

|            | Non-Confidential Proprietary Notice                                                                       |

|            |                                                                                                           |

| Preface    |                                                                                                           |

|            | About this supplement                                                                                     |

|            | Conventions                                                                                               |

|            | Typographical conventions                                                                                 |

|            | Numbers xi                                                                                                |

|            | Pseudocode descriptions xi                                                                                |

|            | Asterisks in instruction mnemonics                                                                        |

|            | Assembler syntax descriptions                                                                             |

|            | Rules-based writing                                                                                       |

|            | Identifiers                                                                                               |

|            |                                                                                                           |

|            | Additional reading                                                                                        |

|            | <b>— — — —</b>                                                                                            |

|            | Progressive terminology commitment                                                                        |

|            |                                                                                                           |

|            | duction                                                                                                   |

| Chapter A1 | SME Introduction           A1.1         About the Scalable Matrix Extension (SME)         18              |

| Chapter A2 | Architecture Features and Extensions         A2.1       Extensions and features defined by SME         19 |

|            | A2.2 Changes to existing features and extension requirements                                              |

|            |                                                                                                           |

| Part B SME | application level programmers' model                                                                      |

| Chapter B1 | Application processing modes                                                                              |

|            | B1.1 Overview                                                                                             |

|            | B1.1.1 Process state                                                                                      |

| Chapter B2 | Architectural state                                                                                       |

| -          | B2.1 Architectural state summary                                                                          |

|            | B2.2 SME ZA storage 28                                                                                    |

|            | B2.2.1 ZA array vector access                                                                             |

|            | B2.2.2 ZA tile access                                                                                     |

|            | B2.2.3 Accessing an 8-bit element ZA tile                                                                 |

|            | B2.2.4 Accessing a 16-bit element ZA tile                                                                 |

B2.2.5

B2.2.6

31

32

**Chapter B3**

|       | B2.2.7   | Accessing a 128-bit element ZA tile               | 32 |

|-------|----------|---------------------------------------------------|----|

| B2.3  | ZA sto   | prage layout                                      | 34 |

|       | B2.3.1   | ZA array vector and tile slice mappings           | 34 |

|       | B2.3.2   | Tile mappings                                     | 34 |

|       | B2.3.3   | Horizontal tile slice mappings                    | 36 |

|       | B2.3.4   | Vertical tile slice mappings                      | 36 |

|       | B2.3.5   | Mixed horizontal and vertical tile slice mappings | 37 |

| Float | ting-poi | nt behaviors                                      |    |

| B3.1  | Överv    | iew                                               | 39 |

|       | B3.1.1   | Extended BFloat16                                 | 39 |

|       | B3.1.2   | BFloat16 behaviors                                | 39 |

|       | B3.1.3   | Floating-point behaviors in Streaming SVE mode    | 41 |

|       | B3.1.4   | ZA-targeting floating-point behaviors             | 41 |

## Part C SME system level programmers' model

## Chapter C1 Introduction

| Chapter C2 | Syst | em man  | agement                                                 |

|------------|------|---------|---------------------------------------------------------|

|            | C2.1 | Over    | <i>r</i> iew                                            |

|            |      | C2.1.1  | Identification                                          |

|            |      | C2.1.2  | Traps and exceptions                                    |

|            |      | C2.1.3  | Vector lengths                                          |

|            |      | C2.1.4  | Streaming execution priority                            |

|            | C2.2 | Proce   | essor behavior                                          |

|            |      | C2.2.1  | Exception priorities                                    |

|            |      | C2.2.2  | Synchronous Data Abort                                  |

|            |      | C2.2.3  | Validity of SME and SVE state                           |

|            |      | C2.2.4  | Streaming execution priority for shared implementations |

|            |      | C2.2.5  | Security considerations                                 |

|            | C2.3 | Chan    | ges to existing System registers                        |

|            |      | C2.3.1  | ID_AA64PFR1_EL1                                         |

|            |      | C2.3.2  | ID_AA64ZFR0_EL1                                         |

|            |      | C2.3.3  | CPACR_EL1                                               |

|            |      | C2.3.4  | CPTR_EL2                                                |

|            |      | C2.3.5  | CPTR_EL3 55                                             |

|            |      | C2.3.6  | HCR_EL2                                                 |

|            |      | C2.3.7  | HCRX_EL2                                                |

|            |      | C2.3.8  | SCR_EL3                                                 |

|            |      | C2.3.9  | SCTLR_EL1                                               |

|            |      | C2.3.10 | SCTLR_EL2                                               |

|            |      | C2.3.11 | HFGRTR_EL2                                              |

|            |      | C2.3.12 | HFGWTR_EL2 56                                           |

|            |      | C2.3.13 | ESR_EL1, ESR_EL2, and ESR_EL3 56                        |

|            |      | C2.3.14 | ZCR_EL1, ZCR_EL2, and ZCR_EL3                           |

|            | C2.4 | SME-    | specific System registers 58                            |

|            |      | C2.4.1  | ID_AA64SMFR0_EL1                                        |

|            |      | C2.4.2  | SMCR_EL1                                                |

|            |      | C2.4.3  | SMCR_EL2                                                |

|            |      | C2.4.4  | SMCR_EL3 58                                             |

|            |      | C2.4.5  | SVCR 58                                                 |

|            |      | C2.4.6  | SMPRI_EL1                                               |

|            |      | C2.4.7  | SMPRIMAP_EL2                                            |

|            | C2.4.8 SMIDR_EL1                                           |  |

|------------|------------------------------------------------------------|--|

| Chapter C3 | Interaction with other Armv9-A architectural features      |  |

| •          | C3.1 Overview                                              |  |

|            | C3.2 Other architectural features                          |  |

|            | C3.2.1 Watchpoints                                         |  |

|            | C3.2.2 Self-hosted debug                                   |  |

|            | C3.2.3 External debug                                      |  |

|            | C3.2.4 Memory Tagging Extension (MTE)                      |  |

|            | C3.2.5 Reliability, Availability, and Serviceability (RAS) |  |

|            | C3.2.6 Memory Partitioning and Monitoring (MPAM)           |  |

|            | C3.2.7 Transactional Memory Extension (TME)                |  |

|            | C3.2.8 Memory consistency model                            |  |

|            |                                                            |  |

## Part D SME instruction set

Chapter D1

**SME instructions**

| D1.1 | SME     | data-processing instructions |

|------|---------|------------------------------|

|      | D1.1.1  | ADDHA                        |

|      | D1.1.2  | ADDSPL                       |

|      | D1.1.3  | ADDSVL                       |

|      | D1.1.4  | ADDVA                        |

|      | D1.1.5  | BFMOPA                       |

|      | D1.1.6  | BFMOPS                       |

|      | D1.1.7  | FMOPA (non-widening)         |

|      | D1.1.8  | FMOPA (widening)             |

|      | D1.1.9  | FMOPS (non-widening)         |

|      | D1.1.10 | FMOPS (widening)             |

|      | D1.1.11 | LD1B                         |

|      | D1.1.12 | LD1D                         |

|      | D1.1.13 | LD1H                         |

|      | D1.1.14 | LD1Q                         |

|      | D1.1.15 | LD1W                         |

|      | D1.1.16 | LDR                          |

|      | D1.1.17 | MOV (tile to vector)         |

|      | D1.1.18 | MOV (vector to tile)         |

|      | D1.1.19 | MOVA (tile to vector)        |

|      | D1.1.20 | MOVA (vector to tile)        |

|      | D1.1.21 | RDSVL                        |

|      | D1.1.22 | SMOPA 111                    |

|      | D1.1.23 | SMOPS                        |

|      | D1.1.24 | ST1B                         |

|      | D1.1.25 | ST1D                         |

|      | D1.1.26 | ST1H                         |

|      | D1.1.27 | ST1Q                         |

|      | D1.1.28 | ST1W                         |

|      | D1.1.29 | STR 125                      |

|      | D1.1.30 | SUMOPA                       |

|      | D1.1.31 | SUMOPS                       |

|      | D1.1.32 | UMOPA                        |

|      | D1.1.33 | UMOPS                        |

|      | D1.1.34 | USMOPA                       |

|      | D1.1.35 | USMOPS                       |

| D1.4<br>D1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D1.2.1       MSR (immediate)       140         D1.2.2       SMSTART       144         D1.2.3       SMSTOP       146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part E Appendices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter E1 Ins<br>E1. <sup>-</sup><br>E1.2<br>E1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | E1.1.1       Illegal Advanced SIMD instructions       158         E1.1.2       Illegal SVE instructions       166         Unimplemented SVE instructions       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter E2       SM         E2.1       E2.2         E2.2       E2.2         E2.3       E2.4         E2.4       E2.5         E2.5       E2.6         E2.6       E2.7         E2.7       E2.6         E2.7       E2.7         E2.7< | CheckFPAdvSIMDEnabled64       174         CheckNonStreamingSVEEnabled       174         CheckSMEAccess       174         CheckSMEAndZAEnabled       174         CheckSMEEnabled       174         CheckSMEEnabled       174         CheckSMEEnabled       175         CheckStreamingSVEAndZAEnabled       175         CheckStreamingSVEEnabled       175         O FPDot       175         1 FPDotAdd_ZA       177         2 FPMulAdd_ZA       177         3 FPProcessDenorms4       177         4 FPProcessNaNs4       177         5 HaveEBF16       178         6 HaveSME       178         7 HaveSMEF64F64       178         8 HaveSME116164       178         9 ImplementedSMEVectorLength       179         1 IsStreamingSVEEnabled       179         1 IsStreamingSVEEnabled       179         1 IsStreamingSVEEnabled       180         5 IsSVEEnabled       180         6 MaybeZeroSVEUppers       181         7 ResetSMEState       182         9 ResetSVEState       182         9 ResetSVEState       182         9 ResetSVEState       182         9 ResetSVESt |

Contents

|              | E2.32 SetP   | STATE_ZA                                                           |

|--------------|--------------|--------------------------------------------------------------------|

|              | E2.33 SME    | AccessTrap                                                         |

|              | E2.34 SVL    |                                                                    |

|              | E2.35 VL .   |                                                                    |

|              | E2.36 ZAhs   | lice                                                               |

|              | E2.37 ZAsli  | ce                                                                 |

|              | E2.38 ZAtile |                                                                    |

|              | E2.39 ZAve   | ctor                                                               |

|              | E2.40 ZAvs   | lice                                                               |

| Chapter E3   | System regi  | sters affected by SME                                              |

| •            |              | -Specific System registers                                         |

|              | E3.1.1       | ID AA64SMFR0 EL1, SME Feature ID register 0                        |

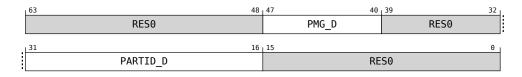

|              | E3.1.2       | MPAMSM_EL1, MPAM Streaming Mode Register                           |

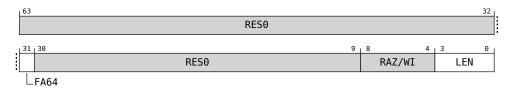

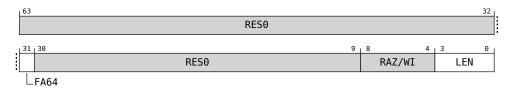

|              | E3.1.3       | SMCR_EL1, SME Control Register (EL1)                               |

|              | E3.1.4       | SMCR_EL2, SME Control Register (EL2)                               |

|              | E3.1.5       | SMCR_EL3, SME Control Register (EL3)                               |

|              | E3.1.6       | SMIDR_EL1, Streaming Mode Identification Register                  |

|              | E3.1.7       | SMPRI_EL1, Streaming Mode Priority Register                        |

|              | E3.1.8       | SMPRIMAP_EL2, Streaming Mode Priority Mapping Register 214         |

|              | E3.1.9       | SVCR, Streaming Vector Control Register                            |

|              | E3.1.10      | TPIDR2 EL0, EL0 Read/Write Software Thread ID Register 2 224       |

|              | E3.1.11      | EDHSR, External Debug Halt Status Register                         |

|              |              | ges to existing System registers                                   |

|              | E3.2.1       | CPACR EL1, Architectural Feature Access Control Register 231       |

|              | E3.2.2       | CPTR_EL2, Architectural Feature Trap Register (EL2)                |

|              | E3.2.3       | CPTR_EL3, Architectural Feature Trap Register (EL3)                |

|              | E3.2.4       | FAR EL1, Fault Address Register (EL1)                              |

|              | E3.2.5       | FAR EL2, Fault Address Register (EL2)                              |

|              | E3.2.6       | FAR EL3, Fault Address Register (EL3)                              |

|              | E3.2.7       | FPCR, Floating-point Control Register                              |

|              | E3.2.8       | HCRX_EL2, Extended Hypervisor Configuration Register               |

|              | E3.2.9       | HFGRTR_EL2, Hypervisor Fine-Grained Read Trap Register 285         |

|              | E3.2.10      | HFGWTR_EL2, Hypervisor Fine-Grained Write Trap Register 310        |

|              | E3.2.11      | ID_AA64ISAR1_EL1, AArch64 Instruction Set Attribute Register 1 330 |

|              | E3.2.12      | ID AA64PFR1 EL1, AArch64 Processor Feature Register 1 338          |

|              | E3.2.13      | ID AA64ZFR0 EL1, SVE Feature ID register 0                         |

|              | E3.2.14      | MPAM2 EL2, MPAM2 Register (EL2)                                    |

|              | E3.2.15      | SCR EL3, Secure Configuration Register                             |

|              | E3.2.16      | SCTLR_EL1, System Control Register (EL1)                           |

|              | E3.2.17      | SCTLR_EL2, System Control Register (EL2)                           |

|              | E3.2.18      | EDDEVID1, External Debug Device ID register 1                      |

| a <b>-</b> . |              | ,                                                                  |

|              |              |                                                                    |

Chapter E4

**Glossary terms**

## Preface

## About this supplement

IRFSSZThis supplement is the Arm® Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME),<br/>for Armv9-A.

ILZCVC This supplement describes the changes and additions introduced by SME to the Armv9-A architecture.

I<sub>CDMPR</sub>

• Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture [1]

For SME, this supplement is to be read with the following documents:

- Arm<sup>®</sup> Architecture Registers Armv9, for Armv9-A architecture profile [2]

- Arm<sup>®</sup> A64 Instruction Set Architecture Armv9, for Armv9-A architecture profile [3]

Together, the supplement and these documents provide a full description of the Armv9-A Scalable Matrix Extension.

This supplement is organized into parts:

• SME Application level programmers' model

Describes how the PE at an application level is altered by the implementation of SME.

• SME System level programmers' model

Describes how the PE at a system level is altered by the implementation of SME.

• SME instruction set

Describes the extensions made for SME to the A64 instruction set.

• Appendices

Provides reference information relating to the SME. This includes summarized information about the instruction set, imported shared pseudocode and System register data, and a glossary that defines terms used in this document that have a specialized meaning.

## Conventions

#### **Typographical conventions**

The typographical conventions are:

italic

Introduces special terminology, and denotes citations.

#### bold

Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace

Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for some common terms such as IMPLEMENTATION DEFINED.

Used for a few terms that have specific technical meanings, and are included in the Glossary.

#### Blue text

Indicates a link. This can be

- A cross-reference to another location within the document

- A URL, for example http://developer.arm.com

#### Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000. To improve readability, long numbers can be written with an underscore separator between every four characters, for example  $0xFFFF_0000_0000_0000$ . Ignore any underscores when interpreting the value of a number.

#### **Pseudocode descriptions**

This book uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font. The pseudocode language is described in the Arm Architecture Reference Manual.

#### Asterisks in instruction mnemonics

Some behavior descriptions in this manual apply to a group of similar instructions that start with the same characters. In these situations, an \* might be inserted at the end of a series of characters as a wildcard.

Preface Conventions

## Assembler syntax descriptions

This book contains numerous syntax descriptions for assembler instructions and for components of assembler instructions. These are shown in a monospace font.

## **Rules-based writing**

This specification consists of a set of individual rules. Each rule is clearly identified by the letter R.

Rules must not be read in isolation, and where more than one rule relating to a particular feature exists, individual rules are grouped into sections and subsections to provide the proper context. Where appropriate, these sections contain a short introduction to aid the reader. An implementation which is compliant with the architecture must conform to all of the rules in this specification.

Some architecture rules are accompanied by rationale statements which explain why the architecture was specified as it was. Rationale statements are identified by the letter X.

Some sections contain additional information and guidance that do not constitute rules. This information and guidance is provided purely as an aid to understanding the architecture. Information statements are clearly identified by the letter I.

Implementation notes are identified by the letter U.

Software usage descriptions are identified by the letter S.

Arm strongly recommends that implementers read *all* chapters and sections of this document to ensure that an implementation is compliant.

Rules, rationale statements, information statements, implementation notes and software usage statements are collectively referred to as *content items*.

#### **Identifiers**

Each content item may have an associated identifier which is unique within the context of this specification.

When the document is prior to beta status:

• Content items are assigned numerical identifiers, in ascending order through the document (0001, 0002, ...).

• Identifiers are volatile: the identifier for a given content item may change between versions of the document.

After the document reaches beta status:

- Content items are assigned random alphabetical identifiers (HJQS, PZWL, ...).

- Identifiers are preserved: a given content item has the same identifier across versions of the document.

#### **Examples**

Below are examples showing the appearance of each type of content item.

- R<sub>BNPWG</sub> This is a rule statement.

- $I_{RSPLN}$  This is an information statement.

- D<sub>DDYRY</sub> This is a term, syntax, data structure, or encoding description.

- G<sub>PBGWT</sub> This is a goal statement.

## **Additional reading**

This section lists publications by Arm and by third parties.

See Arm Developer (http://developer.arm.com) for access to Arm documentation.

[1] Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture. (ARM DDI 0487) Arm Ltd.

[2] Arm<sup>®</sup> Architecture Registers Armv9, for Armv9-A architecture profile. (ARM DDI 0601) Arm Ltd.

[3] Arm<sup>®</sup> A64 Instruction Set Architecture Armv9, for Armv9-A architecture profile. (ARM DDI 0602) Arm Ltd.

[4] Arm<sup>®</sup> Architecture Reference Manual Supplement Armv9, for A-profile architecture. (ARM DDI 0608) Arm Ltd.

[5] *Arm<sup>®</sup> Reliability, Availability, and Serviceability (RAS) Specification, for A-profile architecture.* (ARM DDI 0587) Arm Ltd.

[6] Arm<sup>®</sup> Architecture Reference Manual Supplement, Memory System Resource Partitioning and Monitoring (MPAM), for A-profile architecture. (ARM DDI 0598) Arm Ltd.

## Feedback

Arm welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title (Arm® Architecture Reference Manual Supplement, The Scalable Matrix Extension (SME), for Armv9-A).

- The number (DDI0616 A.a).

- The page numbers to which your comments apply.

- The rule identifiers to which your comments apply, if applicable.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

#### Note

Arm tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

## Progressive terminology commitment

Arm values inclusive communities. Arm recognizes that we and our industry have used terms that can be offensive. Arm strives to lead the industry and create change.

We believe that this document contains no offensive terms. If you find offensive terms in this document, please contact terms@arm.com.

Part A Introduction

## Chapter A1 SME Introduction

## A1.1 About the Scalable Matrix Extension (SME)

I<sub>YVCPK</sub> The Scalable Matrix Extension (SME) defines architectural state capable of holding two-dimensional matrix tiles, and a Streaming SVE mode which supports execution of SVE2 instructions with a vector length that matches the tile width, along with instructions that accumulate the outer product of two vectors into a tile, as well as load, store, and move instructions that transfer a vector to or from a tile row or column. The extension also defines System registers and fields that identify the presence and capabilities of SME, and enable and control its behavior at each Exception level.

$I_{SQCGB}$  Unless otherwise specified by this document, the behaviors of instructions and architectural state when the PE is in *Streaming SVE mode* are as described in *Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture* [1].

## Chapter A2 Architecture Features and Extensions

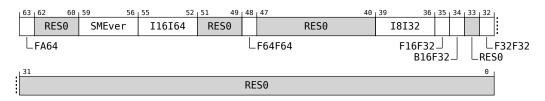

## A2.1 Extensions and features defined by SME

The Scalable Matrix Extension (SME) inherits the rules for architectural features and extensions from Armv9-A *Arm<sup>®</sup> Architecture Reference Manual for A-profile architecture* [1]. This specification describes changes to those rules, and defines any features added by SME.

R<sub>PDXHJ</sub> An architecture extension, the Scalable Matrix Extension (SME), is introduced. SME is represented by the feature FEAT\_SME.

R<sub>QFSVK</sub> SME is an OPTIONAL extension from Armv9.2-A.

$I_{VQCZZ}$  The following list summarizes the OPTIONAL SME features:

- FEAT\_SME\_FA64: Support the full A64 instruction set in *Streaming SVE mode*.

- FEAT\_SME\_F64F64: Double-precision floating-point outer product instructions.

- FEAT\_SME\_I16I64: 16-bit to 64-bit integer widening outer product instructions.

- FEAT\_EBF16: Support for Extended BFloat16 mode.

## A2.2 Changes to existing features and extension requirements

R<sub>DSHWS</sub> If SME is implemented, the following features that are not already mandatory in Armv9.1 are also implemented:

• FEAT\_HCX.

Part B SME application level programmers' model

## Chapter B1 Application processing modes

## **B1.1 Overview**

SME extends the AArch64 application level programmers' model with added processing modes and related instructions, architectural state, and registers:

- The PSTATE.SM control to enable an execution mode, known as *Streaming SVE mode*.

- The PSTATE.ZA control to enable access to SME ZA storage.

- The Special-purpose register, SVCR, which provides read/write access to PSTATE.SM and PSTATE.ZA from any Exception level.

- The SMSTART and SMSTOP instructions, aliases of MSR (immediate) instructions, that can set or clear PSTATE.SM, PSTATE.ZA, or both PSTATE.SM and PSTATE.ZA from any Exception level.

#### B1.1.1 Process state

- DXDPXSA PE that implements SME has a Streaming SVE mode.DJYVLMStreaming SVE register state is the vector registers Z0-Z31 and predicate registers P0-P15 that may be accessed by<br/>SME, SVE, Advanced SIMD, and floating-point instructions when the PE is in Streaming SVE mode.DDMZFRStreaming SVE register state includes the SVE FFR predicate register if FEAT\_SME\_FA64 is implemented and<br/>enabled at the current Exception level.LXXKGVIf SME is implemented, a PE has the following additional architectural state:

- Streaming SVE vector and predicate register state.

- SME ZA storage.

## Chapter B1. Application processing modes B1.1. Overview

| I <sub>ZTTNW</sub> | A PE enters Streaming SVE mode to access Streaming SVE vector and predicate register state.                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>NXQFB</sub> | If SME is implemented, this does not imply that FEAT_SVE and FEAT_SVE2 are implemented by the PE when it is not in <i>Streaming SVE mode</i> .                                                                                                                                                                                                                                                                                                          |

| I <sub>rntpx</sub> | When the PE is in <i>Streaming SVE mode</i> , a different set of vector lengths might be available for SVE instructions, as specified in C2.1.3 <i>Vector lengths</i> .                                                                                                                                                                                                                                                                                 |

| I <sub>TDSPN</sub> | When the PE is in <i>Streaming SVE mode</i> , the performance characteristics of some instructions may be significantly reduced, as specified in E1.3 <i>Reduced performance in Streaming SVE mode</i> .                                                                                                                                                                                                                                                |

| I <sub>nwfqx</sub> | SME extends a PE's <i>Process state</i> or PSTATE with the SM and ZA fields, which control the execution mode, <i>Streaming SVE mode</i> , and access to SME ZA storage, respectively. These PSTATE fields can be modified by the SMSTART and SMSTOP instructions, and can also be read and written using the SVCR register.                                                                                                                            |

| I <sub>dvpdl</sub> | The SMSTART instruction is used to enter <i>Streaming SVE mode</i> , or to enable the SME ZA storage, or both simultaneously.                                                                                                                                                                                                                                                                                                                           |

| I <sub>QQZTL</sub> | The SMSTOP instruction is used to exit Streaming SVE mode, or to disable the SME ZA storage, or both simultaneously.                                                                                                                                                                                                                                                                                                                                    |

| I <sub>NKJKL</sub> | After entering <i>Streaming SVE mode</i> , subsequent SMSTART and SMSTOP instructions might be used to enable and disable the ZA storage for different phases of execution within <i>Streaming SVE mode</i> , before using a final SMSTOP instruction to exit <i>Streaming SVE mode</i> .                                                                                                                                                               |

| D <sub>rsypb</sub> | SME instructions are the instructions defined by the SME architecture in Chapter D1 SME instructions.                                                                                                                                                                                                                                                                                                                                                   |

| $D_{LSJBN}$        | SME data-processing instructions are the instructions defined in D1.1 SME data-processing instructions.                                                                                                                                                                                                                                                                                                                                                 |

| $D_{\rm NHNFF}$    | A <i>legal</i> instruction is an implemented instruction which can be executed by a PE when PSTATE.SM and PSTATE.ZA are in the required state, unless its execution at this Exception level is prevented by a configurable trap or enable.                                                                                                                                                                                                              |

| D <sub>hzfsg</sub> | An <i>illegal</i> instruction is an implemented instruction whose attempted execution by a PE when PSTATE.SM and PSTATE.ZA are not in the required state will cause an SME illegal instruction exception to be taken, unless its execution at this Exception level is prevented by a higher-priority configurable trap or enable.                                                                                                                       |

| I <sub>PSNCC</sub> | When the PE is in <i>Streaming SVE mode</i> :                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | <ul> <li>SME data-processing instructions that do not access the SME ZA storage are <i>legal</i>.</li> <li>SME data-processing instructions that access SME ZA storage are <i>legal</i>, if SME ZA storage is enabled.</li> </ul>                                                                                                                                                                                                                       |

| I <sub>CKSBS</sub> | When the PE is in <i>Streaming SVE mode</i> and FEAT_SME_FA64 is not implemented or not enabled at the current Exception level:                                                                                                                                                                                                                                                                                                                         |

|                    | <ul> <li>Most Advanced SIMD instructions become <i>illegal</i>, as described in E1.1.1 <i>Illegal Advanced SIMD instructions</i>.</li> <li>Some SVE and SVE2 instructions become <i>illegal</i>, as described in E1.1.2 <i>Illegal SVE instructions</i>.</li> <li>Most other instructions implemented by the PE, including scalar floating-point instructions, remain <i>legal</i>.</li> </ul>                                                          |

| I <sub>DGNQM</sub> | When the PE is not in <i>Streaming SVE mode</i> :                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | <ul> <li>SME data-processing instructions that access SVE vector registers <i>Z0-Z31</i> and predicate registers <i>P0-P15</i> are <i>illegal</i>.</li> <li>SME LDR, STR, and ZERO instructions that access the SME ZA storage are <i>legal</i> if ZA is enabled.</li> <li>The MSR and MRS instructions that directly access the SME SVCR register are <i>legal</i>.</li> <li>All other instructions implemented by the PE are <i>legal</i>.</li> </ul> |

| I <sub>HDWMG</sub> | When the SME ZA storage is not enabled:                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | <ul><li>SME data-processing instructions that access SME ZA storage are <i>illegal</i>.</li><li>There is no effect on other instructions implemented by the PE.</li></ul>                                                                                                                                                                                                                                                                               |

|                    | See also:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | • SVCR                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

• ESR\_EL1, ESR\_EL2, and ESR\_EL3

Chapter B1. Application processing modes B1.1. Overview

- MSR (immediate)

- SMSTART

- SMSTOP

- C2.1.3 Vector lengths

- C2.2.3 Validity of SME and SVE state

- Chapter E1 Instructions affected by SME

#### B1.1.1.1 PSTATE.SM

The value of PSTATE.SM can be changed by executing the MSR instructions that access the SVCR. For more information, IYYOJK see B1.1.1.3 Changing PSTATE.SM and PSTATE.ZA. The PE is in *Streaming SVE mode* when the Effective value of PSTATE.SM is 1. D<sub>PRGHY</sub> When the PE is in *Streaming SVE mode*: R<sub>QGXCF</sub> • Streaming SVE register state is valid. • SME data-processing instructions which access any of the SVE registers Z0-Z31 and P0-P15 are legal. • Legal instructions which access SVE or SIMD&FP registers will access Streaming SVE register state. The SVE FFR predicate register is not architecturally visible when the PE is in Streaming SVE mode if IYDRPH FEAT SME FA64 is not implemented or not enabled at the current Exception level. When the PE is in Streaming SVE mode and FEAT\_SME\_FA64 is not implemented or not enabled at the current R<sub>GBNWK</sub> Exception level: • Most Advanced SIMD instructions are *illegal*, as described in E1.1.1 *Illegal Advanced SIMD instructions*. • Some SVE and SVE2 instructions are *illegal*, as described in E1.1.2 *Illegal SVE instructions*. The PE is not in Streaming SVE mode when the Effective value of PSTATE. SM is 0. D<sub>DVDTY</sub> When the PE is not in *Streaming SVE mode*: R<sub>CSSWX</sub> • Streaming SVE register state is not valid. Instructions which access SVE or SIMD&FP registers will access the Non-streaming SVE or SIMD&FP register state. • SME data-processing instructions which access any of the SVE registers Z0-Z31 and P0-P15 are illegal. When the Effective value of PSTATE.SM is changed by any means from 0 to 1, an entry to Streaming SVE mode is R<sub>RSWFQ</sub> performed, and each implemented bit of SVE registers Z0-Z31, P0-P15, and FFR in the new mode is set to zero. When the Effective value of PSTATE.SM is changed by any means from 1 to 0, an exit from Streaming SVE mode is R<sub>KFRQZ</sub> performed, and each implemented bit of SVE registers Z0-Z31, P0-P15, and FFR in the new mode is set to zero. When the Effective value of PSTATE.SM is changed by any means from 0 to 1, or from 1 to 0, the FPSR is set to the R<sub>MHTLZ</sub> value 0x0000\_0000\_0800\_009f, in which all of the cumulative status bits are set to 1. Statements which refer to the value of the SVE vector registers, Z0-Z31, implicitly also refer to the lower bits I<sub>YTZVD</sub> of those registers accessed by the SIMD&FP register names V0-V31, Q0-Q31, D0-D31, S0-S31, H0-H31, and BO-B31. See also: • SVCR • C2.1.2 Traps and exceptions

#### B1.1.1.2 PSTATE.ZA

- IGJZLDThe value of PSTATE.ZA can be changed by executing the MSR instructions that access the SVCR. For more information,<br/>see B1.1.1.3 Changing PSTATE.SM and PSTATE.ZA.

- D<sub>HBFWD</sub> The SME ZA storage is enabled when PSTATE.ZA is 1.

## Chapter B1. Application processing modes B1.1. Overview

| R <sub>sfwmy</sub> | When ZA storage is enabled:                                                                                                                                                                                                                                                                                                                       |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>The contents of <i>ZA</i> storage is valid and will be retained by hardware irrespective of whether the PE is in <i>Streaming SVE mode</i>.</li> <li>SME data-processing instructions which access the <i>ZA</i> storage are <i>legal</i> and may be executed, unless execution is prevented by some other trap or exception.</li> </ul> |

| D <sub>VLMFC</sub> | The SME ZA storage is disabled when PSTATE.ZA is 0.                                                                                                                                                                                                                                                                                               |

| R <sub>JHMYL</sub> | When ZA storage is disabled:                                                                                                                                                                                                                                                                                                                      |

|                    | <ul><li>The contents of <i>ZA</i> storage is not valid.</li><li>SME data-processing instructions which access the <i>ZA</i> storage are <i>illegal</i>.</li></ul>                                                                                                                                                                                 |

| R <sub>yrzrm</sub> | When PSTATE.ZA is changed by any means from 0 to 1, all implemented bits of the SME ZA storage are set to zero.                                                                                                                                                                                                                                   |

| I <sub>lrdzr</sub> | There is no architecturally defined effect on the SME ZA storage when PSTATE.ZA is changed from 1 to 0, because the contents of ZA storage cannot be observed when PSTATE.ZA is 0.                                                                                                                                                                |

| I <sub>QWCJS</sub> | When PSTATE.ZA is changed from 0 to 1, or 1 to 0, there is no effect on the SVE vector and predicate registers and the FPSR if PSTATE.SM is not changed.                                                                                                                                                                                          |

|                    | See also:                                                                                                                                                                                                                                                                                                                                         |

|                    |                                                                                                                                                                                                                                                                                                                                                   |

SVCRC2.1.2 *Traps and exceptions*

## B1.1.1.3 Changing PSTATE.SM and PSTATE.ZA

- D<sub>QRSXV</sub> The MSR (immediate) instructions, MSR SVCRSM, #<imm1>, MSR SVCRZA, #<imm1>, and MSR SVCRSMZA, #<imm1>, are provided to independently set or clear PSTATE.SM, PSTATE.ZA, or both PSTATE.SM and PSTATE.ZA respectively.

- R<sub>MPOWY</sub> MSR SVCRSM, MSR SVCRZA, and MSR SVCRSMZA instructions are permitted to be executed from any Exception level.

- L<sub>SZYBC</sub> Access to svcr through the MRS and MSR (register) instructions might be used where a calling convention or ABI requires save/restore of current state, and are permitted to be executed from any Exception level. However, the MSR (immediate) instructions might be higher performance than the MSR (register) instruction, so the MSR (immediate) instructions should be preferred for explicit changes to PSTATE.SM and PSTATE.ZA.

- DYGDXX The SMSTART instruction is the preferred alias of the MSR SVCRSM, #1, MSR SVCRZA, #1, and MSR SVCRSMZA, #1 instructions.

- D<sub>DZTDH</sub> The smstop instruction is the preferred alias of the msr svcrsm, #0, msr svcrza, #0, and msr svcrsmza, #0 instructions.

- I<sub>HNNJR</sub> The PE might consume less power when pSTATE.SM is 0 and pSTATE.ZA is 0.

See also:

- SVCR

- MSR (immediate)

- SMSTART

- SMSTOP

## Chapter B2 Architectural state

## **B2.1** Architectural state summary

D<sub>XJCGQ</sub> The Effective Streaming SVE vector length, SVL, is a power of two in the range 128 to 2048 bits inclusive.

I<sub>NBPPM</sub> When the PE is in *Streaming SVE mode*, the Effective SVE vector length, VL, is equal to SVL.

This might be different from the value of VL when the PE is not in *Streaming SVE mode*, as described in C2.1.3 *Vector lengths*.

D<sub>JBVYJ</sub> In a vector of SVL bits:

- SVL<sub>B</sub> is the number of 8-bit elements.

- SVL<sub>H</sub> is the number of 16-bit elements.

- SVL<sub>s</sub> is the number of 32-bit elements.

- SVL<sub>D</sub> is the number of 64-bit elements.

- $SVL_Q$  is the number of 128-bit elements.

| SVL [bits] | SVL <sub>B</sub> | SVL <sub>H</sub> | SVL <sub>S</sub> | SVL <sub>D</sub> | SVLQ |

|------------|------------------|------------------|------------------|------------------|------|

| 128        | 16               | 8                | 4                | 2                | 1    |

| 256        | 32               | 16               | 8                | 4                | 2    |

| 512        | 64               | 32               | 16               | 8                | 4    |

| 1024       | 128              | 64               | 32               | 16               | 8    |

| 2048       | 256              | 128              | 64               | 32               | 16   |

## Chapter B2. Architectural state B2.1. Architectural state summary

See also:

- Chapter B1 Application processing modes

- C2.1.3 Vector lengths.

## B2.2 SME ZA storage

$D_{SSXPL}$  The ZA storage is architectural register state consisting of a two-dimensional ZA array of  $[SVL_B \times SVL_B]$  bytes.

#### B2.2.1 ZA array vector access

| R <sub>FFWNB</sub> | The ZA array can be accessed as vectors of SVL bits.                                                                                                                                     |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>pppcm</sub> | An untyped vector access to the ZA array is represented by $ZA[N]$ , where N is in the range 0 to $SVL_B-1$ inclusive.                                                                   |

| $D_{\rm DTVZN}$    | In SME LDR and STR instructions an untyped ZA array vector is selected by the sum of a 32-bit general-purpose register (vector select register $Wv$ ) and an immediate, modulo $SVL_B$ . |

| $D_{\rm YXHFR}$    | The preferred disassembly for an untyped ZA array vector is ZA[Wv, <i>imm</i> ], where <i>imm</i> is in the range 0 to 15 inclusive.                                                     |

| D <sub>CRJPC</sub> | The ZA array can be accessed as vectors of 8-bit, 16-bit, 32-bit, 64-bit, or 128-bit elements.                                                                                           |

$D_{WMVZT}$  An element-wise vector access to the ZA array is indicated by appending a vector index "[N]" to the ZA array name and element size qualifier, where N is in the range 0 to SVL<sub>B</sub>-1 inclusive, as follows:

- An 8-bit element vector access to the ZA array is represented by ZA.B[N].

- A 16-bit element vector access to the ZA array is represented by ZA.H[N].

- A 32-bit element vector access to the ZA array is represented by ZA.S[N].

- A 64-bit element vector access to the ZA array is represented by ZA.D[N].

- A 128-bit element vector access to the ZA array is represented by ZA.Q[N].

### B2.2.2 ZA tile access

| D <sub>VSVMX</sub> | A ZA tile is a square, two-dimensional sub-array of elements within the ZA array.                                                                                                             |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>WLRTV</sub> | Depending on the element size with which it is accessed, the ZA array is treated as containing one or more ZA tiles, as described in the following sections.                                  |

| D <sub>DWMYT</sub> | A ZA tile is indicated by appending the tile number to the ZA name.                                                                                                                           |

| D <sub>ZGBHT</sub> | A ZA tile slice is a one-dimensional set of horizontally or vertically contiguous elements within a ZA tile.                                                                                  |

| $R_{PZNWB}$        | A vector access to a tile reads or writes a ZA tile slice.                                                                                                                                    |

| I <sub>NFXHH</sub> | A ZA tile can be accessed as vectors of 8-bit, 16-bit, 32-bit, 64-bit, or 128-bit elements.                                                                                                   |

| I <sub>YZDBS</sub> | A ZA tile can be accessed as horizontal slices of SVL bits.                                                                                                                                   |

| R <sub>gpvsz</sub> | A ZA tile is accessed as horizontal slices if the V field in the accessing instruction opcode is 0.                                                                                           |

| D <sub>trhtx</sub> | An access to horizontal tile slices is indicated by an "H" suffix on the ZA tile name.                                                                                                        |

| I <sub>hbytt</sub> | A ZA tile can be accessed as vertical slices of SVL bits.                                                                                                                                     |

| R <sub>gpppk</sub> | A ZA tile is accessed as vertical slices if the V field in the accessing instruction opcode is 1.                                                                                             |

| D <sub>WSBVG</sub> | An access to vertical tile slices is indicated by a "V" suffix on the ZA tile name.                                                                                                           |

| $R_{\text{TWWTL}}$ | In SME instructions the tile slice is selected by the sum of a 32-bit general-purpose register (slice index register $W_s$ ) and an immediate, modulo the number of slices in the named tile. |

### B2.2.3 Accessing an 8-bit element ZA tile

D<sub>HMSNH</sub> An 8-bit element ZA tile is indicated by a ".B" qualifier following the tile name.

- $D_{\text{NLCNH}}$  There is a single tile named ZA0.B which consists of [SVL<sub>B</sub> × SVL<sub>B</sub>] 8-bit elements and occupies all of the ZA storage.

- R<sub>NBSMJ</sub> An access to a horizontal or vertical 8-bit element ZA tile slice reads or writes SVL<sub>B</sub> 8-bit elements.

- $D_{\text{NMHLM}}$  An access to a horizontal or vertical 8-bit element ZA tile slice is indicated by appending a slice index "[N]" to the tile name, direction suffix, and qualifier, ZA0H.B[N] or ZA0V.B[N], where N is in the range 0 to SVL<sub>B</sub>-1 inclusive.

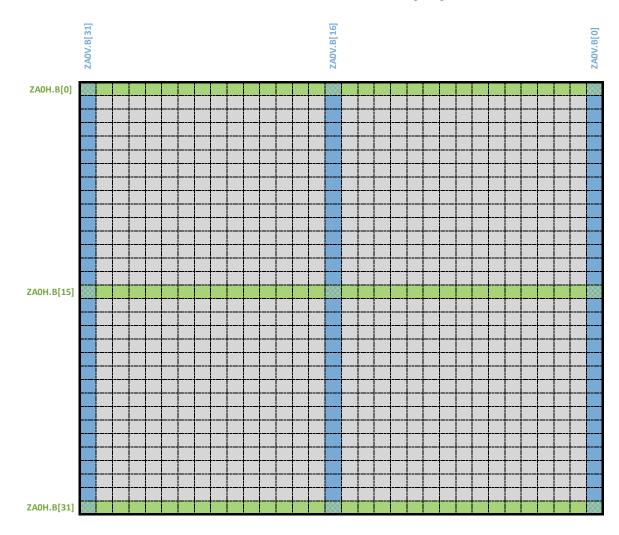

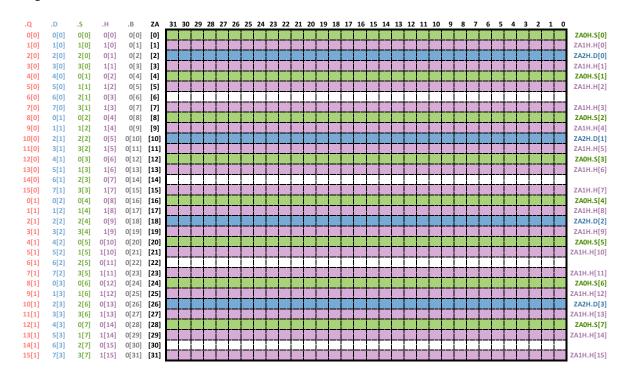

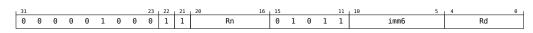

I<sub>JVTNY</sub> Horizontal and vertical ZA0.B slice accesses are illustrated in the following diagram for SVL of 256 bits:

| R <sub>dcsdx</sub> | An access to the horizontal slice ZA0H.B[N] reads or writes the SVL <sub>B</sub> bytes in ZA array vector ZA.B[N].    |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| R <sub>fhysq</sub> | An access to the vertical slice $ZA0V.B[N]$ reads or writes the 8-bit element [N] within each horizontal slice ZA0.B. |

D<sub>CDDVV</sub> The preferred disassembly is:

- ZA0H.B[Ws, imm], for a horizontal 8-bit element ZA tile slice selection.

- ZA0V.B[Ws, *imm*], for a vertical 8-bit element ZA tile slice selection.

of

Where *imm* is in the range 0 to 15 inclusive.

## B2.2.4 Accessing a 16-bit element ZA tile

- D<sub>LNXPD</sub> A 16-bit element ZA tile is indicated by a ".H" qualifier following the tile name.

- $D_{GWZDM}$  There are two tiles named ZA0.H and ZA1.H which each consists of  $[SVL_H \times SVL_H]$  16-bit elements. Each tile occupies half of the ZA storage.

- R<sub>NMGXG</sub> An access to a horizontal or vertical 16-bit element ZA tile slice reads or writes SVL<sub>H</sub> 16-bit elements.

- $\mathbb{D}_{DHKMC}$  An access to a horizontal or vertical 16-bit element ZA tile slice is indicated by appending a slice index "[N]" to the tile name, direction suffix, and qualifier, ZAtH.H[N] or ZAtV.H[N], where *t* is 0 or 1 and *N* is in the range 0 to SVL<sub>H</sub>-1 inclusive.

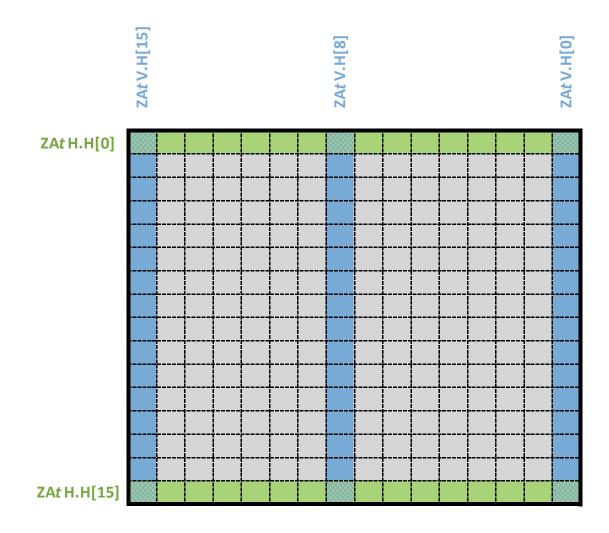

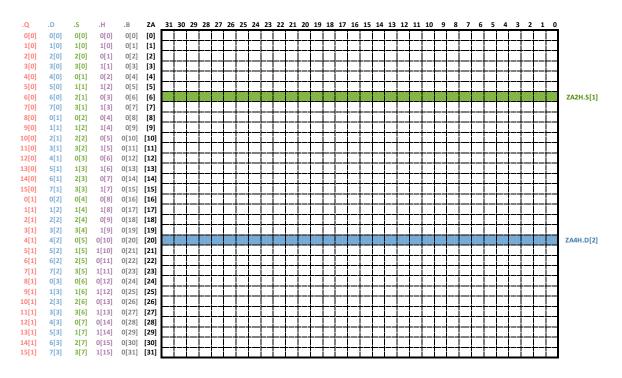

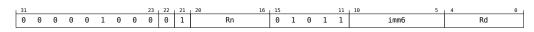

- $I_{ZSWJW}$  Horizontal and vertical ZA*t*.H slice accesses, where *t* is 0 or 1, are illustrated in the following diagram for SVL of 256 bits:

$\mathbb{R}_{BTLQC}$  An access to the horizontal slice ZA*t*H.H[*N*] reads or writes the SVL<sub>H</sub> 16-bit elements in ZA array vector ZA.H[*t* + 2 \* *N*].

$R_{\rm NGJBJ}$

An access to the vertical slice ZAtV.H[N] reads or writes the 16-bit element [N] within each horizontal slice of ZAt.H.

D<sub>RHOJT</sub> The preferred disassembly is:

- ZAtH.H[Ws, imm], for a horizontal 16-bit element ZA tile slice selection.

- ZAtV.H[Ws, *imm*], for a vertical 16-bit element ZA tile slice selection.

Where *t* is 0 or 1, and *imm* is in the range 0 to 7 inclusive.

#### B2.2.5 Accessing a 32-bit element ZA tile

- D<sub>HBKZV</sub> A 32-bit element ZA tile is indicated by a ".S" qualifier following the tile name.

- $D_{RDRT}$  There are four tiles named ZA0.S, ZA1.S, ZA2.S, and ZA3.S. Each tile consists of  $[SVL_S \times SVL_S]$  32-bit elements. Each tile occupies quarter of the ZA storage.

- R<sub>XFPPL</sub> An access to a horizontal or vertical 32-bit element ZA tile slice reads or writes SVL<sub>S</sub> 32-bit elements.

- $D_{JFPSJ}$  An access to a horizontal or vertical 32-bit element ZA tile slice is indicated by appending a slice index "[N]" to the tile name, direction suffix, and qualifier, ZAtH.S[N] or ZAtV.S[N], where t is 0, 1, 2, or 3 and N is in the range 0 to SVL<sub>S</sub>-1 inclusive.

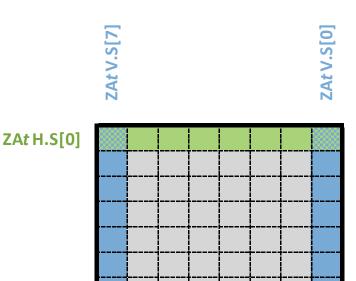

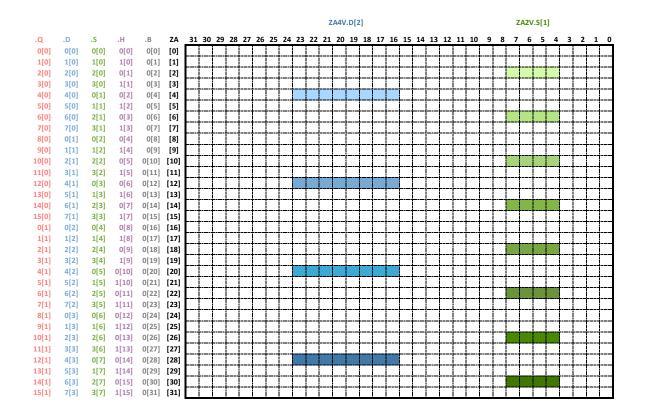

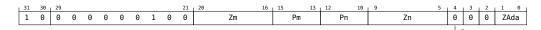

- $I_{SZXZR}$  Horizontal and vertical ZA*t*.S slice accesses, where *t* is 0, 1, 2, or 3, are illustrated in the following diagram for SVL of 256 bits:

| $R_{JBJZY}$     | An access to the horizontal slice ZA <i>t</i> H.S[ <i>N</i> ] reads or writes the SVL <sub>S</sub> 32-bit elements in ZA array vector ZA.S[ $t + 4 * N$ ].                    |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_{GBYSJ}$     | An access to the vertical slice $ZAtV.S[N]$ reads or writes the 32-bit element [N] within each horizontal slice of ZAt.S.                                                     |

| $\rm D_{LQLJH}$ | The preferred disassembly is:                                                                                                                                                 |

|                 | <ul> <li>ZAtH.S[Ws, imm], for a horizontal 32-bit element ZA tile slice selection.</li> <li>ZAtV S[Ws, imm] for a vertical 32-bit element ZA tile slice selection.</li> </ul> |

ZAt H.S[7]

• ZAtV.S[Ws, imm], for a vertical 32-bit element ZA tile slice selection.

Where *t* is 0, 1, 2, or 3, and *imm* is 0, 1, 2, or 3.

### B2.2.6 Accessing a 64-bit element ZA tile

- D<sub>TWMMM</sub> A 64-bit element ZA tile is indicated by a ".D" qualifier following the tile name.

- $D_{\text{THPSD}}$  There are eight tiles named ZA0.D, ZA1.D, ZA2.D, ZA3.D, ZA4.D, ZA5.D, ZA6.D, and ZA7.D. Each tile consists of [SVL<sub>D</sub> × SVL<sub>D</sub>] 64-bit elements. Each tile occupies an eighth of the ZA storage.

- R<sub>ZXYBQ</sub> An access to a horizontal or vertical 64-bit element ZA tile slice reads or writes SVL<sub>D</sub> 64-bit elements.

- $D_{DCXSX}$  An access to a horizontal or vertical 64-bit element ZA tile slice is indicated by appending a slice index "[N]" to the tile name, direction suffix, and qualifier, ZAtH.D[N] or ZAtV.D[N], where t is in the range 0 to 7 inclusive and N is in the range 0 to SVL<sub>D</sub>-1 inclusive.

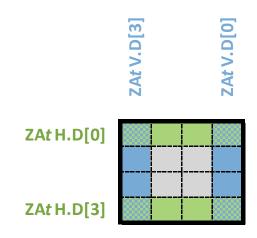

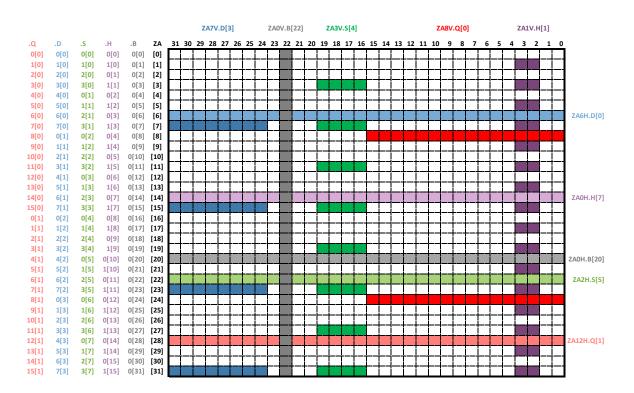

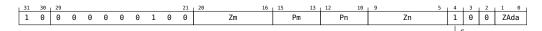

- $I_{LGJZC}$  Horizontal and vertical ZA*t*.D slice accesses, where *t* is in the range 0 to 7 inclusive, are illustrated in the following diagram for SVL of 256 bits:

| B2.2.7             | Accessing a 128-bit element ZA tile                                                                                                                                                          |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Where $t$ is in the range 0 to 7 inclusive, and <i>imm</i> is 0 or 1.                                                                                                                        |

|                    | <ul> <li>ZAtH.D[Ws, <i>imm</i>], for a horizontal 64-bit element ZA tile slice selection.</li> <li>ZAtV.D[Ws, <i>imm</i>], for a vertical 64-bit element ZA tile slice selection.</li> </ul> |

| D <sub>mqqpx</sub> | The preferred disassembly is:                                                                                                                                                                |

| R <sub>jyqkk</sub> | An access to the vertical slice $ZAtV.D[N]$ reads or writes the 64-bit element [N] within each horizontal slice of ZAt.D.                                                                    |

| R <sub>cvvjk</sub> | An access to the horizontal slice ZA <i>t</i> H.D[ <i>N</i> ] reads or writes the SVL <sub>D</sub> 64-bit elements in ZA array vector ZA.D[ $t$ + 8 * <i>N</i> ].                            |

D<sub>GZDSH</sub>

A 128-bit element ZA tile is indicated by a ".Q" qualifier following the tile name.

D<sub>RPMJL</sub>

There are sixteen tiles named ZA0.Q, ZA1.Q, ZA2.Q, ZA3.Q, ZA4.Q, ZA5.Q, ZA6.Q, ZA7.Q, ZA8.Q, ZA9.Q, ZA10.Q, ZA11.Q, ZA12.Q, ZA13.Q, ZA14.Q, and ZA15.Q. Each tile consists of [SVL<sub>Q</sub> × SVL<sub>Q</sub>] 128-bit elements. Each tile occupies a sixteenth of the ZA storage.

R<sub>QGHPF</sub>

An access to a horizontal or vertical 128-bit element ZA tile slice reads or writes SVL<sub>Q</sub> 128-bit elements.

D<sub>RLQKW</sub>

Image: Sixteen tile store reads or writes SVL<sub>Q</sub> 128-bit elements.

## Chapter B2. Architectural state B2.2. SME ZA storage

An access to a horizontal or vertical 128-bit element ZA tile slice is indicated by appending a slice index "[N]" to the tile name, direction suffix, and qualifier, ZAtH.Q[N] or ZAtV.Q[N], where t is in the range 0 to 15 inclusive and N is in the range 0 to  $SVL_Q-1$  inclusive.

$I_{YQPWS}$  Horizontal and vertical ZAt.Q slice accesses, where t is in the range 0 to 15 inclusive, are illustrated in the following diagram for SVL of 256 bits:

- $\mathbb{R}_{PJTQJ}$  An access to the horizontal slice ZA*t*H.Q[*N*] reads or writes the SVL<sub>Q</sub> 128-bit elements in ZA array vector ZA.Q[*t* + 16 \* *N*].

- $R_{TRJFZ}$  An access to the vertical slice ZAtV.Q[N] reads or writes the 128-bit element [N] within each horizontal slice of ZAt.Q.

- D<sub>VCLJP</sub> The preferred disassembly is:

- ZAtH.Q[Ws, 0], for a horizontal 128-bit element ZA tile slice selection.

- ZAtV.Q[Ws, 0], for a vertical 128-bit element ZA tile slice selection.

Where *t* is in the range 0 to 15 inclusive, and the immediate offset is always zero.

## B2.3 ZA storage layout

#### B2.3.1 ZA array vector and tile slice mappings

$I_{PYTLW}$  Each horizontal tile slice corresponds to one ZA array vector.

The horizontal slice mappings for all tile sizes are illustrated by this table:

| ZA Array<br>Vector                                 | 8-bit element Tile<br>Horizontal Slice | 16-bit element Tile<br>Horizontal Slice | 32-bit element Tile<br>Horizontal Slice | 64-bit element Tile<br>Horizontal Slice | 128-bit element Tile<br>Horizontal Slice |

|----------------------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|

| ZA[0]                                              | ZA0H.B[0]                              | ZA0H.H[0]                               | ZA0H.S[0]                               | ZA0H.D[0]                               | ZA0H.Q[0]                                |

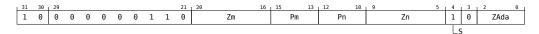

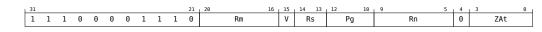

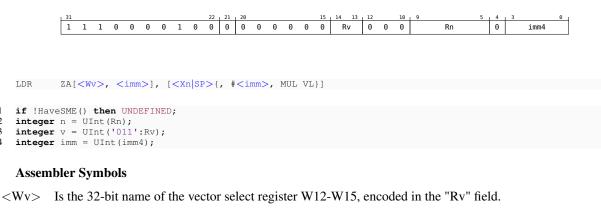

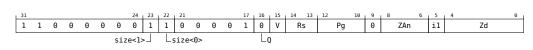

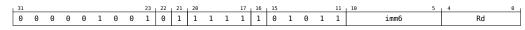

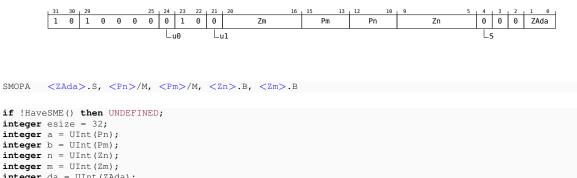

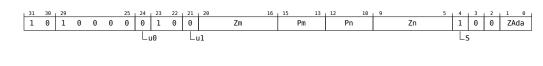

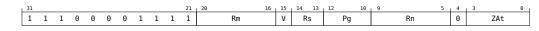

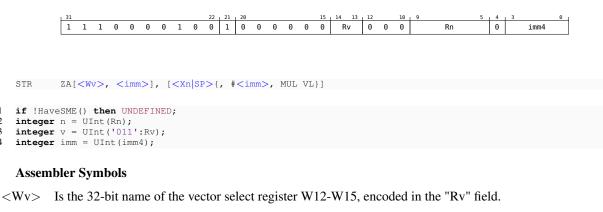

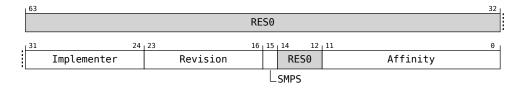

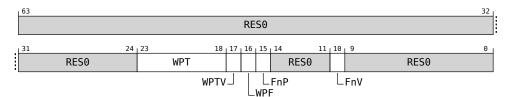

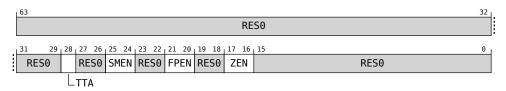

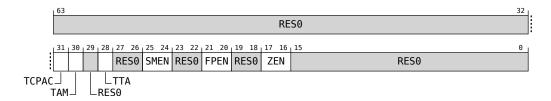

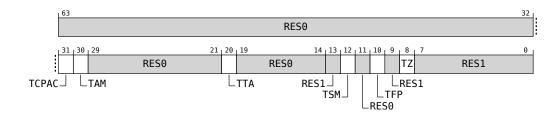

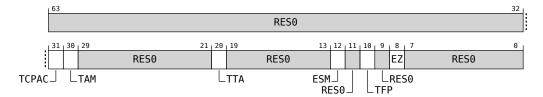

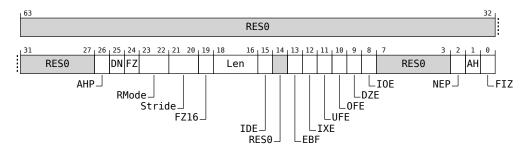

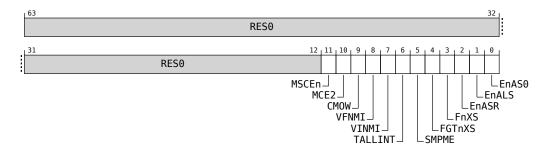

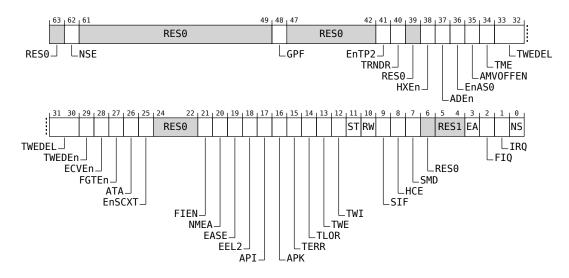

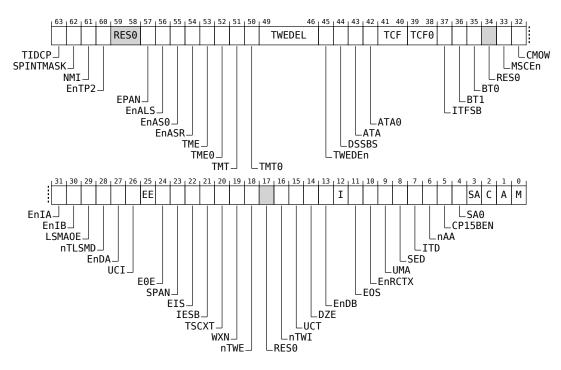

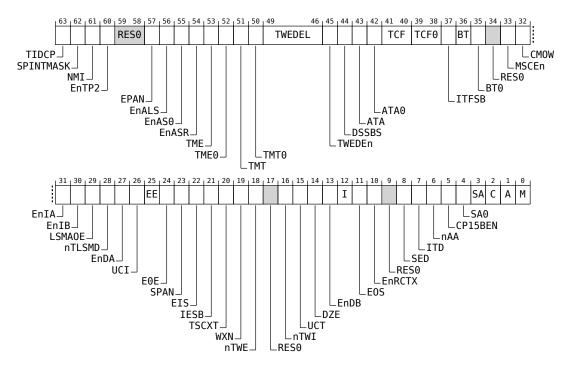

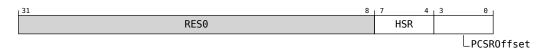

| ZA[1]                                              | ZA0H.B[1]                              | ZA1H.H[0]                               | ZA1H.S[0]                               | ZA1H.D[0]                               | ZA1H.Q[0]                                |