# ARM<sup>®</sup> System Memory Management Unit Architecture Specification SMMU architecture version 2.0

# ARM System Memory Management Unit Architecture Specification SMMU architecture version 2.0

Copyright © 2012, 2013, 2015 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

**Change History**

| Date              | Issue | Confidentiality       | Change                                                                                        |

|-------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------|

| 23 March 2012     | А     | Confidential Beta     | Issue A. Beta release for architecture version 1.0.                                           |

| 18 December 2012  | В     | Non-Confidential      | Issue B. Final release for architecture version 1.0.                                          |

| 16 September 2013 | C.a   | Non-Confidential Beta | Issue C. Beta release for architecture version 2.0.                                           |

| 13 January 2015   | D     | Non-Confidential      | Issue D full release for architecture version 2.0 with architecture extensions.               |

| 28 January 2015   | D.a   | Non-Confidential      | Non-Confidential Issue D full release. Architecture version 2.0 with architecture extensions. |

| 15 July 2015      | D.b   | Non-Confidential      | Issue D.b update with corrections and clarifications.                                         |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM Limited ("ARM"). **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version shall prevail.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

Words and logos marked with \* or m are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademark-usage-guidelines.php.

This document is Non-Confidential but any disclosure by you is subject to you providing the recipient the conditions set out in this notice and procuring the acceptance by the recipient of the conditions set out in this notice.

Copyright © 2012, 2013, 2015, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

#### Web Address

http://www.arm.com

# Contents ARM System Memory Management Unit Architecture Specification SMMU architecture version 2.0

# Preface

|           |     | About this specification<br>Using this specification |      |

|-----------|-----|------------------------------------------------------|------|

|           |     | Conventions                                          | xiii |

|           |     | Additional reading                                   | xiv  |

|           |     | Feedback                                             | xv   |

| Chapter 1 |     | Introduction                                         |      |

| -         | 1.1 | About the ARM System MMU architecture                | 1-18 |

|           | 1.2 | About the SMMU                                       |      |

|           | 1.3 | ARM PE Exception levels and Execution states         | 1-23 |

|           | 1.4 | ARM translation regimes                              |      |

|           | 1.5 | SMMU translation schemes                             | 1-28 |

|           | 1.6 | SMMU address support                                 | 1-37 |

| Chapter 2 |     | SMMU Operation                                       |      |

| •         | 2.1 | Overview of SMMU operation                           | 2-44 |

|           | 2.2 | Security State Determination (SSD)                   |      |

|           | 2.3 | Context determination                                |      |

|           | 2.4 | Memory type and shareability attribute determination |      |

|           | 2.5 | TLB operation                                        | 2-74 |

|           | 2.6 | Translation context                                  |      |

|           | 2.7 | Translation and protection checks                    |      |

|           | 2.8 | Hypervisor contexts (HYPC)                           |      |

|           |     | <b>,</b>                                             |      |

|                        | 2.9                                                                                                                 | Monitor contexts (MONC)                                                                                                                                                                                               | 2-87                                                                                                                                                           |

|------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 2.10                                                                                                                | E2H contexts (E2HC)                                                                                                                                                                                                   | 2-88                                                                                                                                                           |

| •                      |                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                |

| Chapter 3              |                                                                                                                     | The Fault Model                                                                                                                                                                                                       |                                                                                                                                                                |

|                        | 3.1                                                                                                                 | Overview of fault types                                                                                                                                                                                               |                                                                                                                                                                |

|                        | 3.2                                                                                                                 | Fault-handling terminology                                                                                                                                                                                            |                                                                                                                                                                |

|                        | 3.3                                                                                                                 | Handling multiple memory faults                                                                                                                                                                                       |                                                                                                                                                                |

|                        | 3.4                                                                                                                 | Recording memory attributes                                                                                                                                                                                           | 3-95                                                                                                                                                           |

|                        | 3.5                                                                                                                 | Recording stage 1 followed by stage 2 translation faults                                                                                                                                                              |                                                                                                                                                                |

|                        | 3.6                                                                                                                 | Fault interrupts                                                                                                                                                                                                      |                                                                                                                                                                |

|                        | 3.7                                                                                                                 | Context faults                                                                                                                                                                                                        |                                                                                                                                                                |

|                        | 3.8                                                                                                                 | Global faults                                                                                                                                                                                                         | -                                                                                                                                                              |

|                        | 3.9                                                                                                                 | Configuration access                                                                                                                                                                                                  |                                                                                                                                                                |

|                        | 3.10                                                                                                                | External faults                                                                                                                                                                                                       |                                                                                                                                                                |

|                        | 3.11                                                                                                                | Reporting exclusive access transactions                                                                                                                                                                               |                                                                                                                                                                |

|                        | 3.12                                                                                                                | Fault behavior in virtualized context banks                                                                                                                                                                           | 3-121                                                                                                                                                          |

| Chapter 4              |                                                                                                                     | Address Translation Operations                                                                                                                                                                                        |                                                                                                                                                                |

| -                      | 4.1                                                                                                                 | About address translation operations                                                                                                                                                                                  | 4-124                                                                                                                                                          |

|                        | 4.2                                                                                                                 | Address translation registers in a stage 1 translation context                                                                                                                                                        |                                                                                                                                                                |

|                        | 4.3                                                                                                                 | Address translation registers in the global address space                                                                                                                                                             |                                                                                                                                                                |

|                        |                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                |

| Chapter 5              |                                                                                                                     | Coherency Issues and Cache Maintenance Operations                                                                                                                                                                     | = 400                                                                                                                                                          |

|                        | 5.1                                                                                                                 | Updating the state of a context bank                                                                                                                                                                                  |                                                                                                                                                                |

|                        | 5.2                                                                                                                 | Translation table walk coherency                                                                                                                                                                                      |                                                                                                                                                                |

|                        | 5.3                                                                                                                 | Broadcast TLB maintenance operations                                                                                                                                                                                  |                                                                                                                                                                |

|                        | 5.4                                                                                                                 | TLB maintenance operations                                                                                                                                                                                            |                                                                                                                                                                |

|                        | 5.5                                                                                                                 | Cache maintenance operations                                                                                                                                                                                          | 5-139                                                                                                                                                          |

|                        |                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                |

| Chanter 6              |                                                                                                                     | SMMIL Performance Monitors Extension                                                                                                                                                                                  |                                                                                                                                                                |

| Chapter 6              | 6 1                                                                                                                 | SMMU Performance Monitors Extension                                                                                                                                                                                   | 6-144                                                                                                                                                          |

| Chapter 6              | 6.1<br>6.2                                                                                                          | About the SMMU Performance Monitors Extension                                                                                                                                                                         |                                                                                                                                                                |

| Chapter 6              | 6.2                                                                                                                 | About the SMMU Performance Monitors Extension<br>The register map                                                                                                                                                     | 6-145                                                                                                                                                          |

| Chapter 6              | 6.2<br>6.3                                                                                                          | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes                                                                                                                                    | 6-145<br>6-146                                                                                                                                                 |

| Chapter 6              | 6.2<br>6.3<br>6.4                                                                                                   | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups                                                                                                                 | 6-145<br>6-146<br>6-147                                                                                                                                        |

| Chapter 6              | 6.2<br>6.3<br>6.4<br>6.5                                                                                            | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups                                                                                               | 6-145<br>6-146<br>6-147<br>6-148                                                                                                                               |

| Chapter 6              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                                     | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups<br>Event filtering                                                                            | 6-145<br>6-146<br>6-147<br>6-148<br>6-149                                                                                                                      |

| Chapter 6              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                              | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups<br>Event filtering<br>Translation context bank assignment                                     | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150                                                                                                             |

| Chapter 6              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                                     | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups<br>Event filtering                                                                            | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150                                                                                                             |

| Chapter 6<br>Chapter 7 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                              | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups<br>Event filtering<br>Translation context bank assignment                                     | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150                                                                                                             |

|                        | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                              | About the SMMU Performance Monitors Extension<br>The register map<br>Event classes<br>StreamID groups<br>Counter groups<br>Event filtering<br>Translation context bank assignment<br>Event counter overflow interrupt | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151                                                                                                    |

|                        | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                                       | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151                                                                                                    |

|                        | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                                       | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155                                                                                  |

| Chapter 7              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2                                                         | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155                                                                                  |

|                        | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3                                                  | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155<br>7-156                                                                         |

| Chapter 7              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3                                                  | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155<br>7-156<br>8-162                                                                |

| Chapter 7              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2                                    | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163                                                       |

| Chapter 7              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3                                                  | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163                                                       |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2                                    | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163                                                       |

| Chapter 7              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3                             | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163<br>8-165                                              |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3<br>9.1                      | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163<br>8-165<br>9-168                            |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3                             | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-154<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163<br>8-165<br>9-168<br>9-173                   |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3<br>9.1<br>9.2               | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-155<br>7-155<br>8-162<br>8-163<br>8-165<br>9-168<br>9-173<br>9-175          |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3<br>9.1<br>9.2<br>9.3        | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-155<br>7-155<br>8-162<br>8-163<br>8-165<br>9-168<br>9-173<br>9-175<br>9-177 |

| Chapter 7<br>Chapter 8 | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>7.1<br>7.2<br>7.3<br>8.1<br>8.2<br>8.3<br>9.1<br>9.2<br>9.3<br>9.4 | About the SMMU Performance Monitors Extension                                                                                                                                                                         | 6-145<br>6-146<br>6-147<br>6-148<br>6-149<br>6-150<br>6-151<br>7-155<br>7-155<br>7-155<br>7-156<br>8-162<br>8-163<br>8-165<br>9-168<br>9-173<br>9-177<br>9-178 |

| Chapter 10 |      | SMMU Global Register Space 1                              |        |

|------------|------|-----------------------------------------------------------|--------|

| •          | 10.1 | SMMU Global Register Space 1 register summary             | 10-236 |

|            | 10.2 | SMMU Global Register Space 1 register descriptions        |        |

| Chapter 11 |      | SMMU IMPLEMENTATION DEFINED Address Space                 |        |

|            | 11.1 | About the SMMU IMPLEMENTATION DEFINED address space       | 11-248 |

| Chapter 12 |      | SMMU Performance Monitors Extension Register Map          |        |

|            | 12.1 | SMMU Performance Monitors Extension register summary      |        |

|            | 12.2 | SMMU Performance Monitors Extension register descriptions | 12-252 |

| Chapter 13 |      | The Security State Determination Address Space            |        |

|            | 13.1 | SMMU SSD address space                                    | 13-268 |

| Chapter 14 |      | Extended Stream Matching Extension                        |        |

|            | 14.1 | About the Extended Stream Match extension                 | 14-272 |

|            | 14.2 | Extended Stream Match Extension registers                 | 14-275 |

| Chapter 15 |      | StreamID Compressed Indexing Extension                    |        |

|            | 15.1 | About the StreamID Compressed Indexing Extension          | 15-278 |

|            | 15.2 | StreamID Compressed Indexing Extension registers          | 15-280 |

| Chapter 16 |      | Stage 1 Translation Context Bank Format                   |        |

| -          | 16.1 | Stage 1 translation context bank address space            | 16-282 |

|            | 16.2 | Reset values                                              | 16-286 |

|            | 16.3 | Memory attribute indirection                              |        |

|            | 16.4 | Multi-format registers and reserved fields                |        |

|            | 16.5 | Stage 1 translation context bank register descriptions    | 16-290 |

| Chapter 17 |      | Stage 2 Translation Context Bank Format                   |        |

|            | 17.1 | Stage 1 and stage 2 context bank format differences       |        |

|            | 17.2 | Stage 2 translation context bank address space            |        |

|            | 17.3 | Stage 2 translation context bank register descriptions    | 17-344 |

| Appendix A |      | Register Names                                            |        |

|            | A.1  | Summary of corresponding SMMU and ARM registers           | A-360  |

|            |      | Glossary                                                  |        |

# Preface

This preface introduces the ARM<sup>®</sup> System Memory Management Unit Architecture Specification. It contains the following sections:

- *About this specification on page x.*

- Using this specification on page xi.

- Conventions on page xiii.

- Additional reading on page xiv.

- Feedback on page xv.

# About this specification

This specification introduces the ARM System MMU (SMMU) architecture.

# Intended audience

This specification is written for readers who are familiar with system memory management concepts, but who do not necessarily have any experience of the ARM architecture.

# Using this specification

The information in this specification is organized into the following chapters:

#### **Chapter 1** Introduction

Read this for an introduction to the SMMU architecture.

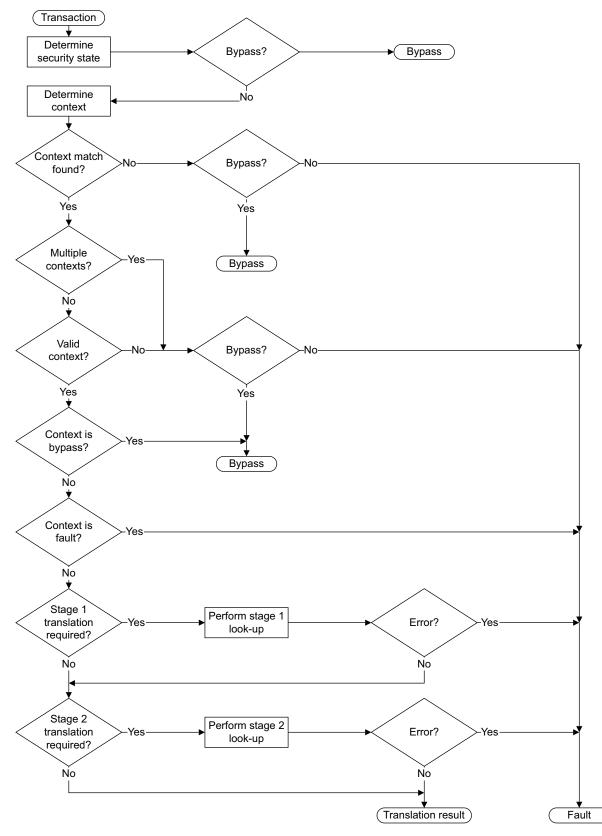

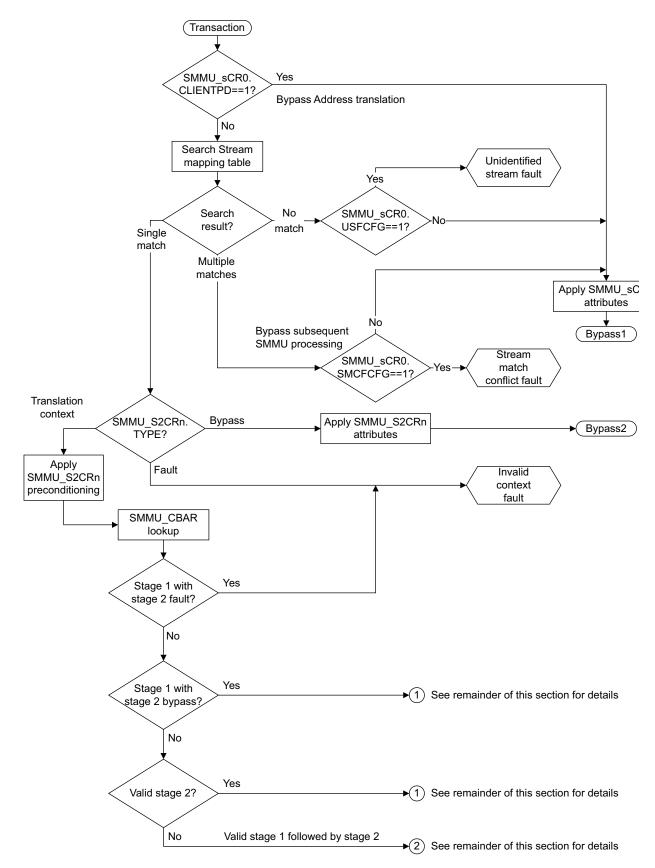

### Chapter 2 SMMU Operation

Read this for information about the steps that the SMMU performs on receiving a memory access request.

#### Chapter 3 The Fault Model

Read this for information about fault conditions the SMMU might encounter, and how the SMMU handles these faults.

### **Chapter 4** Address Translation Operations

Read this for information about address translation operations that are initiated using software-accessible registers.

#### **Chapter 5** Coherency Issues and Cache Maintenance Operations

Read this for information about the relationship between controlling software and the SMMU, including optional support for coherent translation table walks and cache maintenance operations.

### Chapter 6 SMMU Performance Monitors Extension

Read this for information about OPTIONAL SMMU support for performance monitoring functionality.

#### Chapter 7 SMMU Support for Two Security States

Read this for information about OPTIONAL SMMU support for two Security states.

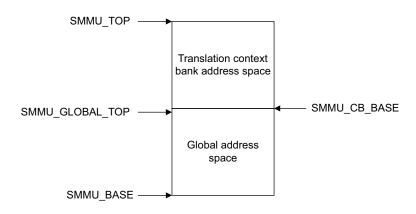

### Chapter 8 SMMU Address Space

Read this for information about the SMMU register address map in terms of the SMMU address spaces.

### Chapter 9 SMMU Global Register Space 0

Read this for information about the contents of Global Register Space 0. This address space provides high-level control of the SMMU resources.

### Chapter 10 SMMU Global Register Space 1

Read this for information about the contents of Global Register Space 1. In addition to providing high-level SMMU resource control, this space accommodates the number of addresses in the global register space exceeding the capacity of a single memory page, when the page size is 4KB.

### Chapter 11 SMMU IMPLEMENTATION DEFINED Address Space

Read this for information about address space reserved for IMPLEMENTATION DEFINED purposes.

### Chapter 12 SMMU Performance Monitors Extension Register Map

Read this for information about the recommended memory-mapped and external debug interface to the Performance Monitors Extension.

### Chapter 13 The Security State Determination Address Space

Read this for information about the address space used by the Security State Determination part of the translation process.

### Chapter 14 Extended Stream Matching Extension

Read this for information about the optional extension that supports up to 1024 Stream Match Register Groups.

### Chapter 15 StreamID Compressed Indexing Extension

Read this for information about StreamID compressed indexing extension.

# Chapter 16 Stage 1 Translation Context Bank Format

Read this for information about the stage 1 translation context bank format.

## Chapter 17 Stage 2 Translation Context Bank Format

Read this for information about the stage 2 translation context bank format.

### Appendix A Register Names

Read this for information about differences in register names between SMMU architecture versions.

*Glossary* Read this for definitions of some terms used in this specification.

# Conventions

The following sections describe conventions that this book can use:

- Typographic conventions

- Register names

- Numbers

- Pseudocode descriptions.

# Typographic conventions

The typographical conventions are:

| italic              | Introduces special terminology, and denotes citations.                                                                                                                   |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bold                | Denotes signal names, and is used for terms in descriptive lists, where appropriate.                                                                                     |  |

| monospace           | Used for assembler syntax descriptions, pseudocode, and source code examples.                                                                                            |  |

|                     | Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples. |  |

| SMALL CAPITALS      | Used for a few terms that have specific technical meanings, and are included in the glossary.                                                                            |  |

| <b>Colored text</b> | Indicates a link. This can be:                                                                                                                                           |  |

|                     | • a URL, for example http://infocenter.arm.com                                                                                                                           |  |

|                     | • a cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, <i>Pseudocode descriptions</i>           |  |

|                     | • a link to a chapter or appendix, or to a glossary entry, or to the section of the                                                                                      |  |

a link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example *Translation context bank*.

# **Register names**

In a register name, *s* denotes the presence or absence of the Secure register prefix, S. For example, in an implementation that supports two Security states, the register SMMU\_sACR is implemented as both:

- the Secure register SMMU\_SACR

- the Non-secure register SMMU\_ACR.

# Numbers

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

# **Pseudocode descriptions**

This manual uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font.

# Additional reading

This section lists relevant publications from ARM and third parties.

See the Infocenter http://infocenter.arm.com, for access to ARM documentation.

# **ARM** publications

See the following documents for other information.

- ARM<sup>®</sup> Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile (ARM DDI 0487)

- CoreSight<sup>™</sup> Architecture Specification (ARM IHI 0029).

# Feedback

ARM welcomes feedback on its documentation.

# Feedback on this manual

If you have comments on the content of this manual, send e-mail to errata@arm.com. Give:

- The title.

- The number, ARM IHI 0062D.b.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# — Note –

ARM tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of any document when viewed with any other PDF reader.

Preface Feedback

# Chapter 1 Introduction

This chapter provides an introduction to the ARM *System Memory Management Unit* (SMMU) architecture. It contains the following sections:

- About the ARM System MMU architecture on page 1-18.

- About the SMMU on page 1-21.

- *ARM PE Exception levels and Execution states on page 1-23.*

- ARM translation regimes on page 1-24.

- SMMU translation schemes on page 1-28.

- SMMU address support on page 1-37.

# 1.1 About the ARM System MMU architecture

The ARM *System MMU* (SMMU) architecture provides a flexible implementation framework for a *Memory Management Unit* (MMU) implementation, with a number of IMPLEMENTATION DEFINED options.

The architecture can be used for a system-level MMU. It supports address translation from an *input address* to an *output address*, based on address mapping and memory attribute information held in *translation tables*.

An address translation from an input address to an output address is described as a stage of address translation.

The SMMU architecture also supports the concept of *translation regimes*, in which a required memory access might require two stages of address translation. For example, in a virtualized processor implementation:

- An operating system defines the translation tables for its own memory accesses, and for accesses by applications running under it. It does this believing it is mapping the *virtual addresses* (VAs) used by the processor to *physical addresses* (PAs) in the physical memory system. However, it actually defines addresses in an *intermediate physical address* (IPA) memory map.

- A hypervisor defines the translation tables that translate the IPAs for a particular *guest operating system* to PAs.

This means that any memory access by a Guest OS, or by an application, requires two stages of translation, that together define a single translation regime:

- Stage 1, from VA to IPA.

- Stage 2, from IPA to PA.

Within this system, the hypervisor must also define the required translation tables for its own memory accesses. These are in a separate translation regime, with only one stage of translation in which the stage 1 translation maps VAs to PAs.

A single stage of address translation can require multiple translation table lookups. In this case, each translation table lookup is described as a *level* of address lookup.

An implementation of the ARM SMMU architecture can provide:

- Multiple transaction contexts, that apply to specific streams of transactions.

- Single or two stage translation.

- For any stage of translation, multiple levels of address lookup, to provide fine-grained memory control.

- Fault handling, logging, and signaling functionality.

- Debug and OPTIONAL performance monitoring functionality.

# 1.1.1 Debug support

The SMMU architecture does not require the provision of debug support features. However, if an implementation supports two Security states, a Non-secure debug agent must not be able to read any data relating to Secure transaction handling.

# 1.1.2 TLB visibility

ARM strongly recommends that an implementation provides a mechanism to read the content of any *Translation Lookaside Buffer* (TLB) structure in the implementation. The method by which the SMMU provides this feature is IMPLEMENTATION DEFINED, but it must ensure that Non-secure resources cannot access Secure TLB entries. The SMMU global register map reserves space to provide access to such a function. See Chapter 9 *SMMU Global Register Space 0* for more information.

# 1.1.3 SMMU architecture version

This specification defines version 2.0 of the SMMU architecture (SMMUv2), and also describes version 1.0 of the architecture (SMMUv1).

# 1.1.4 Changes in version 2.0 of the SMMU architecture

Version 2.0 of the SMMU architecture contains the following changes and additions to version 1.0:

- A requirement that any SMMUv1 Secure software that changes the partitioning of context banks between Secure and Non-secure be updated in accordance with *SMMUv2 backwards compatibility problem with SMMUv1 on page 1-20*.

- Support for the address translations required by both Execution states of ARMv8 processors, where the AArch32 state processes addresses in 32-bit registers, and the AArch64 state processes addresses in 64-bit registers. This means SMMUv2 supports the following *translation schemes*:

- AArch32 Short-descriptor.

- AArch32 Long-descriptor.

- AArch64.

- Modified address translation and TLB invalidate registers, and new SMMUv2-only registers. See.

- Chapter 9 SMMU Global Register Space 0.

- Chapter 16 Stage 1 Translation Context Bank Format.

- Chapter 17 Stage 2 Translation Context Bank Format.

- Changed status of address translation registers. These registers are OPTIONAL in SMMUv2. See *Address* translation registers in SMMUv2 on page 4-124.

- New SMMU\_CBA2Rn register that extends the configuration attributes for the translation context bank. See *SMMU\_CBA2Rn, Context Bank Attribute Registers on page 10-243*.

- Support for *Translation Table Base Register* (TTBR) determination for Secure and Non-secure translation context banks. See *The translation context bank table on page 2-77*.

- Support for a 16KB and 64KB *translation granule* size. See *SMMU translation schemes on page 1-28* and *SMMU\_IDR2 on page 9-184*.

- Support for Monitor context for the Secure EL3 translation regime. See *Monitor contexts (MONC) on* page 2-87.

- Support for E2H context. See *E2H contexts (E2HC) on page 2-88*.

- Modified context interrupt behavior. See *Context interrupts on page 3-98*.

- Modified invalid context fault behavior. See *Global faults on page 3-112*.

- Modified configuration access fault behavior. See *Configuration access on page 3-117* and *SMMU\_SCR1*, *Secure Configuration Register 1 on page 9-224*.

- Modified external fault behavior. See *External faults on page 3-118*.

- Modified MemAttr encoding. See *Memory attribute, MemAttr on page 9-177* and *SMMU\_CBn\_MAIRm, Memory Attribute Indirection Registers on page 16-300.*

- Renaming of SMMU\_CBn\_TTBCR registers to SMMU\_CBn\_TCR registers.

- New SMMU\_CBn\_TCR2 register that extends the SMMU\_CBn\_TCR functionality. See SMMU\_CBn\_TCR2, Translation Control Register 2 on page 16-332.

- Modified SMMU\_CBn\_RESUME behavior. See *SMMU\_CBn\_RESUME*, *Transaction Resume register on* page 16-310.

- New SMMU\_CBn\_IPAFAR register that records the IPA for transactions that fault during stage 2 translation. See SMMU\_CBn\_IPAFAR, IPA Fault Address Register on page 17-346.

- Modified behavior when certain register fields are encoded as Reserved. See *Reserved memory type and shareability attributes on page 2-64*.

# 1.1.5 SMMUv2 backwards compatibility problem with SMMUv1

SMMUv1 compliant Non-secure software running with a non-existent or SMMUv2 compliant Secure software requires no change.

SMMUv1 compliant Secure software that changes the partitioning of the context banks between Secure and Non-secure must be updated for SMMUv2. The change required should be confined to the code that changes the partitioning, that is, the write of SMMU\_SCR1.NSNUMCBO.

See Resource allocation on page 7-156 for more information.

# 1.2 About the SMMU

The interfaces to an ARM SMMU are IMPLEMENTATION DEFINED, but the description of the SMMU in this manual is based on the implementation model summarized in this section,

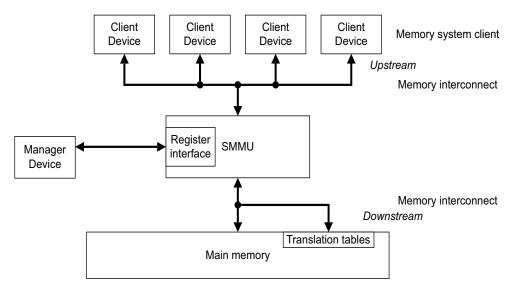

Figure 1-1 shows the implementation of an ARM SMMU in the memory system.

## Figure 1-1 An ARM SMMMU in the memory system

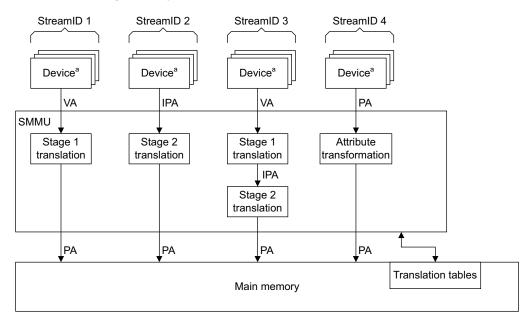

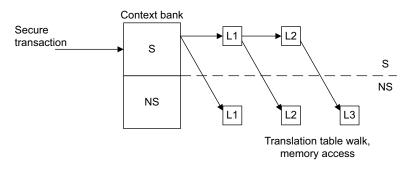

In this implementation model:

- One or more *Client devices* connect through the memory interconnect to the SMMU.

- Client devices are described as being *upstream* of the SMMU. The connection between the SMMU and the client devices is the *upstream bus*.

- The SMMU connects to the rest of the memory system, through to main memory.

- The rest of the memory system is described as being *downstream* of the SMMU. The connection between the SMMU and the rest of the memory system is the *downstream bus*.

- A client device issues a transaction request to the SMMU. The SMMU processes that transaction, and returns a response to the client.

A simple description of a possible usage model for the SMMU is that client device makes a memory access that is routed to the SMMU. The SMMU performs the address translation required for the access, using translation tables in memory, and makes the required access permission and attribute checks:

- If the translation is successful and the access is valid, the SMMU performs the access and returns the

result to the client.

- Otherwise, the SMMU returns fault information to the client.

The client device might not be aware that the SMMU is handling its access to the memory system.

In addition to these memory system connections to the SMMU, the SMMU provides a memory-mapped register interface. A *manager device* uses this interface to configure and control the SMMU.

— Note

This specification assumes that the *manager device* is independent of any *client device*, although this is not a requirement of the SMMU architecture.

This specification defines:

The processing of transaction requests by the SMMU.

•

The memory-mapped register interface to the SMMU.

# 1.3 ARM PE Exception levels and Execution states

The ARMv8 exception model defines the exception level ELn, where n can have the values 0-3. Software execution privilege increases with increase in the value of n, with EL0 software having the lowest level of privilege. Execution at EL0 is described as unprivileged execution. It is IMPLEMENTATION DEFINED whether a processor implementation includes EL2 or EL3. The typical use of the different Exception levels is:

- EL0 Application software. Secure or Non-secure state.

- EL1 Operating system. Secure or Non-secure state.

- EL2 Hypervisor. Non-secure state only.

- EL3 Secure monitor.

The permitted processor exception levels depend on the processor security state, as Table 1-1 shows.

# Table 1-1 Exception level implementation by security state

| Non-secure | Secure |

|------------|--------|

| -          | EL3    |

| EL2        | -      |

| EL1        | EL1    |

| EL0        | EL0    |

ARMv8 defines AArch64 and AArch32 execution states that define the supported instruction set, and whether the processor uses 64-bit or 32-bit PC, LR, SP, and general-purpose registers.

Based on the AArch32 and AArch64 execution states and the associated translation table formats, the SMMU architecture defines the following *translation schemes*:

- AArch32 Short-descriptor.

- AArch32 Long-descriptor.

- AArch64.

The remainder of this chapter provides more information about the SMMU translation schemes.

# 1.4 ARM translation regimes

The ARM architecture supports different translation regimes and stages for AArch32 and AArch64. Figure 1-2 shows the ARM architecture translation regimes for memory accesses made from AArch64 state, where.

- VA is Virtual Address.

- PA is Physical Address.

- IPA is Intermediate Physical Address.

Translation regimes, when EL3 is using AArch64

| Secure EL3                  | VA - | Secure EL3 stage 1                                                                                                                             | → PA, Secure or Non-secure         |

|-----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                             | •7 ( |                                                                                                                                                |                                    |

| Secure EL1&0                |      | Secure EL1&0 stage 1                                                                                                                           |                                    |

|                             | VA · | Controlled from Secure EL1                                                                                                                     | → PA, Secure or Non-secure         |

| Non-secure <sup>a</sup> EL2 | VA · | Non-secure EL2 stage 1                                                                                                                         | → PA, Non-secure only              |

|                             |      | Controlled from EL2                                                                                                                            | ,                                  |

| Non-secure EL1&0            | VA   | Non-secure EL1&0 stage 1         IPA         Non-secure EL1&0 stage           Controlled from EL1 <sup>b</sup> IPA         Controlled from EL2 | <sup>2</sup> → PA, Non-secure only |

a. The SMMU also includes a Secure EL2 translation regime

b. Or higher

#### Figure 1-2 ARM processor architecture AArch64 translation regimes and stages

#### In Figure 1-2:

- The Non-secure EL1&0 translation regime comprises two stages of translation.

- The other translation regimes comprise only a single stage of translation.

*Translation regimes for accesses from AArch32 state* describes how the translation regimes differ for memory accesses from AArch32 state, and the different terminology used to describe these regimes.

# 1.4.1 Translation regimes for accesses from AArch32 state

In the ARM processor architecture, the behavior of a PE that is executing in AArch32 state is defined in relation to different PE *modes*. Most of these modes have the level of execution privilege that is appropriate to an operating system. In a processor implementation that includes EL3, if EL3 can use AArch32 state or AArch64 state, the Exception level of these modes can depend on whether EL3 is using AArch32 or AArch64, as Table 1-2 shows.

### Table 1-2 Mapping of AArch32 PE modes to Exception levels

| PE mode                                        | Non-secure<br>state | Secur             | Privilege         |       |

|------------------------------------------------|---------------------|-------------------|-------------------|-------|

| PE mode                                        |                     | EL3 using AArch64 | EL3 using AArch32 | level |

| User                                           | EL0                 | EL0               | EL0               | PL0   |

| System, Supervisor, Abort, Undefined, IRQ, FIQ | EL1                 | EL1               | EL3               | PL1   |

| Hyp <sup>a</sup>                               | EL2                 | -                 | -                 | PL2   |

| Monitor <sup>b</sup>                           | -                   | -                 | EL3               | PL1   |

a. Implemented only in Non-secure state, and only present when EL2 is using AArch32.

b. Implemented only in Secure state, and only present when EL3 is using AArch32.

To provide descriptions of the AArch32 translation regimes that are independent of whether EL3 is using AArch32 or AArch64, these translation regimes are described in terms of *privilege levels*, PL0-PL2, as Figure 1-3 shows.

| Translation regime          |                                                  |                            |

|-----------------------------|--------------------------------------------------|----------------------------|

| Secure PL1&0                | VA Secure PL1&0 stage 1                          | → PA, Secure or Non-secure |

| Non-secure <sup>a</sup> PL2 | VA Non-secure PL2 stage 1                        | → PA, Non-secure only      |

| Non-secure PL1&0            | VA Non-secure PL1&0 IPA Non-secure PL1&0 stage 2 | → PA, Non-secure only      |

a. The SMMU also includes a Secure EL2 translation regime

#### Figure 1-3 ARM processor architecture AArch32 translation regimes and stages

#### —— Note –

The regime that is affected by how the mapping of PE modes to Exception level is determined by the current Execution state is the Secure PL1&0 translation regime. If this was described in terms of Exception levels it would be:

- The Secure EL1&0 regime when EL3 is using AArch64.

- The Secure EL3&0 regime when EL3 is using AArch32.

The SMMU controls for the Secure PL1&0 translation regime are those defined for the Secure EL1&0 translation regime.

For the Non-secure PL1&0 translation regime, the second stage of translation, that maps the IPA from stage 1 to a PA, might be:

- An AArch32 translation stage, as shown in Figure 1-3.

- An AArch64 translation stage, as shown in Figure 1-2 on page 1-24.

For more information see the ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

## 1.4.2 SMMU register controls of the translation regimes

The different translation regimes have associated SMMU registers, that are accessible at the corresponding Exception level, as Table 1-3 on page 1-26 shows.

| Translation regime         | Register         | Description                                                                          | Notes                                                                              |

|----------------------------|------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Secure EL3<br>Secure EL1&0 | SMMU_CBA2Rn      | SMMU_CBA2Rn, Context Bank Attribute<br>Registers on page 10-243                      | Register applies to Secure context banks                                           |

|                            | SMMU_CBARn       | SMMU_CBARn, Context Bank Attribute<br>Registers on page 10-237                       | Register applies to Secure context banks                                           |

|                            | SMMU_CBFRSYNRAn  | SMMU_CBFRSYNRAn, Context Bank Fault<br>Restricted Syndrome Register A on page 10-245 | -                                                                                  |

|                            | SMMU_SCR0        | SMMU_SCR0, Secure Configuration Register 0 bit assignments on page 9-188             | -                                                                                  |

|                            | SMMU_SCR1        | SMMU_SCR1, Secure Configuration Register 1 on page 9-224                             | -                                                                                  |

|                            | SMMU_SGATS*      | SMMU Global Register Space 0 register descriptions on page 9-179                     | Secure global address translation registers                                        |

|                            | SMMU_SGF*        | SMMU Global Register Space 0 register descriptions on page 9-179                     | Secure global fault registers                                                      |

|                            | SMMU_SGPAR       | SMMU_sGPAR, Global Physical Address<br>Register on page 9-212                        | -                                                                                  |

|                            | SMMU_NSGATS*     | Secure alias for Non-secure registers on page 9-175                                  | Secure aliases for Non-secure<br>copies of Global address<br>translation registers |

|                            | SMMU_NSGF*       | Secure alias for Non-secure registers on page 9-175                                  | Secure aliases for Non-secure copies of Global fault registers                     |

|                            | SMMU_NSGPAR      | Secure alias for Non-secure registers on page 9-175                                  | Secure alias for Non-secure copy of SMMU_sGPAR                                     |

|                            | SMMU_sTLBGSTATUS | SMMU_sTLBGSTATUS, Global TLB Status register on page 9-216                           | Secure alias for Non-secure copies of Global TLB registers                         |

|                            | SMMU_sTLBGSYNC   | SMMU_sTLBGSYNC, Global Synchronize TLB<br>Invalidate on page 9-217                   | _                                                                                  |

|                            | SMMU_SSDRn       | SMMU SSD address space on page 13-268                                                | Security state determination registers                                             |

|                            | SMMU_STLBI       | Chapter 9 SMMU Global Register Space 0                                               | Secure TLB Invalidate registers                                                    |

|                            | SMMU_S2CRn       | SMMU_S2CRn, Stream-to-Context Register on page 9-218                                 | Registers apply to Secure<br>Stream Match Register groups                          |

|                            | SMMU_SMRn        | SMMU_SMRn, Stream Match Register on page 9-228                                       | Registers apply to Secure<br>Stream Match Register groups                          |

| Secure EL3                 | SMMU_CBn_*       | Chapter 17 Stage 2 Translation Context Bank<br>Format                                | Monitor context, Secure only                                                       |

| Secure EL2                 | SMMU_CBn_*       | Chapter 17 Stage 2 Translation Context Bank<br>Format                                | Hypervisor context, Secure and Non-secure                                          |

# Table 1-3 Translation regime control of SMMU registers

| Translation regime  | Register    | Description                                                                 | Notes                                                         |

|---------------------|-------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|

| Non-secure<br>EL2   | SMMU_CR0    | SMMU_CR0, Non-secure Configuration Register 0 bit assignments on page 9-193 | -                                                             |

|                     | SMMU_GATS*  | SMMU Global Register Space 0 register descriptions on page 9-179            | Non-secure global address translation registers               |

|                     | SMMU_GF*    |                                                                             | Non-secure global fault registers                             |

|                     | SMMU_GPAR   | SMMU_sGPAR, Global Physical Address<br>Register on page 9-212               | -                                                             |

|                     | SMMU_CBARn  | SMMU_CBARn, Context Bank Attribute<br>Registers on page 10-237              | Register applies to Non-secure context banks                  |

|                     | SMMU_CBA2Rn | SMMU_CBA2Rn, Context Bank Attribute<br>Registers on page 10-243             | Register applies to Non-secure context banks                  |

|                     | SMMU_S2CRn  | SMMU_S2CRn, Stream-to-Context Register on page 9-218                        | Registers apply to Non-secure<br>Stream Match Register groups |

|                     | SMMU_SMRn   | SMMU_SMRn, Stream Match Register on page 9-228                              | Registers apply to Non-secure<br>Stream Match Register groups |

|                     | SMMU_CBn_*  | Chapter 17 Stage 2 Translation Context Bank<br>Format                       | Registers apply to stage 2 translation context banks          |

| Secure EL1&0        | SMMU_CBn_*  | Chapter 16 Stage 1 Translation Context Bank                                 | For Secure context banks                                      |

| Non-secure<br>EL1&0 | SMMU_CBn_*  | Format                                                                      | For Non-secure context banks                                  |

# Table 1-3 Translation regime control of SMMU registers (continued)

# 1.5 SMMU translation schemes

The SMMUv2 translation schemes support address translations required by both the AArch 32 and AArch64 Execution states, for each translation regime, as follows:

### AArch32 Short-descriptor translation scheme

This translation scheme:

- Uses 32-bit entries, or *descriptors*, in its translation tables.

- Is compatible with the ARMv7 architecture.

- Supports the translation of VAs of up to 32 bits.

- Supports output addresses of up to 32 bits, or up to 40 bits with loss of granularity.

- Can be used only from the AArch32 processor execution state.

- Can be used only for stage 1 translation.

#### AArch32 Long-descriptor translation scheme

This translation scheme:

- Uses 64-bit descriptors in its translation tables.

- Is added to the ARMv7 architecture by the Large Physical Address Extension (LPAE).

- Supports the translation of VAs of up to 32 bits.

- Supports output addresses of up to 40 bits, that can be IPAs or VAs.

#### AArch64 translation scheme

This translation scheme:

- Uses 64-bit descriptors in its translation tables.

- Is defined by the ARMv8 architecture.

- Supports the translation of VAs of up to 49 bits.

- Supports output addresses of up to 48 bits, as two independent address ranges.

In the ARM architecture, a *translation granule* is the smallest region of input address space that an SMMU implementation can be configured to support. A translation granule defines both:

- The maximum size of a single translation table.

- The memory page size, that is, the granularity at which attributes can be assigned to memory regions.

The AArch32 translation schemes use a translation granule of 4KB, meaning that the translation tables can define the attributes of memory regions at a granularity of 4KB.

Although the AArch32 Short-descriptor translation scheme has a translation granule of 4KB, it can support output addresses of more than 32 bits by using page sizes larger than 4KB.

The AArch32 Long-descriptor translation scheme:

- Has a translation granule of 4KB for stage 1 translations.

- By default, has a translation granule of 4KB for stage 2 translations.

The AArch64 translation scheme supports a translation granule of 4KB, 16KB, or 64KB.

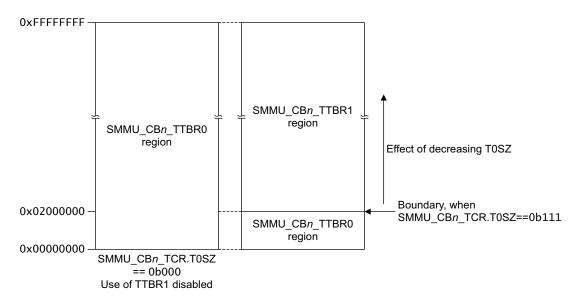

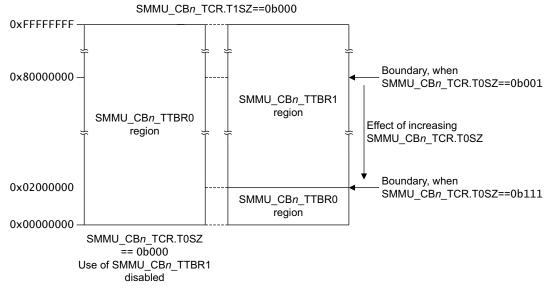

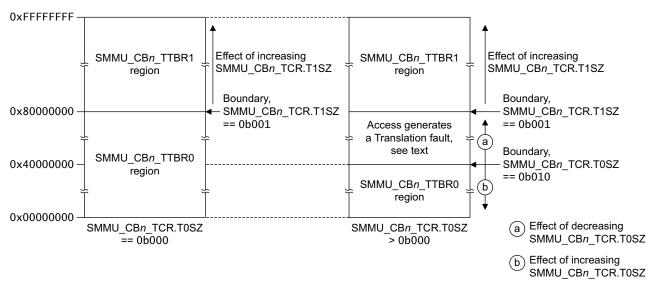

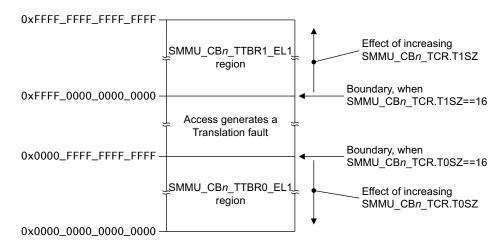

For EL1&0 stage 1 translations, the ARM architecture supports two VA subranges, determined by the SMMU\_CBn\_TCR.T0SZ and SMMU\_CBn\_TCR.T1SZ size fields:

- The AArch32 translation schemes provide these two subranges by splitting the available 32-bit VA range.

- In the AArch64 translation scheme, the two subranges are completely independent ranges of up to 48-bits, where:

- The lower VA range runs from 0x0000\_0000\_0000\_0000 to (Size indicated by T0SZ).

- The upper VA range runs from (0xFFFF\_FFFF\_FFFF\_FFFF (Size indicated by T1SZ)) to 0xFFFF\_FFFFF\_FFFFF.

There is always a gap between the two VA subranges.

The VA model for the AArch64 translation scheme can be described as using a 49-bit VA range, where VA[48] indicates the VA subrange for the address.

For more information, see Defining the VA subranges for stage 1 translations on page 1-30.

Table 1-4 shows the AArch64 translation regimes. All of these regimes use the AArch64 translation scheme, for all translations.

| Translation regime                      | Translation context                 | Note                                                                                        |

|-----------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|

| Secure EL3                              | Stage 1 context with stage 2 bypass | Monitor context only. See <i>Monitor contexts (MONC) on</i> page 2-87 for more information. |

| Secure EL1                              | -                                   | -                                                                                           |

| Non-secure EL2                          | -                                   | Hypervisor context (HYPC) only. See Hypervisor contexts                                     |

| Secure EL2 <sup>a</sup>                 | -                                   | (HYPC) on page 2-84 for more information.                                                   |

| Non-secure EL1&0, no EL2 <sup>b</sup>   | -                                   | -                                                                                           |

| Non-secure EL1&0, with EL2 <sup>c</sup> | Stage 1 followed by stage 2         | For stage 2, VMSAv8 Long-descriptor                                                         |

| Non-secure IPA address spaced           | Stage 2                             | Applies to device-based stage 1 translation and IPA generation                              |

# Table 1-4 AArch64 translation regimes

a. This translation regime does not correspond to an ARM processor architecture translation regime.

b. The implementation does not include EL2.

c. The implementation includes EL2.

d. This translation regime does not correspond to an ARM processor architecture translation regime, but is equivalent to the stage 2 translation of the Non-secure EL1&0 translation regime.

Table 1-5 on page 1-30 shows the AArch32 translation regimes, and translation schemes that can be used with each regime

# Table 1-5 AArch32 translation regimes

| Translation regime                      | Translation context                 | Note                                                                                                                                                                                                 |  |

|-----------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Secure EL1                              | Stage 1 context with stage 2 bypass | Either of:<br>• AArch32 Short-descriptor.<br>• AArch32 Long-descriptor.                                                                                                                              |  |

| Non-secure EL2                          | -                                   | AArch32 Long-descriptor, hypervisor context (HYPC) only.                                                                                                                                             |  |

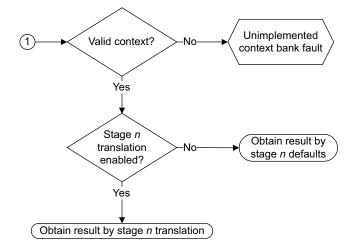

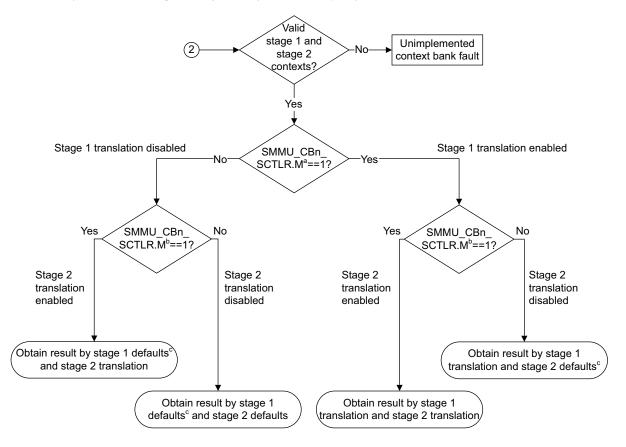

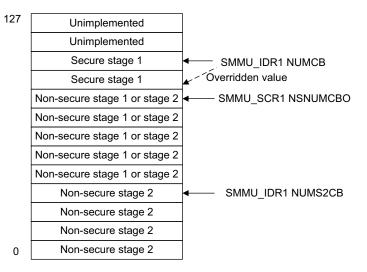

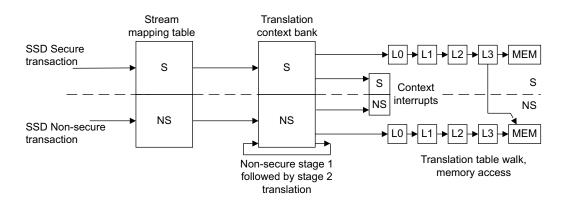

| Secure EL2 <sup>a</sup>                 | -                                   | See <i>Hypervisor contexts (HYPC) on page 2-84</i> for more information.                                                                                                                             |  |