# 80386 A Collection of Article Reprints

# 80386

# A Collection of Article Reprints

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, FASTPATH, GENIUS, i, <sup>1</sup>, ICE, iCEL, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>IBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or UPI and a numerical suffix, 4-SITE.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Distribution Mail Stop SC6-59 3065 Bowers Avenue Santa Clara, CA 95051

©INTEL CORPORATION 1986

3/86

## TABLE OF CONTENTS

# 32-Bit Microprocessor Can Run UNIX and MS-DOS Programs Concurrently

Timothy J. Keating; Jan Willem L. Prak, PhD; and Ken Shoemaker Electronic Design, October 17, 1985 .....

1

# 32-Bit $\mu$ P Is A Fine Match For Today's Languages and Operating Systems

# The Intel 80386—Architecture and Implementation

Khaled A. El-Ayat; Rakesh K. Agarwal IEEE Micro, December 1985 ..... 17

## Building With The 80386

Glen Shires Computer Systems, January 1986 ..... 37

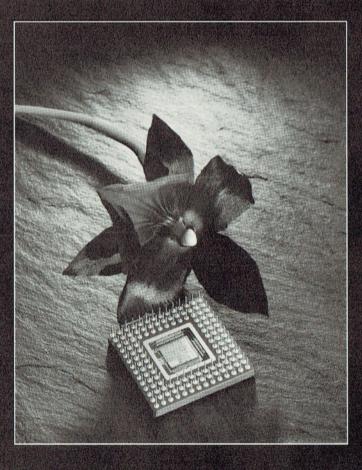

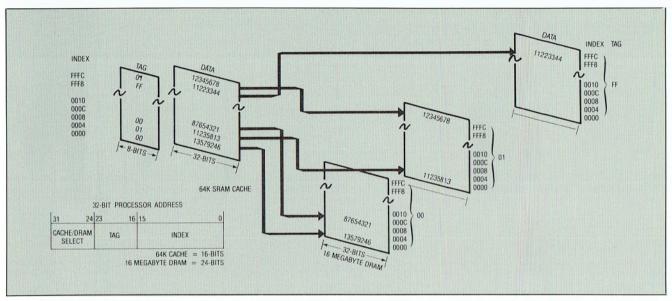

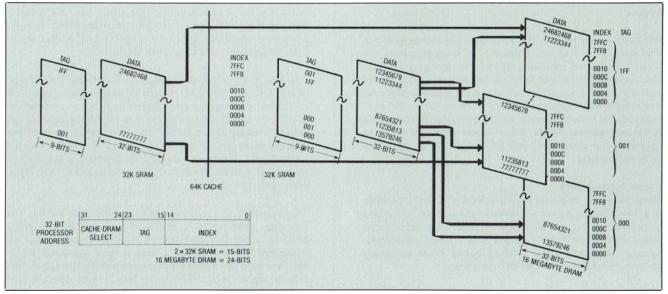

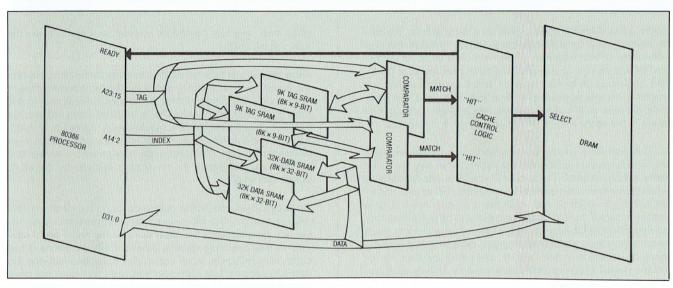

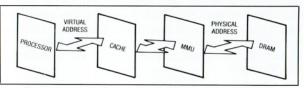

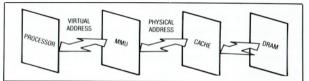

## 80386 Cache Design

Glen Shires Solutions, November/December 1985 ..... 43

51

TECH NOTES ----R and Brites American Magel

## Tech Notes On The 80386

Stephen E. Yoken; Paul Johnson; Peter D. Schleider; and James I. Magid Tech Notes, December 1985 .....

## INTRODUCTION

This collection of articles highlights the features, benefits, and market implications of Intel's new 32-bit microprocessor, the 80386. With its high level of performance and uniquely flexible architecture, the 80386 is an excellent match to the needs of a wide range of application areas from factory machine control to engineering workstations and multiuser departmental computers.

The first three articles provide an overview of the 386, with concentration on application and system software programming models. The flexibility of the 386, as well as the performance characteristics of its architecture are highlighted. Two additional articles discuss hardware design aspects of the 386, including the special features of the 386 that allow implementation of fast, efficient main memory and cache designs. Finally, the last article provides an overview of the implications that the 386 is expected to have on microprocessor and application markets.

I hope you find this set of articles useful in understanding the 386 and the substantial capabilities it offers.

\$7

Sincerely,

Sene Kill

Gene Hill 386 Product Line Director

Into

# 32-bit microprocessor can run Unix and MS-DOS programs concurrently

On-chip paged and segmented MMUs and 3- to 4-MIPS performance are just two of the noteworthy features that distinguish the latest 32-bit  $\mu$ P.

This is the first article in a three-part series on the 80386, the newest 32-bit microprocessor. It concentrates on the chip's hardware. The other articles will focus on the chip's features from the point of view of software, both operating systems and applications programs, and on the system design considerations.

ith the appearance of the first 32-bit parts, microprocessor-based systems began to encroach on the performance of minicomputers in applications like engineering workstations, high-resolution graphics, robotics, and office automation. Only large systems, however, could furnish most of the features needed by such advanced applications—primarily throughput and memory support.

System size need no longer be equated with performance. One 32-bit microprocessor now delivers an unprecedented 3 million to 4 million instructions every second. The 80386 also is the first to put paged and segmented memory management units on chip. Thanks in large part to the internal MMUs; to its binary compatibility with its 16-bit predecessors, the 8086 and 80286; and to hardware for fast context switching, it has a virtual machine capability, enabling it to switch between programs written for different operating systems, such as Unix and MS-DOS. Hence it opens the wide world of MS-DOS programs

### Timothy J. Keating; Jan Willem L. Prak, PhD; and Ken Shoemaker

Intel Corp., 3065 Bowers Ave., Santa Clara, CA 95051; (408) 987-7471.

to Unix systems.

Other features that add to the processor's punch are a pipelined architecture, a set of eight 32-bit general-purpose registers, a complete set of instructions for manipulating an extremely wide range of data types, and 11 addressing modes. (Included in the hardware is a barrel shifter that can shift up to 64 bits in a single clock cycle.)

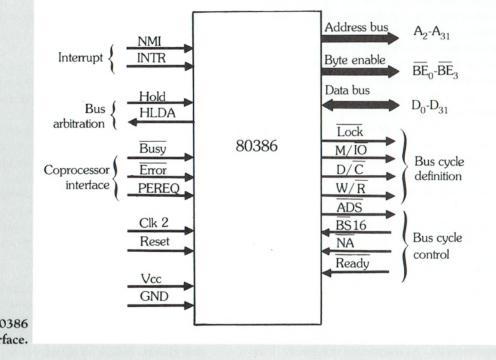

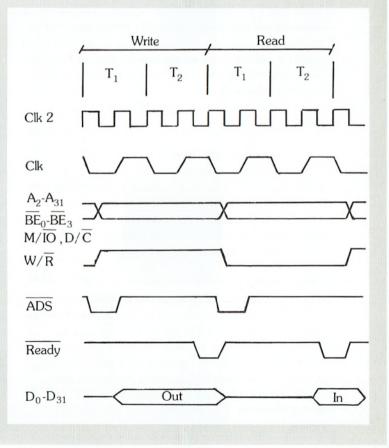

But the processor's accomplishments do not end there. A fast local bus and separate data and address buses, coupled with a two-clock access cycle, result in the highest bus bandwidth of any microprocessor— 32 Mbytes/s with a 16-MHz clock. The dual-clock bus timing accommodates high-speed local memories

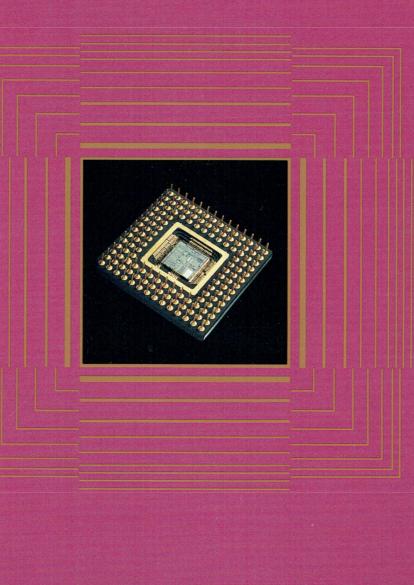

#### Cover: 32-bit microprocessor

and caches (static RAM); to work comfortably with slower memories (dynamic RAM), addresses can be pipelined.

Finally, the chip carries hardware for system debugging and self-testing to an extent not seen before in microprocessors. Specifically, four debugging registers furnish the ability to set data breakpoints, in addition to the more familiar instruction breakpoints.

#### Chip holds 275,000 devices

Making possible all that capability on a single chip are over 275,000 transistors. Fabricated using Intel's  $1.5-\mu$ m CHMOS III process, the 386 operates at a clock frequency of 12 or 16 MHz and consumes no more than 2 W. To allow nonmultiplexed buses and a large number of control lines, the device is housed in a 132-lead ceramic pin-grid array.

For memory management, the segmented and paged architecture, each backed up by a 32-entry

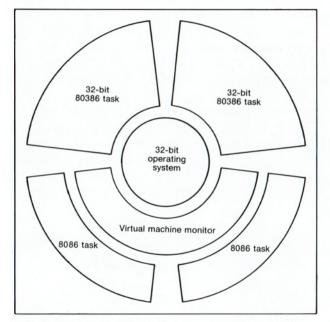

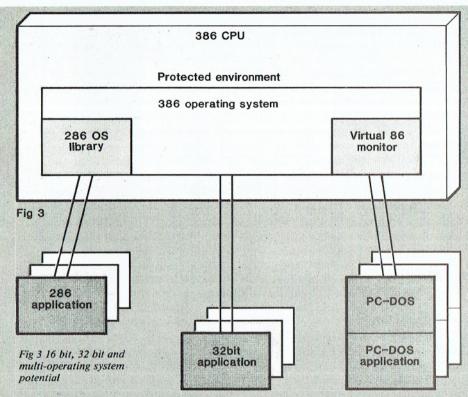

1. Suitable operating systems for the 32-bit 80386 microprocessor can run 16-bit applications as tasks by using a virtual machine mode. Both 32- and 16-bit programs—say, those written for Unix and MS-DOS—can run concurrently.

cache, allows designers to select the scheme they require. For simple applications, segment sizes can reach 4 Gbytes (the entire physical address space of the chip), thus supplying a linear address space for those programs that require it. The logical address space itself is awesome for a microprocessor— 64 terabytes (2<sup>46</sup> bytes).

In more sophisticated applications, segmentation ensures protection and modularity for any size code or data structure, while paging affords physical memory management in virtual memory systems. The designer can use segmentation alone, paging alone, or join the two to make the most of their power: The choice of memory management fits the requirements of the wide spectrum of 32-bit systems.

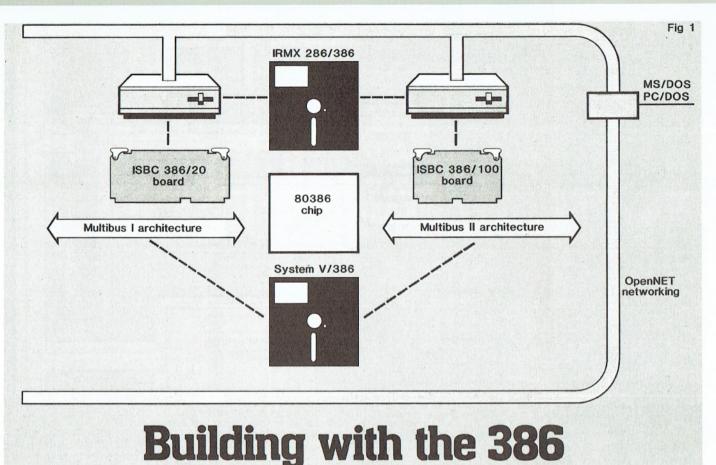

As indicated, designers that have developed programs that run on the processors' forerunners—the 8086, 80186, and 80286 families—will not be left out in the cold. The 80386 serves as a virtual environment that allows 8086 programs to run as guests under new, appropriately written 32-bit operating systems (Fig. 1). Programs created for the 8086 would be encapsulated within an 80386 task, and since 80386 tasks can be protected and paged in virtual memory, those two features would then be available to 8086 programs.

Furthermore, because the segmented memory management and protection mechanism of the 80286 and 80386 are identical, no changes are necessary to the operating system routines in charge of managing the memory. If paging is called for, routines to manage the pages can be added with the help of the segmentation software. Both 16- and 32-bit code can coexist in the same system, and each can even call the other, allowing new 32-bit code to make use of current 16-bit programs.

What's more, multiple 8086 programs can concurrently run on the same 32-bit processor, with each program appearing to have its own processor and address space. Paging handles mapping the processor address spaces to the disk for swapping, and the protection mechanisms come through with all the hardware hooks needed to implement a virtual machine monitor. (A virtual machine monitor, in this case, is a program that maps resources from the virtual machine—the 8086—to the host operating system.) The hooks include I/O and address space protection traps and interrupt traps that allow the monitor to emulate the virtual environment. Operating systems, peripheral devices, and even bitmapped graphics programs can thus be emulated. Since memory management is done on chip, the processor avoids the serious performance degradations caused by wait states, which are inherent in systems that use off-chip memory management. Also, since the management functions are always available, memory management software standards are possible—a key point that allows freedom in porting operating systems between different 386-based systems.

#### Performed by an octet

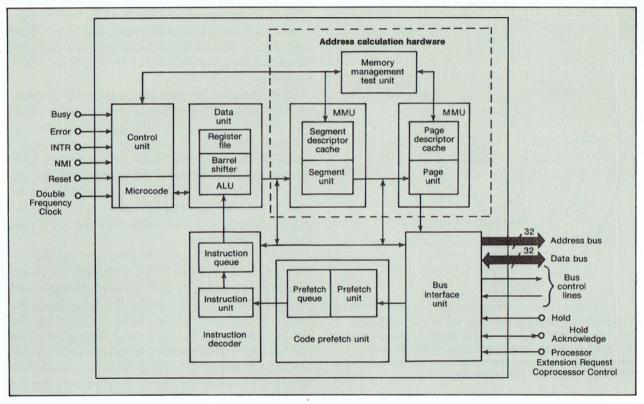

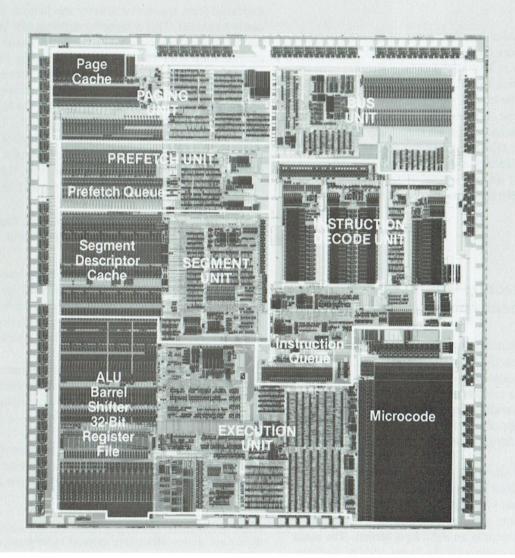

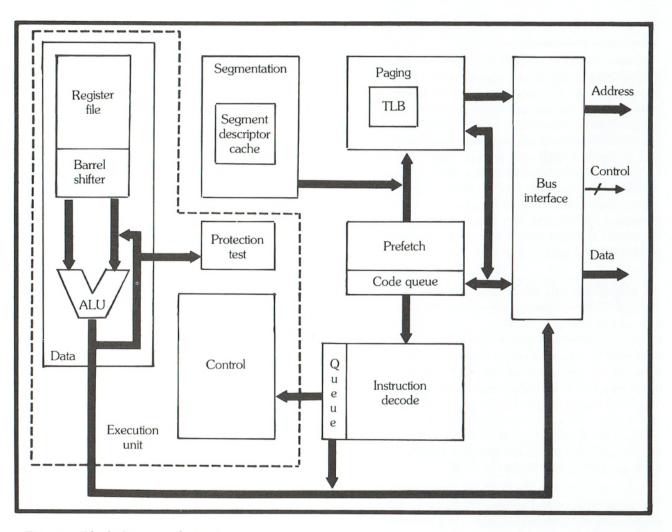

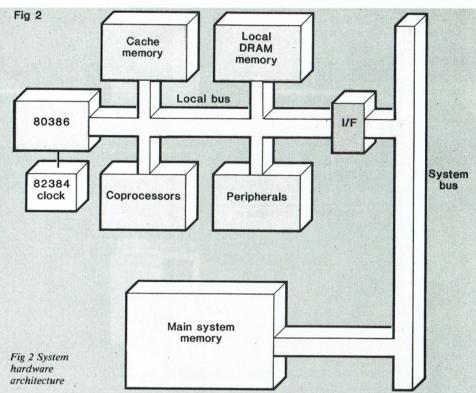

Within the chip the instruction processing is broken up into eight steps, with each performed by a separate optimized processing unit (Fig. 2). That scheme allows every step of any instruction to be completed quickly. It also permits several instructions to be in progress simultaneously, each in a different stage of execution.

The bus interface unit performs external bus accesses; while the bus is idle, the prefetch unit fills an operation-code queue. The instruction decoder deciphers the op codes to fill an instruction queue. In the data unit are the ALU, registers, and the 64-bit barrel shifter, all of which are manipulated by the microcode in the control unit. The latter unit, which also contains interrupt, processor, and coprocessor control circuitry, executes commands that come from the instruction queue.

The segmentation unit converts logical addresses into linear addresses using the chip's segment descriptor cache. The paging unit incorporates a 32-entry descriptor cache to convert linear addresses into physical addresses. Finally, the memory management test unit performs checks for protection violations and for the presence of pages in external memory, as well as other memory management functions.

#### Fast—and flexible

Although the processor can run at 16 MHz, it does not require premium-speed memories. To take advantage of slower chips for main memory, the chip adds a novel control input, called Next Address. The input allows external hardware to switch from the bus's fast two-clock access to a slower pipelined mode in order to increase the address access time without decreasing the data bus bandwidth. Address pipe-

2. Divided into eight subprocessing units, the 80386 microprocessor takes full advantage of pipelining to permit many of the subunits to operate in parallel. The architecture helps produce a speed of 3 to 4 MIPS.

#### Cover: 32-bit microprocessor

lining works by overlapping the address of the next bus cycle with the data already on the bus during the last clock of the previous bus cycle. Thus the pipelined cycle has a three-clock-cycle latency from address to data but consumes only two clocks on each of the address and data buses to maintain the 32-Mbyte/s bandwidth.

To remain compatible with 16-bit hardware, the processor can change the bus size during any bus cycle. That allows systems to mix 16- and 32-bit peripherals, buses, and memory boards, thereby enabling users to take advantage of the broad range of readily available peripherals.

An input signal called Bus Size 16 (BS<sub>16</sub>) can be activated by, say, an external memory system. The chip will automatically convert transfers that are larger than 16 bits or are misaligned into two transfers. The entire function is invisible to the programmer, who can continue to write code independent of the bus width. As a result, the external hardware required to support both main 32-bit memory and 16-bit I/O, EPROM, or system bus is easy to design.

#### **Full sets**

Within the data unit are eight interchangeable 32-bit general-purpose registers. Any of these registers can be used as accumulators for arithmetic or logical operations, as address registers, or as data registers. Additionally, they can handle 8- or 16-bit operations. For the latter, the low word (16 bits) of each register is directly accessible. For 8-bit operations four of the 16-bit registers can be split into pairs of separate 8-bit registers.

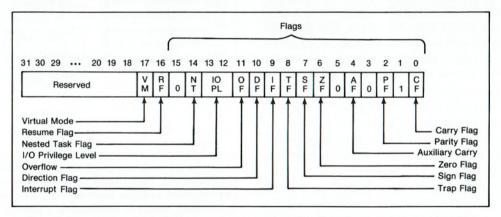

Full 32-bit instruction pointer and flags registers record and control the processor state. The instruction pointer contains the full 32-bit offset of the next sequential instruction to be executed. The flags register contains three kinds of flags (Fig. 3). The status flags reflect the outcome of computations such as parity, sign, and overflow. The control flags modify the operation of some instructions—for example, direction flag is set to control self-incrementing/decrementing indexes for block move instructions. System flags control system-wide resources and functions like I/O privilege, external interrupt masking, and virtual machine control.

#### Many options

The processor's instruction set is a superset of the 8086's that provides for full 32-bit data and address manipulation; among its enhancements are a full complement of bit manipulation commands. Most instructions operate with any general-purpose register and allow for 8-, 16-, or 32-bit operands. A wide spectrum of data types can be handled—integers, bytes, strings and bit strings up to 4 Gbits long.

On the average, the typical instruction length has been kept to just 3.1 bytes, and the average instruction time has been reduced to 4.4 clock cycles. Short instructions and low instruction clock counts form the base for the 386's 3- to 4-MIPS performance. Many factors combined to give these impressive results, some of the most notable being the fast 64-bit barrel shifter and multiplication and division hard-

3. The 13 flags in the 32-bit flags register can be divided into three classes: status, control, and system. The first class indicates the result of computations, the second modifies how some instructions are executed, and the third governs systemwide resources.

ware that yields 32-bit results in 0.5 to 2.4  $\mu s$  (when the chip runs at 16 MHz). The barrel shifter operates in parallel with the ALU to speed bit manipulations, multiplication and division, and shifting and rotation.

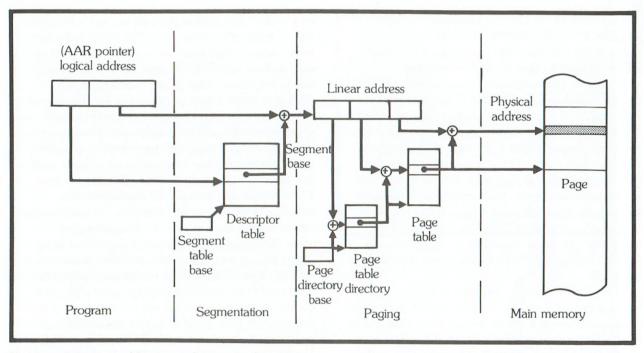

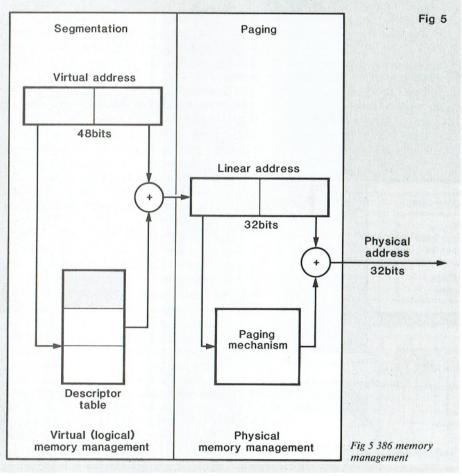

Virtual memory management makes it possible for programs larger than physical memory to be transparently mapped from secondary storage to physical memory. Consequently, very large programs can be written without regard to the main memory size of different target systems. Address translation, swapping, and protection data are kept in memory-based lookup tables. Operating systems and memory management hardware use this information to translate from logical into linear into physical addresses and make program protection checks.

Within the processor, the first step in the translation is through the segmentation unit. Segmentation manages each user's logical memory—differentsized segments (up to 4 Gbytes) can be set up for code modules and different types of data (file buffers, program variables, work areas, and so forth). The programmer can also break up logical memory according to the organization of program routines, thus permitting different routines to be modularly compiled at separate times. By nature, both code and data vary in size; segmentation ensures the right virtual memory fit, assigning only as much memory as needed for the individual routines and data. It is a way of directly relating memory organization and usage to program code and data structures.

#### Logical addresses for segmentation

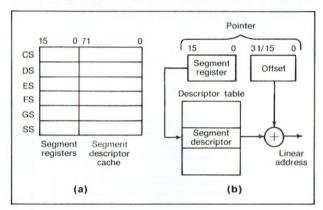

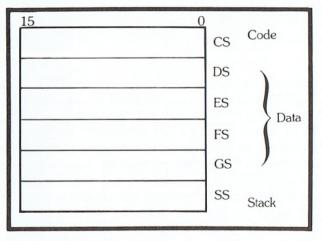

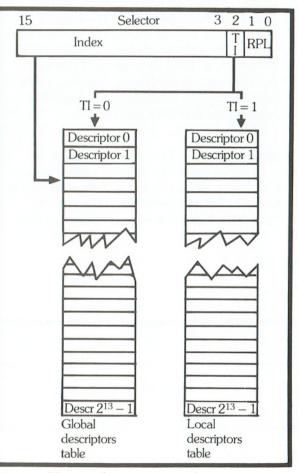

Under segmentation, the addresses that the programmer sees are called logical addresses. The logical address (48 bits) consists of a 16-bit segment selector and a 32-bit segment offset. The segment selector indexes into a table of segment descriptors. Segment descriptors contain the base address, the limit, and the access rights (such as read-only or read/write) and "privilege" information that specify the type of accesses that are permitted to the segment. To keep the speed high, current segment selectors and descriptors are automatically loaded at program initialization into six high-speed segment registers (Fig. 4a).

The 48-bit addresses are transformed by the segmentation hardware into a 32-bit address called a linear address. That transformation is performed by adding the segment offset to the 32-bit segment base value held in a segment register (Fig. 4b). In doing the transformation, the segmentation hardware checks the access against the limit and access rights for the segment used to ensure the integrity of the memory reference. If the chip's paging mechanism is disabled, the calculated linear address becomes the physical address used by the processor.

Further, programmers need only manipulate offsets as effective addresses. Instructions need not explicitly specify which segment register is used, because the correct segment register is automatically chosen for each instruction. Code references use the code segment (CS) register, data references use the data segment (DS) register, and stack references use the stack segment (SS) register. Three extra, uncommitted segment registers add flexibility—for example, when manipulating multiple data structures. The extra registers (ES, FS and GS), reflect the way programs are written, that is, as independent modules that require areas for code and data, a stack, and access to external data areas.

Since there is the potential for segments as large as 4 Gbytes, an efficient mechanism to manage physical memory becomes necessary. Although such management is not an issue for static systems, transferring large segments of hundreds of kilobytes between disk and physical memory can be slow and cumbersome in dynamic systems. Consequently, the processor uses its paged memory manager to handle the physical memory.

When operating under segmentation, the chip breaks up large segments into small fixed-size

4. To handle segmentation, 48-bit words are divided into a 16-bit segment register and a 72-bit descriptor cache (a). To perform segment computations, the segment register points to the desired segment descriptor, which is automatically loaded into the cache, and the descriptor is added to the offset value to form a 32-bit linear address (b).

### Cover: 32-bit microprocessor

blocks. Instead of loading the entire segment, the operating system loads the individual pages as needed. That simplifies the management of physical memory. It also allows for small amounts of physical memory to be allocated for each task; rather than having many megabytes per task present in physical memory, the operating system only needs to keep a current working set of pages. The approach takes advantage of the locality of reference displayed by most programs and supports efficient management of physical memory, both main memory and swapping storage.

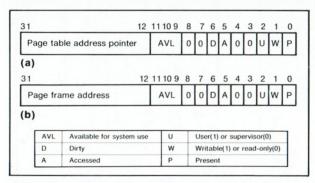

The page-based protection mechanism allows easy implementation of a demand-paged virtual memory system. To support page-based virtual memory, each 4-kbyte page can be designated as present or not present, dirty, accessed, user/supervisor, or read/ write. If a page is not present, it must be restored to physical memory before it can be accessed. Whenever a page that is not present is accessed, the processor signals the operating system by raising a page fault indicator. The operating system page fault handler would typically pull the page in from disk, and then the faulting instruction is restarted. Every instruction may be restarted after a page fault.

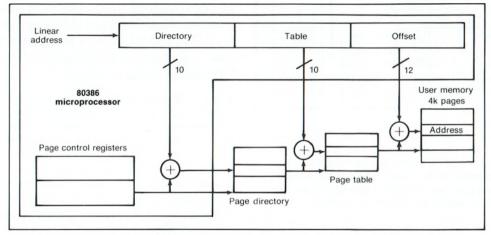

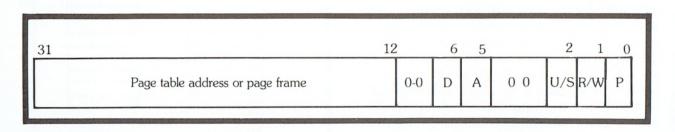

The programmer controls paging through two levels of memory-based tables and two internal registers (Fig. 5). At the lower level, the page tables map the pages; at the higher level a page directory maps the page tables. An entry in a page directory or a page table requires four bytes, and each page directory and each page table is 4 kbytes long. Thus each contains 1024 entries. Hence only a single page directory, mapping 1024 tables, need be used to map the entire 4-Gbyte linear address space.

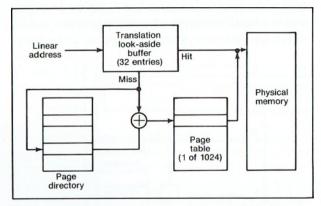

To ensure high performance, the memory-based page tables are not actually referenced for each physical address translation; instead the chip includes a 4-kbit associative cache for paging information. The cache, which is called a translation look-aside buffer, or TLB, contains the most recently used linear addresses and their translated physical addresses.

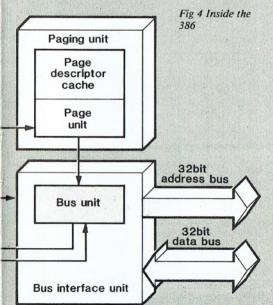

The cache is implemented with on-chip hardware consisting of control logic and a 32-entry page descriptor cache (Fig. 6). Since the address translation caches are part of the memory management unit, address translation can be done in parallel with other CPU activities.

The cache is organized as a four-way set-associative type. With such a cache and the 4k-page size, the processor can internally hold the mapping information for 128 kbytes of memory. Simulations show that this setup provides a hit ratio of greater than 98%, thus minimizing the performance impact of enabling the paging. The address generation time is the same when paging is enabled or disabled; however, there is a small performance penalty paid (2% to 4%) when page table entries must be fetched from exter-

5. The two-level paging scheme starts with the page directory and then moves down to the page table, which maps the pages. Once the page is located, its address is added to an offset value to access the desired address in main memory.

#### Cover: 32-bit microprocessor

nal tables on cache misses.

To allow multiple programs to execute concurrently, the operating system must be able to support multitasking. Because task switching occurs so frequently, special high-speed hardware to perform the operation was included on the chip, permitting a complete task switch with a single instruction or in response to an interrupt. A 16-MHz processor can save the state of one task (all registers), load the state of another task (all registers, including segment and paging registers if required), and resume execution in less than 17  $\mu$ s.

#### **Avoiding accidents**

One of the most common problems in multitasking systems occurs when a task accidentally violates the address space of another, thereby using or modifying the other task's code or data. To counter that problem, the processor permits any task to have a separate address space, which is enforced by hardware. The protection mechanism also offers up to four privilege levels to protect sensitive code and data within a task. Additionally, read, write, read/write, and execution privilege can be granted on a segment or page basis. That allows a combination of operating system, system services, shared libraries, and appli-

6. To speed the page lookup process, a 32-entry page descriptor cache, or translation look-aside buffer, is included in the MMU. The cache permits page addresses to be looked up quickly when the desired page is not in the physical memory.

cation programs to reside in a common virtual address space, yet still to be protected.

For software design, one of the most time-consuming phases is integration and debugging. External program debugging tools are used to test and monitor the operation of each module as it interacts with other modules, but hardware support for these software tools has been very limited, with only simple instruction breakpoint interrupts and single-step capabilities.

The processor contains a set of four debugging (breakpoint) registers into which linear addresses can be placed by a software debugger. If the processor attempts an access to the address in one of these registers, it will trap to the debugger. The processor can be set to trap when a memory read, a memory write, either a memory read or a write, or an instruction execution is attempted to the address in one of these registers. These registers thus simplify the design of sophisticated debuggers and allow the designer to implement features that were not possible without hardware support, such as breakpoints on data reads and writes and breakpoints in ROM.

To simplify the design of such diagnostics as power-up system confidence tests, the processor can be directed to test itself upon reset. When so requested, it enters a mode in which it tests over 75% of its 275,000 transistors. After the check is performed, a result signature is placed in two of the chip's general-purpose registers and the processor begins executing code at the normal reset location. Usersupplied restart code can then check the signature from the internal self-test to ensure that the processor is operating properly before attempting to perform any meaningful work.□

Timothy Keating, a product manager, has been with Intel for four years and has held various positions in the company's U.S. and European operations. He received a bachelor's degree in computer and electrical engineering from the University of Santa Barbara.

A senior project manager, Jan Prak also has worked at Intel for four years. He earned doctoral and master's degrees at North Carolina State University.

Ken Shoemaker, a graduate of Purdue University's Electrical Engineering program, is a design engineer.

Into

# 32-bit μP is a fine match for today's languages and operating systems

By supporting the data types, constructs, and other features of modern languages, a microcomputer can outperform minis while remaining compatible with its predecessors.

This is the second article in a series on the 80386 microprocessor. The first part, which appeared in the Oct. 17 issue (p. 115), focused on the chip's architecture. The final installment will cover system design considerations.

or many microprocessor-based systems, software has become the dominant development consideration. All too often, it also is the premier cause of delays. Systems like multitasking engineering workstations, multiple-cell process controllers, and multiuser transaction processors usually incorporate sophisticated software. To be successful, then, a high-end microprocessor must satisfy stringent software demands.

First and foremost, a 32-bit processor must accommodate efficient compilers. That way both operating systems and application programs will reflect the device's inherent abilities. Second, the chip must also deliver the high throughput required by advanced software. Third, the chip must support the large logical address spaces required for programs run by both engineering and business workstations. Fourth, ensuring that confidential data remains secure is a key concern in military and financial applications. Finally, compatibility with previous microprocessors is highly desirable, so that existing software remains usable.

The 32-bit 80386 makes the grade on all of these is-

**Rakesh Agarwal, Greg Blanck,** and **Dana Krelle** Intel Corp., 3065 Bowers Ave., Santa Clara, CA 95051; (408) 987-5778. sues. Its extensive register set, as well as some of the types of data it handles, is geared to writing efficient compilers and guarantees fast context-switching in real-time systems. Further, its rich set of data types and operators make sure that it is fluent in nearly all of today's sophisticated languages. The chip's segmentation and paging units fill the bill when the large logical address spaces are the order of the day, and its levels of protected memories keep the most sensitive data safe. Lastly, to ensure that already written code remains current, the processor's protected mode enables it to execute unaltered 8086 and 80286 code automatically.

#### **Unrestricted registers**

Naturally, the chip's power is rooted in its main architectural features. Its set of 32-bit general-purpose registers, for one, may be used, without restriction, either to carry out calculations or to form memory addresses. The eight registers (EAX, EBX, ECX, EDX, ESP, EBP, ESI, and EDI) supply ample room to implement the most common addressing modes, or to accommodate a generous set of register variables without wasting silicon. Furthermore, the set incorporates the 286's 16-bit registers, some of which consist of 8-bit segments.

Three control registers and the flags register oversee machine behaviour and report the status of various operations. For their part, the six segment registers (CS, DS, ES, FS, GS and SS) can structure the 64-terabyte (2<sup>46</sup>-byte) address space into separate logical spaces, or segments (Fig. 1). Each

#### 32-bit microprocessor

program can then have six logical address spaces mapped at one time, including four data spaces. Furthermore, six debugging registers permit up to four code or data breakpoints to be defined, making for previously unrealizable debugging ease.

One common use of registers is to store operands. For instance, to perform the simple computation Distance = Speed  $\times$  Time, the following instruction sequence might be used:

| MOV  | EDI, ESI | ; | Save Speed in EDI        |

|------|----------|---|--------------------------|

| IMUL | EDI, EBX | ; | Multiply Speed with Time |

Here, Speed is originally stored in ESI and Time in EBX; the result is stored in EDI. When it comes time to write the compiler, such a scheme is especially effective for languages like C that define register variables. The orthogonal qualities of the processor's addressing modes provide the user with several register variables.

If the variables do not reside in registers, operands must be fetched from memory. In its simplest form,

1. In the 80386 register set, the general registers can be used to store 8-, 16-, and 32-bit data (highlighted). Together with part of the segment registers they can substitute for the 80286 register set to execute 16-bit programs (overlay). The instruction pointer covers the full address space, and the large set of flags supports complex systems. the effective address (or byte index) of an operand within a given logical address space can be directly specified in an instruction. A particular memory address, however, is often not known until the program is actually executing—say, in accessing a dynamic array and executing relocatable code. In those cases, the microprocessor forms an effective address by summing the contents of one, or two, generalpurpose registers and an optional constant value, or displacement.

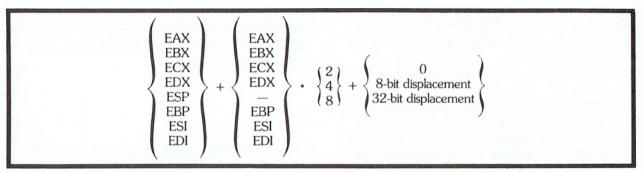

An effective address, EA, is generated by:

$Base + Index \times Scale + Displacement$

where the base value can be stored in any general register, and the index in any general register other than ESP, whose contents always point to the current stack and can be easily used for stack-relative addressing. The scale is a constant value -1, 2, 4, or 8 (depending on word length)—by which the index may be multiplied. The displacement field is also a constant; its value may range anywhere from  $-2^{31}$  to  $+2^{31}$  -1. Because the base, index, and displacement are optional, as is the scale when an index is present, the processor supplies 11 distinct 32-bit addressing modes. That set contains all of the most commonly used modes employed by compilers for advanced high-level languages (Table 1). In addition, direct and register operands are also furnished.

#### **Base displacement**

Assume that parameters are passed to a subroutine by pushing them onto a stack. The last parameter could be obtained from register EAX in two clock cycles by using the base-displacement mode:

#### MOV DWORD PTR [ESP+4], EAX

Similarly, suppose that the pointer nextRecord is stored in register EAX. In four clock cycles, it can be linked into a data structure—without additional overhead—using the instruction:

#### MOV EAX, DWORD PTR [EAX+LinkOffset]

Finally, imagine that V points to a dynamically allocated integer vector and that the term V[i+2]should be initialized to 5. If V is loaded into the ESI register and is a register variable stored in EDI, the following statement performs the desired operation in three clock cycles, working with the based scaledindex displacement mode:

MOV DWORD PTR [ESI+EDI\*4 + 8], 5

The use of scaled indexing to generate a byte index into a 4-byte integer array eliminates the need for another instruction to generate the byte index.

The processor's high performance is manifested in

the low clock counts required for each of the instructions. A lid is kept on clock counts because, when executing in-line code, the effective address formation for a given instruction starts during the last clock cy-

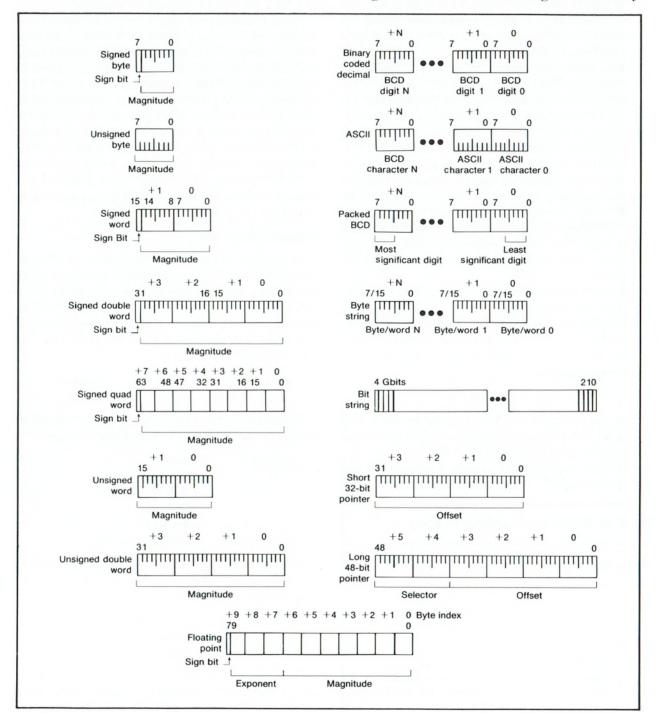

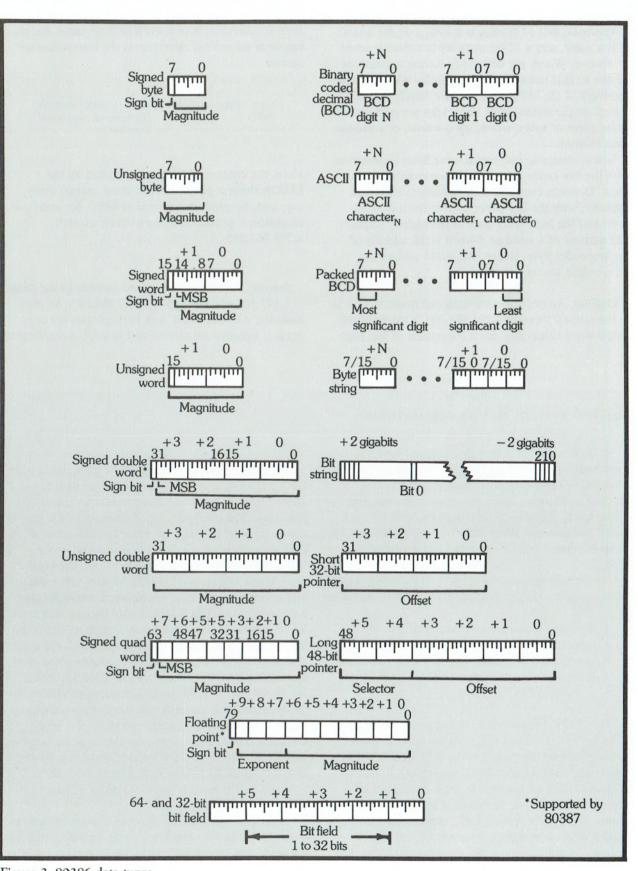

2. Binary coded decimals, bit and byte strings, and floating-point integers are among the numerous data types that the processor accommodates. Such dexterity lets the device meet the needs of virtually all high-level languages. (Unless otherwise noted the left-most digit is the most significant one.)

### 32-bit microprocessor

cle of the previous instruction. Since it takes only one clock cycle to form an effective address (except when an index is specified), the address formation time is almost always hidden.

Since memory management is on chip, time taken to create the effective address includes the logical-tophysical address translation. Thus the processor exhibits virtually no address generation and translation delays. Only when an index is used, a second clock cycle is needed to create an effective address.

To extend its usefulness and to protect existing software, the microprocessor is compatible with the addressing modes of all of the 16-bit members of the 8086 family. Moreover, the processor supports all of the fundamental data types found in most high-level languages (Fig. 2). Its basic operations, when applicable, can work with any of these data types (Table 2).

To start, an integer is a two's complement signed number in the range of  $-2^{31}$  to  $+2^{31}-1$  (about  $\pm 2.15$  billion). If only smaller numbers are needed, 16- and 8-bit signed integers are also supplied. An example of an integer operation can be seen in the instruction sequence:

#### IMUL EBX, V [EDX\*4]

Here, the contents of the EBX register are multiplied with the Nth element of the integer array V, where N is stored in EBX and the result in EDX.

Ordinal numbers are unsigned integers in the range 0 though  $2^{32}-1$ . As with integers, 32-bit 16-bit,

| Comp                  | onents of address                                                                                                                                                                   |                  | Mode                                                                          |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|--|

|                       |                                                                                                                                                                                     | Disp             | Displacement only                                                             |  |

| Base<br>Base          |                                                                                                                                                                                     | + Disp           | Base only<br>Base displacement                                                |  |

|                       | $\begin{array}{l} \operatorname{Index} \\ \operatorname{Index} \times \operatorname{Scale} \\ \operatorname{Index} \\ \operatorname{Index} \times \operatorname{Scale} \end{array}$ | + Disp<br>+ Disp | Index only<br>Scaled index<br>Index displacement<br>Scaled index displacement |  |

| Base                  | + Index                                                                                                                                                                             |                  | Based index                                                                   |  |

| Base                  | + Index × Scale                                                                                                                                                                     |                  | Based scaled index                                                            |  |

| Base                  | + Index                                                                                                                                                                             | + Disp           | Based index displacement                                                      |  |

| Base                  | + Index $	imes$ Scale                                                                                                                                                               | + Disp           | Based scaled<br>index displacement                                            |  |

| Register<br>Immediate |                                                                                                                                                                                     |                  | Register operand<br>Immediate operand                                         |  |

and 8-bit variants of ordinals are available.

Another data type is the pointer, which identifies a memory address. All pointers have two components: a 16-bit selector that names the logical address space and a 32-bit effective address, or offset, that specifies the byte index within the logical address space. Since addresses can be generated with an implied selector, the full 48-bit selector-offset pair can often be abbreviated as the 32-bit offset, which can address a linear 4-Gbyte address space. A compact version features a 16-bit selector and a 16-bit offset, which also works with 8086 family software (A more detailed discussion of the addressing mechanism can be found in part 1, Oct. 17, p. 115).

#### Accessing single bits

In system software, individual bits must often be accessed. Single bits or contiguous sequences up to 31 bits long can be retrieved from—or stored in—a string that extends to 4 Gbits. An example implements a semaphore by performing an atomic (locked) test-and-set on the second bit of the sema byte and waiting until the bit is clear:

| waitLp: | LOCK BTS | sema, 2 |

|---------|----------|---------|

|         | JC       | waitLp  |

Alternatively, consider a C program fragment that defines the bit fields for the variable accessRights:

| struct | Present: 1;                |

|--------|----------------------------|

|        | DPL : 2;                   |

|        | Seg : 1;                   |

|        | ECRA: 4;                   |

|        | accessRights;              |

|        | regVar = accessRights.DPL; |

Assuming regVar is a register variable stored in ESI, this code translates directly into the processor instruction sequence:

| MOV  | CL, 2; setup field length        |

|------|----------------------------------|

| MOV  | EAX, 5; setup field offset (1+4) |

| XBTS | ESI, accessRights, EAX, CL       |

To facilitate floating-point operations, the chip can be teamed with either the 80287 or 80387 math coprocessor. Both augment the types of data that the processor manipulates to encompass 64-bit long integers, 18-digit BCD integers, 32-bit single-real values, 64-bit double-real formats, and 80-bit extended-real digits. The coprocessors also furnish a comprehensive set of numeric instructions suited to these data types.

To accommodate BCD numbers, primitives are supplied that help set up both packed and unpacked decimal arithmetic. In addition, arithmetic operations on 80-bit packed decimal numbers are fielded by the math coprocessors.

The processor also is targeted for 64-bit operations such as multiplying integers and ordinals. Divisions that yield 64-bit products and dividends are also within its grasp, and multiple precision addition and substraction are implemented easily with the help of add-with-carry and subtract-with-carry operations.

#### More than math

Beyond arithmetic, the processor also carries out 64-bit shifts with 32-bit results. Those calculations are useful for creating high-performance loops to process unaligned, memory-based operands. A routine to move a bit string from one location to another -one double word at a time-might be desired in a bit-mapped graphics system (see the program, p. 167). First, however, the counter variable must be set and the source pointer, SP, incremented. Assume here that register ESI holds a double-word-aligned source address. Register CL stores the bit offset BO that points to the start of the bit string, and EDI contains the destination address.

The routine assumes that the destination is double-word aligned. If it is not (i.e., if an arbitrary bit field is selected), it is only necessary to move sufficient bits from the source to the destination to align the latter. Then the program can be used.

So far the processor has been looked at only from the application program's point of view. Equally important is the view from the side of the operating system that manages the application environment. By including many of the features required by an advanced operating system on chip, the processor establishes the framework to design fast, simple, and standard operating systems.

Such operating-system support is totally invisible to the application program. Functions featured on chip include a versatile memory management unit that encompasses segmentation and paging. Also, fast task switching in hardware facilitates efficient multitasking, while the ability to dynamically execute and address 16- and 32-bit code further enhances the chip's versatility.

An operating system, in addition to allocating memory, must isolate and protect each application from all others. Both segmenting and paging can be used to enforce this isolation. For example, the access control field of the segment descriptor handles many different types of information. A read-only segment, say, could be defined to hold sensitive system configuration data. Alternatively, an execute-only code segment might be created to ensure that a program will not be corrupted. Other segment types, such as the task state, are on hand to improve execution speed. And an operating system is free to dynamically create segments as required by the executing application. In fact, the chip can assign up to 16,384 segments to a task. Combined with the 32-bit offsets,

|                                                             | Type of expression |         |        |               |                    |                  |  |  |  |

|-------------------------------------------------------------|--------------------|---------|--------|---------------|--------------------|------------------|--|--|--|

| Operation                                                   | Integer            | Ordinal | String | Bit<br>string | Floating-<br>point | BCD              |  |  |  |

| Move<br>To and from memory,<br>convert precision            | Yes                | Yes     | Yes    | Yes           | Yes <sup>1</sup>   | Yes <sup>2</sup> |  |  |  |

| Arithmetic<br>Add, subtract,<br>multiply, divide,<br>negate | Yes                | Yes     | No     | No            | Yes <sup>1</sup>   | Yes <sup>2</sup> |  |  |  |

| Logical<br>And, Or,<br>exclusive OR,<br>shift               | Yes                | Yes     | No     | No            | No                 | No               |  |  |  |

| Compare                                                     | Yes                | Yes     | Yes    | Yes           | Yes <sup>1</sup>   | Yes <sup>2</sup> |  |  |  |

| Transcendental<br>functions                                 | No                 | No      | No     | No            | Yes <sup>1</sup>   | No               |  |  |  |

Available directly with 80287 or 80387 math processors.

ASCII and decimal adjustment instructions are supplied to implement efficient loops. BCD is supported directly by the 80287 and 80387 math coprocessors.

#### 32-bit microprocessor

that makes for the aforementioned logical address space of 64 terabytes that is available for each task. Besides relocation and protection, descriptors also deliver semantic controls for each segment, used to specify the word length of its contents.

Because the processor's segmentation mechanism is capable of incorporating various degrees of protection in a system, the integrity of a program address is always guaranteed. Specifically, an application-generated offset is added to the segment's base value to create the linear address. If the offset is greater than that allowed by the segment descriptor's limit field, a protection violation occurs. A semantic control bit, called the Granularity bit (G bit), interprets the limit field within the descriptor: A value of 0 indicates an absolute limit (byte-granular limit); 1 signifies that the restriction specifies a page (page-granular limit).

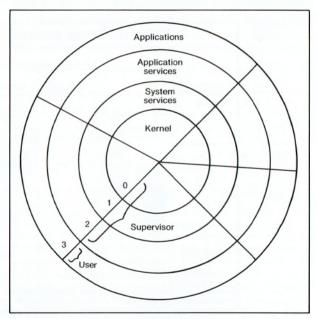

#### Levels of privilege

The limit fields are supplemented by program level protection, which is based on privilege levels. The access right byte of each segment descriptor contains a descriptor privilege level (DPL) that identifies the access permitted for a particular segment. Privilege levels range from 0 to 3, with the first being the most privileged (Fig. 3). At any point, the processor's current privilege level (CPL) is determined by the privilege level of the executing code segment.

As a rule, a program has the right to access segments that are no more privileged than itself and to call other programs that are at least as privileged. Interlevel transfers are fielded by a special descriptor, the call gate, which furnishes a controlled entry point to more privileged routines.

Intertask protection is furthered by defining an individual local descriptor table (LDT) for every task. Using a separate LDT logically isolates each applica-

|       | A double          | e | -word shift                                             |  |

|-------|-------------------|---|---------------------------------------------------------|--|

|       | MOV EBX, Length   | ; | Set loop counter to string length                       |  |

|       | LODS EAX, [ESI]   | ; | Grab first DWORD,<br>increment SP                       |  |

|       | MOV EDX, EAX      | ; | EDX = first DWORD                                       |  |

| loop: | LODS EAX, ESI     | ; | Grab next DWORD,<br>increment SP                        |  |

|       | SHRD EAX, EDX, CL | ; | Align DWORD shifted by<br>CL bits                       |  |

|       | XCHG EDX, EAX     | ; | Swap EAX with EDX                                       |  |

|       | STOS [EDI], EAX   | ; | Store aligned data,<br>increment EDI                    |  |

|       | DEC EBX           | ; | Decrement loop count                                    |  |

|       | JA loop           |   | Repeat loop if $count = 0$<br>R indicates contents of R |  |

tions address space.

Several other semantic control bits reveal the processor's power. One, the Default Size bit (D bit) determines whether code segments will assume 32-bit (D is set to 1) or 16-bit (D is set to 0) operands and operations. The Expand Down bit (E bit) defines whether a given data segment needs an expand-down or expand-up stack, and interprets the limit field accordingly. Importantly, all of these semantic controls permit dynamic switching between 16- and 32-bit code, segment by segment. That power makes it easy to vary between unchanged 8086 or 80286 software and new 32-bit code.

#### **Double-level page map**

The processor incorporates a two-level page translation mechanism that allows any 4-kbyte linear address page to be mapped into any arbitrary 4-kbyte section of physical memory. The double-level page map for the current task is located in memory by a pointer in control register 3 (CR3), which is also called the page directory base register. All page tables are located on page boundaries, to ensure that they are efficiently manipulated. For each page in the logical memory space, a page descriptor is defined (Fig. 4). It contains the physical address corresponding to each logical page, as well as other page

3. Of four protection levels, the top three (0-2) are assigned to the supervisor. The lowest is allotted to user code. Such a system is more suitable for multi-tasking than one with a single supervisory level.

status information.

To speed translating from linear to physical addresses, the chip carries a page descriptor cache, also known as a translation look-aside buffer (TLB). Its 32 entries can obviate full address translation more than 98% of the time. Hence, address translation degrades performance in only 2% of all cases.

The User bit and the Write bit assign varying degrees of protection to each page (Table 3). In addition, two status bits are present for the system designer to track page usage. The Accessed bit is true if a page or page directory has been accessed by the MMU; the Dirty bit is true if the page or directory has been written to.

The processor's paging mechanisms thus form a powerful base for implementing the key operating system services necessary to paged virtual memory management. Specifically, these are algorithms to allocate and replace memory page frames and to store a virtual page in secondary memory.

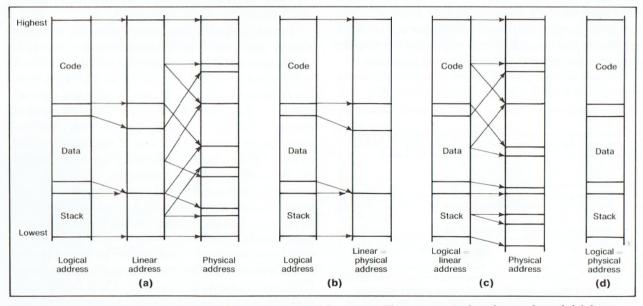

#### Four address space formats

The memory management units furnish a flexible means to fit address space architecture to different applications. Four major address architectures can be directly implemented. For example, the segmented and paged model (Fig. 5a), which unleashes the chip's full power, is the one used for the Unix System V operating system. There, each task has a code segment, data segment, and stack segment; the processor's segmentation unit furnishes the per-task segments, and the paging unit allows the working set kept in main memory to be effectively managed.

The segmented mode (Fig. 5b) is very useful when segments are not large and when compatibility with

4. For every page, the directory descriptor (a) and the table descriptor (b) each contain 12 flag bits. In addition to governing memory management and protection, flag bits can be employed by the system designer for proprietary functions. previous processors in the 8086 family is a must. When system security and reliability are important, the protection scheme established by segmentation mechanism is particularly helpful.

Some designers prefer a completely flat logical architecture in which paging is used to manage physical memory. The processor makes possible this memory arrangement in the paged linear model (Fig. 5c). Since the processor's paging mechanism is on chip, the device performs better than systems that use this model with off-chip MMUs.

Finally, the completely linear model is the design of choice in many real-time applications (Fig. 5d). It suits very compact, user-designed operating systems because niether segmentation nor paging need be employed. In this model, the program address is also the physical address.

#### **Multitasking a must**

For systems that require multitasking or even multiple environments, the processor's task state segment, or TSS, is useful. This is a repository for all task state information that allows tasks to be switched quickly with a hardware assist by storing and reloading information from old and new TSSs in a single instruction. The chip remains compatible with the 80286's task-switching mechanism. Since the TSS includes the state of the page directory base register, the user can assign a different page map for each task with a single instruction.

The chip packs the most power when the semantic control, flexible address space architecture, and multitasking assistance mechanisms are all combined. Application programs written for each of the following environments, for instance, could exist concurrently—in fact, there could be multiple instances of each environment executing concurrently. And because all semantic control bits of the processor are switched when a task is switched, a new environment can be entered with one instruction.

One environment could be the segmented and paged model, executing 32-bit code under Unix System V. Another might be the segmented and paged model, executing 16-bit 80286 object code. A third environment could apply the paged linear model to execute 32-bit code transported from linear Unix environments like Berkeley 4.2. A fourth environment might directly execute unchanged 8086 and 8088 object code using the segmented and paged model—say, programs written for the IBM PC.

To emulate the operation of the 8086 and 8088 pro-

#### 32-bit microprocessor

cessors within its protected virtual address mode environment, the processor is controlled by the Virtual Mode bit (VM bit) in the flags register. In a virtual 8086 code segment, the segment register semantics are the same as in the 8086 itself. Thus unchanged 8086 code can be executed in the processor's protected mode—even code that follows the frowned-upon practice of employing segment registers for temporary storage.

#### Just like an 8086

In the virtual 8086 mode, the processor looks just like an 8086 to the application program; the value in the segment selector register is shifted left by four bits to compute the actual segment base. As in the 8086, and in real modes of the 80286 and 80386, each segment is 64 kbytes long. And even though the processor can generate larger offsets, that memory is not accessible.

Interrupts cause an automatic switch out of the virtual 8086 mode, so that the operating system's interrupt handler can process the interrupt or hand it back to the 8086 program, if appropriate.

Each virtual 8086 code section generates linear addresses up to 1 Mbyte long. To supply separate address spaces for each of these, the operating system must create a separate page directory for each task. The paging mechanism also can be used to simulate the address wraparound at 1 Mbyte employed by the 8086. Nevertheless, the processor's protection scheme remains intact in the virtual 8086 mode because such programs always execute at the least privileged level.□

Senior engineer Rakash Agarwal is a five-year veteran of Intel. His bachelor's degree is from the University of British Columbia and his master's was awarded by the University of Toronto.

Greg Blanck is a design engineer who has worked at Intel for a year. He holds a BSEE in electrical engineering from Case Western Reserve University.

Dana Krelle was formerly assigned to the 80286 microprocessor and is a product marketing engineer for the 80386. He holds a BSEE from the University of Michigan and an MBA from the University of California at Berkeley.

5. The processor directly implements four address architectures. The segmented and paged model (a) unleashes the device's full power. The segmented model (b) is appropriate when the fields are fairly short. A linear model is possible in which paging oversees physical memory (c), and a completely flat model is the choice for real-time applications (d).

inta

# The Intel 80386—Architecture and Implementation

Khaled A. El-Ayat and Rakesh K. Agarwal Intel Corporation

he Intel 80386 represents the state of the art in high-performance, 32-bit microprocessors. It features absolute object code compatibility with previous members of the iAPX 86 family of microprocessors, including the 80286, 80186, 80188, 8086, and 8088. This protects major investments in application and operating systems software developed for the iAPX 86 family, while offering a significant enhancement in performance. The 80386's architecture and performance should allow it to be used in a wide range of demanding applications—e.g., in engineering workstations, office systems, robotic and control systems, and expert systems.

The 80386 implements a full 32-bit architecture with a 32-bit-wide internal data path including registers, ALU, and internal buses; it provides 32-bit instructions, addressing capability, and data types, and a 32-bit external bus interface. It extends the iAPX 86 family architecture with additional instructions, addressing modes, and data types. It incorporates a complete memory management/unit. The 80386 extends the 80286 segmentation model to support four-gigabyte segments and to provide a standard two-level paging mechanism for physical memory management. System designers can use segmentation or paging or both, without performance penalties, to meet their memory management requirements. The 80386 architecture is complemented by a bus interface that uses only two clocks per bus cycle; this allows efficient interfacing to high-speed as well as low-speed memory systems. At 16 MHz, the bus can sustain a 32-megabyte-per-second transfer rate. Other bus features include dynamic bus sizing to support mixed 16/32-bit port interfacing and a dynamically selectable pipelined mode to facilitate high-speed memory interleaving and allow longer access times.

The 80386 is implemented in Intel's CHMOS-III 1.5-micrometer process. Typical instruction mixes indicate an average processing rate of 4.4 clocks per instruction and an overall execution rate of three to four MIPS. To facilitate system debugging, the chip incorporates hardware debug features and selftesting.

## 80386 base architecture

Different microprocessor applications require different types of architectural support. Some applications—such as those running under Berkeley UNIX—may prefer a linear address space. Others that manage a multitude of dynamic data structures may require hardware-enforced rules to protect the visibility of the dynamically created objects. The 80386 architecture supports these diverse requirements by providing the user with several memory management and addressing models. Further, its repertoire of addressing modes, data types, instructions, and special constructs make it well suited to modern high-level languages.

The base architecture of the 80386 encompasses the register model, data types, addressing modes, and instruction set. It forms the basis for high-levellanguage compiler code generation and for assemblylanguage-level application programming. Other features of the machine useful for implementing operating systems are discussed in the section on OS architecture.

**Registers.** The 80386 possesses several on-chip register sets to support various machine features. Figure 1 shows the eight general-purpose registers available for calculations and memory addressing, the flags register, and the instruction pointer. Other registers include control registers, six segment registers used to structure the four-gigabyte address space and to facilitate system debug, and six debug registers used to control the setting of up to four code or data breakpoints.

The 32-bit general registers are named EAX, EBX, ECX, EDX, ESP, EBP, ESI, and EDI. To allow 16-bit operations and to provide compatibility with the 16-bit members of the iAPX 86 family, eight 16-bit registers are superimposed onto the low-order parts of the 32-bit registers. Similarly, there are eight 8-bit registers that are aliases for the lower and upper halves of each of the 16-bit registers. Operations on 8-bit or 16-bit registers. For example, the carry out of bit 7 during an 8-bit add is not propagated into bit 9 of the destination; instead, the carry flag (CF) of the flags register is set appropriately. This is true for all condition code settings in the flags.

**Operand addressing.** 80386 operands may reside on the chip (in registers), in main memory, or in the I/O address space. Furthermore, an operand may be implied in the instruction or specified explicitly as a part of the instruction.

Storing operands in registers generally provides the fastest method of processing data. The contents of any 80386 general register can be operated on by any arithmetic or logical operator. Alternatively, 8-, 16-, or 32-bit constants (immediates) can be embedded directly in an instruction. Sixteen- and 32-bit operations may specify 8-bit sign-extended or zero-extended immediates. Table 1 includes sample instructions employing registers and immediates as

|             | AH        | AX  | AL | EAX |

|-------------|-----------|-----|----|-----|

|             | BH        | BX  | BL | EBX |

|             | CH        | СХ  | CL | ECX |

|             | DH        | DX  | DL | EDX |

|             |           | SP  |    | ESP |

|             |           | BP  |    | EBP |

|             |           | SI  |    | ESI |

|             |           | DI  |    | EDI |

| FLAGS       | register  |     |    |     |

| Instruction | pointer I | EIP |    |     |

|             |           |     |    |     |

Figure 1. The 80386 general register set, FLAGS, and instruction pointer.

operands. In general, register-to-register operations execute in two clocks on the 80386. At a clock rate of 16 MHz, this translates to 125 nanoseconds per operation.

Most operands are stored in main memory. The 80386 has a full complement of address generation mechanisms for specifying the effective address of such operands. These mechanisms were developed in response to the storage paradigms present in highlevel languages.

In its simplest form, the effective address of a memory operand can be encoded directly in an instruction. Usually, however, a particular memory address is not known until the program is actually executing. In this case, the effective address can be obtained by summing the contents of one or two general-purpose registers and an optional immediate value or *displacement*. This register-based effective address scheme can be summarized as

[base register] + [index register] \* (scale) + [displacement].

Here the base register is any general-purpose register and the index register is any general-purpose register INTEL 80386

#### Table 1. Examples of operand addressing in the 80386. Semantics Clocks Instruction Increment contents of EAX by 1. 2 INC EAX 9 Multiply the integer in EBX by -3. IMUL EBX, -3 2 Compare contents of CX with 0 and set CMP CX, 0 condition codes. Sign extend the contents of the 16-bit register 3 MOVSX EAX, SI SI and move into EAX. 2 Assign -12445654 to the 32-bit integer at MOV DWORD PTR [56], -12445654 address 56. Jump to the address stored at entry EBX of 10 JMP jumpTable[EBX\*4] jump table. 7 Subtract from DX the 16-bit quantity at SUB DX, WORD PTR address [EBP + EDI\*2-10]. [EBP + EDI\*2-10]

Figure 2. 32-bit memory addressing modes.

Table 2. 80386 support of high-level-language memory addressing.

| Storage<br>class | Type specifier                                                 | Addressing mode                                                                  |

|------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------|

| Static           | Scalar<br>Structure<br>Array of scalars<br>Array of structures | [disp]<br>[disp]<br>[disp + index]<br>[disp + index]                             |

| Automatic        | Scalar<br>Structure<br>Array of scalars<br>Array of structures | [base + disp]<br>[base + disp]<br>[base + disp + index]<br>[base + disp + index] |

| Неар             | Scalar<br>Structure<br>Array of scalars<br>Array of structures | [base]<br>[base + disp]<br>[base + index]<br>[base + disp + scale]               |

other than ESP. The scale specification is a constant value, either 2, 4, or 8. If specified, it scales the index register by the required amount, thus simplifying indexing into arrays of multibyte elements. The displacement field is also a constant, its value ranging from  $-2^{31}$  to  $+2^{31}-1$ . Figure 2 shows all of the 80386's 32-bit memory addressing modes, and Table 2 correlates high-level-language addressing forms with those modes. (Example of memory addressing appear in Table 1.)

Data types. As shown in Figure 3, the 80386 directly supports the fundamental data types found in most high-level languages. The basic operations provided by the 80386 for each of these data types are shown in Table 3. Most of these operations execute in two clocks when register or immediate operands are used. Furthermore, because of pipelining and the two-clock memory bus, stores to memory also execute in two clocks.

Figure 3. 80386 data types.

The basic unit of storage is a *byte*; a 16-bit quantity is a *word*, and a 32-bit quantity is a *double word*, or *d-word*. Words are defined as having a length of 16 bits so that notational compatibility with the other members of the iAPX 86 processor family will be retained. In the 80386, most data types are represented in the form of bytes, words, or d-words, or combinations thereof.

Words comprise two consecutive bytes in memory, with the low-order byte at the lower-numbered address. D-words comprise four consecutive bytes in memory, with the low-order byte at the lowest address and the high-order byte at the highest address. The address of a word or d-word is the address of the low-order byte. Hence, the 80386 utilizes the little-endian storage scheme.

*Ordinal.* An ordinal is an unsigned number. If it is in the range 0 through 4,294,967,295, it corresponds to a d-word value. If it has a magnitude of less than

zero, it corresponds to a word or byte value. An example of an ordinal operation is the instruction sequence

MUL EBX,vec[EDX \*4] ;EBX := EBX \* vec[EDX] INTO ;Generate an exception if :overflow

Here, the content of EBX is multiplied by the EDXth element of the d-word-sized ordinal array vec, and the product is stored in EBX. An overflow exception is generated if the product exceeds 4,294,967,295.

Integer. An integer is a signed number in the range -2,147,483,648 through +2,147,483,647. As with ordinals, d-word, word, and byte integers are supported. Integers are represented in two's-complement

### 80386 system debug capabilities

A large portion of system development time is usually devoted to system debugging and verification. The magnitude of the problem is strongly influenced by system complexity at both the software and the hardware levels. In highly complex systems, external hardware and software debug aids alone cannot provide the level of support needed; internal CPU assistance is required.

To facilitate system development and real-time system debugging, the 80386 provides the following capabilities:

- detection of instruction breakpoints,

- detection of data reference breakpoints,

- specification of four separate breakpoint addresses,

- instruction single-stepping, and

- a one-byte trap instruction.

The 80386 has six system debug registers (see figure). The first four, DR0 to DR3, store the required breakpoint addresses. Registers DR6 and DR7 contain debug status and control information, respectively. Registers DR4 and DR5 are reserved by Intel. Breakpoint addresses must be linear addresses of instructions or data items. The control register, DR7, specifies the conditions under which a breakpoint is recognized and includes enable/disable masking fields, the breakpoint type, and the breakpoint length fields.

The enable/disable masking fields determine whether a detected breakpoint condition will be recognized by the CPU and whether an exception will be generated or simply stored in the debug status register for future examination. The breakpoint type field indicates the type of memory reference-e.g., an instruction execution, a data write reference, or a data read/write referencethat is intended to cause the system break. The breakpoint length field is used primarily for data references and selects byte, word, or double-word ranges for data item breakpoints. This field is needed because of a problem that arises in data referencing. Simply specifying the starting address of a data item is too restrictive and is insufficient for matching a breakpoint condition. The problem exists because there are three different data item lengths (8, 16, and 32); under erroneous conditions the generated address and data type length may not exactly match the specified breakpoint condition. The length field adds flexibility by selecting a range in which breakpoints can occur. Instruction breakpoints always specify a one-byte length field, since system breakpoints should uniquely specify the byte-granular starting address of intended instructions.

Let us illustrate the use of the debug capability with an example. To cause a break at a particular instruction, the user loads the starting address of that instruction into one of the breakpoint address registers, DR0 to DR3. The

|                                                              |         |         | Data | type     |        |        |

|--------------------------------------------------------------|---------|---------|------|----------|--------|--------|

| Orantian                                                     | 0-1-1   |         | DCD  | Floating |        | Bit    |

| Operation                                                    | Ordinal | Integer | BCD  | point    | String | string |

| Move<br>to/from memory,<br>convert precision                 | х       | x       | х    | x        | Х      | x      |

| Arithmetics<br>add, subtract,<br>multiply, divide,<br>negate | х       | х       | х    | x        |        |        |

| Logicals<br>AND, OR, XOR,<br>shift                           | Х       | х       |      |          |        |        |

| Compare                                                      | х       | х       | х    | x        | x      | x      |

| Transcendentals                                              |         |         |      | х        |        |        |

Table 3. Data types supported by the 80386 instruction set. (Floating point is available when numeric coprocessor is added.)

corresponding enable bit for the selected register must be set, and the type and length field must be set to instruction break (length = one byte). When the CPU is certain it is about to execute that instruction, it completes the execution of the current instruction, and a debug exception is generated. Note that if a successful branch or transfer of control precedes the intended breakpoint instruction, the break does not occur. An instruction break occurs before the instruction causing it is executed, whereas a data reference break occurs after the instruction causing it is executed.

The single-stepping-by-instruction feature forces an exception after each instruction execution. It can be used for system monitoring on an instruction-by-instruction basis. The one-byte trap instruction causes a software trap when executed and is useful for debugging exception-handling code.

#### 80386 system debug registers.

| 1                           |                             |                             |                             |        |                          | 0  |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--------|--------------------------|----|

|                             |                             |                             | Breakpoint () linear a      | ddress |                          | DR |

|                             |                             |                             | Breakpoint 1 linear a       | ddress |                          | DR |

|                             |                             |                             | Breakpoint 2 linear a       | ddress |                          | DR |

| Breakpoint 3 linear address |                             |                             |                             |        |                          | DR |

|                             |                             |                             |                             |        | Break Point<br>Status    | DR |

| Break pt.<br>length<br>type | Break pt.<br>length<br>type | Break pt.<br>length<br>type | Break pt.<br>length<br>type | Brea   | k pt. enable/<br>disable | DR |

#### INTEL 80386

notation. This allows a common set of instructions for addition and subtraction. For example,

SUB ESP, 5

subtracts five from ESP whether ESP stores an integer or an ordinal. The settings of the overflow, sign, zero, and carry flags allow a program to determine whether a signed or an unsigned overflow has occurred. However, special instructions are provided for determining overflow in multiply and divide operations involving integers, since an integer multiply has its own rules for overflow and an integer divide produces its own unique bit patterns.

**Pointers.** A pointer is a memory address. There are two types of pointers in the 80386: near pointers and far pointers. A near pointer is another term for an effective address. A far pointer has two components: a word-sized selector and a d-word-sized effective address. The selector names the logical address space in which the effective address resides. This ability to define logical address spaces gives a user greater flexibility in structuring memory. (This is discussed in greater detail below.) To retain compatibility with 16-bit members of the iAPX 86 processor family, the 80386 also supports pointers having word-sized selectors and word-sized effective addresses.

**Bit fields.** The 80386 can do fetches from, or perform stores into, contiguous bit sequences of up to 31 bits each, where such bit fields themselves reside in a bit string of up to four gigabits. Single-bit values can also be tested and modified. Furthermore, bit fields can be scanned for the first set bit in either a forward or a reverse direction. This feature can be used to implement the *set* type of Pascal. For example, if *col* is an object of the type *set of color*, then the Pascal fragment

#### while c in col do

can be translated into

BSF EAX, col ; Find first set element. Store in EAX JZ loopExit ; Exit if none left

**Floating-point operations.** By adding the 80287 floating-point coprocessor, or the higher-performance 80387, the user can extend the 80386 instruction set to support 32-bit, 64-bit, and 80-bit IEEE-standard floating-point arithmetic directly. These coprocessors provide the accuracy and performance demanded by numerically intensive applications such as robotics and graphics.

**Multiprecision operations.** The 80386 provides limited support for 64-bit operands. Integer and ordinal multiply and divide operations may have 64-bit products and dividends; the multiplier, multiplicand, divisor, quotient, and remainder are limited to d-word quantities. Multiprecision add and subtract operations can be easily synthesized with the addwith-carry (ADC) and subtract-with-borrow (SBB) operations.

Besides multiprecision arithmetic operations, the 80386 provides double-width shift instructions that accept a 64-bit input and generate a 32-bit output. These instructions can be viewed as generalizations of the normal logical shifts, except that the value shifted in is not zeroes but is specified by the contents of another 32-bit operand. Double-width shifts are especially useful for buffering intermediate data when performing operations on unaligned bit strings. A barrel shifter within the 80386 makes the execution times of these instructions independent of the size of the shift—any register-based, double-shift operation can be done in three clock periods.

Logical addresses. Thus far we have discussed memory addresses only in the context of effective addresses. We shall now investigate the logical address spaces provided by the 80386 to allow convenient memory partitioning. Each logical address space is named by means of a word-sized selector. All memory addresses have two components: the selector that names the logical address space (or segment) and an effective address (or offset) that indexes into the named logical address space. The full selector:offset form of address is the far pointer mentioned previously. The selector is not usually directly specified in an instruction's operand field; it is instead stored in a segment register.

There are six segment registers named CS, DS, ES, FS, GS, and SS, as shown in Figure 4. Segment registers are not usually encoded in instructions; the segment register to be used is instead implied in the operand type. For example, code is fetched from the logical address space named by the selector in CS, at the offset specified by the instruction pointer EIP. Similarly, the stack is located in the logical address space named by the selector in SS, with the top-of-stack at offset ESP.

For memory operands not residing in the stack, the implied segment is usually DS. If a memory operand's default segment register is not desired, it

## The 80386 physical implementation