# AMD Processor Recognition

**Application Note**

Publication # 20734 Rev: W-1 Issue Date: November 2002

#### © 2000-2002 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD Arrow logo, AMD Athlon, AMD Duron, and combinations thereof, and 3DNow! are trademarks, and AMD-K6-III, AMD-K6-2, AMD-K6, Am486, and  ${\rm Am5}_{\rm x}$ 86 are registered trademarks of Advanced Micro Devices, Inc.

MMX is a trademark of Intel Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| Introduction                                              |

|-----------------------------------------------------------|

| CPUID Instruction Overview                                |

| Testing for the CPUID Instruction                         |

| Illegal Instruction Exception Method 3                    |

| EFLAGS ID-Bit Method                                      |

| Using CPUID Functions                                     |

| Identifying the Processor Vendor                          |

| Testing For Extended Functions                            |

| Determining the Processor Signature 7                     |

| Identifying Supported Features                            |

| Determining Instruction Set Support                       |

| CPUID Test                                                |

| MMX <sup>TM</sup> Test                                    |

| SSE Test                                                  |

| Extended Functions Test                                   |

| 3DNow! <sup>TM</sup> Instruction Test                     |

| Vendor Check                                              |

| MMX Extensions Test                                       |

| AMD Processor Signature (Extended Function) 13            |

| Displaying the Processor Name                             |

| Name String Supports up to 48 Characters14                |

| Differentiation of Processors of the Same Model Number 14 |

| S3 State Considerations                                   |

| Displaying Cache Information                              |

| Determining Power Management Capabilities 17              |

| Determining Maximum Physical and Linear Address Size 17   |

| Code Samples                                              |

| Example CPUID Code                                        |

| Example Function Call                                     |

Contents

| 2 0 0                                   | on <sup>TM</sup> Processor or AMD Duron <sup>TM</sup> |

|-----------------------------------------|-------------------------------------------------------|

| K7_CPUID                                | oroutine                                              |

| Appendix A CPUID Instruction Definition | 31                                                    |

| CPUID Instruction                       | 31                                                    |

| Standard Functions                      | 32                                                    |

|                                         | dard Function Input Value and ng32                    |

| · ·                                     | nature and Standard Feature                           |

| Extended Functions                      | 37                                                    |

|                                         | rgest Extended Function Input                         |

|                                         | ID Processor Signature and                            |

|                                         | 00_0003h, and 8000_0004h—<br>43                       |

|                                         | TLB/Cache Information for aron Processors 43          |

|                                         | Cache Information for AMD-K5 ors                      |

| <del>-</del>                            | TLB/L2 Cache Information for aron Processors          |

|                                         | Cache Information for the                             |

| Associativity Field Definit             | tions                                                 |

|                                         | dvanced Power Management49                            |

|                                         | hysical Address and Linear                            |

*iv* Contents

| Appendix B | Register Values Returned by the AMD Family Processors                               | 51 |

|------------|-------------------------------------------------------------------------------------|----|

|            | AMD Athlon Processor and AMD Duron Processor Values                                 | 52 |

|            | AMD-K6 <sup>®</sup> Processor Values                                                | 60 |

|            | Am486 <sup>®</sup> , Am5 <sub>x</sub> 86 <sup>®</sup> , and AMD-K5 Processor Values | 62 |

Contents

20734W-1 – November 2002

*vi* Contents

## **List of Figures**

| Figure 1. | Contents of EAX Register Returned by Function 1 | . 8 |

|-----------|-------------------------------------------------|-----|

| Figure 2. | Contents of EAX Register Returned by Extended   |     |

|           | Function 8000_0001h                             | 13  |

List of Figures vii

20734W-1 – November 2002

viii List of Figures

## **List of Tables**

| Table 1.  | Summary of CPUID Functions in AMD Processors 5                                                                   |

|-----------|------------------------------------------------------------------------------------------------------------------|

| Table 2.  | Summary of CPUID Functions in AMD Athlon <sup>TM</sup> and AMD Duron <sup>TM</sup> Processors                    |

| Table 3.  | Summary of Processor Signatures for AMD Processors 9                                                             |

| Table 4.  | Summary of Standard and Extended Feature Bits 10                                                                 |

| Table 5.  | Processor Name Strings for AMD Athlon and AMD Duron Family of Processors Through Model 4 14                      |

| Table 6.  | Recommended Name String by Platform Segment for AMD Athlon and AMD Duron Family of Processors Models 6 and Above |

| Table 7.  | Model Number Mappings for AMD Athlon Family of Processors                                                        |

| Table 8.  | Standard Feature Flag Descriptions for AMD-K6 <sup>®</sup> -2 and AMD-K6 <sup>®</sup> -III Processors            |

| Table 9.  | Standard Feature Flag Descriptions for AMD Athlon Processors                                                     |

| Table 10. | Standard Feature Flag Descriptions for AMD Duron Processors                                                      |

| Table 11. | Extended Feature Flag Descriptions for AMD-K6-2 and AMD-K6-III Processors                                        |

| Table 12. | Extended Feature Flag Descriptions for AMD Athlon Processors                                                     |

| Table 13. | Extended Feature Flag Descriptions for AMD Duron Processors                                                      |

| Table 14. | EAX Format Returned by Function 8000_0005h 44                                                                    |

| Table 15. | EBX Format Returned by Function 8000_0005h 44                                                                    |

| Table 16. | ECX Format Returned by Function 8000_0005h 44                                                                    |

| Table 17. | EDX Format Returned by Function 8000_0005h 44                                                                    |

| Table 18. | EBX Format Returned by Function 8000_0005h 45                                                                    |

| Table 19. | ECX Format Returned by Function 8000_0005h 45                                                                    |

| Table 20. | EDX Format Returned by Function 8000_0005h 45                                                                    |

List of Tables ix

| Table 21. | EAX Format Returned by Function 8000_0006h 46                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 22. | EBX Format Returned by Function 8000_0006h 46                                                                                                            |

| Table 23. | ECX Format Returned by Function 8000_0006h 47                                                                                                            |

| Table 24. | ECX Format Returned by Function 8000_0006h for the AMD-K6®-III Processor                                                                                 |

| Table 25. | Associativity Values For L2 Caches and TLBs 48                                                                                                           |

| Table 26. | Values Returned by AMD Athlon <sup>TM</sup> and AMD Duron <sup>TM</sup> Processors Models 6, 7, and 8                                                    |

| Table 27. | Values Returned by Mobile AMD Athlon <sup>TM</sup> Processors<br>Models 6, 7, and 8, and Mobile AMD Duron <sup>TM</sup><br>Processors Models 3, 6, and 7 |

| Table 28. | Values Returned by AMD Athlon <sup>TM</sup> Processors Models 1, 2, and 4, and AMD Duron <sup>TM</sup> Processors Model 3 58                             |

| Table 29. | Values Returned by AMD-K6® Processors 60                                                                                                                 |

| Table 30. | Values Returned by Am486 <sup>®</sup> , Am5 <sub>x</sub> 86 <sup>®</sup> , and                                                                           |

|           | AMD-K5 Processors                                                                                                                                        |

x List of Tables

## **Revision History**

| Date          | Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| November 2002 | W-1 | Revised Table 12 in Appendix A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| November 2002 | W   | Revised Table 7: Added additional model numbers — 2600+, a 2700+, and a 2800+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| August 2002   | ٧   | Added 2400+ and 2600+ models to table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| August 2002   | U   | Added AMD Athlon™ processor model 8 information to the following:  Table 2, "Summary of CPUID Functions in AMD Athlon™ and AMD Duron™ Processors"  Table 3, "Summary of Processor Signatures for AMD Processors," on page 9  Table 6, "Recommended Name String by Platform Segment for AMD Athlon™ and AMD Duron™ Family of Processors Models 6 and Above," on page 15  Table 7, "Model Number Mappings for AMD Athlon™ Family of Processors," on page 16  Table 9, "Standard Feature Flag Descriptions for the AMD Athlon™ Processors"  Table 12, "Extended Feature Flag Descriptions for AMD Athlon™ Processors"  Table 26, "Values Returned By the AMD Athlon™ and AMD Duron™ Processors models 6 and 7, and 8" |  |  |  |  |

Revision History xi

| Date         | Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| January 2002 | T   | Added the following:  "Name String Supports up to 48 Characters" on page 14  "Differentiation of Processors of the Same Model Number" on page 14  "S3 State Considerations" on page 14  "Recommended Name String" on page 14  Table 5, "Processor Name Strings for AMD Athlon™ and AMD Duron™ Family of Processors Through Model 4," on page 14  Revised the following:  Table 2, "Summary of CPUID Functions in AMD Athlon™ and AMD Duron™ Processors," on page 6  "Testing For Extended Functions" on page 7  Table 3, "Summary of Processor Signatures for AMD Processors," on page 8  Table 4, "Summary of Standard and Extended Feature Bits," on page 10  Table 6, "Recommended Name String by Platform Segment for AMD Athlon™ and AMD Duron™ Family of Processors Models 6 and Above," on page 16  Table 7, "Model Number Mappings for AMD Athlon™ Family of Processors," on page 35  Table 10, "Standard Feature Flag Descriptions for the AMD Duron™ Processors," on page 36  Table 12, "Extended Feature Flag Descriptions for AMD Athlon™ Processors," on page 39  Table 13, "Extended Feature Flag Descriptions for AMD Duron™ Processors," on page 41  Table 26, "Values Returned By the AMD Athlon™ and AMD Duron™ Processors Models 6 and 7," on page 52  Table 27, "Values Returned by the Mobile AMD Athlon™ Processors Models 6, 7, and 8, and |  |  |  |  |

| July 2001    | S   | the Mobile AMD Duron™ Processors Models 3, 6, and 7," on page 55  Added information about the mobile AMD Athlon™ 4 processor, the AMD Athlon™ MP processor, and the mobile AMD Duron™ processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| June 2000    | R   | Added information about the AMD Duron <sup>™</sup> processor throughout the document.  Revised "CPUID Instruction Overview" on page 3.  Added "The AMD Duron <sup>™</sup> Processor" on page 2.  Added Table 5, "Processor Name Strings for the AMD Duron <sup>™</sup> Processor," on page 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

xii Revision History

| Date                                                                                                                     | Rev | Description                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                          |     | Added information about the AMD Athlon™ processor Model 4 throughout the document.                                                                                                                                                                                   |

|                                                                                                                          |     | Revised "CPUID Instruction Overview" on page 3.                                                                                                                                                                                                                      |

|                                                                                                                          |     | Revised Table 5, "Processor Name String," on page 15.                                                                                                                                                                                                                |

|                                                                                                                          |     | Added code sample to "Code Samples" on page 17.                                                                                                                                                                                                                      |

|                                                                                                                          |     | Added "Displaying the AMD Athlon™ or AMD Duron™ Processor Name String" on page 25 and "DisplayK7NameString Subroutine" on page 26.                                                                                                                                   |

|                                                                                                                          |     | Revised information about bit 15 in Table 4, "Summary of Standard and Extended Feature Bits," on page 11.                                                                                                                                                            |

|                                                                                                                          |     | Revised name string for AMD Athlon™ processor Model 1 in Table 5, "Processor Name String," on page 15.                                                                                                                                                               |

| June 2000                                                                                                                | Q   | Made Table 6, "Standard Feature Flag Descriptions for the AMD-K6®-2 and AMD-K6-III Processors," on page 32 is specific to these processors.                                                                                                                          |

|                                                                                                                          |     | Added Table 6, "Standard Feature Flag Descriptions for the AMD Athlon™ Processors," on page 31, which is specific to these processors.                                                                                                                               |

|                                                                                                                          |     | Clarified instruction family and generation being derived from function 1 and function 8000_0001 respectively.                                                                                                                                                       |

|                                                                                                                          |     | Made Table 9, "Extended Feature Flag Descriptions for the AMD-K6®-2 and AMD-K6-III Processors," on page 36 is specific to these processors.                                                                                                                          |

|                                                                                                                          |     | Added Table 8, "Extended Feature Flag Descriptions for the AMD Athlon™ Processors," on page 34, which is specific to these processors.                                                                                                                               |

|                                                                                                                          |     | Revised Table 21, "Values Returned By the AMD Athlon™ Processor," on page 42.                                                                                                                                                                                        |

| Dec 1999                                                                                                                 | Р   | Added the AMD Athlon processor Model 2 information throughout document. Model 1 refers to the AMD Athlon processor manufactured with 0.25-micron process technology and Model 2 refers to the AMD Athlon processor manufactured with 0.18-micron process technology. |

| Nov 1999                                                                                                                 | 0   | Clarified usage of "Code Samples" on page 17.                                                                                                                                                                                                                        |

| 1000 1999                                                                                                                |     | Added "Example Function Call" on page 25.                                                                                                                                                                                                                            |

| August 1999                                                                                                              | N   | Merged standard and extended feature bits into one table. See Table 4, "Summary of Standard and Extended Feature Bits," on page 11.                                                                                                                                  |

|                                                                                                                          |     | Revised Table 21, "Values Returned By the AMD Athlon™ Processor," on page 42.                                                                                                                                                                                        |

|                                                                                                                          |     | Added the AMD Athlon™ processor information throughout document.                                                                                                                                                                                                     |

|                                                                                                                          |     | Added url www.amd.com/products/cpg/bin, where codes samples and utilities are available.                                                                                                                                                                             |

| August 1999                                                                                                              | М   | Revised "Testing for the CPUID Instruction" on page 4.                                                                                                                                                                                                               |

|                                                                                                                          | 101 | Revised "Determining Instruction Set Support" on page 13.                                                                                                                                                                                                            |

|                                                                                                                          |     | Revised Tables 12 through 22 to cross-reference new section—"Associativity Field Definitions" on page 45.                                                                                                                                                            |

| May 1999  L In Table 11 on page 18, changed function 8000_0001h EDX entries for Models 6 and 7 0080_01BFh to 0080_05BFh. |     |                                                                                                                                                                                                                                                                      |

Revision History xiii

| Date       | Rev | Description                                                                                                                                                   |  |  |  |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| May 1999   | L   | Added note about the name string for the AMD-K6-2 processor to Table 11 on page 18.                                                                           |  |  |  |

|            |     | Added L2 cache information to Table 1 on page 4.                                                                                                              |  |  |  |

|            |     | Added Function 8000_0006h to "Displaying Cache Information" on page 10.                                                                                       |  |  |  |

| Feb 1999   | K   | Added Function 8000_0006h — L2 Cache Information and Table 10, "ECX Format Returned by Function 8000_0006h," on page 17.                                      |  |  |  |

|            |     | Added AMD-K6-III processor Model 9 values and three notes to Table 11 on page 18.                                                                             |  |  |  |

|            |     | In "Standard Functions" on page 12, clarified AMD's vendor identification string stored in registers EBX, EDX, and ECX.                                       |  |  |  |

| Nov 1998   | J   | In Table 11, "Values Returned By AMD-K6® Processors," on page 18, changed function 8000_0001h, EDX value for the AMD-K6 processor Model 7 and deleted note 2. |  |  |  |

| May 1998   |     | Revised "Functions 8000_0002h, 8000_0003h, and 8000_0004h — Processor Name String" on page 16.                                                                |  |  |  |

| IVIAY 1998 | 1   | Added return values for AMD-K6 processor Model 9 to Table 10 on page 18. Divided Appendix B table into two separate tables.                                   |  |  |  |

| Jan 1998   | Н   | Added revised bit 31 description and alternate test for AMD-K6-2 to "Identifying Supported Features" on page 6.                                               |  |  |  |

|            |     | Changed part names for AMD-K6 processor Models 8 and 9 in Table 2 on page 5.                                                                                  |  |  |  |

| Dec 1997   | G   | Added 3DNow!™ instructions feature (bit 31) to Table 4 on page 8 and Table 6 on page 15.                                                                      |  |  |  |

|            |     | Added AMD-K6®-2 processor return values to Table 12 on page 21.                                                                                               |  |  |  |

| Sept 1997  | F   | Moved SYSCALL/SYSRET instruction feature bit (in extended feature function 8000_0001h) from bit 10 to bit 11. See Table 6 on page 15 and Table 12 on page 21. |  |  |  |

| Sept 1997  | F   | Added bit 31 to the extended feature function 8000_0001h for a new feature. See Table 4 on page 8 and Table 6 on page 15.                                     |  |  |  |

| Sept 1997  | F   | Added support for AMD-K6® processor Models 7, 8, and 9 to Table 1 on page 4 and Table 2 on page 5.                                                            |  |  |  |

| Sept 1997  | F   | Added return values for AMD-K6 processor Model 7 to Table 12 on page 21.                                                                                      |  |  |  |

**xiv** Revision History

# Application Note

# **AMD Processor Recognition**

## Introduction

Due to the increasing number of choices available in the x86 processor marketplace, the need for a simple way for hardware and software to identify the type of processor and its feature set has become critical. The CPUID instruction was added to the x86 instruction set for this purpose. This document contains information on how to use the CPUID instruction to identify AMD processors and their features.

After detecting the processor and its capabilities, software can be tuned to the system for maximum performance and benefit to users. For example, software can roughly determine the performance level of a particular processor by detecting the type or speed of the processor. If the performance level is high enough, the software can enable additional capabilities or more advanced algorithms. Another example involves testing for the presence of 3DNow!<sup>TM</sup> instruction, SSE, or MMX<sup>TM</sup> instruction support on the processor. (The combined support of 3DNow! instruction extensions SSE is and 3DNow! Professional technology.) If the software finds these features present when it checks the feature bits, it can utilize these more powerful extensions for dramatically better performance on new multimedia software.

Introduction 1

#### **CPUID Instruction Overview**

Software operating at any privilege level can execute the CPUID instruction to identify the processor and its feature set. In addition, the CPUID instruction implements multiple functions, each providing different information about the processor, including the vendor, model number, revision (stepping), features, cache organization, and processor name. The multiple-function approach allows the CPUID instruction to return a complete picture about the type of processor and its capabilities—more detailed information than could be returned by a single function. In addition to gathering all the information by calling multiple functions, the CPUID instruction provides the flexibility of making only one call to obtain the specific data requested.

The functions are divided into two types: standard functions and extended functions. Standard functions provide a simple method for software to access information common to all x86 processors. Extended functions provide information on extensions specific to a vendor's processor (for example, AMD family processors).

The flexibility of the CPUID instruction allows for the addition of new CPUID functions in future generations of processors. Appendix A, "CPUID Instruction Definition," contains a detailed description of the CPUID instruction.

## **Testing for the CPUID Instruction**

Beginning with the Am486<sup>®</sup> DX4 processor, all AMD family processors support the CPUID instruction. To use the CPUID instruction, software must first determine if the processor supports the CPUID instruction. CPUID support is determined in one of the following ways:

- Execute the CPUID instruction and check whether an illegal instruction exception occurs. If an exception occurs, the processor does not have CPUID support.

- Check if the ID bit (bit 21) of the EFLAGS register is writable. If the bit is writable (that is, it can be modified), the CPUID instruction is supported.

The Operating System (OS) environment determines which approach is more appropriate. These methods are described in the following sections.

## **Illegal Instruction Exception Method**

This method requires a way for a user program to detect and handle illegal instruction exceptions. Where such capabilities are present, this method represents a reliable way of detecting support for the CPUID instruction. The CPUID sample code starting on page 18 uses this method.

#### **EFLAGS ID-Bit Method**

This method retrieves the contents of EFLAGS using the PUSHFD instruction, toggles the ID bit, and uses the POPFD instruction to write the modified value of the ID bit into the EFLAGS register. It then retrieves the contents of EFLAGS using a second PUSHFD instruction and checks whether the value of the ID bit differs from the original value. If the value has changed, the CPUID instruction is available for identifying the processor and its features. The following code sample demonstrates the way a program uses the PUSHFD and POPFD instructions to test the ID bit.

```

; Save EFLAGS to stack

pushfd

gog

eax

: Store EFLAGS in EAX

; Save in EBX for testing later

ebx, eax

mov

eax, 00200000h

; Switch bit 21

xor

push

eax

: Copy changed value to stack

popfd

: Save changed EAX to EFLAGS

pushfd

; Push EFLAGS to top of stack

: Store EFLAGS in EAX

рор

eax

; See if bit 21 has changed

cmp

eax, ebx

jΖ

NO CPUID

; If no change, no CPUID

```

A potential problem with this method is that an interrupt or a trap (such as a debug trap) can occur between the POPFD and the following PUSHFD, and that the interrupt or trap handler code destroys the value of the ID bit. Where possible, the preceding code should be preceded by a CLI instruction and followed by an STI instruction, which ensures that no interrupts occur between the POPFD and the PUSHFD. However, traps can still occur, even if the code is preceded by a CLI instruction and followed by an STI instruction.

## **Using CPUID Functions**

When software uses the CPUID instruction to identify a processor, it is important that it uses the instruction appropriately. The instruction has been defined to make it easy to identify the type and features of x86 processors manufactured by many different vendors.

The standard functions (EAX=0 and EAX=1) are the same for all processors. Having standard functions simplifies the software task of testing for and implementing features common to x86 processors. Software can test for these features and, as new x86 processors are released, benefit from these capabilities immediately.

Extended functions are specific to a vendor's processor. These functions provide additional information about AMD processors that software can use to identify enhanced features and functions. To test for extended functions, software checks for a value of at least 8000\_0001h in the EAX register returned by function 8000\_0000h.

Within the AMD family of processors, different members can execute a different number of functions. Table 1 on page 5 and

Table 2 on page 6 summarize the CPUID functions currently implemented on AMD processors.

**Table 1. Summary of CPUID Functions in AMD Processors**

| Standard<br>Function | Extended<br>Function | Description                                                  | AMD-K5<br>Processor<br>(Model 0),<br>Am486 <sup>®</sup> DX4<br>and Am5 <sub>x</sub> 86 <sup>®</sup><br>Processors | AMD-K5<br>Processor<br>(Models 1,<br>2, and 3) | AMD-K6 <sup>®</sup> Processor (Models 6, 7) AMD-K6-2 Processor (Model 8) | AMD-K6-III<br>Processor<br>(Model 9) |

|----------------------|----------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------|

| 0                    | -                    | Vendor String and Largest<br>Standard Function Value         | Х                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| 1                    | _                    | Processor Signature and<br>Standard Feature Bits             | Х                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0000h           | Largest Extended<br>Function Value                           | _                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0001h           | Extended Processor<br>Signature and Extended<br>Feature Bits | _                                                                                                                 | Х                                              | X                                                                        | Х                                    |

| _                    | 8000_0002h           | Processor Name                                               | _                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0003h           | Processor Name                                               | _                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0004h           | Processor Name                                               | _                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0005h           | L1 TLB*/Cache<br>Information                                 | _                                                                                                                 | Х                                              | Х                                                                        | Х                                    |

| _                    | 8000_0006h           | L2 TLB/Cache<br>Information                                  | -                                                                                                                 | _                                              | _                                                                        | Х                                    |

| _                    | 8000_0007h           | Advanced Power<br>Management Feature<br>Flags                | _                                                                                                                 | -                                              | _                                                                        | -                                    |

| - Notes:             | 8000_0008h           | Physical Address and<br>Linear Address Size                  | _                                                                                                                 | -                                              | -                                                                        | -                                    |

#### Notes:

Future versions of these processors may implement additional functions.

Appendix A, "CPUID Instruction Definition," contains detailed descriptions of the functions.

Using CPUID Functions 5

<sup>\*</sup> TLB = Translation Lookaside Buffer.

Table 2. Summary of CPUID Functions in AMD Athlon™ and AMD Duron™ Processors

| Standard<br>Function | Extended<br>Function | Description                                                  | AMD Athlon™<br>Processor<br>Models 1, 2,<br>and 4 | AMD Duron™<br>Processor<br>Model 3 | AMD Athlon<br>and<br>AMD Duron<br>Processors<br>Model 6 <sup>2</sup> | AMD Duron<br>Processors<br>Model 7 <sup>3</sup> | AMD Athlon<br>Processors<br>Model 8 <sup>4</sup> |

|----------------------|----------------------|--------------------------------------------------------------|---------------------------------------------------|------------------------------------|----------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------|

| 0                    | _                    | Vendor String and<br>Largest Standard<br>Function Value      | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| 1                    | _                    | Processor Signature<br>and Standard Feature<br>Bits          | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0000h           | Largest Extended<br>Function Value                           | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0001h           | Extended Processor<br>Signature and<br>Extended Feature Bits | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0002h           | Processor Name                                               | X                                                 | X                                  | X                                                                    | X                                               | Х                                                |

| _                    | 8000_0003h           | Processor Name                                               | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0004h           | Processor Name                                               | Х                                                 | X                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0005h           | L1 TLB <sup>1</sup> /Cache<br>Information                    | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| _                    | 8000_0006h           | L2 TLB/Cache<br>Information                                  | Х                                                 | Х                                  | Х                                                                    | Х                                               | Х                                                |

| -                    | 8000_0007h           | Advanced Power<br>Management Feature<br>Flags                | _                                                 | -                                  | Х                                                                    | Х                                               | Х                                                |

| - Notes              | 8000_0008h           | Physical Address and<br>Linear Address Size                  | -                                                 | _                                  | X                                                                    | X                                               | Х                                                |

#### Notes:

Future versions of these processors may implement additional functions.

Appendix A, "CPUID Instruction Definition," contains detailed descriptions of the functions.

- 1. TLB = Translation Lookaside Buffer.

- 2. The AMD Athlon™ processor model 6 includes the AMD Athlon MP processor, the AMD Athlon XP processor, and the mobile AMD Athlon 4 processor. The AMD Duron™ processor model 6 includes the AMD Duron processor and the mobile AMD Duron processor.

- 3. The AMD Duron processor model 7 includes both the AMD Duron processor and the mobile AMD Duron processor.

- 4. The AMD Athlon processor model 8 includes the AMD Athlon MP processor, the AMD Athlon XP processor, and the mobile AMD Athlon XP processor.

## **Identifying the Processor Vendor**

Software must execute the standard function EAX=0. The CPUID instruction returns a 12-character string that identifies the vendor of the processor. The instruction also returns the largest standard function input value defined for the CPUID instruction on the processor.

For AMD processors, function 0 returns a vendor string of "AuthenticAMD". This string informs the software to follow AMD's definition for subsequent CPUID functions and the registers returned for those functions.

Once the software identifies the vendor of the processor, it knows the definition for all the functions supplied by the CPUID instruction. By using these functions, the software obtains the processor information needed to tune its functionality to the capabilities of the processor.

## **Testing For Extended Functions**

Software must test for extended functions with function 8000\_0000h. The EAX register returns the largest extended function input value defined for the CPUID instruction on the processor. If this value is at least 8000\_0001h, extended functions are supported.

## **Determining the Processor Signature**

Standard function 1 (EAX=1) of the CPUID instruction returns the standard processor signature and feature bits. The standard processor signature is returned in the EAX register and provides information regarding the specific revision (stepping) and model of the processor and the instruction family level supported by the processor. The revision level can be used to determine if the processor supports specific features. However, it is not recommended that the revision level be used in this manner unless this information is not available through the standard or extended feature bits.

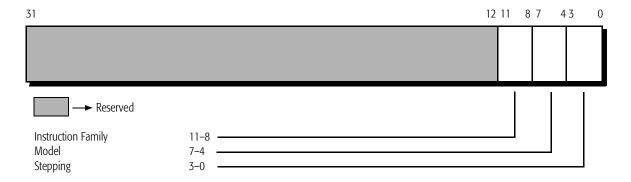

All AMD-K6® processor models belong to instruction family 5 (as returned in EAX by function 1). All AMD Athlon<sup>TM</sup> processor models and the AMD Duron<sup>TM</sup> processor belong to instruction family 6. Figure 1 shows the contents of the EAX register obtained by function 1. Table 3 on page 9 summarizes the specific processor signature values returned for AMD processors.

Figure 1. Contents of EAX Register Returned by Function 1

**Table 3. Summary of Processor Signatures for AMD Processors**

| Processor                                                          | Instruction<br>Family [11:8] | Model<br>[7:4]    | Stepping ID <sup>2</sup> [3:0] |

|--------------------------------------------------------------------|------------------------------|-------------------|--------------------------------|

| Am486 <sup>®</sup> and Am5 <sub>x</sub> 86 <sup>®</sup> Processors | 0100b (4h)                   | yyyy <sup>1</sup> | xxxx                           |

| AMD-K5 Model 0                                                     | 0101b (5h)                   | 0000b (0h)        | XXXX                           |

| AMD-K5 Model 1                                                     | 0101b (5h)                   | 0001b (1h)        | XXXX                           |

| AMD-K5 Model 2                                                     | 0101b (5h)                   | 0010b (2h)        | XXXX                           |

| AMD-K5 Model 3                                                     | 0101b (5h)                   | 0011b (3h)        | XXXX                           |

| AMD-K6 <sup>®</sup> Model 6                                        | 0101b (5h)                   | 0110b (6h)        | XXXX                           |

| AMD-K6 Model 7                                                     | 0101b (5h)                   | 0111b (7h)        | XXXX                           |

| AMD-K6 <sup>®</sup> -2 Model 8                                     | 0101b (5h)                   | 1000b (8h)        | XXXX                           |

| AMD-K6 <sup>®</sup> -III Model 9                                   | 0101b (5h)                   | 1001b (9h)        | xxxx                           |

| AMD Athlon™ Model 1                                                | 0110b (6h)                   | 0001b (1h)        | XXXX                           |

| AMD Athlon Model 2                                                 | 0110b (6h)                   | 0010b (2h)        | XXXX                           |

| AMD Duron™ Model 3                                                 | 0110b (6h)                   | 0011b (3h)        | xxxxb                          |

| AMD Athlon Model 4                                                 | 0110b (6h)                   | 0100b (4h)        | xxxxb                          |

| AMD Athlon MP Model 6                                              | 0110b (6h)                   | 0110b (6h)        | xxxxb                          |

| AMD Athlon XP Model 6                                              | 0110b (6h)                   | 0110b (6h)        | xxxxb                          |

| Mobile AMD Athlon 4 Model 6                                        | 0110b (6h)                   | 0110b (6h)        | xxxxb                          |

| AMD Duron Model 6                                                  | 0110b (6h)                   | 0110b (6h)        | xxxxb                          |

| Mobile AMD Duron Model 6                                           | 0110b (6h)                   | 0110b (6h)        | xxxxb                          |

| AMD Duron Model 7                                                  | 0110b (6h)                   | 0111b (7h)        | xxxxb                          |

| Mobile AMD Duron Model 7                                           | 0110b (6h)                   | 0111b (7h)        | xxxxb                          |

| AMD Athlon XP Model 8                                              | 0110b (6h)                   | 1000b (8h)        | xxxxb                          |

| AMD Athlon MP Model 8                                              | 0110b (6h)                   | 1000b (8h)        | xxxxb                          |

| Mobile AMD Athlon XP Model 8                                       | 0110b (6h)                   | 1000b (8h)        | xxxxb                          |

#### Notes:

<sup>1.</sup> Contact your AMD representative for model identifier information.

<sup>2.</sup> Stepping ID may change. Consult the appropriate processor Revision Guide, or contact your AMD representative for the latest stepping information. AMD Athlon™ processors of the same model numbers share the same Revision Guide. AMD Duron™ processors of the same model number share the same Revision Guide.

## **Identifying Supported Features**

The feature bits are returned in the EDX register for two CPUID functions: standard function 1 and extended function 8000\_0001h. Each bit corresponds to a specific feature and indicates if that feature is present on the processor. Table 4 summarizes the standard and extended feature bits.

**Table 4. Summary of Standard and Extended Feature Bits**

| Bit <sup>1</sup> | Feature                                                                        | Description                                                                                                          | Standard <sup>2</sup> | Extended <sup>2</sup> |

|------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| 0                | Floating-Point Unit                                                            | A floating-point unit is available.                                                                                  | 1                     | 1                     |

| 1                | Virtual Mode Extensions                                                        | Virtual mode extensions are available.                                                                               | 1                     | 1                     |

| 2                | Debugging Extensions                                                           | I/O breakpoint debug extensions are supported.                                                                       | 1                     | 1                     |

| 3                | PSE (Page Size Extensions)                                                     | Four-Mbyte pages are supported.                                                                                      | 1                     | 1                     |

| 4                | Time Stamp Counter<br>(with RDTSC and CR4 disable bit)                         | A time stamp counter is available in the processor, and the RDTSC instruction is supported.                          | 1                     | 1                     |

| 5                | K86 Family of Processors<br>Model-Specific Registers (with<br>RDMSR and WRMSR) | The K86 model-specific registers are available in the processor, and the RDMSR and WRMSR instructions are supported. | 1                     | 1                     |

| 6                | PAE (Page Address Extensions)                                                  | Page address extensions are supported using an 8-byte directory entry.                                               | 1                     | 1                     |

| 7                | MCE (Machine Check Exception)                                                  | The machine check exception is supported.                                                                            | 1                     | 1                     |

| 8                | CMPXCHG8B Instruction                                                          | The CMPXCHG8B instruction is supported.                                                                              | 1                     | 1                     |

| 9                | APIC                                                                           | A local APIC unit is available.                                                                                      | 1                     | 1                     |

| 11               | SYSENTER/SYSEXIT Instructions                                                  | The SYSENTER and SYSEXIT instructions are supported.                                                                 | 1                     | 0                     |

| ''               | SYSCALL and SYSRET Instructions                                                | The SYSCALL and SYSRET instructions and associated extensions are supported.                                         | 0                     | 1                     |

| 12               | MTRR (Memory Type Range<br>Registers)                                          | Memory type range registers are available.                                                                           | 1                     | 1                     |

| 13               | Global Paging Extension                                                        | Global paging extensions are available.                                                                              | 1                     | 1                     |

| 14               | MCA (Machine Check Architecture)                                               | Machine check architecture is supported                                                                              | 1                     | 1                     |

| 15               | Conditional Move Instructions                                                  | The conditional move instructions, CMOV and FCMOV, are supported.  The FCOMI instruction is also supported.          | 1                     | 1                     |

| 16               | PAT (Page Attribute Table)                                                     | The Page attribute tables are supported.                                                                             | 1                     | 1                     |

| Note:            | I.                                                                             | 1                                                                                                                    |                       | ı                     |

- 1. Appendix A, "CPUID Instruction Definition," contains details on bit locations and values.

- 2. Bit definitions are as follows: 0 = No Support, 1 = Support.

| Bit <sup>1</sup> | Feature                                  | Description                                                                             | Standard <sup>2</sup> | Extended <sup>2</sup> |

|------------------|------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------|-----------------------|

| 17               | PSE-36 (Page Size Extension)             | Page size extensions for 36-bit addresses are supported using a 4-byte directory entry. | 1                     | 1                     |

| 19               | Multiprocessing Capable                  | Processor capable of operating in multiprocessing configuration.                        | 0                     | 1                     |

| 22               | AMD Multimedia Instruction<br>Extensions | AMD additions to the original MMX <sup>™</sup> instruction set are supported.           | 0                     | 1                     |

| 23               | MMX Instructions                         | The MMX instruction set is supported.                                                   | 1                     | 1                     |

| 24               | FXSAVE/FXRSTOR Instructions              | Fast floating-point save and restore is supported.                                      | 1                     | 1                     |

| 25               | Streaming SIMD Extensions (SSE)          | Streaming SIMD instruction set extensions are supported.                                | 1                     | 0                     |

| 30               | 3DNow!™ Instruction Extensions           | Extensions to the 3DNow! instructions set are supported.                                | 0                     | 1                     |

| 31               | 3DNow! Instructions                      | 3DNow! instructions are supported.                                                      | 0                     | 1                     |

**Table 4. Summary of Standard and Extended Feature Bits (continued)**

#### Note:

- 1. Appendix A, "CPUID Instruction Definition," contains details on bit locations and values.

- 2. Bit definitions are as follows: 0 = No Support, 1 = Support.

Before using any of the enhanced features added to the latest generation of processors, software should test each feature bit returned by functions 1 and 8000\_0001h to identify the capabilities available on the processor. For example, software must test feature bit 23 to determine if the processor executes the MMX technology instructions. Attempting to execute an unavailable feature can cause errors and exceptions.

Bit 31, as returned by extended function 8000\_0001h, designates the presence of 3DNow! technology. Other processor vendors have adopted this technology, so bit 31 is now considered an open standard. Appendix A, "CPUID Instruction Definition," and Appendix B, "Register Values Returned by the AMD Family Processors," contain details on bit locations and values.

## **Determining Instruction Set Support**

It is preferable to use CPUID feature flags as much as possible, rather than deriving capabilities from vendor specifiers combined with CPUID model numbers.

To simplify the detection of the new instructions supported in different models of AMD Athlon and AMD Duron family of

processors, including the original 3DNow! and MMX instructions, Enhanced 3DNow!, and 3DNow! Professional (combining 3DNow! and SSE support), use the following algorithm.

#### **CPUID Test**

1. Establish that the processor has support for CPUID. See "Testing for the CPUID Instruction" on page 3.

#### Standard Function Test

- 2. Execute CPUID function 0, which returns the processor vendor string and the highest standard function supported. Save the vendor string for a later comparison. (See step 9.)

- 3. If step 2 indicates that the highest standard function is at least 1, execute CPUID function 1, which returns the standard feature flags in the EDX register.

#### **MMX™** Test

4. If bit 23 of the standard feature flags is set to "1", MMX technology is supported. MMX instruction support is the basic minimum processor feature required to support other instruction extensions.

#### **SSE Test**

5. If bit 25 of the standard feature flags is set to "1" on an AMD Athlon or AMD Duron model 6 or greater, SSE instructions are supported. Optionally, if bit 25 of the standard feature flags is set on any previous AMD processor, it has streaming SIMD extensions (SSE) capabilities. Further qualification of SSE is done by checking for OS support. SSE support might be present in the processor but is not usable due to a lack of OS support for the additional architected registers.

## **Extended Functions Test**

- 6. Execute CPUID extended function 8000\_0000h. This function returns the highest extended function supported in EAX. If EAX=0, there is no support for extended functions.

- 7. If the highest extended function supported is at least 8000\_0001h, execute CPUID function 8000\_0001h. This function returns the extended feature flags in EDX.

#### 3DNow!™ Instruction Test

8. If bit 31 of the extended feature flags is set to "1", the 3DNow! instructions are supported.

#### **Vendor Check**

9. If the previously saved vendor string (see step 2) contains "AuthenticAMD", continue on to the next step.

**3DNow!™ Extensions Test**

10. If bit 30 of the extended feature flags is set to "1", the additions to the 3DNow! instruction set are supported.

MMX™ Extensions Test 11. If bit 22 of the extended feature flags is set to "1", the new multimedia enhancement instructions that augment the MMX instruction set are supported.

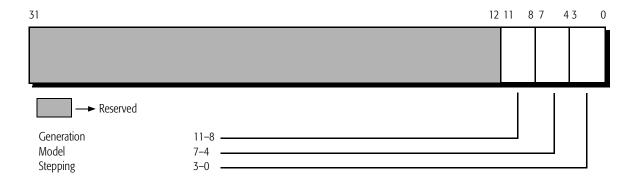

#### **AMD Processor Signature (Extended Function)**

Extended function 8000\_0001h returns the AMD processor signature. The signature is returned in the EAX register and provides generation, model, and stepping information for AMD processors. Figure 2 shows the contents returned in the EAX register.

Figure 2. Contents of EAX Register Returned by Extended Function 8000\_0001h

#### **Displaying the Processor Name**

Functions 8000\_0002h, 8000\_0003h, and 8000\_0004h return an ASCII string containing the name of the processor. These functions eliminate the need for software to search for the processor name in a lookup table, a process requiring a large block of memory and frequent updates. Instead, software can simply call these three functions to obtain the name string (48 ASCII characters in little endian format) and display it on the screen. Although the name string can be up to 48 characters in length, shorter names have the remaining byte locations filled with the ASCII NULL character (00h). To simplify the display routines and avoid using screen space, software only needs to display characters until a NULL character is detected.

See "Displaying the AMD Athlon™ Processor or AMD Duron™ Processor Name String" on page 26 for an example of how to properly obtain and display the processor name string.

#### **Name String Supports** up to 48 Characters

Note that the processor name string supports up to 48 characters. For example, the name string "AMD Athlon(tm)" uses 14 characters. Future name strings may be longer, so BIOS vendors should take this into consideration when displaying the name string on boot-up or in a system configuration screen.

#### **Differentiation of Processors of the Same Model Number**

AMD Athlon and AMD Duron processors model 6 must have the name string programmed properly according to the values in Table 6 on page 15 depending on the processor's L2 cache size. If the L2 cache size value reported by extended function 8000\_0006h ECX bits[31:16] is 256 or greater, then the processor is an AMD Athlon family processor. If the L2 cache size reported is less than 256, then the processor is an AMD Duron family processor.

#### S3 State **Considerations**

Before entering the S3—Suspend to RAM (STR)—state, the BIOS must save off the processor name string MSRs. Upon exiting the S3 state, the BIOS must then reload the processor name string back into the appropriate MSRs.

#### **Recommended Name String**

Table 5 summarizes the recommended name strings for AMD Athlon and AMD Duron processors through model 4.

Table 5. Processor Name Strings for AMD Athlon™ and AMD Duron™ Family of Processors **Through Model 4**

| Processor                | ASCII Name String                 |

|--------------------------|-----------------------------------|

| AMD Athlon™ Model 1      | AMD-K7(tm) processor              |

| AMD Athlon Model 2       | AMD Athlon(tm) processor          |

| AMD Duron™ Model 3       | AMD Duron(tm) <sup>1</sup>        |

| Mobile AMD Duron Model 3 | mobile AMD Duron(tm) <sup>1</sup> |

| AMD Athlon Model 4       | AMD Athlon(tm) <sup>1</sup>       |

| Notes:                   | <u> </u>                          |

This name string must be programmed into the processor by the BIOS. See the document, Displaying and Programming the Processor Name String BIOS Application Note, order# 90056.

Table 6. Recommended Name String by Platform Segment for AMD Athlon™ and AMD Duron™ Family of Processors Models 6 and Above

| Processor           | CPUID            | MP Capable (bit 19<br>of Extended<br>Feature Flags) | Platform Segment | Recommended Name String <sup>1</sup>          |

|---------------------|------------------|-----------------------------------------------------|------------------|-----------------------------------------------|

| AMD Athlon™ Model 6 | 660 or 661       | Reserved                                            | Multiprocessing  | AMD Athlon(tm) MP                             |

| AMD Athlon Model 6  | 660 or 661       | Reserved                                            | Desktop          | AMD Athlon(tm)                                |

| AMD Athlon Model    | 660 or 661       | Reserved                                            | Mobile           | mobile AMD Athlon(tm) 4                       |

| AMD Athlon Model 6  | 662              | 0                                                   | Multiprocessing  | AMD Athlon(tm) XP [xxxxx] <sup>2</sup>        |

| AMD Athlon Model 6  | 662              | 1                                                   | Multiprocessing  | AMD Athlon(tm) MP [xxxxx] <sup>2</sup>        |

| AMD Athlon Model 6  | 662              | N/A                                                 | Desktop          | AMD Athlon(tm) XP [xxxxx] <sup>2</sup>        |

| AMD Athlon Model 6  | 662              | N/A                                                 | Mobile           | mobile AMD Athlon(tm) 4                       |

| AMD Duron™ Model 6  | N/A <sup>3</sup> | N/A                                                 | Desktop          | AMD Duron(tm)                                 |

| AMD Duron Model 6   | N/A <sup>3</sup> | N/A                                                 | Mobile           | mobile AMD Duron(tm)                          |

| AMD Duron Model 7   | N/A <sup>3</sup> | Reserved                                            | Desktop          | AMD Duron(tm)                                 |