#### Advanced Micro Devices, Inc. AMD I/O Virtualization Technology (IOMMU) Specification License Agreement

AMD I/O Virtualization Technology (IOMMU) Specification License Agreement (this "Agreement") is a legal agreement between Advanced Micro Devices, Inc., Sunnyvale CA ("AMD") and the recipient of the AMD IO MMU Specification (any version) (the "Specification"), whether an individual or an entity ("You"). If you have accessed this Agreement as part of the Specification, or in the process of downloading the Specification from an AMD web site, by clicking an "I Accept" or similar button, or otherwise in the process of acquiring the Specification, or by using or providing feedback on the Specification, You agree to these terms. If this Agreement is attached to the Specification, by accessing, using or providing feedback on the Specification, You agree to these terms.

For good and valuable consideration, the receipt and sufficiency of which are acknowledged, You and AMD agree as follows:

- 1. You may review the Specification only (a) as a reference to assist You in planning and designing Your product, service or technology ("Product") to interface with an AMD or third-party Product as described in the Specification; and (b) to provide Feedback (defined below) on the Specification to AMD. All other rights are retained by AMD; this agreement does not give You rights under any AMD patents. You may not (i) duplicate any part of the Specification, (ii) remove this agreement or any notices from the Specification, or (iii) give any part of the Specification, or assign or otherwise provide Your rights under this Agreement, to anyone else.

- 2. The Specification may contain preliminary information or inaccuracies. The Specification is provided entirely "AS IS." To the extent permitted by law, AMD MAKES NO WARRANTY OF ANY KIND, DIS-CLAIMS ALL EXPRESS, IMPLIED AND STATUTORY WARRANTIES, AND ASSUMES NO LIABIL-ITY TO YOU FOR ANY DAMAGES OF ANY TYPE IN CONNECTION WITH THESE MATERIALS OR ANY INTELLECTUAL PROPERTY IN THEM.

- 3. If You are an entity and (a) merge into another entity or (b) a controlling ownership interest in You changes, Your right to use the Specification automatically terminates and You must destroy it.

- 4. You have no obligation to give AMD any suggestions, comments or other feedback ("Feedback") relating to the Specification. However, any Feedback you voluntarily provide may be used by AMD without restriction including the use in any revision or update to the Specification. Accordingly, if You do give AMD Feedback on any version of the Specification, You agree: (a) AMD may freely use, reproduce, license, distribute, and otherwise commercialize Your Feedback in any product made or distributed by or for AMD (an "AMD Product"); (b) You also grant third parties, without charge, only those patent rights necessary to enable other products to use or interface with any specific parts of an AMD Product that incorporates Your Feedback or Your Product; and (c) You will not give AMD any Feedback (i) that You have reason to believe is subject to any patent, copyright or other intellectual property claim or right of any third party; or (ii) subject to license terms which seek to require any product incorporating or derived from Your Feedback, any AMD Product or other AMD intellectual property, to be licensed to or otherwise provided to any third party.

- 5. This Agreement is governed by the laws of the State of Texas without regard to its choice of law principles. Any dispute involving it must be brought in a court having jurisdiction of such dispute in Travis County, Texas, and You waive any defenses allowing the dispute to be litigated elsewhere. If there is litigation, the losing party must pay the other party's reasonable attorneys' fees, costs and other expenses. If any part of this agreement is unenforceable, it will be considered modified to the extent necessary to make it enforceable, and the remainder shall continue in effect. This agreement is the entire agreement between You and AMD concerning the Specification; it may be changed only by a written document signed by both You and AMD.

# AMD I/O Virtualization Technology (IOMMU) Specification

Publication # **34434** Revision: **1.20**

Issue Date: February 2007

#### © 2005, 2006 Advanced Micro Devices, Inc.

All rights reserved. The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD Arrow logo, and combinations thereof, 3DNow!, and AMD PowerNow! are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a trademark of the HyperTransport Technology Consortium.

PCI Express and PCIe are trademarks of the PCI Special Interest Group.

PCI-X is registered trademark of the PCI Special Interest Group.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### **Advanced Micro Devices**

### **Table of Contents**

| 1 | Over | view    |                                                | 15 |

|---|------|---------|------------------------------------------------|----|

|   | 1.1  | Intende | ed Audience                                    | 15 |

|   | 1.2  | Definit | ions                                           | 15 |

|   | 1.3  | Bit Att | ributes                                        | 16 |

| 2 | IOM  | MII Ov  | erview                                         | 17 |

| _ | 2.1  |         | ecture Summary                                 |    |

|   | 2.2  |         | Models                                         |    |

|   | 2.2  | 2.2.1   | Replacing the GART                             |    |

|   |      | 2.2.2   | Substituting for the DEV                       |    |

|   |      | 2.2.3   | 32-bit to 64-bit Legacy I/O Device Mapping     |    |

|   |      | 2.2.4   | User Mode Device Accesses                      |    |

|   |      | 2.2.5   | Virtual Machine Guest Access to Devices.       |    |

|   |      | 2.2.6   | Virtualizing the IOMMU                         |    |

| _ |      |         | •                                              |    |

| 3 |      |         |                                                |    |

|   | 3.1  |         | or                                             |    |

|   |      | 3.1.1   | Normal Operation                               |    |

|   |      | 3.1.2   | IOMMU Logical Topology                         |    |

|   |      | 3.1.3   | IOMMU Error Reporting                          |    |

|   |      | 3.1.3.1 |                                                |    |

|   |      | 3.1.3.2 | $\epsilon$                                     |    |

|   |      | 3.1.3.3 | Memory Access Errors                           |    |

|   |      | 3.1.4   | Special Conditions                             |    |

|   | 3.2  |         | ructures                                       |    |

|   |      | 3.2.1   | Updating Shared Tables                         |    |

|   |      | 3.2.2   | Device Table                                   |    |

|   |      | 3.2.2.1 | Device Table Entry Format                      |    |

|   |      | 3.2.2.2 | Making Device Table Entry Changes              |    |

|   |      | 3.2.3   | I/O Page Tables                                |    |

|   |      | 3.2.4   | Sharing AMD64 CPU and IOMMU Page Tables        |    |

|   |      | 3.2.5   | Interrupt Remapping Tables                     |    |

|   | 3.3  |         | ands                                           |    |

|   |      | 3.3.1   | COMPLETION_WAIT                                |    |

|   |      | 3.3.2   | INVALIDATE_DEVTAB_ENTRY                        |    |

|   |      | 3.3.3   | INVALIDATE_IOMMU_PAGES                         |    |

|   |      | 3.3.4   | INVALIDATE_IOTLB_PAGES                         |    |

|   |      | 3.3.5   | INVALIDATE_INTERRUPT_TABLE                     |    |

|   |      | 3.3.6   | IOMMU Ordering Rules                           | 47 |

|   |      | 3.3.6.1 | Invalidation Command Ordering Requirements     |    |

|   | 2.4  | 3.3.6.2 | Invalidation Commands Interaction Requirements |    |

|   | 3.4  |         | Logging                                        |    |

|   |      | 3.4.1   | ILLEGAL_DEV_TABLE_ENTRY                        |    |

|   |      | 3.4.2   | IO_PAGE_FAULT                                  |    |

|   |      | 3.4.3   | DEV_TAB_HARDWARE_ERROR                         |    |

|   |      | 3.4.4   | PAGE_TAB_HARDWARE_ERROR                        |    |

|   |      | 3.4.5   | ILLEGAL_COMMAND_ERROR                          | 57 |

#### PID 34434 Rev 1.20 - February 2007

|   |      | 3.4.6 COMMAND_HARDWARE_ERROR                                     | 58         |

|---|------|------------------------------------------------------------------|------------|

|   |      | 3.4.7 IOTLB_INV_TIMEOUT                                          |            |

|   |      | 3.4.8 INVALID_DEVICE_REQUEST                                     | 59         |

|   | 3.5  | IOMMU Interrupt Support                                          | 61         |

|   | 3.6  | PCI Resources                                                    |            |

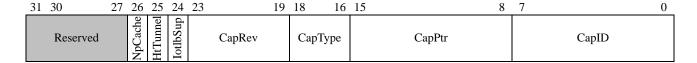

|   |      | 3.6.1 IOMMU Capability Block Registers                           | 61         |

|   |      | 3.6.2 IOMMU Control Registers                                    |            |

| 4 | Imp  | ementation Considerations                                        | 72         |

|   | 4.1  | Caching and Invalidation Strategies                              | 72         |

|   | 4.2  | Recommended IOMMU Topologies                                     | 73         |

|   | 4.3  | Issues Specific to the HyperTransport <sup>TM</sup> Architecture | 75         |

|   | 4.4  | Chipset Specific Implementation Issues                           | 75         |

|   | 4.5  | Software and BIOS Implementation Issues                          | 75         |

| 5 | ION  | MU Page Walker Pseudo Code                                       | 77         |

| 6 | Regi | ster List                                                        | <b>7</b> 9 |

## **List of Figures**

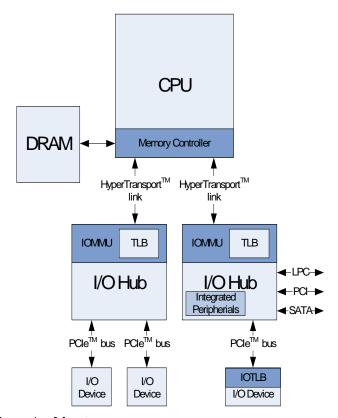

| Figure 1:  | Example Platform Architecture                                        | 18 |

|------------|----------------------------------------------------------------------|----|

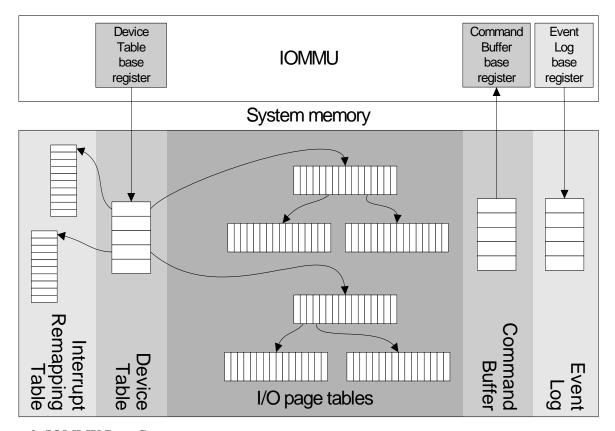

| Figure 2:  | IOMMU Data Structures                                                | 26 |

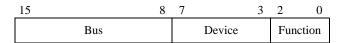

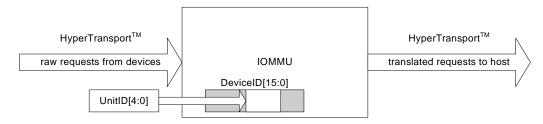

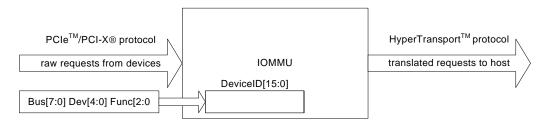

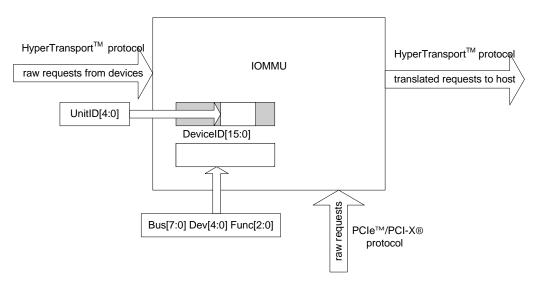

| Figure 3:  | DeviceID Derived from Peripheral RequesterID                         | 26 |

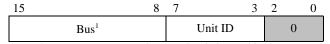

| Figure 4:  | DeviceID Derived from Peripheral UnitID                              | 27 |

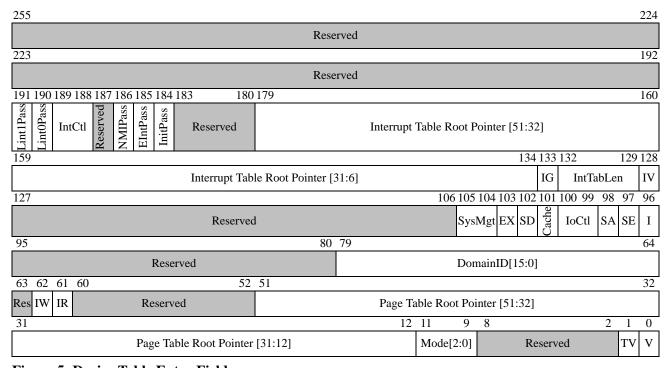

| Figure 5:  | Device Table Entry Fields                                            | 27 |

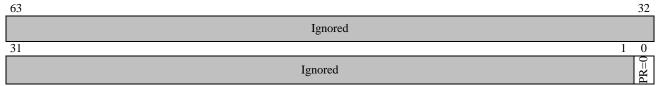

| Figure 6:  | I/O Page Table Entry Not Present (any level)                         | 36 |

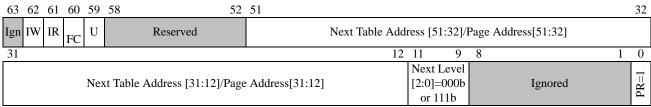

| Figure 7:  | I/O Page Translation Entry (PTE)                                     | 36 |

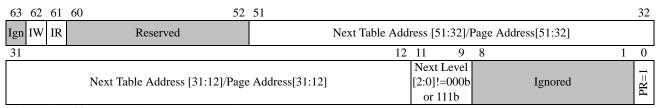

| Figure 8:  | I/O Page Directory Entry (PDE)                                       | 36 |

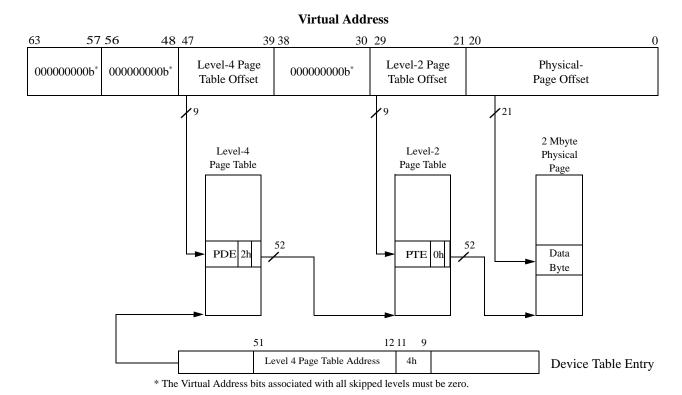

| Figure 9:  | Address Translation Example with Skipped Level                       | 37 |

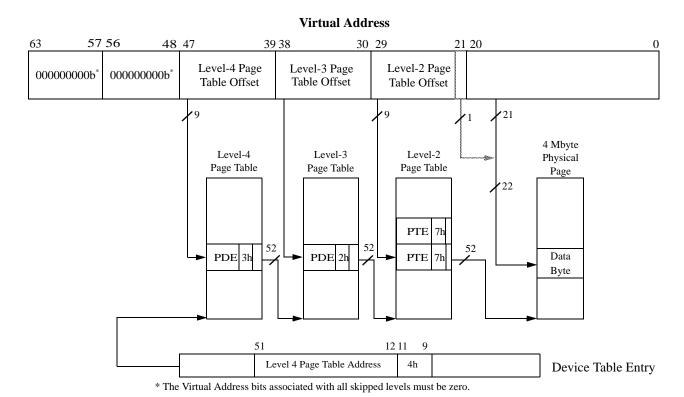

| Figure 10: | Address Translation Example with Page Size Larger than Default Size  | 37 |

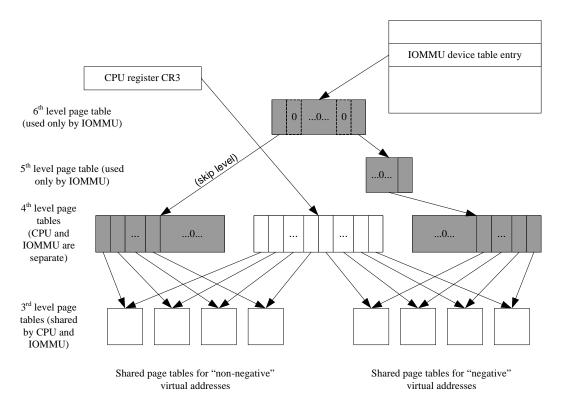

| Figure 11: | Sharing AMD64 and IOMMU Page Tables with Identical Addressing        | 39 |

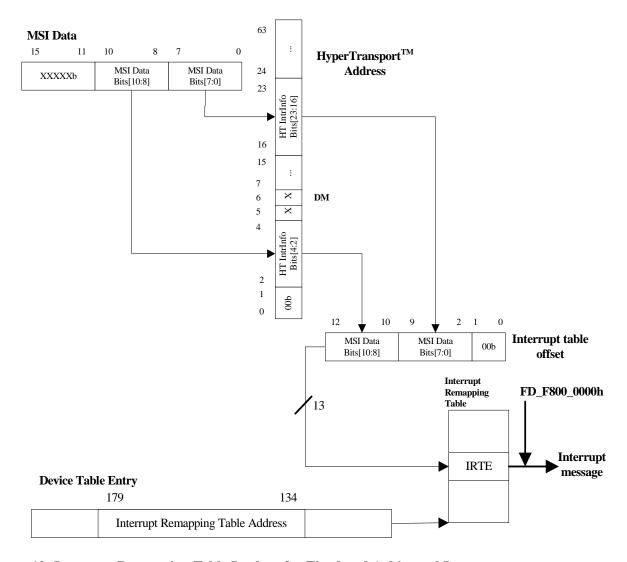

| Figure 12: | Interrupt Remapping Table Lookup for Fixed and Arbitrated Interrupts | 41 |

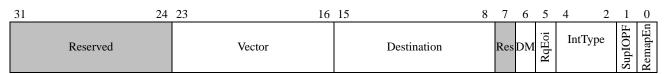

| Figure 13: | Interrupt Remapping Table Entry                                      | 41 |

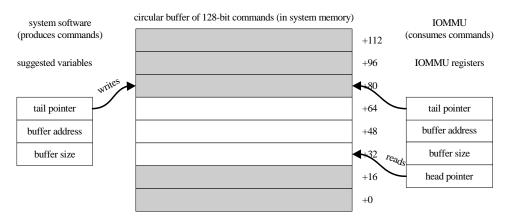

| Figure 14: | Circular Command Buffer in System Memory                             | 42 |

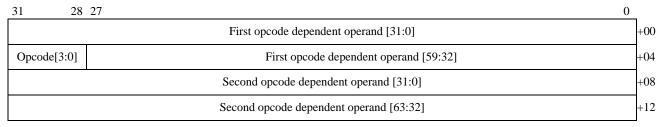

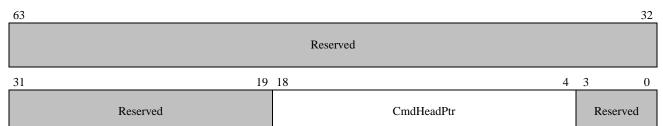

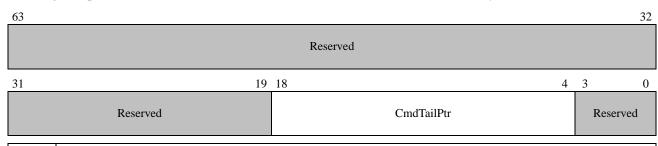

| Figure 15: | Generic Command Buffer Entry                                         | 43 |

| Figure 16: | COMPLETION_WAIT command format                                       | 44 |

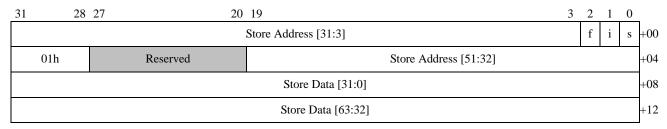

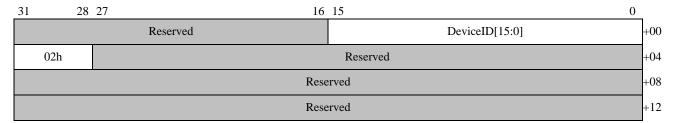

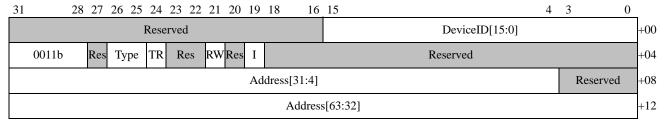

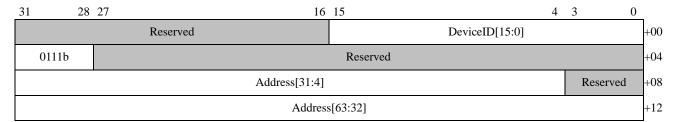

| Figure 17: | INVALIDATE_DEVTAB_ENTRY Command Format                               | 45 |

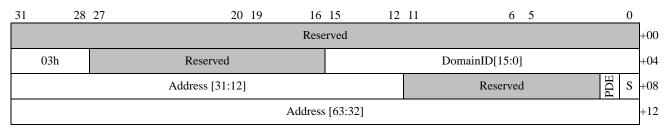

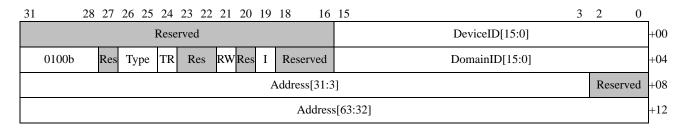

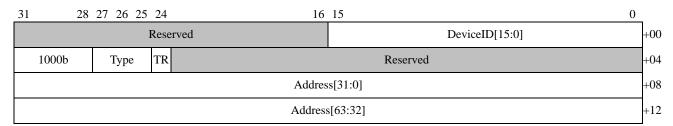

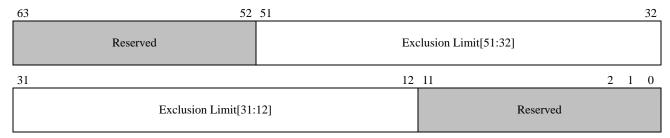

| Figure 18: | INVALIDATE_IOMMU_PAGES Command Encoding                              | 45 |

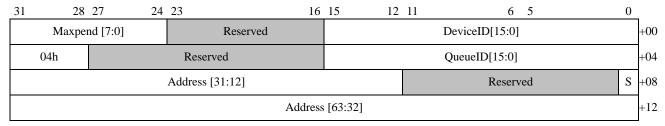

| Figure 19: | INVALIDATE_IOTLB_PAGES                                               | 46 |

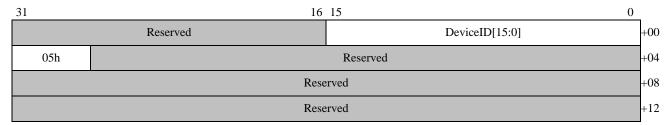

| Figure 20: | INVALIDATE_INTERRUPT_TABLE                                           | 46 |

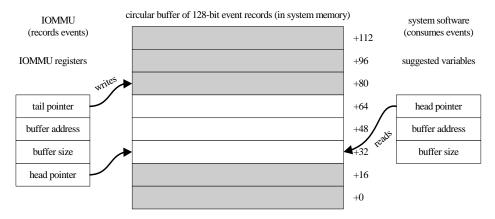

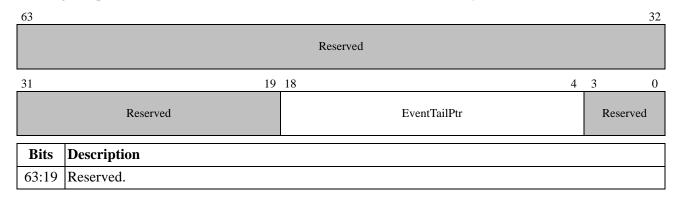

| Figure 21: | Circular Event Log in System Memory                                  | 48 |

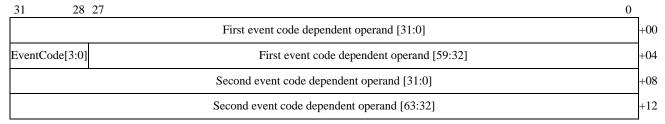

| Figure 22: | Generic Event Log Buffer Entry                                       | 49 |

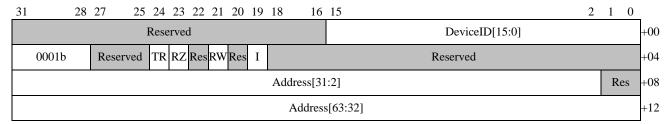

| Figure 23: | ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry                       | 53 |

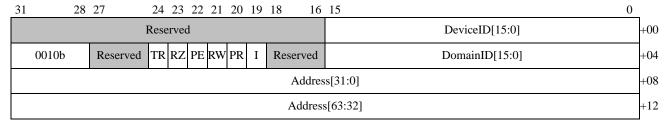

| Figure 24: | IO_PAGE_FAULT Event Log Buffer Entry                                 | 54 |

| Figure 25: | DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry                        | 55 |

| Figure 26: | PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry                       |    |

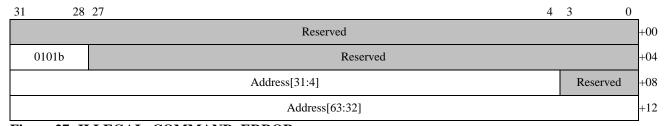

| Figure 27: | ILLEGAL_COMMAND_ERROR                                                | 57 |

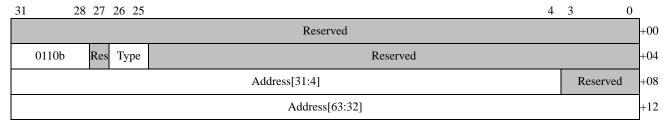

| Figure 28: | COMMAND_HARDWARE_ERROR Event Log Buffer Entry                        | 58 |

| Figure 29: | IOTLB_INV_TIMEOUT Event Log Buffer Entry                             | 59 |

| Figure 30: | INVALID_DEVICE_REQUEST Event Log Buffer Entry                        | 60 |

| Figure 31: | IOMMU in a Tunnel                                                    | 73 |

| Figure 32: | IOMMU in a Peripheral Bus Bridge                                     | 74 |

| Figure 33: | Hybrid IOMMU                                                         | 74 |

| Figure 34. | Chained Hybrid IOMMII in a Large System                              | 75 |

### **List of Tables**

| Table 1:  | Bit Attribute Definitions                                                      | 16 |

|-----------|--------------------------------------------------------------------------------|----|

| Table 2:  | Special Address Controls                                                       | 23 |

| Table 3:  | Device Table Entry Field Definitions                                           | 28 |

| Table 4:  | V and TV Fields in Device Table Entry                                          | 31 |

| Table 5:  | IV and IntCtl Fields in Device Table Entry for Fixed and Arbitrated Interrupts | 32 |

| Table 6:  | IV and Pass Fields in Device Table Entry for Selected Interrupts               | 32 |

| Table 7:  | Example Page Size Encodings                                                    | 34 |

| Table 8:  | Page Table Level Parameters                                                    |    |

| Table 9:  | IOMMU Interrupt Controls and Actions                                           | 40 |

| Table 10: | Interrupt Remapping Table Fields                                               |    |

| Table 11: | Event Summary                                                                  | 49 |

| Table 12: | ILLEGAL_DEV_TABLE_ENTRY Event Log Buffer Entry Fields                          | 53 |

| Table 13: | IO_PAGE_FAULT Event Log Buffer Entry Fields                                    | 54 |

| Table 14: | Event Log Type Field Encodings                                                 | 55 |

| Table 15: | DEV_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields                           | 55 |

| Table 16: | PAGE_TAB_HARDWARE_ERROR Event Log Buffer Entry Fields                          | 56 |

| Table 17: | ILLEGAL_COMMAND_ERROR Event Log Buffer Entry Fields                            | 57 |

| Table 18: | COMMAND_HARDWARE_ERROR Event Log Buffer Entry Fields                           | 58 |

| Table 19: | IOTLB_INV_TIMEOUT Event Log Buffer Entry Fields                                | 59 |

| Table 20: | INVALID_DEVICE_REQUEST Type Field Encodings                                    |    |

| Table 21: | INVALID_DEVICE_REQUEST Event Log Buffer Entry Fields                           | 60 |

## **Revision History**

| Date      | Rev  | Description                                                                                            |

|-----------|------|--------------------------------------------------------------------------------------------------------|

| February, | 1.20 | Throughout document, corrected trademark attributions.                                                 |

| 2007      |      | • In Section 1.2 [Definitions], defined low and high memory, MMU, PDE, and PTE.                        |

|           |      | • In Section 2.1 [Architecture Summary], clarified need for multiple IOMMUs.                           |

|           |      | • In Section 2.1 [Architecture Summary], revised Figure 1.                                             |

|           |      | • In Section 2.1 [Architecture Summary], clarified differences from GART and DEV.                      |

|           |      | • In Section 2.1 [Architecture Summary], added interrupt remapping.                                    |

|           |      | • In Section 2.2 [Usage Models], text clarifications throughout.                                       |

|           |      | • In Section 2.2.1 [Replacing the GART], clarified NPcache.                                            |

|           |      | • In Section 2.2.5 [Virtual Machine Guest Access to Devices], Table 10, marked all but                 |

|           |      | Fixed and Arbitrated as Reserved.                                                                      |

|           |      | • In Section 2.2.5 [Virtual Machine Guest Access to Devices], clarified DomainID.                      |

|           |      | • In Section 2.2.6 [Virtualizing the IOMMU] removed performance comments.                              |

|           |      | • In Section 3 [Architecture], clarified text throughout.                                              |

|           |      | • In Section 3.1 [Behavior], updated IOMMU transaction requirements.                                   |

|           |      | • In Section 3.1 [Behavior] and Section 3.1.1 [Normal Operation], added interrupt text.                |

|           |      | • In Section 3.1 [Behavior], added atomic operations.                                                  |

|           |      | • In Section 3.1 [Behavior], inserted text relocated from Section 3.1.1 [Normal Operation].            |

|           |      | • In Section 3.1 [Behavior], deleted reference to (deleted) Figure 2.                                  |

|           |      | • In Section 3.1 [Behavior], Table 2, deleted footnote #1 and renumbered footnotes.                    |

|           |      | • In Section 3.1 [Behavior] and Section 3.1.1 [Normal Operation], updated transactions types.          |

|           |      | • In Section 3.1 [Behavior] and Section 3.1.1 [Normal Operation], clarified behavior.                  |

|           |      | • In Section 3.1.1 [Normal Operation], clarified enumeration.                                          |

|           |      | • In Section 3.1.1 [Normal Operation], specified Port I/O space mappings and added I.                  |

|           |      | • In Section 3.1.1 [Normal Operation], clarified terminology and changed master abort to target abort. |

|           |      | Added Section 3.1.2 [IOMMU Logical Topology].                                                          |

|           |      | • In Section 3.1.2 [IOMMU Logical Topology], clarified topology comments.                              |

|           |      | • In Section 3.1.2 [IOMMU Logical Topology], clarified and extended Table 2.                           |

|           |      | • In Section 3.1.3 [IOMMU Error Reporting], clarified SA and SE.                                       |

|           |      | • In Section 3.1.3 [IOMMU Error Reporting], clarified event logging.                                   |

|           |      | • In Section 3.1.3 [IOMMU Error Reporting], added software note.                                       |

|           |      | • Added Section 3.1.3.1 [IOMMU Error Responses].                                                       |

|           |      | • In Section 3.1.3.1 [IOMMU Error Responses], Figure 5, added TaErrEn.                                 |

|           |      | • In Section 3.1.3.1 [IOMMU Error Responses], added clarifications and references.                     |

|           |      | • In Section 3.1.3.1 [IOMMU Error Responses], clarified error condition.                               |

|           |      | • In Section 3.1.3.1 [IOMMU Error Responses], clarified behavior when not enabled.                     |

|           |      | • In Section 3.1.3.2 [I/O Page Faults], clarified error handling.                                      |

|           |      | • In Section 3.1.3.2 [I/O Page Faults], changed "master abort" to "target abort".                      |

|           |      | Added Section 3.1.4 [Special Conditions].                                                              |

| Date | Rev | Description                                                                                                                                                                               |

|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     | • In Section 3.2 [Data Structures], added interrupt text.                                                                                                                                 |

|      |     | • In Section 3.2 [Data Structures], Figure 2, added Interrupt Remapping Tables.                                                                                                           |

|      |     | • In Section 3.2.1 [Updating Shared Tables], clarifications.                                                                                                                              |

|      |     | • In Section 3.2.2 [Device Table], enlarged device table entries to 256 bits and added                                                                                                    |

|      |     | interrupt information.                                                                                                                                                                    |

|      |     | • In Section 3.2.2 [Device Table], expanded discussion of valid bits.                                                                                                                     |

|      |     | • In Section 3.2.2 [Device Table], swapped order of Section 3.2.2.1 [Device Table Entry                                                                                                   |

|      |     | Format] and Section 3.2.2.2 [Making Device Table Entry Changes].                                                                                                                          |

|      |     | • In Section 3.2.2 [Device Table], added PCI Phantom functions.                                                                                                                           |

|      |     | • Added Section 3.2.2.1 [Device Table Entry Format].                                                                                                                                      |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], defined IV bit in Table 3, updated                                                                                                      |

|      |     | IntTabLen and reserved field [133:132], and clarified V bit.                                                                                                                              |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3, required alignment of                                                                                                          |

|      |     | interrupt table root pointer.                                                                                                                                                             |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3 and Table 5, added TV.                                                                                                          |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3, updated EX, IoCtl, SA, SE.                                                                                                     |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3 and Figure 5, defined IG.                                                                                                       |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3, renamed Lint1En and                                                                                                            |

|      |     | Lint0En as Lint1Pass and Lint0Pass.                                                                                                                                                       |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3 and Figure 5, defined                                                                                                           |

|      |     | NMIPass, InitPass, and EIntPass.                                                                                                                                                          |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3, added software note for SE.                                                                                                    |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 3, clarified SysMgt, IntCtl,                                                                                                      |

|      |     | Mode, IoCtl, EX, and Cache.  • In Section 3.2.2.1 [Device Table Entry Format], Table 3, replaced H with SysMgt.                                                                           |

|      |     | • In Section 3.2.2.1 [Device Table Entry Format], Table 5, replaced H with Systingt. • In Section 3.2.2.1 [Device Table Entry Format], added Table 4, Table 5, and Table 6.               |

|      |     | • Added Section 3.2.2.2 [Making Device Table Entry Changes].                                                                                                                              |

|      |     | Added Section 3.2.2.2 [Making Device Table Entry Changes].     In Section 3.2.2.2 [Making Device Table Entry Changes], revised pseudo-code                                                |

|      |     | examples.                                                                                                                                                                                 |

|      |     |                                                                                                                                                                                           |

|      |     | • In Section 3.2.3 [I/O Page Tables], removed S bit definition and modified next level                                                                                                    |

|      |     | encodings to make page tables compatible with AMD64 page table.                                                                                                                           |

|      |     | • In Section 3.2.3 [I/O Page Tables], Figure 7 and Figure 8, renamed NS bit as FC.                                                                                                        |

|      |     | • In Section 3.2.3 [I/O Page Tables], clarified Table 7 and added Figure 10.                                                                                                              |

|      |     | • In Section 3.2.3 [I/O Page Tables], added row to Table 7, clarified software note.                                                                                                      |

|      |     | • In Section 3.2.3 [I/O Page Tables], corrected typos in Figure 9 and Figure 10.                                                                                                          |

|      |     | • In Section 3.2.3 [I/O Page Tables], clarified usage of FC bit.                                                                                                                          |

|      |     | • In Section 3.2.3 [I/O Page Tables], corrected FC bit, U bit, and physical address bits                                                                                                  |

|      |     | [63:53] descriptions.                                                                                                                                                                     |

|      |     | • In Section 3.2.3 [I/O Page Tables], clarified zero-fill. • In Section 3.2.3 [I/O Page Tables], Table 7, changed law order "Un" bits to be 1s                                            |

|      |     | <ul> <li>In Section 3.2.3 [I/O Page Tables], Table 7, changed low-order "Un" bits to be 1s.</li> <li>In Section 3.2.3 [I/O Page Tables], clarified address bits above 48 bits.</li> </ul> |

|      |     | - In Section 3.2.3 [1/O I age Tables], claimed address bits above 46 bits.                                                                                                                |

| Date | Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     | <ul> <li>Added Section 3.2.5 [Interrupt Remapping Tables].</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], restructured text for clarity.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], clarified INIT, Startup, and device table control bits.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], Table 9, added to define interrupt controls.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], Table 10, updated IntType.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], Table 10 and Figure 13, added SupIOPF and redefined RemapEn.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], Figure 12, corrected DM.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], added software note for EOI.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], added EOI reply requirement.</li> <li>In Section 3.2.5 [Interrupt Remapping Tables], Figure 12, added MSI interrupt fields.</li> </ul>                                                                                                                                                                                                                                          |

|      |     | <ul> <li>In Section 3.3 [Commands], corrected command buffer tail pointer definition to match the definition in the register.</li> <li>In Section 3.3 [Commands], clarified command buffer head pointer.</li> <li>In Section 3.3.1 [COMPLETION_WAIT], changed scope of COMPLETION_WAIT.</li> <li>In Section 3.3.3 [INVALIDATE_IOMMU_PAGES], clarified PDE bit.</li> <li>In Section 3.3.3 [INVALIDATE_IOMMU_PAGES] and Section 3.3.4 [INVALIDATE_IOTLB_PAGES], corrected Address field.</li> <li>In Section 3.3.4 [INVALIDATE_IOTLB_PAGES], updated discussion of Maxpend.</li> <li>In Section 3.3.4 [INVALIDATE_IOTLB_PAGES], added QueueID to support virtual functions.</li> <li>In Section 3.3.4 [INVALIDATE_IOTLB_PAGES], added software note.</li> <li>In Section 3.3.5 [INVALIDATE_IOTLB_PAGES], clarified flush of entire IOTLB.</li> <li>Added Section 3.3.5 [INVALIDATE_INTERRUPT_TABLE].</li> <li>In Section 3.3.6 [IOMMU Ordering Rules], added requirements from Section 3.3.5 [INVALIDATE_INTERRUPT_TABLE] and HyperTransport™ tunnel requirements.</li> <li>In Section 3.3.6.2 [Invalidation Commands Interaction Requirements], clarified Invalidation Completion.</li> </ul> |

|      |     | <ul> <li>In Section 3.4 [Event Logging], corrected event log tail pointer definition to match the definition in the register.</li> <li>In Section 3.4 [Event Logging], defined "halt command processing".</li> <li>In Section 3.4 [Event Logging] updated descriptions to match Section 3.1.3.1 [IOMMU Error Responses].</li> <li>In Section 3.4 [Event Logging], clarified error recovery procedures.</li> <li>In Section 3.4 [Event Logging], clarified logging requirements.</li> <li>In Section 3.4 [Event Logging], Table 11, reclassified certain errors and renamed ILLEGAL_DEV_TABLE_ENTRY.</li> <li>In Section 3.4 [Event Logging], Table 11, updated with interrupt remapping and HyperTransport<sup>TM</sup> special address events.</li> <li>In Section 3.4 [Event Logging], Table 11, updated illegal level encoding error in IO_PAGE_FAULT event type.</li> <li>In Section 3.4 [Event Logging], Table 11 updated invalid translation errors, and split out some posted and non-posted writes.</li> <li>In Section 3.4 [Event Logging], Table 11, updated ILLEGAL_DEV_TABLE_ENTRY, INVALID_DEVICE_REQUEST, and IO_PAGE_FAULT event types.</li> </ul>                            |

| Date | Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     | <ul> <li>In Section 3.4.1 [ILLEGAL_DEV_TABLE_ENTRY], updated with interrupt remapping and HyperTransport™ special address events.</li> <li>In Section 3.4.1 [ILLEGAL_DEV_TABLE_ENTRY], moved text to Table 12.</li> <li>In Section 3.4.1 [ILLEGAL_DEV_TABLE_ENTRY], added RZ bit to Figure 23 and Table 12.</li> <li>In Section 3.4.1 [ILLEGAL_DEV_TABLE_ENTRY], Figure 23, corrected low-order address bits.</li> <li>In Section 3.4.2 [IO_PAGE_FAULT], moved text to Table 13.</li> <li>In Section 3.4.2 [IO_PAGE_FAULT], updated with interrupt remapping and HyperTransport™ special address events.</li> <li>In Section 3.4.3 [DEV_TAB_HARDWARE_ERROR], updated with interrupt remapping and HyperTransport™ special address events.</li> <li>In Section 3.4.3 [DEV_TAB_HARDWARE_ERROR], clarified use of I, TR, and RW.</li> <li>In Section 3.4.3 [DEV_TAB_HARDWARE_ERROR], moved text to Table 15.</li> <li>In Section 3.4.4 [PAGE_TAB_HARDWARE_ERROR], moved text to Table 16.</li> <li>In Section 3.4.5 [ILLEGAL_COMMAND_ERROR], moved text to Table 16.</li> <li>In Section 3.4.6 [COMMAND_HARDWARE_ERROR], moved text to Table 17.</li> <li>In Section 3.4.7 [IOTLB_INV_TIMEOUT], moved text to Table 19.</li> <li>In Section 3.4.8 [INVALID_DEVICE_REQUEST], updated with interrupt remapping and HyperTransport™ special address events.</li> <li>In Section 3.4.8 [INVALID_DEVICE_REQUEST], updated Table 20, added new error code, harmonized with changes to Table 11, and corrected reserved range.</li> </ul> |

|      |     | <ul> <li>In Section 3.4.8 [INVALID_DEVICE_REQUEST], moved text to Table 21.</li> <li>In Section 3.5 [IOMMU Interrupt Support], updated MSI requirements.</li> <li>In Section 3.5 [IOMMU Interrupt Support], clarified PassPW.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |     | <ul> <li>In Section 3.6 [PCI Resources], updated with the requirement that the IOMMU be implemented in an independent function, and the HyperTransport<sup>TM</sup> UnitId requirements.</li> <li>In Section 3.6 [PCI Resources], clarified wording and added PCI class and subclass.</li> <li>In Section 3.6 [PCI Resources], defined behavior of undefined IOMMU registers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Date Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

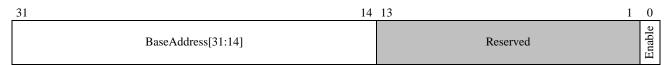

|          | <ul> <li>In IOMMU Range Register [Capability Offset 0Ch], added BusNumber, UnitID.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Capability Header [Capability Offset 00h] clarified.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Base Address Low Register [Capability Offset 04h] corrected alignment.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Base Address Low Register [Capability Offset 04h], added locking attribute to Enable; and applied locking to LastDevice, FirstDevice, and BusNumber in IOMMU Range Register [Capability Offset 0Ch].</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Base Address Low Register [Capability Offset 04h], the fields are optionally RO.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Base Address High Register [Capability Offset 08h], updated alignment.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], renamed IOMMU Miscellaneous Information Register [Capability Offset 10h] from IOMMU MSI Message Number Register, added VAsize and PAsize, and corrected MsiNum.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Miscellaneous Information Register [Capability Offset 10h], corrected MsiNum.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], clarified Bus Number field in IOMMU Range Register [Capability Offset 0Ch] description table.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Miscellaneous Information Register [Capability Offset 10h], updated Reserved, VAsize and PAsize.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], clarified NpCache and added implementation note.</li> <li>In Section 3.6.1 [IOMMU Capability Block Registers], IOMMU Miscellaneous Information Register [Capability Offset 10h], added HtAtsResv.</li> </ul> |

| Date | Rev | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date | Kev | <ul> <li>In Section 3.6.2 [IOMMU Control Registers], added byte-level addressing.</li> <li>In Section 3.6.2 [IOMMU Control Registers], Device Table Base Address Register [MMIO Offset 0000h], specified RW and reset.</li> <li>In Section 3.6.2 [IOMMU Control Registers], Device Table Base Address Register [MMIO Offset 0000h], corrected Size and changed Figure 5 [Device Table Entry Fields].</li> <li>In Section 3.6.2 [IOMMU Control Registers], Command Buffer Base Address Register [MMIO Offset 0008h], changed buffer alignment.</li> <li>In Command Buffer Base Address Register [MMIO Offset 0008h], updated ComLen encodings.</li> <li>In Section 3.6.2 [IOMMU Control Registers], Command Buffer Base Address Register [MMIO Offset 0008h] and Event Log Base Address Register [MMIO Offset 0010h], updated length fields.</li> <li>In Section 3.6.2 [IOMMU Control Registers], Event Log Base Address Register [MMIO Offset 0010h], changed buffer alignment and clarified write behavior.</li> <li>In Section 3.6.2 [IOMMU Control Registers], Event Log Base Address Register [MMIO Offset 0010h], corrected EventLen encodings.</li> <li>In Section 3.6.2 [IOMMU Control Registers], defined IOMMU Control Register [MMIO Offset 0018h] and IOMMU Status Register [MMIO Offset 2020h] to be 64-bit registers.</li> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Control Register [MMIO Offset 0018h], deleted TranCheckDis and expanded InvTimeOut.</li> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Control Register [MMIO Offset 0018h], deleted TranCheckDis and expanded InvTimeOut.</li> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Control Register [MMIO Offset 0018h], deleted TranCheckDis and expanded InvTimeOut.</li> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Control Register [MMIO Offset 0018h], defined 1 and 0 states and clarified ComwaitIntEn behavior.</li> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Control Register [MMIO Offset 0028h], corrected length of reset value.</li> <li>In Section 3.6.2 [IOMMU Control Regist</li></ul> |

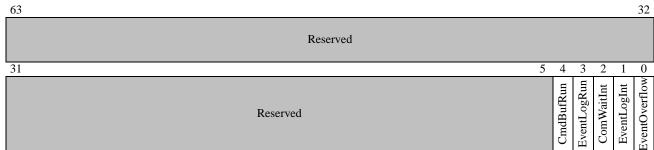

|      |     | <ul> <li>In Section 3.6.2 [IOMMU Control Registers], IOMMU Status Register [MMIO Offset 2020h] adds CmdBufRun, EventLogRun, and clarified EventOverflow behavior.</li> <li>Deleted Section 4.3 [RequesterID Mapping Capability Block Registers], causing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |     | Sections 4.4, 4.5, and 4.6 to be renumbered.  • Added Section 4.5 [Software and BIOS Implementation Issues].  • In Section 4.5 [Software and BIOS Implementation Issues], clarified "root device".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Date     | Rev  | Description                                                                                       |

|----------|------|---------------------------------------------------------------------------------------------------|

|          |      | • In Section 5 [IOMMU Page Walker Pseudo Code], updated pseudo-code for clarity and completeness. |

|          |      | Added Section 6 [Register List].                                                                  |

| 02/01/06 | 1.00 | • Initial Public Release.                                                                         |

#### 1 Overview

The I/O Memory Management Unit (IOMMU) is a chipset function that translates addresses used in DMA transactions and protects memory from illegal access by I/O devices.

The IOMMU can be used to:

- Replace the existing GART mechanism.

- Remap addresses above 4GB for devices that do not support 64-bit addressing.

- Allow a guest OS running under a VMM to have direct control of a device.

- Provide fine-grain control of device access to system memory.

- Enable a device direct access to user space I/O.

#### 1.1 Intended Audience

This document provides the IOMMU behavioral definition and associated design notes. It is intended for the use chipset designers and programmers involved in the development of low-level BIOS (basic input/output system) functions, drivers, and operating system kernel modules. It assumes prior experience in personal computer chipset design, microprocessor programming, and legacy x86 and AMD64 microprocessor architecture.

#### 1.2 Definitions

- ATS. Address translation service.

- BAR. PCI defined base address register.

- **Bounce Buffer**. A buffer located in low system memory for DMA traffic from devices that do not support 64-bit addressing. The OS copies the DMA data to or from the buffer to the real buffer in high memory used by the driver.

- Cold Reset. A reset generated by removing and reapplying power to the device.

- **Device Exclusion Vector (DEV)**. Contiguous arrays of bits in physical memory. Each bit in the DEV table represents a 4KB page of physical memory (including system memory and MMIO). The DEV table is packed as follows: bit[0] of byte 0 controls the first 4K bytes of physical memory; bit[1] of byte 0 controls the second 4K bytes of physical memory; etc.

- **DeviceID**. A 16 bit device identification number consisting of the Bus number, Device number and Function number.

- **Device Virtual Address**. The untranslated address used by a device in a DMA transaction. If the IOMMU is not enabled this address corresponds to the system physical address.

- Device Table. A table in system memory that maps DeviceIDs to DomainIDs and page table root pointers.

- Domain. See Protection Domain.

- **DomainID.** A 16-bit number chosen by software to identify a domain.

- GART. Graphics Address Remapping Table.

- Guest. An application or OS run by the host in its own virtual environment.

- **Guest Physical Address**. An address that is created by using the guest page tables to translate a guest virtual address. The result of the translation is a Guest Physical Address.

- Guest Virtual Address. The virtual addresses used by a guest application.

- **High memory.** Memory with addresses at or above 4G bytes.

- **Host**. The system software layer responsible for running guests.

- Low memory. Memory with addresses below 4G bytes.

- IOMMU. Refers to the I/O Memory Management Unit defined by this specification.

- MMIO. Read or write access to memory mapped resources provided by devices.

- MMU. Memory Management Unit.

- Message Signalled Interrupt (MSI). An interrupt that is signalled by generating a posted write to a system-defined physical address.

- Page Tables. A table structure in main memory used to translate an address from one representation to an alternate representation.

- **PR.** The present bit in the page table entries shown in Figure 6, Figure 7, and Figure 8.

- **Protection Domain**. A set of address mappings and access rights that can be shared by multiple devices.

- PDE. Page directory entry for address translation as shown in Figure 8.

- PTE. Page translation entry for address translation as shown in Figure 7.

- **System Physical Address**. The address used by the DRAM controller to specify a specific memory location or the address given to a MMIO device to specify a specific MMIO register.

#### 1.3 Bit Attributes

All bit attributes used in this specification are defined in Table 1. These attributes apply to register definitions, device table entries, page table entries, command buffer entries and event log entries.

**Table 1: Bit Attribute Definitions**

| Attribute       | Description                                                                                                                                                                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HwInit          | <b>Hardware Initialized</b> : Register bits are initialized by firmware or hardware mechanisms such as pin strapping or serial EEPROM. Bits are read-only after initialization and can only be reset (or write-once by firmware) with a cold reset. |

| Ignored<br>Ign  | <b>Ignored or Ign:</b> The state of the bit is a don't care to the IOMMU but is used by the processor MMU.                                                                                                                                          |

| RO              | Read-only register: Register bits are read-only and cannot be altered by software.                                                                                                                                                                  |

| RW              | <b>Read-Write register:</b> Register bits are read-write and may be either set or cleared by software to the desired state.                                                                                                                         |

| RW1C            | <b>Read-only status, Write-1-to-clear status register:</b> Register bits indicate status when read, a set bit indicating a status event may be cleared by writing a 1. Writing a 0 to RW1C bits has no effect.                                      |

| RW1S            | <b>Write-1-to-set register:</b> Register bits indicate status of an operation when read, setting bit initiates the operation. Hardware clears the bit when the operation completes. Writing a 0 to RW1S bits has no effect.                         |

| Reserved<br>Res | <b>Reserved or Res:</b> Reserved for future implementations. Bits must be implemented as read only zero.                                                                                                                                            |

| Unused<br>Un    | <b>Unused or Un:</b> Bit is not used by hardware. Software is allowed to use the bit for its own purposes.                                                                                                                                          |

#### 2 IOMMU Overview

The I/O Memory Management Unit (IOMMU) extends the AMD64 system architecture with support for address translation and access protection on DMA transfers by peripheral devices. The IOMMU enables several significant enhancements to system-level software:

- Legacy 32-bit I/O device support on 64-bit systems (without requiring bounce buffers and expensive memory copies).

- Secure user-level application access to selected I/O devices.

- Secure virtual machine guest operating system access to selected I/O devices.

The IOMMU can be thought of as a combination and generalization of two facilities included in the AMD64 architecture: the Graphics Aperture Remapping Table (GART) and the Device Exclusion Vector (DEV). The GART provides address translation of I/O device accesses to a small range of the system physical address space, and the DEV provides a limited degree of I/O device classification and memory protection. In combination with appropriate software manipulation of host CPU page tables, the IOMMU can provide GART or DEV functionality.

#### 2.1 Architecture Summary

The detailed architecture of the IOMMU is discussed in Chapter 3. The remainder of Chapter 2 consists of a brief summary of the architecture of the IOMMU along with a discussion of some anticipated usage models.

The IOMMU extends the concept of protection domains (domains for short) first introduced with the DEV. The IOMMU allows each I/O device in the system to be assigned to a specific domain and a distinct set of I/O page tables. When an I/O device attempts to read or write system memory, the IOMMU intercepts the access, determines the domain to which the device has been assigned, and uses the TLB entries associated with that domain or the I/O page tables associated with that I/O device to determine whether the access will be permitted as well as the actual location in system memory that will be accessed.

The IOMMU may optionally include support for remote IOTLBs. An I/O device with IOTLB support can cooperate with the IOMMU to maintain its own cache of address translations. This creates a framework for creating scalable systems with an IOMMU in which I/O devices may have different usage models and working set sizes. IOTLB-capable I/O devices contain private TLBs tailored for their own needs, creating a scalable distributed system of TLBs. The performance of IOTLB-capable I/O devices is not limited by the number of TLB entries implemented in the IOMMU.

Major system resources provided by the IOMMU include:

- I/O page tables which the IOMMU uses to provide permission checking and address translation on memory accesses by I/O devices.

- A device table that allows I/O devices to be assigned to specific domains and contains pointers to the I/O devices' page tables.

- An interrupt remapping table which the IOMMU uses to provide permission checking and interrupt remapping for I/O device interrupts.

In summary, the IOMMU is very similar to the processor's MMU, except that it provides address translation and page protection to memory accesses by peripheral devices rather than memory accesses by the processor and that it provides an interrupt remapping capability. However, compared to the processor's MMU, the IOMMU has a few differences.

The first difference is that the IOMMU provides no direct indication to an I/O device of a failed translation when processing an untranslated posted request.

A second difference is related to the organization of the AMD64 system architecture. AMD64 systems can consist of a number of processor and device nodes connected to each other by HyperTransport<sup>TM</sup> links. The IOMMU can only see and translate memory traffic that is routed through its node in the system fabric. In a system with multiple links and buses to I/O devices (see Figure 1), multiple IOMMUs are required to ensure that each I/O link or bus has appropriate protection and translation applied.

Figure 1: Example Platform Architecture

#### 2.2 Usage Models

Six models are discussed to highlight potential uses of the IOMMU in conventional and virtualized systems. These usage models can enhance system security and stability.

#### 2.2.1 Replacing the GART

The GART is a system facility that performs physical-to-physical translation of memory addresses within a graphics aperture. The GART was defined to allow complex graphical objects, such as texture maps, to appear to a graphics co-processor as if they were located in contiguous pages of memory, even though they are actually scattered across randomly allocated pages by most operating systems. The GART translates all accesses to the graphics aperture, including loads and stores executed by the host CPU as well as memory reads and writes performed by I/O devices. Only accesses whose system physical addresses are within the GART aperture are translated; however, the results of the translation can be any system physical address.

Unlike the GART, the IOMMU translates only memory accesses by I/O devices. However, with appropriate

programming, a host OS can use the IOMMU as a functional equivalent of the GART. First, the host OS must set up its own page tables to perform translations of host CPU accesses formerly translated by the GART. Then, to set up the same translations for I/O device-initiated accesses, the host OS must:

- Construct I/O page tables that specify the desired translations.

- Make an entry in the device table pointing to the newly constructed I/O page tables.

- Notify the IOMMU of the newly updated device table entry if NPcache=1.

At this point, all accesses by both the host CPU and the graphics device will have been mapped to the same pages as they would have been by the GART.

If the host OS wishes to change the page protection or translation, it must update both the processor page tables and, if not shared, the I/O page tables, and issue appropriate page-invalidate commands to both the processor and the IOMMU. Unlike the processor, the IOMMU may require page-invalidate commands after any change to the I/O page tables. (AMD64 processors do not require page-invalidate operations after changes to leaf page table entries that add permission and make no change to translation.) Sharing of page tables is discussed in Section 3.2.1 [Updating Shared Tables] and Section 3.2.4 [Sharing AMD64 CPU and IOMMU Page Tables].

Eventually the host OS may have to tear down the mappings when they are no longer used (e.g., removed from the system). The procedure is similar to setup:

- Mark the device table entry as not valid by setting V=1b, IV=0b, and IntCtl=00b in the device table entry. If transaction pass-through is acceptable, set V=0b and IV=0b.

- Notify the IOMMU of the newly invalidated device table entry.

- Wait for the IOMMU to indicate that the invalidation is complete.

- Finally, de-allocate the I/O page tables.

Since the IOMMU offers no facilities for restarting device accesses to unmapped or protected addresses, all pages that the device might access must be mapped with appropriate permissions. In this respect the IOMMU is no different from the GART.

The IOMMU cannot be used to emulate the GART if processor paging is not enabled; in that case host CPU accesses are not translated. This should not be a problem in practice, however, since historically the GART has only been used by systems that enable paging on the CPU.

In the foregoing procedures for setup and teardown of IOMMU page tables, the order of operations is chosen to prevent the IOMMU from ever looking at device or page table contents before they are initialized. During setup, the I/O page tables are constructed before the pointers are installed, and in teardown the pointers are cleared before the page table is destroyed. Similar principles apply to the other applications in this chapter.

#### 2.2.2 Substituting for the DEV

The Device Exclusion Vector is a simple security mechanism that was introduced with Secure Virtual Machine Architecture. Like the IOMMU, the DEV allows I/O devices to be classified into different domains. Associated with each domain is a bit vector, indexed by physical page address, indicating whether I/O devices in that domain are allowed to access the corresponding physical page.

The IOMMU provides not only protection but also translation. If only protection is needed, software can create identity-mapped I/O page tables that specify the desired protection.

#### 2.2.3 32-bit to 64-bit Legacy I/O Device Mapping

With the advent of large physical memories, legacy 32-bit devices that rely on DMA can no longer access arbitrary system memory. This complicates operating systems, which must introduce a distinction between low memory and high memory, and perform appropriate bookkeeping to ensure that legacy I/O devices are only commanded to perform transfers using low memory. The cost is not just complexity: in order to perform a transfer from a legacy I/O device to high memory, for example, the operating system typically allocates a bounce buffer in low memory, performs the transfer in low memory, and then copies the result to the real destination in high memory. For high-bandwidth I/O devices like disk controllers and network interfaces, the performance cost of bounce buffer allocation and copying can be large.

In some operating systems, the GART has been used to work around this problem. When the OS wishes to perform a transfer between a legacy I/O device and high memory, it allocates a portion of the GART aperture and maps those pages to high memory. It then commands the I/O device to execute the transfer using the address within the GART aperture, which must be located in low memory. Although this approach avoids the cost of bounce buffer copies, it is less than desirable, since the relatively small GART aperture must be shared by all legacy I/O devices and any graphics processors in the system. In the best case, device drivers will have additional locking and synchronization overhead associated with page allocation and de-allocation in the GART aperture; in the worst case, system performance is actually degraded due to serialization waiting for the GART aperture to become available.

The IOMMU creates a better solution. First of all, IOMMU translation applies to the full range of addresses an I/O device can generate, rather than requiring high-memory transfers to be mapped only within the narrow range of GART addresses. Moreover, the IOMMU's ability to assign each I/O device to a different domain means that heavily used I/O devices can be given their own sets of I/O page tables, and do not have to contend with other I/O devices for allocation and de-allocation of I/O pages.

#### 2.2.4 User Mode Device Accesses