# **AMD64 Technology**

# **Lightweight Profiling Specification**

| Publication No. | Revision | Date        |

|-----------------|----------|-------------|

| 43724           | 3.08     | August 2010 |

© 2008 — 2010 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD Arrow logo, AMD Opteron and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Linux is a registered trademark of Linus Torvalds.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| 1.1   Overview   1.1   Overview   2   Events and Event Records   2.1   Programmed Value Sample   2.2   Instructions Retired   2.3   Branches Retired   2.4   DCache Misses   2.4.1   Measuring Latency   2.4.2   Reporting the DCache Miss Data Address   2.5   CPU Clocks not Halted   2.6   CPU Reference Clocks not Halted   2.7   Programmed Event   2.8   Other Events   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Introduction   |                                         |    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------|----|--|--|

| 2.1         Programmed Value Sample           2.2         Instructions Retired           2.3         Branches Retired           2.4         DCache Misses           2.4.1         Measuring Latency           2.4.2         Reporting the DCache Miss Data Address           2.5         CPU Clocks not Halted           2.6         CPU Reference Clocks not Halted           2.7         Programmed Event           2.8         Other Events           3         Detecting LWP           3.1         Detecting LWP Presence           3.2         Detecting LWP SAAVE Area           3.3         Detecting LWP Capabilities           4         LWP Registers           4.1         XFEATURE_ENABLED_MASK Support           4.2         LWP_CFG—LWP Configuration MSR           4.3         LWP_CBADDR—LWPCB Address MSR           5.1         LLWPCB—Load LWPCB Address           5.2         SLWPCB—Store LWPCB Address           5.3         LWPUSHS—Insert User Sevent Record in LWP Ring Buffer           5.4         LWPINS—Insert User Event Record in LWP Ring Buffer           6         LWP Control Block           7         XSAVE/Area           7.3         XSAVE operation |                |                                         |    |  |  |

| 2.1         Programmed Value Sample           2.2         Instructions Retired           2.3         Branches Retired           2.4         DCache Misses           2.4.1         Measuring Latency           2.4.2         Reporting the DCache Miss Data Address           2.5         CPU Clocks not Halted           2.6         CPU Reference Clocks not Halted           2.7         Programmed Event           2.8         Other Events           3         Detecting LWP           3.1         Detecting LWP Presence           3.2         Detecting LWP SAAVE Area           3.3         Detecting LWP Capabilities           4         LWP Registers           4.1         XFEATURE_ENABLED_MASK Support           4.2         LWP_CFG—LWP Configuration MSR           4.3         LWP_CBADDR—LWPCB Address MSR           5.1         LLWPCB—Load LWPCB Address           5.2         SLWPCB—Store LWPCB Address           5.3         LWPUSHS—Insert User Sevent Record in LWP Ring Buffer           5.4         LWPINS—Insert User Event Record in LWP Ring Buffer           6         LWP Control Block           7         XSAVE/Area           7.3         XSAVE operation | d Event Recor  | ls                                      |    |  |  |

| 2.3   Branches Retired   2.4   DCache Misses   2.4.1   Measuring Latency   2.4.2   Reporting the DCache Miss Data Address   2.5   CPU Clocks not Halted   2.6   CPU Reference Clocks not Halted   2.7   Programmed Event   2.8   Other Events   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                                         |    |  |  |

| 2.4 DCache Misses 2.4.1 Measuring Latency 2.4.2 Reporting the DCache Miss Data Address 2.5 CPU Clocks not Halted 2.6 CPU Reference Clocks not Halted 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP Capabilities 4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block 7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                   | 0              | •                                       |    |  |  |

| 2.4.1 Measuring Latency 2.4.2 Reporting the DCache Miss Data Address  2.5 CPU Clocks not Halted 2.6 CPU Reference Clocks not Halted 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 5.4 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                    | nches Retired  |                                         | 17 |  |  |

| 2.4.2 Reporting the DCache Miss Data Address 2.5 CPU Clocks not Halted 2.6 CPU Reference Clocks not Halted 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 5.4 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                    |                |                                         |    |  |  |

| 2.5 CPU Clocks not Halted 2.6 CPU Reference Clocks not Halted 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 5.4 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                 | •              | •                                       |    |  |  |

| 2.6 CPU Reference Clocks not Halted 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP. 3.1 Detecting LWP Presence 3.2 Detecting LWP SAVE Area 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block.  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                            |                |                                         |    |  |  |

| 2.7 Programmed Event 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP XSAVE Area 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                                         |    |  |  |

| 2.8 Other Events  3 Detecting LWP 3.1 Detecting LWP Presence 3.2 Detecting LWP XSAVE Area 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  5.4 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                         |    |  |  |

| 3.1 Detecting LWP Presence 3.2 Detecting LWP XSAVE Area 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -              |                                         |    |  |  |

| 3.1 Detecting LWP Presence. 3.2 Detecting LWP XSAVE Area. 3.3 Detecting LWP Capabilities.  4 LWP Registers. 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR.  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address. 5.2 SLWPCB—Store LWPCB Address. 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer. 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer. 5.4 LWP Control Block.  7 XSAVE/XRSTOR 7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation. 7.4 XRSTOR operation. 7.5 Processor supplied values.  8 Implementation Notes. 8.1 Multiple Simultaneous Events. 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                                         |    |  |  |

| 3.2 Detecting LWP XSAVE Area 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                         |    |  |  |

| 3.3 Detecting LWP Capabilities  4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block 7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C              |                                         |    |  |  |

| 4 LWP Registers 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR. 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0              |                                         |    |  |  |

| 4.1 XFEATURE_ENABLED_MASK Support. 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer 6 LWP Control Block.  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                         |    |  |  |

| 4.2 LWP_CFG—LWP Configuration MSR 4.3 LWP_CBADDR—LWPCB Address MSR  5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR  7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes  8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LWP Registers  |                                         |    |  |  |

| 4.3 LWP_CBADDR—LWPCB Address MSR  LWP Instructions.  5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  LWP Control Block  XSAVE/XRSTOR  7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  Implementation Notes  8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EATURE_ENAI    | LED_MASK Support                        | 27 |  |  |

| 5 LWP Instructions. 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                                         |    |  |  |

| 5.1 LLWPCB—Load LWPCB Address 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block 7 XSAVE/XRSTOR 7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P_CBADDR—      | LWPCB Address MSR                       | 28 |  |  |

| 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR  7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ructions       | • • • • • • • • • • • • • • • • • • • • |    |  |  |

| 5.2 SLWPCB—Store LWPCB Address 5.3 LWPVAL—Insert Value Sample in LWP Ring Buffer 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR  7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WPCB—Load L    | WPCB Address                            | 29 |  |  |

| 5.4 LWPINS—Insert User Event Record in LWP Ring Buffer  6 LWP Control Block  7 XSAVE/XRSTOR  7.1 Configuration 7.2 XSAVE Area 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                                         |    |  |  |

| 6 LWP Control Block  7 XSAVE/XRSTOR  7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation 7.4 XRSTOR operation 7.5 Processor supplied values  8 Implementation Notes. 8.1 Multiple Simultaneous Events. 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PVAL—Insert    | Value Sample in LWP Ring Buffer         | 32 |  |  |

| 7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation. 7.4 XRSTOR operation. 7.5 Processor supplied values.  8 Implementation Notes. 8.1 Multiple Simultaneous Events. 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PINS—Insert U  | ser Event Record in LWP Ring Buffer     | 34 |  |  |

| 7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation. 7.4 XRSTOR operation. 7.5 Processor supplied values.  8 Implementation Notes. 8.1 Multiple Simultaneous Events. 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | trol Block     | •••••                                   | 37 |  |  |

| 7.1 Configuration. 7.2 XSAVE Area. 7.3 XSAVE operation. 7.4 XRSTOR operation. 7.5 Processor supplied values.  8 Implementation Notes. 8.1 Multiple Simultaneous Events. 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                         |    |  |  |

| 7.2 XSAVE Area. 7.3 XSAVE operation 7.4 XRSTOR operation. 7.5 Processor supplied values  8 Implementation Notes 8.1 Multiple Simultaneous Events 8.2 Processor State for Context Switch, SVM, and SMM. 8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                         |    |  |  |

| 7.3 XSAVE operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •              |                                         |    |  |  |

| 7.4 XRSTOR operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                                         |    |  |  |

| 7.5 Processor supplied values  8 Implementation Notes  8.1 Multiple Simultaneous Events  8.2 Processor State for Context Switch, SVM, and SMM.  8.2.1 Saving State at Thread Context Switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                                         |    |  |  |

| 8.1 Multiple Simultaneous Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •              |                                         |    |  |  |

| 8.1 Multiple Simultaneous Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tation Notes   |                                         |    |  |  |

| 8.2 Processor State for Context Switch, SVM, and SMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                                         |    |  |  |

| 8.2.1 Saving State at Thread Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                                         |    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                                         |    |  |  |

| 6.2.2 Saving State at 3 vivi worldswitch to a Different Guest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                | at SVM Worldswitch to a Different Guest |    |  |  |

| 8.2.3 Enabling SVM Live Migration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .3 Enabling SV | M Live Migration                        | 54 |  |  |

Contents 3

## 43724—Rev. 3.08—August 2010

| Appendix A | Glossary                                 | 59 |

|------------|------------------------------------------|----|

| 8.8        | Summary of LWP State                     | 57 |

|            | 8.7.2 Thread support                     |    |

|            | 8.7.1 System initialization              | 56 |

| 8.7        | Guidelines for Operating Systems         | 56 |

| 8.6        | Memory Access During LWP Operation       | 56 |

| 8.5        | Interrupts                               | 55 |

| 8.4        | Security                                 | 55 |

| 8.3        | LWPCB Access                             | 54 |

|            | 8.2.5 Notes on Restoring LWP State       | 54 |

|            | 8.2.4 Saving State at SMM Entry and Exit | 54 |

4 Contents

# **Figures**

| Figure 2-1. | Generic Event Record                         | 15 |

|-------------|----------------------------------------------|----|

| Figure 2-2. | Programmed Value Sample Event Record         | 16 |

| Figure 2-3. | Instruction Retired Event Record             | 17 |

| Figure 2-4. | Branch Retired Event Record                  | 18 |

| Figure 2-5. | DCache Miss Event Record                     | 20 |

| Figure 2-6. | CPU Clocks not Halted Event Record           | 21 |

| Figure 2-7. | CPU Reference Clocks not Halted Event Record | 21 |

| Figure 2-8. | Programmed Event Record                      | 22 |

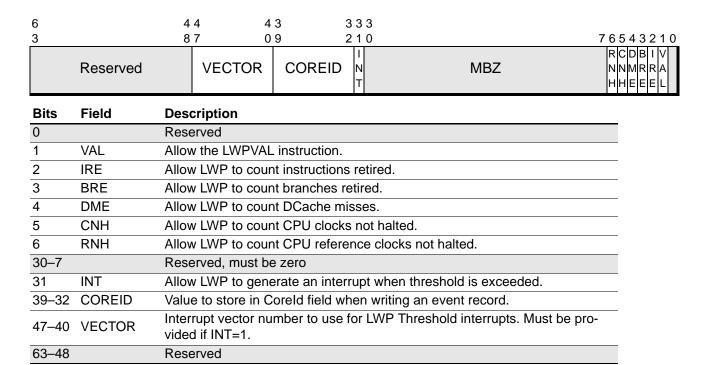

| Figure 4-1. | LWP_CFG—Lightweight Profiling Features MSR   | 28 |

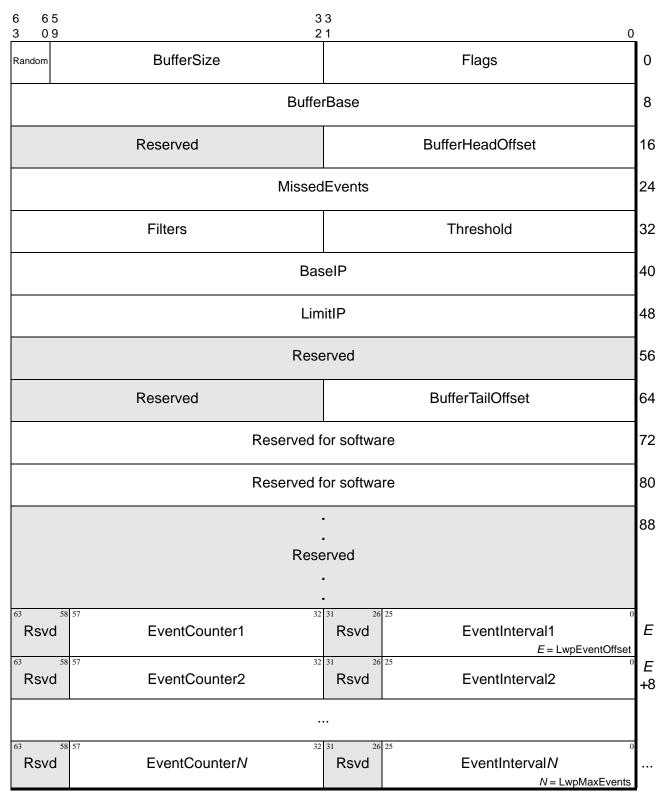

| Figure 6-1. | LWPCB—Lightweight Profiling Control Block    | 38 |

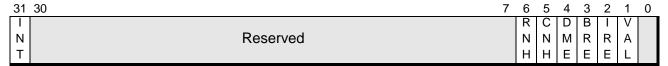

| Figure 6-2. | LWPCB Flags                                  | 42 |

| Figure 6-3. | LWPCB Filters                                | 42 |

| Figure 7-1. | XSAVE Area for LWP                           | 49 |

Figures 5

43724—Rev. 3.08—August 2010

6 Figures

## Lightweight Profiling Specification

## **Tables**

| Table 2-1. | EventId Values                                   | 16 |

|------------|--------------------------------------------------|----|

| Table 3-1. | Lightweight Profiling CPUID Values               | 24 |

| Table 6-1. | LWPCB—Lightweight Profiling Control Block Fields | 39 |

| Table 6-2. | LWPCB Filters                                    | 43 |

| Table 7-1. | XSAVE Area for LWP Fields                        | 49 |

Tables 7

43724—Rev. 3.08—August 2010

8 Tables

# **Revision History**

| Date        | Revision | Description                                                                                                                                                                                                                                                                                               |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2010 | 3.08     | Correct description of XRSTOR. Added reserved fields for software in LWPCB. Clarify PRD bit in Branches Retired event.                                                                                                                                                                                    |

| April 2010  | 3.06     | New encoding for LWP instructions. Removed 16-bit operand size variants. BufferSize in XSAVE area shortened to 28 bits. Clarify details of XRSTOR operation. Change "active" to "enabled" in instruction descriptions. Clarified behaviors when the CPL != 3. Specify reset value of LWP_CBADDR MSR as 0. |

| August 2009 | 3.04     | Clarified CPUID bits in 3.1, "Detecting LWP Presence" on page 23. Clarified LWP detections in 8.7.1, "System initialization" on page 56. Corrected 8.7.2, "Thread support" on page 56 to refer to LWP_CBADDR.                                                                                             |

| July 2009   | 3.03     | Second public version.                                                                                                                                                                                                                                                                                    |

| August 2007 | 3.00     | Initial public version.                                                                                                                                                                                                                                                                                   |

Revision History 9

43724—Rev. 3.08—August 2010

10 Revision History

## 1 Introduction

Lightweight Profiling (LWP) is an AMD64 extension to allow user mode processes to gather performance data about themselves with very low overhead. Modules such as managed runtime environments and dynamic optimizers can use LWP to monitor the running program with high accuracy and high resolution. They can quickly discover performance problems and opportunities and immediately act on this information.

LWP allows a program to gather performance data and examine it either by polling or by taking an occasional interrupt. It introduces minimal additional state to the CPU and the process. LWP differs from the existing performance counters and from Instruction Based Sampling (IBS) because it collects large quantities of data before an taking an interrupt. This substantially reduces the overhead of using performance feedback. An application that polls LWP data requires no interrupts at all.

A program can control LWP data collection entirely in user mode. It can start, stop, and reconfigure profiling without calling the kernel.

LWP runs within the context of a thread, so it can be used by multiple processes in a system at the same time without interference. This also means that if one thread is using LWP and another is not, the latter thread incurs no profiling overhead.

LWP is supported in both long mode and legacy mode.

#### 1.1 Overview

When enabled, LWP hardware monitors one or more events during the execution of user-mode code and periodically inserts event records into a ring buffer in the address space of the running process. When the ring buffer is filled beyond a user-specified threshold, the hardware can cause an interrupt which the operating system (OS) uses to signal a process to empty the ring buffer. With proper OS support, the interrupt can even be delivered to a separate process or thread.

LWP only counts instructions that retire in user mode (CPL = 3). Instructions that change to CPL 3 from some other level are not counted, since the instruction address is not an address in user mode space. LWP does not count hardware events while the processor is in system management mode (SMM) and while entering or leaving SMM.

Once LWP is enabled, each user-mode thread uses the *LLWPCB* and *SLWPCB* instructions to control LWP operation. These instructions refer to a data structure in application memory called the Lightweight Profiling Control Block, or *LWPCB*, to specify the profiling parameters and to interact with the LWP hardware. The LWPCB in turn points to a buffer in memory in which LWP stores event records.

Each thread in a multi-threaded process must configure LWP separately. A thread has its own ring buffer and counters which are context switched with the rest of the thread state. However, a single monitor thread could collect and process LWP data from multiple other threads.

During profiling, the LWP hardware monitors and reports on one or more types of events. Following are the steps in this process:

- 1. **Count**—Each time an instruction is retired, LWP decrements its internal event counters for all of the events associated with the instruction. An instruction can cause zero, one, or multiple events. For instance, an indirect jump through a pointer in memory counts as an instruction retired, a branch retired, and may also cause up to two DCache misses (or more, if there is a TLB miss) and up to two ICache misses.

- Some events may have filters or conditions on them that regulate counting. For instance, the application may configure LWP so that only cache miss events with latency greater than a specified minimum are eligible to be counted.

- 2. **Gather**—When an event counter becomes negative, the event should be reported. LWP gathers an event record. This is the equivalent of filling in an internal copy of an event record, though actual implementation may vary. The event's counter may continue to count below zero until the record is written to the event ring buffer.

- For most events, such as instructions retired, LWP gathers an event record describing the instruction that caused the counter to become negative. However, it is valid for LWP to gather event record data for the *next* instruction that causes the event, or to take other measures to capture a record. Some of these options are described with the individual events.

- An implementation can choose to gather event information on one or many events at any one time. If multiple event counters become negative, an advanced LWP implementation might gather one event record per event and write them sequentially. A basic LWP implementation may choose one of the eligible events. Other events continue counting but wait until the first event record is written. LWP picks the next eligible instructions for the waiting events. This situation should be extremely uncommon if software chooses large event interval values.

- LWP may discard an event occurrence. For instance, if the LWPCB or the event ring buffer needs to be paged in from disk, LWP might choose not to preserve the pending event data. If an event is discarded, LWP gathers an event record for the next instruction to cause the event.

- Similarly, if LWP needs to replay an instruction to gather a complete event record, the replay

may abort instead of retiring. The event counter continues counting below zero and LWP

gathers an event record for the next instruction to cause the event.

- 3. **Store**—When a complete event record is gathered, LWP stores it into the event ring buffer in the process' address space and advances the ring buffer head pointer.

- LWP checks to see if the ring buffer is full, i.e., if advancing the ring buffer head pointer would make it equal to the tail pointer. If the buffer is full, LWP increments the 64-bit counter LWPCB. Missed Events. It does not advance the head pointer.

- If more than one event record reaches the Store stage simultaneously, only one need be stored. Though LWP might store all such event records, it may delay storing some event records or it may discard the information and proceed to choose the next eligible instruction for the discarded event type(s). This behavior is implementation dependent.

- The store need not complete synchronously with the instruction retiring. In other words, if LWP buffers the event record contents, the Store stage (and subsequent stages) may complete some number of cycles after the tagged instruction retires. The data about the event and the instruction are precise, but the Report and Reset steps (below) may complete later.

- 4. **Report**—If LWP threshold interrupts are enabled and the space used in the event ring buffer exceeds a user-defined threshold, LWP initiates an interrupt. The OS can use this to signal the process to empty the ring buffer. Note that the interrupt may occur significantly later than the event that caused the threshold to be reached.

- 5. **Reset**—For each event that was stored, the counter is reset to its programmed interval. If requested by the application, LWP applies randomization to the low order bits of the interval. Counting for that event continues. Reset happens if the ring buffer head pointer was advanced or if the missed event counter was incremented. If the event counter went below -1, indicating that additional events occurred between the selected event and the time it was reported, that overrun value reduces the reset value so as to preserve the statistical distribution of events.

- For all events except the LWPVAL instruction, the hardware may impose a minimum on the reset value of an event counter. This prevents the system from spending too much time storing samples rather than making forward progress on the application. Any minimum imposed by the hardware can be detected by examining the EventIntervaln fields in the LWPCB after enabling LWP.

An application should periodically remove event records from the ring buffer and advance the tail pointer. (If the application does not process the event records quickly enough or often enough, the LWP hardware will detect that the ring buffer is full and will miss events.) There are two ways to process the gathered events: interrupts or polling.

The application can wait until a threshold interrupt occurs to process the event records in the ring buffer. This requires OS or driver support. (As a consequence, interrupts can only be enabled if a kernel mode routine allows it; refer to "LWP\_CFG—LWP Configuration MSR" on page 27.) One usage model is to associate the LWP interrupt with a semaphore or mutex. When the interrupt occurs, the OS or driver signals the associated object. A thread waiting on the object wakes up and empties the ring buffer. Other models are possible, of course.

Alternatively, the application can have a thread that periodically polls the ring buffer. The polling thread need not be part of the process that is using LWP. It can be in a separate process that shares the memory containing the LWP control block and ring buffer.

Access to the ring buffer uses a lockless protocol between the LWP hardware and the application. The hardware owns the head pointer and the area in the ring buffer from the head pointer up to (but not including) the tail pointer. (That area might wrap around from the end of the ring to the beginning, of course.) The application must not modify the head pointer nor rely on any data in that region of the ring buffer. If the application has a stale value for the head pointer, it may miss an existing event record but it will never read invalid data. When the application is done emptying the ring buffer, it should refresh its copy of the head pointer to see if the LWP hardware has added any new event records.

Similarly, the application owns the tail pointer and the area in the ring buffer from the tail pointer up to (but not including) the head pointer. The hardware will never modify the tail pointer or overwrite the

data in that region of the ring buffer. If the hardware has a stale value for the tail pointer, it may consider that the ring buffer is full or at its threshold, but it will never overwrite valid data. Instead, it refreshes its copy of the tail pointer and rechecks to see if the full or threshold condition still applies.

## 2 Events and Event Records

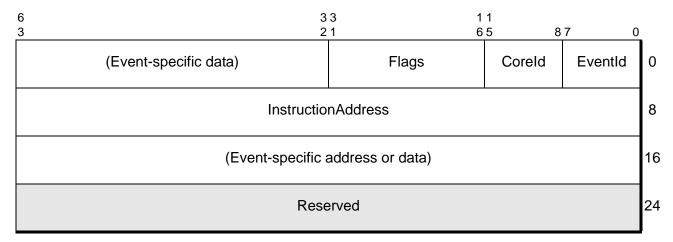

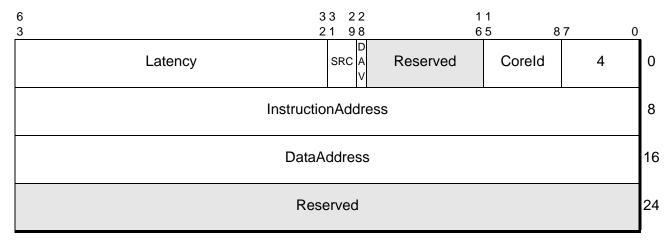

When a monitored event overflows its event counter, LWP puts an event record into the LWP event ring buffer. Each event record in the ring buffer is 32 bytes long in version 1 of LWP. The actual event record size is returned as *LwpEventSize* (see "Detecting LWP Capabilities" on page 23).

Reserved fields and fields that are not defined for a particular event are set to zero when LWP writes an event record.

| Bytes | Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | EventId            | Event identifier specifying the event record type. Valid identifiers are 1 to 255. 0 is an invalid identifier.                                                                                                                                                                                                                                                                                                        |

| 1     | Coreld             | CPU core identifier value from COREID field of LWP_CFG (see "LWP_CFG—LWP Configuration MSR" on page 27). For multicore systems, this typically identifies the core on which LWP is running. This allows software to aggregate event records from multiple threads into a single data structure without losing CPU information. It also allows software to detect when a thread has migrated from one core to another. |

| 3–2   | Flags              | Event-specific flags.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7–4   |                    | Event-specific data.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15–8  | InstructionAddress | The effective address of the instruction that triggered this event record. This is the value before adding in the CS base address. If the base is non-zero, software must track it. (Modern operating systems use a CS base of zero, and CS is unused in long mode.)                                                                                                                                                  |

| 23–16 |                    | Event-specific address or other data.                                                                                                                                                                                                                                                                                                                                                                                 |

| 31–24 |                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                              |

Figure 2-1. Generic Event Record

Table 2-1 lists the event identifiers for the events defined in version 1 of LWP. They are described in detail in the following sections.

Table 2-1. EventId Values

| EventId | Description                     |

|---------|---------------------------------|

| 0       | Reserved – invalid event        |

| 1       | Programmed value sample         |

| 2       | Instructions retired            |

| 3       | Branches retired                |

| 4       | DCache misses                   |

| 5       | CPU clocks not halted           |

| 6       | CPU reference clocks not halted |

| 255     | Programmed event                |

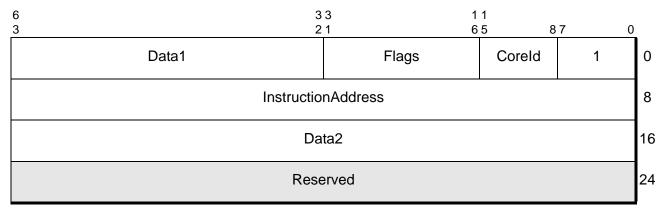

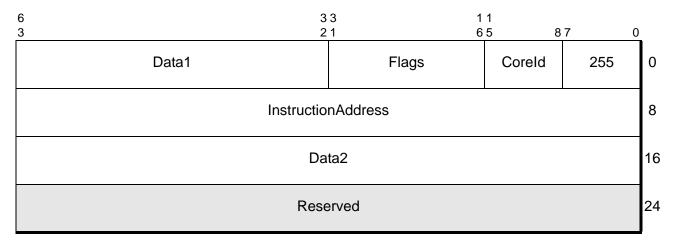

## 2.1 Programmed Value Sample

LWP decrements the event counter each time the program executes the LWPVAL instruction (see "LWPVAL—Insert Value Sample in LWP Ring Buffer" on page 32). When the counter becomes negative, it stores an event record with an EventId of 1. The data in the event record come from the operands to the instruction as detailed in the instruction description.

| <b>Bytes</b> | Field              | Description                                         |

|--------------|--------------------|-----------------------------------------------------|

| 0            | EventId            | Event identifier = 1                                |

| 1            | Coreld             | CPU core identifier from LWP_CFG                    |

| 3–2          | Flags              | Immediate value (bottom 16 bits)                    |

| 7–4          | Data1              | Reg/mem value                                       |

| 15–8         | InstructionAddress | Instruction address of LWPVAL instruction           |

| 23–16        | Data2              | Reg value (zero extended if running in legacy mode) |

| 31–24        |                    | Reserved                                            |

Figure 2-2. Programmed Value Sample Event Record

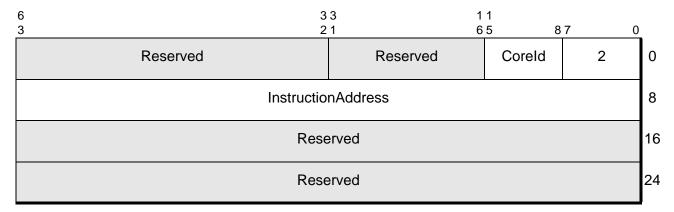

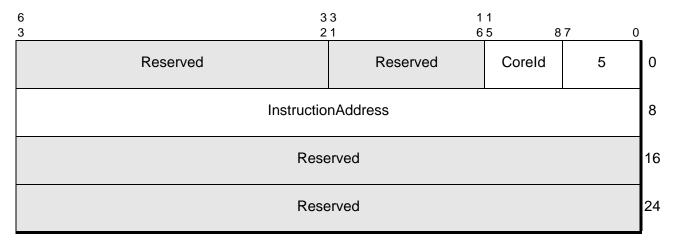

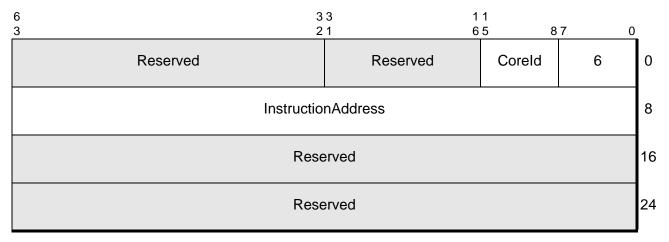

#### 2.2 Instructions Retired

LWP decrements the event counter each time an instruction retires. When the counter becomes negative, it stores a generic event record with an EventId of 2.

Instructions are counted if they execute entirely in user mode (CPL = 3). Instructions that change to CPL 3 from some other level are not counted, since the instruction address is not an address in user mode space. All user mode instructions are counted, including LWPVAL and LWPINS.

Figure 2-3. Instruction Retired Event Record

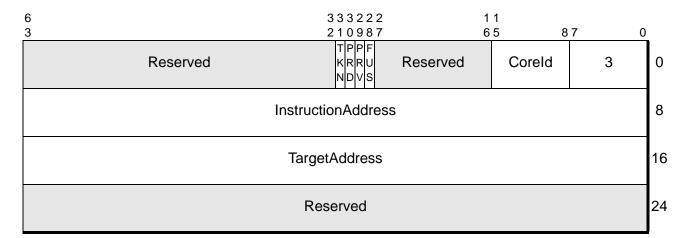

### 2.3 Branches Retired

LWP decrements the event counter each time a transfer of control retires, regardless of whether or not it is taken. When the counter becomes negative, it stores an event record with an EventId of 3.

Control transfer instructions that are counted are:

- JMP (near), Jcc, JCXZ, JEXCZ, and JRCXZ

- LOOP, LOOPE, and LOOPNE

- CALL (near) and RET (near)

LWP does not count JMP (far), CALL (far), RET (far), traps, or interrupts (whether synchronous or asynchronous), nor does it count operations that switch to or from ring 3, SMM, or SVM, such as SYSCALL, SYSENTER, SYSEXIT, SYSRET, VMMCALL, INT, or INTO.

Some implementations of the AMD64 architecture perform an optimization called "fusing" when a compare operation (or other operation that sets the condition codes) is followed immediately by a conditional branch. The processor fuses these into a single operation internally before they are executed. While this is invisible to the programmer, the address of the actual branch is not available for LWP to report when the (fused) instruction retires. In this case, LWP sets the FUS bit in the event record and reports the address of the operation that set the condition codes. If FUS is set, software can find the address of the actual branch by decoding the instruction at the reported InstructionAddress and

adding its length to that address. (Note that fused instructions do count as 2 instructions for the Instructions Retired event, since there were 2 x86 instructions originally.)

| 0       EventId       Event identifier = 3         1       CoreId       CPU core identifier from LWP_CFG         3-2       27-16       Reserved         1—Fused operation. InstructionAddress points to a compare operation (or other operation that sets the condition codes) immediately preceding the branch.         0—InstructionAddress points to the branch instruction.         1—PRD bit is valid         0—Prediction information is not available Some implementations of LWP may be unable to capture branch prediction information on some or all branches. | <b>Bytes</b> | Bits  | Field              | Description                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| 3-2 27-16  Reserved  1—Fused operation. InstructionAddress points to a compare operation (or other operation that sets the condition codes) immediately preceding the branch.  0—InstructionAddress points to the branch instruction.  1—PRD bit is valid  0—Prediction information is not available Some implementations of LWP may be unable to capture                                                                                                                                                                                                                | 0            |       | EventId            | Event identifier = 3                                                                                                       |

| 1—Fused operation. InstructionAddress points to a compare operation (or other operation that sets the condition codes) immediately preceding the branch.  0—InstructionAddress points to the branch instruction.  1—PRD bit is valid  0—Prediction information is not available Some implementations of LWP may be unable to capture                                                                                                                                                                                                                                     | 1            |       | Coreld             | CPU core identifier from LWP_CFG                                                                                           |

| operation (or other operation that sets the condition codes) immediately preceding the branch.  0—InstructionAddress points to the branch instruction.  1—PRD bit is valid  0—Prediction information is not available Some implementations of LWP may be unable to capture                                                                                                                                                                                                                                                                                               | 3–2          | 27–16 |                    | Reserved                                                                                                                   |

| 1—PRD bit is valid  0—Prediction information is not available Some implementations of LWP may be unable to capture                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3            | 28    | FUS                | operation (or other operation that sets the condition codes) immediately preceding the branch.                             |