# Arm Firmware Framework for Arm A-profile

Document number DEN0077A

Document quality ALP0

Document version 1.2

Document confidentiality Non-confidential

Copyright © 2023 Arm Limited or its affiliates. All rights reserved.

# **Arm Firmware Framework for Arm A-profile**

## Release information

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Enabled platforms to optionally bypass multi-borrowe     Added FFA_CONSOLE_LOG ABI     Added guidance to enable communication between ELSPs     Added register based discovery mechanism PARTITIC     Enabled storing IMPDEF information in EMAD     Enabled FFA_YEILD to be used with Direct messagin     Enabled an SP to be periodically woken up     Extended Direct messaging register usage     Enabled an partition to export multiple UUIDs     Allowed delegating of G0 interrupts in EL3 via FFA_E |         | <ul> <li>Added guidance to enable communication between EL3 Logical SPs and other SPs</li> <li>Added register based discovery mechanism PARTITION_INFO_GET_REGS</li> <li>Enabled storing IMPDEF information in EMAD</li> <li>Enabled FFA_YEILD to be used with Direct messaging</li> <li>Enabled an SP to be periodically woken up</li> <li>Extended Direct messaging register usage</li> <li>Enabled an partition to export multiple UUIDs</li> <li>Allowed delegating of G0 interrupts in EL3 via FFA_EL3_INTR_HANDLE</li> <li>Added a canonical UUID for SPs that speak the EFI MM communication</li> </ul>                                                                                                                                                                                                                                                                                                                                            |  |

| 2022/Nov/30 v1.1 REL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | <ul> <li>Language fixes based upon feedback</li> <li>Clarified ABI return code if RX/TX buffers are used but not registered</li> <li>Clarified valid instances and conduits for direct requests and responses</li> <li>Restructured layout of FFA_MEM_PERM documentation</li> <li>Clarified Relayer responsibilities for memory transactions with both VMs and SPs</li> <li>Clarified terminology in FFA_MEM_LEND description to align with lender perspective</li> <li>Clarified when an owner can reclaim access to a memory region</li> <li>Clarified memory handle lifetime</li> <li>Added diagrams to illustrate memory management transactions</li> <li>Clarified allowed usage of FFA_SECONDARY_EP_REGISTER</li> <li>Fixed the reference v1.0 memory descriptor format</li> <li>Clarified run-time model manifest entry depreciation notice</li> <li>Added IMPDEF mechanism example to prevent privilege escalation with FFA_MEM_DONATE</li> </ul> |  |

| Date        | Version   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2022/Mar/29 | v1.1 EAC0 | <ul> <li>Clarified guidance on partition ID and UUID usage</li> <li>Revised protocol to pass boot information to the SPMC or an SP</li> <li>Added compliance requirements for various features supported by the Frameworl</li> <li>Clarified guidance on interrupt management in Secure world</li> <li>Updated guidance on direct message passing to be used with logical partitions</li> <li>Clarified usage of FFA_INTERRUPT ABI depending upon endpoint state and FF-A instance</li> <li>Clarified usage of FFA_VERSION to enable negotiation of a compatible Framework version</li> <li>Clarified responsibilities of FF-A components in memory management transactions involving multiple borrowers</li> <li>Added guidance to enable a Hypervisor signal creation and destruction of VMs to an SP</li> <li>Revised some data structures to make them forwards compatible</li> <li>Added support for reporting execution state of an endpoint through FFA_PARTITION_INFO_GET</li> <li>Miscellaneous clarifications to better describe ABI behaviour and features</li> <li>Relaxed requirements around when the scheduler receiver interrupt is signalled by the SPMC</li> <li>Constrained configuration of a Notification pending interrupt as an SGI or PPI</li> </ul> |

| Date        | Version   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2021/Jul/05 | v1.1 BET0 | <ul> <li>Consolidated guidance on FF-A architecture in chapter 2</li> <li>Removed usage of AArch32 modes with usage of execution states</li> <li>Added concept of logical partitions that could be co-resident with the SPMC or resident in a separate EL but not isolated from the SPMC</li> <li>Replaced terms isolated and non-isolated" partitions with physical and logical partitions where applicable</li> <li>Updated guidance on direct message passing to be used with logical partitions</li> <li>Updated guidance on memory management to accommodate deployment of logical partitions</li> <li>Added more generalised guidance on isolation of DMA capable devices in Section 4.2</li> <li>Extended guidance on memory management to allow a partition to lend memor that it cannot access</li> <li>Reserved value -1 as an invalid memory handle</li> <li>Added guidance on interrupt management in the Secure world</li> <li>Added section on discovery of NS bit usage to allow v1.0 SPs to use the NS bit flag by discovering its presence and requesting this feature</li> <li>Added guidance in FFA_PARITITON_INFO_GET to return the UUIDs and count of partitions in the system.</li> <li>Updated terminology in guidance on interrupt management for consistency and readability</li> <li>Added guidance for notification support without a Hypervisor</li> <li>Replaced RETRY error code with new NO_DATA error code in FFA_NOTIFICATION_INFO_GET</li> <li>Clarified guidance on Delay Schedule Receiver interrupt flag in FFA_NOTIFICATION_SET</li> <li>Updated minor version of the spec to 1</li> <li>Added VM ID field to FFA_RX_ACQUIRE and RELEASE ABIs at NS physical FF-A instance</li> <li>Allowed FFA_SPM_ID_GET to be forwarded by SPMD to SPMC</li> <li>Added VM ID flag to FFA_MSG_SEND2 at NS physical FF-A instance</li> <li>Clarified encoding of information returned by FFA_NOTIFICATION_INFO_GET ABI</li> <li>Clarified that multiple StMM SPs are identified using a single UUID</li> <li>Clarified guidance on SP to OS kernel indirect message passing</li> <li>Restricted usage o</li></ul> |

| 2021/Mar/15 | v1.1 ALP0 | <ul> <li>Added guidance for notifications</li> <li>Added guidance for indirect messaging based upon notifications</li> <li>Extended indirect messaging to the Secure world</li> <li>Generalised guidance on scheduling</li> <li>Clarfied guidance on states of an endpoint execution context</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

- Added guidance on partition runtime models

- Added guidance on interrupt management in the Secure world

- Added guidance on power management

- Added interfaces to discover the ID of the SPMC and SPMD

- Added guidance to specify the security state of a memory region during retrieval

- Added guidance to discover a SEPID

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2020/Jul/24 | REL     | <ul> <li>Language fixes based upon feedback from editorial review</li> <li>Removed reference to PSA from document title</li> <li>Converted document to Arm spec format</li> <li>Converted ffa_init_info C structure into a table</li> <li>Clarified use of Sender ID field in FFA_FRAG_RX/TX</li> <li>Fixed clash in FIDs of FFA_NORMAL_WORLD_RESUME and FFA_MEM_FRAG_RX</li> <li>Clarified use of FFA_MSG_POLL with RX full interrupt</li> <li>Clarified multi-endpoint memory management is an optional feature</li> <li>Clarified how a receiver should request retransmission of a fragmented memory region description</li> <li>Clarified 64-bit registers can be used in direct messaging</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2020/Apr/24 | EAC     | <ul> <li>Replaced occurrences of SPCI with PSA FF-A</li> <li>Added flag to identify other borrowers in a memory retrieve operation</li> <li>Allowed time slicing of memory management operations at Non-secure physical SPCI instance</li> <li>Replaced Cookie with Handle in fragmented and time-sliced memory management operations</li> <li>Added separate ABIs for fragmented memory management operations</li> <li>Allowed multiple retrievals by a Borrower of a memory region</li> <li>Allowed retrieval by Hypervisor of a memory region on behalf of a VM</li> <li>Replaced separate memory transaction descriptors with a single one</li> <li>Removed Write-through attribute to cater for S2FWB</li> <li>Specified coherency requirements for memory zeroing</li> <li>Moved to 64-bit memory Handles</li> <li>Clarifications to existing memory management guidance</li> <li>Made guidance on power management IMPLEMENTATION DEFINED</li> <li>Allowed discovery of minimum buffer size through FFA_FEATURES</li> <li>Changed FFA_VERSION for negotiation of version number between caller and callee</li> <li>Clarified usage and description of FFA_FEATURES</li> <li>Added section on compliance requirements</li> <li>Other errata fixes and language clarifications based on feedback from beta 1</li> </ul> |

| 2019/Dec/20 | beta 1  | <ul> <li>Added ability to pause and resume memory management transactions</li> <li>Restricted indirect messaging to Normal world</li> <li>Reworded guidance on Stream endpoint IDs (SEPIDs)</li> <li>Added ABI to resume Normal world execution after a Secure interrupt</li> <li>Reworded guidance on SPCI instances and Split SPM configuration</li> <li>Added clearer guidance on optional and mandatory interfaces</li> <li>Other errata fixes and language clarifications based on feedback from beta 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2019/Nov/13 | beta 0  | <ul> <li>Replaced some occurrences of ARM with Arm</li> <li>Non-confidential release of beta 0 spec</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2019/Sep/17 | beta 0  | <ul> <li>Added guidance on partition manifest and setup</li> <li>Significant rewrite of section on message passing</li> <li>Added support for multi-component memory management</li> <li>Added new interfaces for RX/TX management and deprecated old interfaces</li> <li>Device reassignment has been removed from the scope of this release</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Date        | Version            | Changes                                                                                                                                                                                                                                                                                              |

|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019/Apr/26 | alpha 3<br>Draft 0 | <ul> <li>Significant rewrite of section on message passing</li> <li>Chapter on scheduling models has been removed</li> <li>Significant rewrite of section on memory management</li> <li>Chapter 5 has become Chapter 10. Its scope has been reduced temporarily due to preceding changes.</li> </ul> |

| 2018/Dec/21 | alpha 2            | <ul> <li>Changed content based on partner feedback since alpha 1</li> <li>There is a clear separation between message passing and scheduling</li> <li>Introduced use of RX/TX buffers to enable message passing</li> </ul>                                                                           |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2023 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349 version 21.0

## **Contents**

# **Arm Firmware Framework for Arm A-profile**

|           | Arm Firmware Framework for Arm A-profile ii Release information ii Non-Confidential Proprietary Notice vii References xiii Feedback xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Document organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 2 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

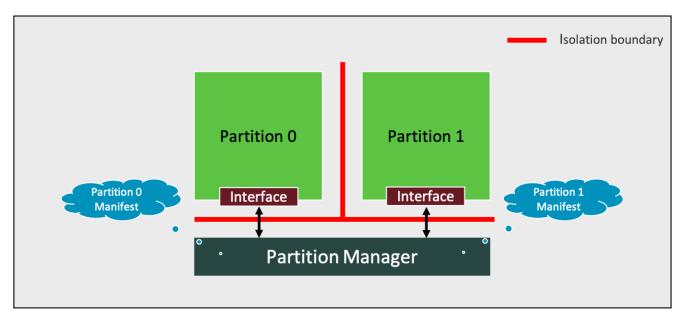

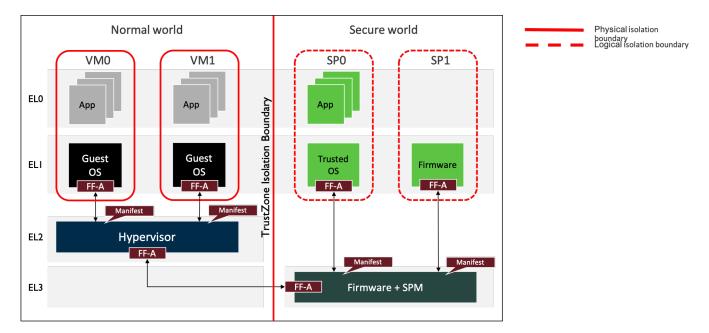

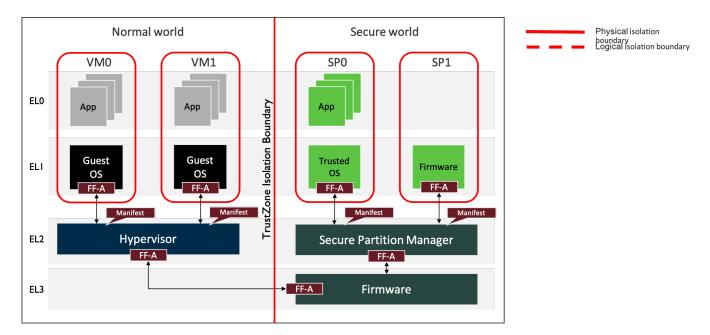

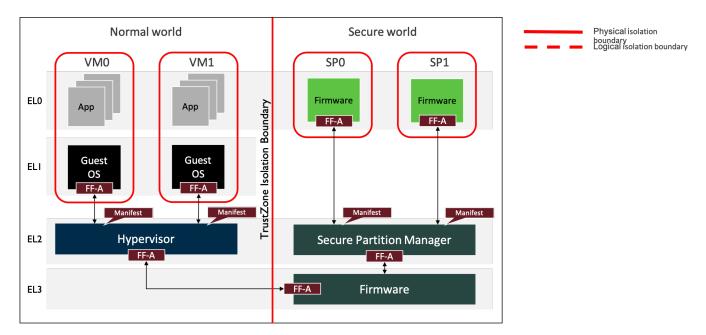

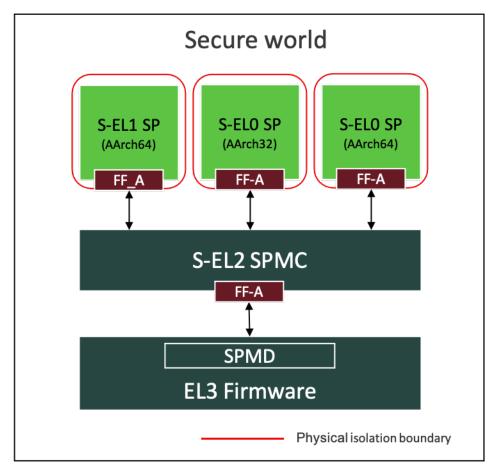

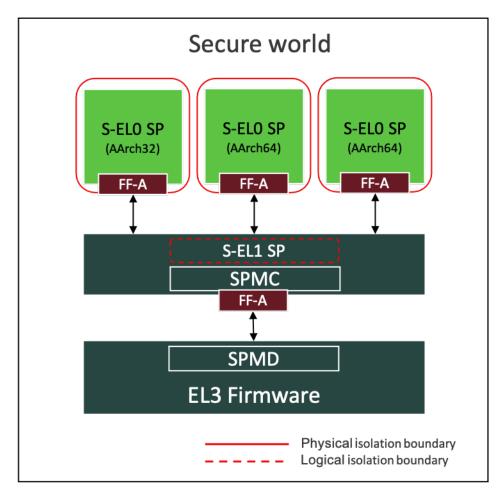

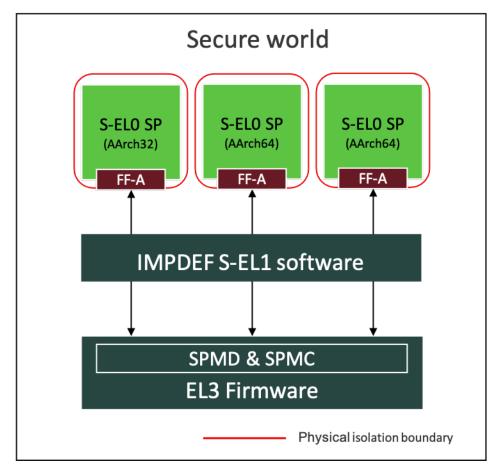

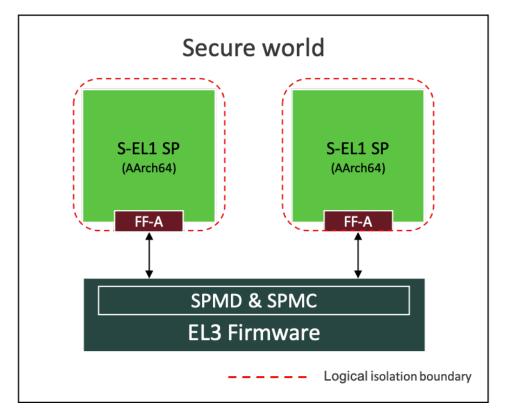

| Chapter 3 | Software architecture         3.1       Isolation boundaries       21         3.2       Partitions       22         3.3       Partition manager       23         3.4       Example configurations       24         3.4.1       FF-A deployment without S-EL2       24         3.4.2       FF-A deployment with S-EL2       25         3.4.3       FF-A deployment with S-EL2 and Armv8.1-VHE       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

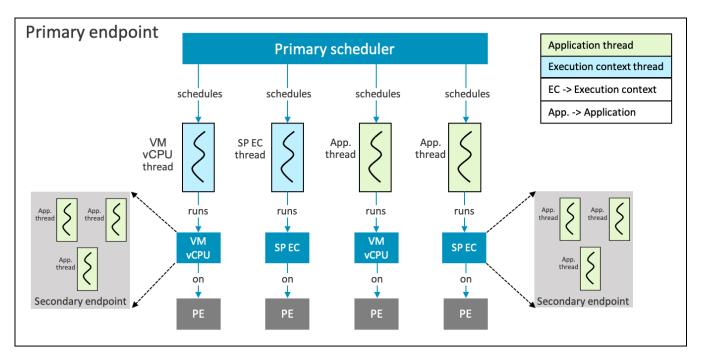

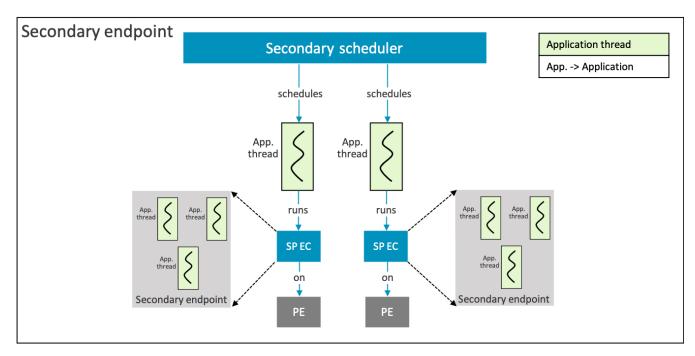

| Chapter 4 | Concepts         4.1       SPM architecture       27         4.1.1       Secure EL2 SPM core component       29         4.1.2       S-EL1 SPM core component       30         4.1.3       EL3 SPM core component       31         4.2       DMA isolation       33         4.2.1       Static DMA isolation       33         4.2.2       Dynamic DMA isolation       34         4.2.3       Other DMA isolation models       35         4.3       FF-A instances       37         4.4       Conduits       39         4.5       Memory types       40         4.6       Memory granularity and alignment       40         4.7       Execution context       41         4.8       System resource management       42         4.9       Primary scheduler       43         4.10       Run-time states       46         4.11       Run-time state transitions       47 |

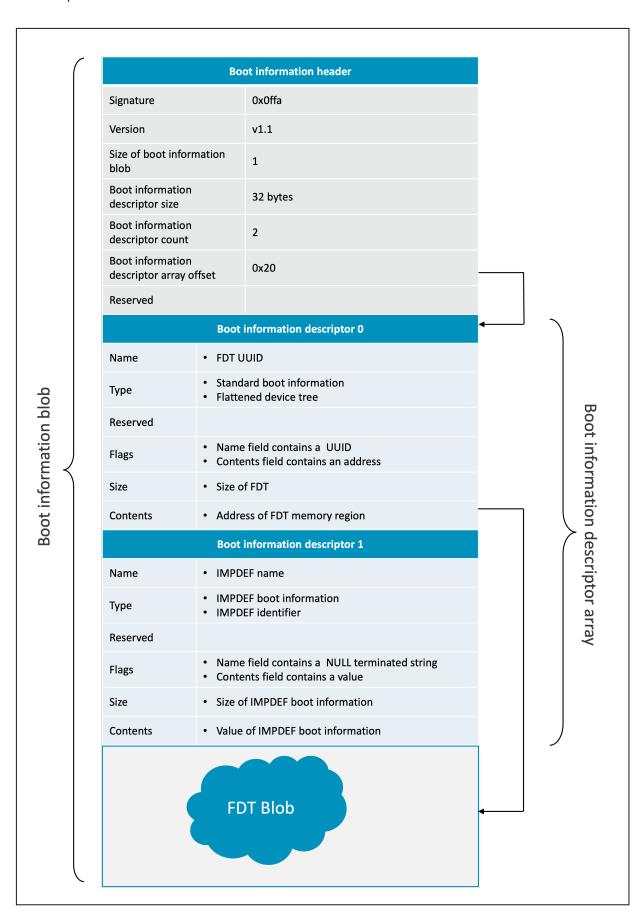

| Chapter 5 | Setup         5.1       Overview       49         5.2       Manifests       51         5.2.1       Partition manifest       51         5.2.2       SPMC manifest       56         5.2.3       Independent peripheral device manifest       57         5.3       Register state       59         5.4       Boot information protocol       60         5.4.1       Boot information descriptor       60         5.4.2       Boot information header       62         5.4.3       Boot information address       66                                                                                                                                                                                                                                                                                                                                                     |

|            | 5.4.4                                                                                                                                                  | boot information memory requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 5.5 Pro                                                                                                                                                | tocol for completing execution context initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Chapter 6  | Idontificati                                                                                                                                           | on and Diagovary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 6  |                                                                                                                                                        | on and Discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |                                                                                                                                                        | tition identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            |                                                                                                                                                        | tition discovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 6.2.1                                                                                                                                                  | Partition information descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 6.2.2                                                                                                                                                  | Partition discovery ABI usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 6.2.3                                                                                                                                                  | Partition UUID usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | 6.3 Pai                                                                                                                                                | tition manager identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 7  | Message p                                                                                                                                              | passing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| •          |                                                                                                                                                        | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

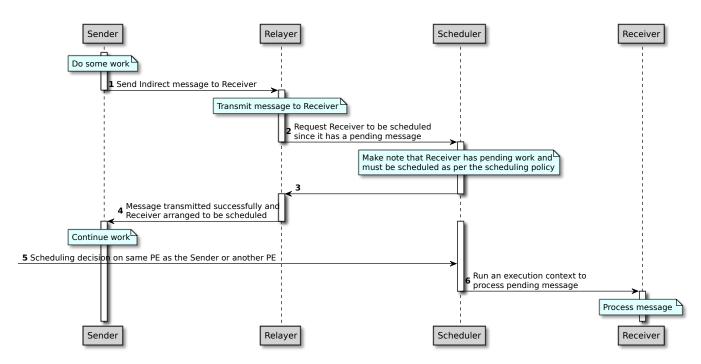

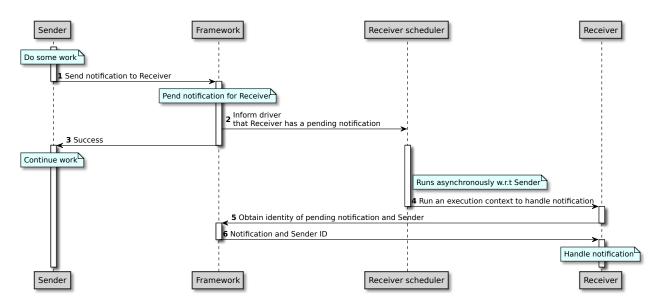

|            | 7.1.1                                                                                                                                                  | Indirect messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

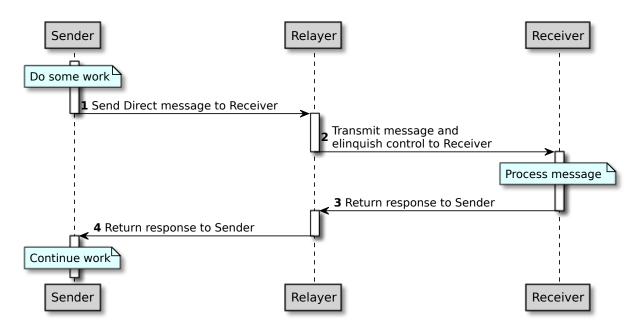

|            | 7.1.2                                                                                                                                                  | Direct messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 7.2 Me                                                                                                                                                 | ssage transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | 7.2.1                                                                                                                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

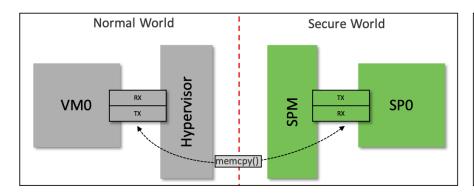

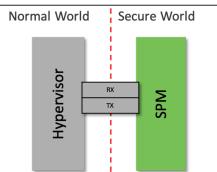

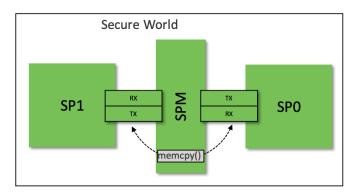

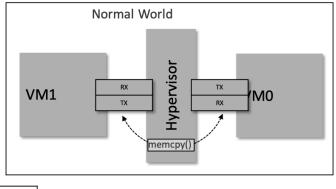

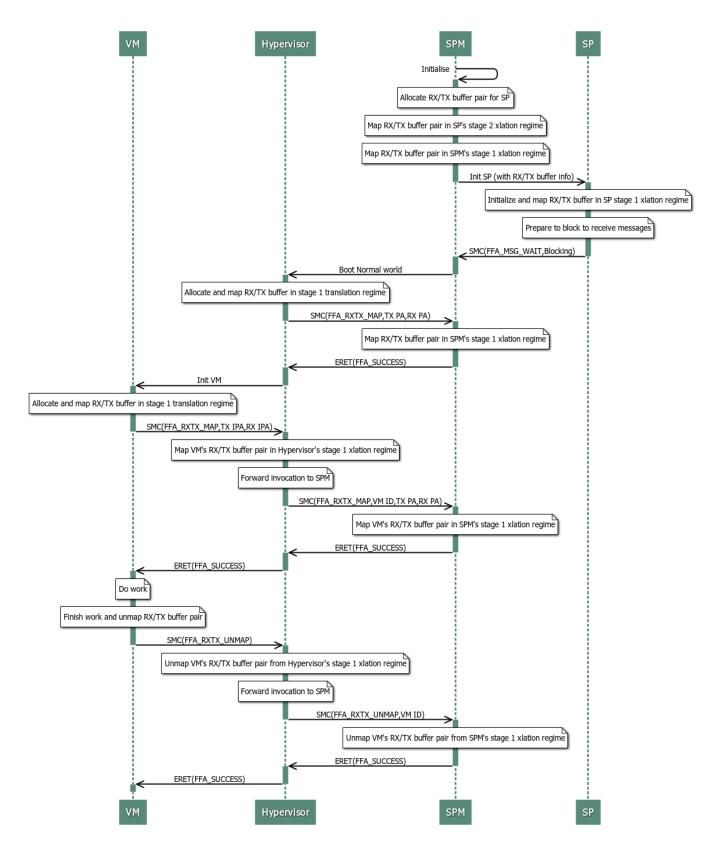

|            | 7.2.2                                                                                                                                                  | RX/TX buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                        | irect messaging usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            | 7.3.1                                                                                                                                                  | Discovery and setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | 7.3.2                                                                                                                                                  | Message delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 7.3.3                                                                                                                                                  | Scheduling the Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

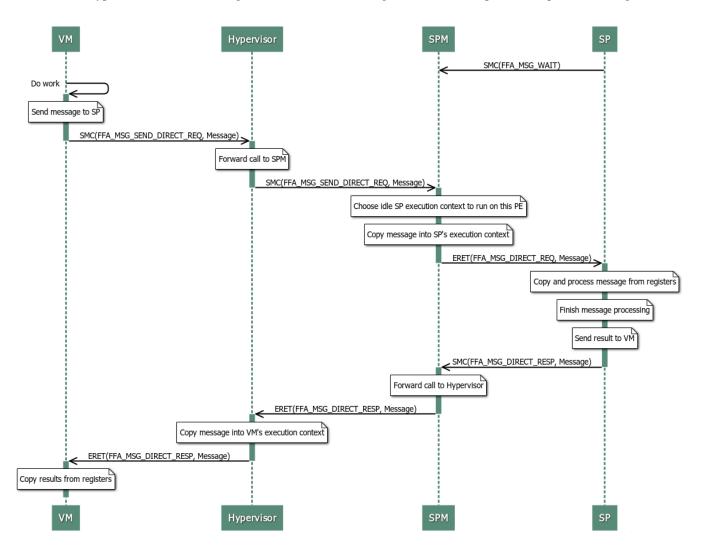

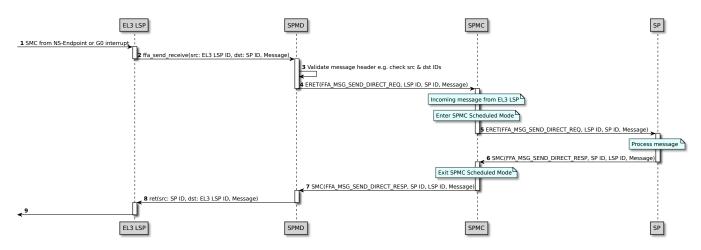

|            |                                                                                                                                                        | ect messaging usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | 7.4.1                                                                                                                                                  | Discovery and setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | 7.4.2                                                                                                                                                  | Message delivery and Receiver execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            |                                                                                                                                                        | mpliance requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            | 7.5.1                                                                                                                                                  | Compliance requirements for Direct messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 7.5.2                                                                                                                                                  | Compliance requirements for Indirect messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | 7.5.2                                                                                                                                                  | Compliance requirements for maneer messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter 8  | Partition ru                                                                                                                                           | untime models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | 8.1 Ov                                                                                                                                                 | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

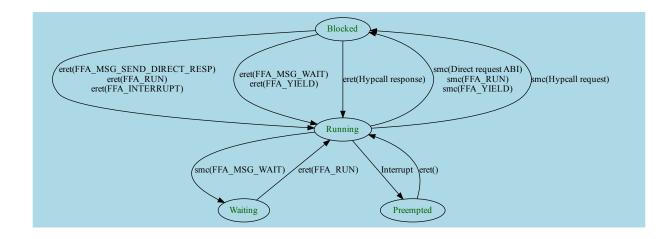

|            | 8.2 Ru                                                                                                                                                 | ntime model for FFA_RUN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

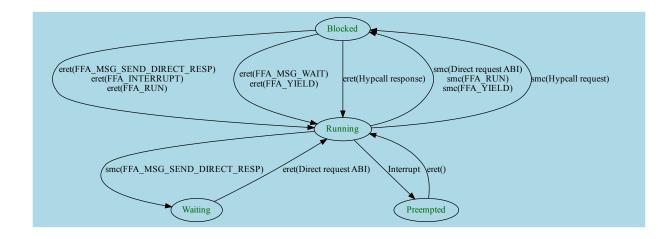

|            | 8.3 Ru                                                                                                                                                 | ntime model for Direct request ABIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

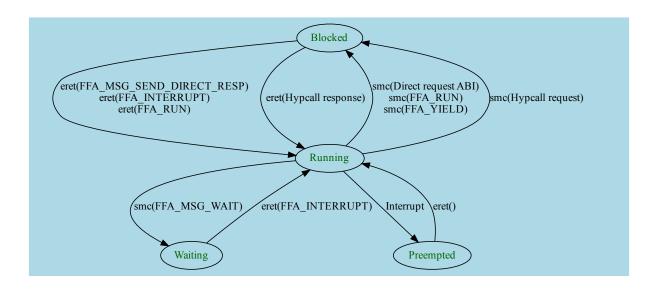

|            | 8.4 Ru                                                                                                                                                 | ntime model for Secure interrupt handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

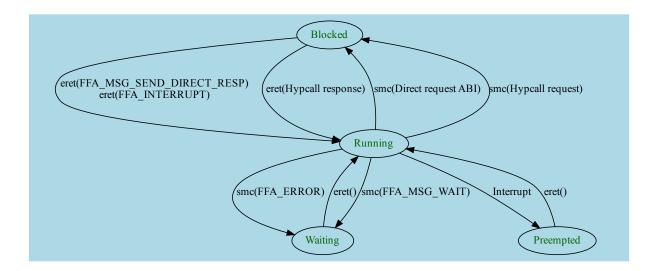

|            | 8.5 Ru                                                                                                                                                 | ntime model for SP initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chamtar 0  |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 9  | Intourint m                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | Interrupt n                                                                                                                                            | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 9.1 Ov                                                                                                                                                 | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | 9.1 Ove<br>9.2 Co                                                                                                                                      | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1                                                                                                                              | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2                                                                                                                     | Priview         104           Incepts         106           Secure interrupt signaling mechanisms         106           Physical interrupt types         108                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3                                                                                                            | Proview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | 9.1 Ove<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4                                                                                                  | rerview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy                                                                                        | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1                                                                               | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

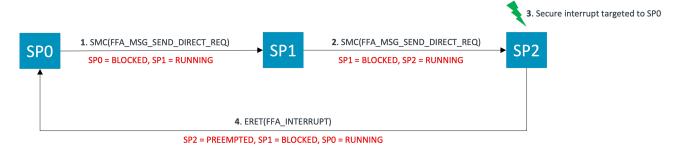

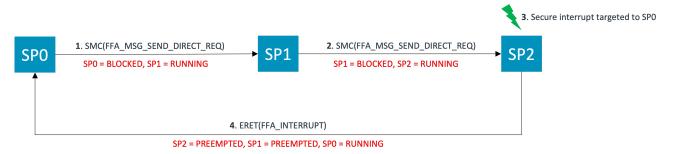

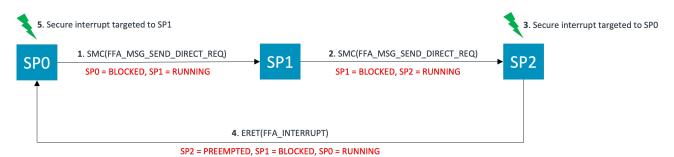

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1<br>9.3.2                                                                      | erview       104         ncepts       106         Secure interrupt signaling mechanisms       106         Physical interrupt types       108         CPU cycle allocation modes       109         SP call chains       110         /sical interrupt actions       112         Actions for a Non-secure interrupt       112         Actions for a Secure interrupt       122                                                                                                                                                                                                                                                              |

|            | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1<br>9.3.2                                                                      | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chapter 10 | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1<br>9.3.2<br>9.4 Sup                                                           | rerview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 10 | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1<br>9.3.2<br>9.4 Su                                                            | rerview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 10 | 9.1 Ov. 9.2 Co 9.2.1 9.2.2 9.2.3 9.2.4 9.3 Phy 9.3.1 9.3.2 9.4 Su  Notificatio 10.1 Ov.                                                                | rerview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 10 | 9.1 Ov<br>9.2 Co<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.3 Phy<br>9.3.1<br>9.3.2<br>9.4 Sul<br><b>Notificatio</b><br>10.1 Ov<br>10.1.1                | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |