arm

# Arm<sup>®</sup> Generic Interrupt **Controller Architecture** Specification GIC architecture version 5

| Document number            | ARM-AES-0070            |

|----------------------------|-------------------------|

| Document quality           | BET                     |

| Document version           | 00bet0                  |

| Document confidentiality   | Non-confidential        |

| Document build information | 0b7a9f48 doctool 0.55.1 |

Copyright © 2022-2025 Arm Limited or its affiliates. All rights reserved.

# Arm® Generic Interrupt Controller Architecture Specification, GIC architecture version 5

### **Release information**

| Date        | Version | Changes              |  |

|-------------|---------|----------------------|--|

| 2025/Mar/28 | 00bet0  | • First BET release. |  |

## **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Copyright © 2022-2025 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

PRE-20349

8 March 2024

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is at Beta quality. Beta quality means that all major features of the specification are described, but some details might be missing.

#### Web Address

https://www.arm.com

# Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 5

|           | Arm® Generic Interrupt Controller Architecture Specification, GIC architecture version 5       ii         Release information       iii         Non-Confidential Proprietary Notice       iii                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | Conventions       xvi         Typographical conventions       xvi         Numbers       xvi         Pseudocode descriptions       xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | Assembler syntax descriptions       xvi         Rules-based writing       xvii         Content item identifiers       xvii         Content item rendering       xvii         Content item classes       xvii                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | Additional reading       xviii         Feedback       xviii         Feedback on this book       xx         Inclusive terminology commitment       xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

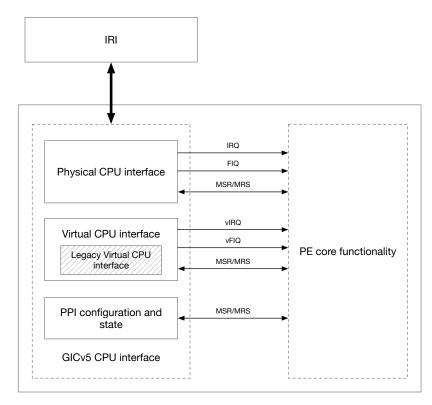

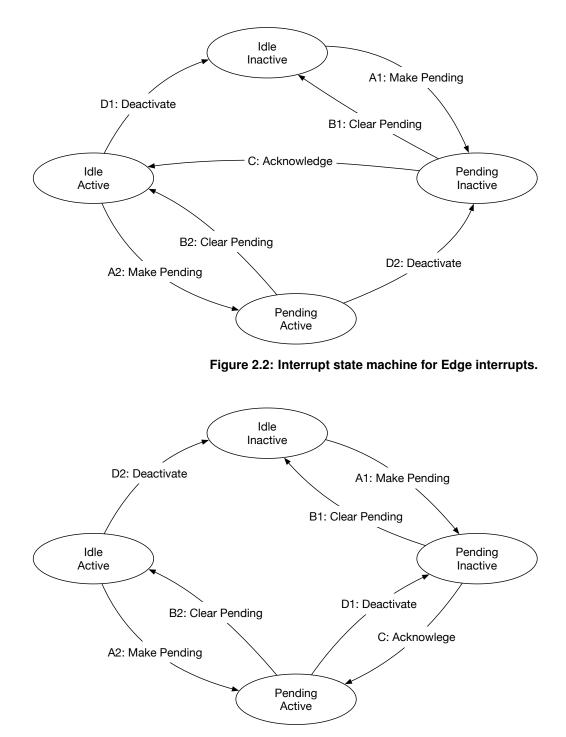

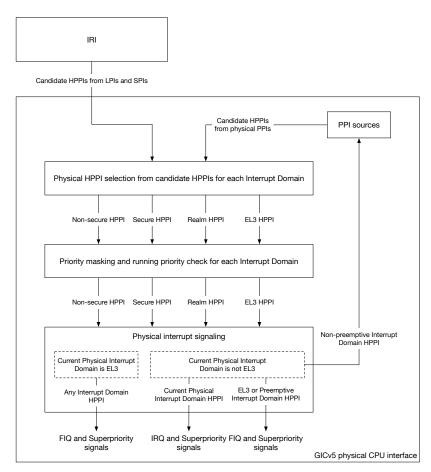

| Chapter 2 | PE architecture         2.1       Architecture features and extensions       23         2.2       The GICv5 CPU interface       25         2.3       Interrupt Domains       27         2.4       Interrupt types and identifiers       29         2.4.1       PE-Private Peripheral Interrupts (PPIs)       30         2.4.2       Logical Peripheral Interrupts (LPIs)       31         2.5       Inter-Processor Interrupts       33         2.6       GIC System instructions       35         2.6.1       LPI and SPI configuration       37         2.7       Interrupt Prioritization       40         2.8       Interrupt handling       42 |

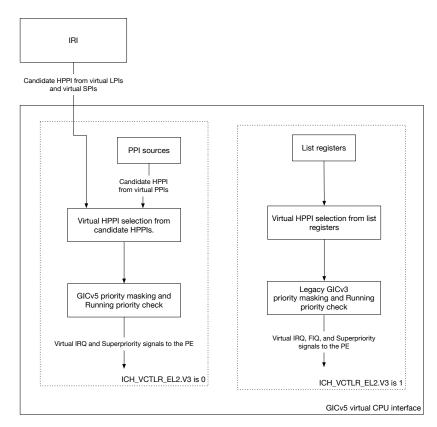

|           | 2.8Interrupt life cycle432.9The physical CPU interface462.9.1Physical PPIs462.9.2Physical priority masking482.9.3Preemptive interrupts492.9.4Physical interrupt signaling502.9.5Physical non-maskable interrupts522.9.6Doorbell PPIs532.10The virtual CPU interface562.10.1Virtual priority masking592.10.3Virtual interrupt signaling602.10.4Virtual non-maskable interrupts62                                                                                                                                                                                                                                                                     |

|           | 2.10.5 Selecting the resident VPE                              | 62  |

|-----------|----------------------------------------------------------------|-----|

|           | 2.10.6 Requesting VPE doorbells                                | 64  |

|           | 2.10.7 Legacy virtual CPU interface                            | 64  |

|           | 2.11 GIC synchronous exception priorities                      | 67  |

|           | 2.12 Interrupt ordering model and synchronization requirements | 68  |

|           | 2.12.1 GIC and GICR ordering semantics                         | 69  |

|           | 2.12.2 GSB instruction semantics                               | 71  |

|           | 2.12.3 GIC Ordering Model                                      | 71  |

|           | 2.13 Effects on the Transactional Memory Extension             | 76  |

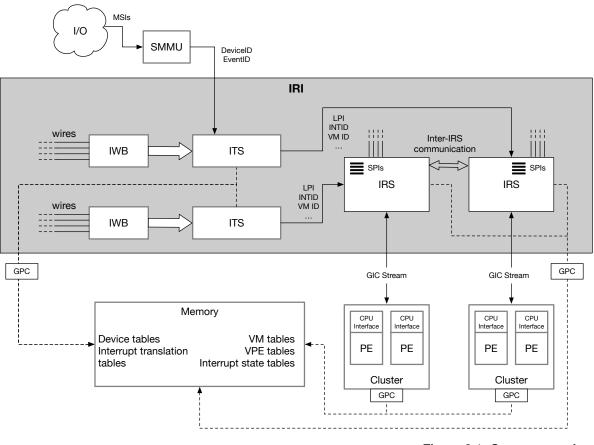

| Chapter 3 | GICv5 system architecture                                      |     |

|           | 3.1 Interrupt Domains                                          | 81  |

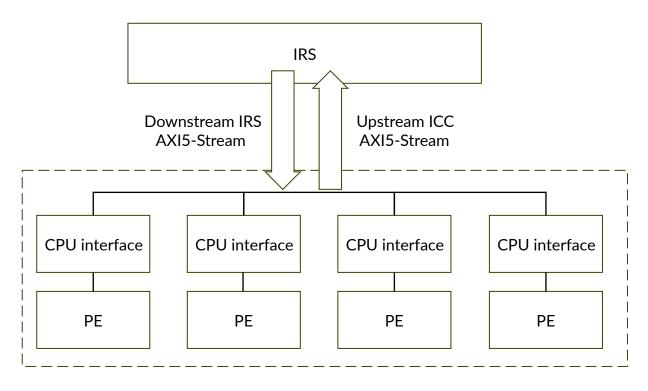

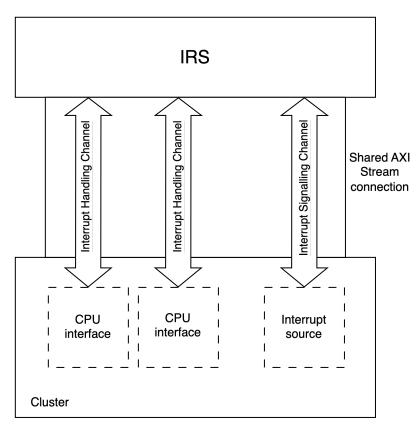

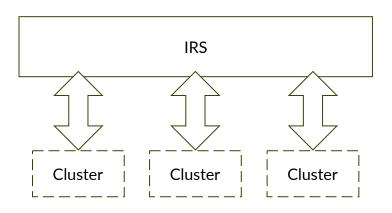

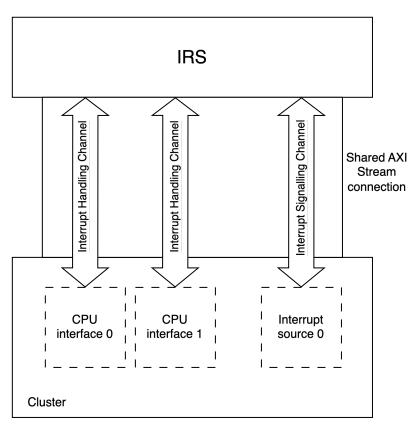

|           | 3.2 Communication between GIC system components                | 83  |

|           | 3.3 Coherency considerations for GIC data structures           | 84  |

| Chapter 4 | Interrupt routing service (IRS)                                |     |

|           | 4.1 Communication between the IRS and the CPU interface        | 87  |

|           | 4.2 Signaling interrupts                                       | 88  |

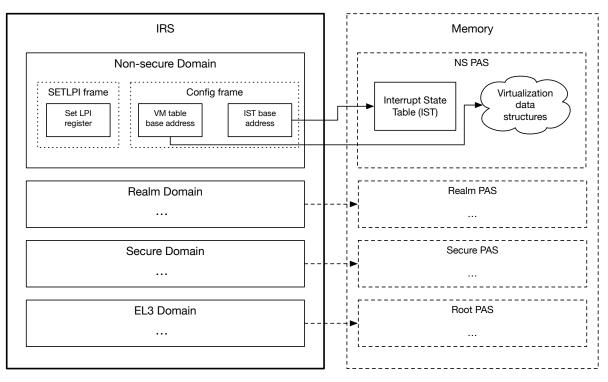

|           | 4.3 IRS Domains                                                | 90  |

|           | 4.4 IRS Configuration                                          | 92  |

|           | 4.4.1 Enabling and disabling the IRS                           | 94  |

|           | 4.5 IRS synchronization requests                               | 95  |

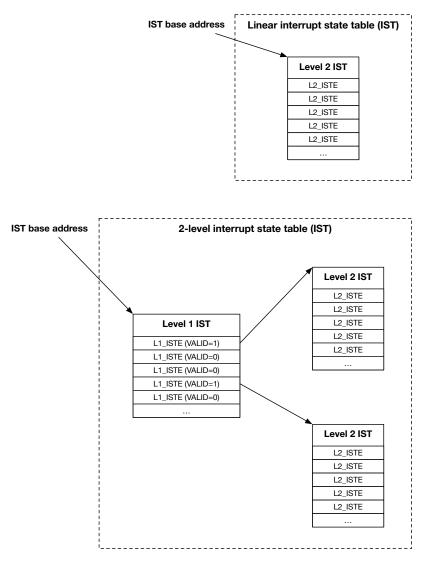

|           | 4.6 Interrupt configuration and state                          | 97  |

|           | 4.7 The interrupt state table (IST)                            | 99  |

|           |                                                                | 101 |

|           | 4.7.2 Initialization of level 2 IST entries                    | 103 |

|           | 4.7.3 INTID state and configuration                            | 103 |

|           |                                                                | 104 |

|           | 4.7.5 Example IST structures                                   | 105 |

|           | ·                                                              | 107 |

|           | 4.8.1 Physical LPIs                                            | 107 |

|           | 4.8.2 Physical SPIs                                            | 108 |

|           | 4.8.3 Physical interrupt routing                               | 112 |

|           | 4.8.4 Physical interrupt signaling                             | 114 |

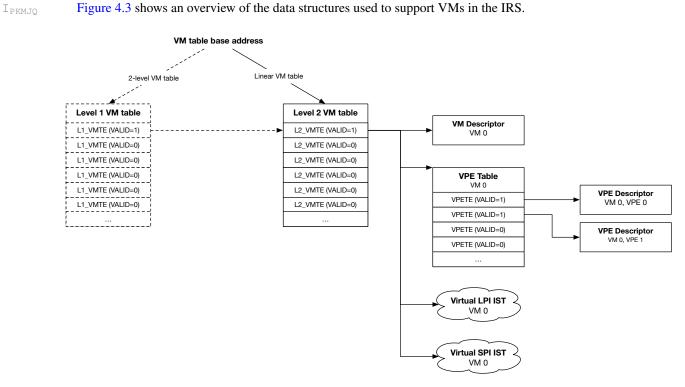

|           | 4.9 Virtualization data structures                             | 116 |

|           | 4.9.1 The VM table                                             | 117 |

|           | 4.9.2 The VPE table                                            | 122 |

|           | 4.10 Virtual interrupts                                        | 126 |

|           | 4.10.1 Virtual LPIs                                            | 126 |

|           | 4.10.2 Virtual SPIs                                            | 129 |

|           | 4.10.3 Virtual interrupt routing                               | 132 |

|           | 4.10.4 Virtual interrupt signaling                             | 133 |

|           | 4.10.5 VPE selection and configuration                         | 135 |

|           | 4.10.6 VPE residency                                           |     |

|           | 4.10.7 VPE doorbells                                           |     |

|           | 4.10.8 1ofN doorbells                                          | 138 |

|           | 4.10.9 Save and restore of virtual interrupts                  | 138 |

|           | 4.11 IRS power management                                      |     |

|           | 4.12 IRS memory access rules                                   |     |

|           | 4.13 IRS support for MPAM                                      | 146 |

|           | 4.14 IRS support for Memory Encryption Contexts                |     |

|           | 4.15 IRS support for software error reporting                  | 149 |

| Chapter 5 | Interrupt translation service (ITS)                            |     |

|           | 5.1 ITS Domains                                                | 155 |

|           |                                                                |     |

|           | 5.1.1       Supporting Realm interrupts from Non-secure writes       15         5.2       Operation       15         5.2.1       Enabling and disabling the ITS       15         5.2.2       Interrupt event types       15         5.2.3       Software generated ITS events       15         5.2.4       ITS synchronization requests       16         5.3       Translation structures       16         5.3.1       The Device Table (DT)       16         5.3.2       The Interrupt Translation Table (ITT)       16         5.4.1       ITS cache management       16         5.4.2       ITS cache management for EventIDs       16         5.4.1       ITS cache management for DeviceIDs       16         5.4.2       ITS cache management for DeviceIDs       16         5.5       ITS memory access rules       17         5.6       ITS support for MPAM       17         5.7       ITS support for Memory Encryption Contexts       17                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 5.8 ITS support for software error reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter 6 | Interrupt Wire Bridge (IWB)         6.1       IWB wire control registers       18         6.2       IWB support for multiple Interrupt Domains       18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 7 | GIC Performance Monitoring Unit (PMU)7.1CoreSight PMU extensions187.2GIC PMU Overflow interrupt187.3GIC PMU event types197.4Event filtering197.5IRS PMU events197.6.1ITS PMU events filtering197.6.1ITS PMU events filtering19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Chapter 8 | System instructions         8.1       System instructions for the Current Interrupt Domain       19         8.1.1       GIC CDAFF, Interrupt Set Target in the Current Interrupt Domain       20         8.1.2       GIC CDDI, Interrupt Deactivate in the Current Interrupt Domain       20         8.1.3       GIC CDDIS, Interrupt Deactivate in the Current Interrupt Domain       20         8.1.4       GIC CDEN, Interrupt Disable in the Current Interrupt Domain       20         8.1.5       GIC CDEOI, Priority Drop in the Current Interrupt Domain       20         8.1.6       GIC CDHM, Interrupt Handling mode state in the Current Interrupt Domain       20         8.1.6       GIC CDPEND, Interrupt Set/Clear Pending state in the Current Interrupt Domain       21         8.1.7       GIC CDPRI, Interrupt Set priority in the Current Interrupt Domain       21         8.1.8       GIC CDPRI, Interrupt Set priority in the Current Interrupt Domain       21         8.1.9       GIC CDRCFG, Request Interrupt Configuration in the Current Interrupt Domain       21         8.1.10       GICR CDIA, Interrupt Acknowledge in the Current Interrupt Domain       21         8.1.11       GICR CDNMIA, Non-maskable Interrupt Acknowledge in the Current Interrupt Domain       22         8.2       System instructions for the Virtual Interrupt Domain       22 |

|           | 8.2.1       GIC VDAFF, Interrupt Set Target in the Virtual Interrupt Domain       22         8.2.2       GIC VDDI, Interrupt Deactivate in the Virtual Interrupt Domain       22         8.2.3       GIC VDDIS, Interrupt Disable in the Virtual Interrupt Domain       22         8.2.4       GIC VDEN, Interrupt Enable in the Virtual Interrupt Domain       22         8.2.5       GIC VDHM, Interrupt Handling mode in the Virtual Interrupt Domain       23         8.2.6       GIC VDPEND, Interrupt Set/Clear Pending state in the Virtual Interrupt Domain       23         2.6       GIC VDPEND, Interrupt Set/Clear Pending state in the Virtual Interrupt Domain       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |     | 8.2.7<br>8.2.8 | GIC VDPRI, Interrupt Set priority in the Virtual Interrupt Domain GIC VDRCFG, Request Interrupt Configuration in the Virtual Interrupt Domain |              |

|-----------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|           | 8.3 | Syster         | m instructions for the Logical Interrupt Domain                                                                                               |              |

|           | 0.0 | 8.3.1          | GIC LDAFF, Interrupt Set Target in the Logical Interrupt Domain                                                                               |              |

|           |     | 8.3.2          | GIC LDDI, Interrupt Deactivate in the Logical Interrupt Domain                                                                                |              |

|           |     | 8.3.3          | GIC LDDIS, Interrupt Disable in the Logical Interrupt Domain                                                                                  |              |

|           |     | 8.3.4          | GIC LDEN, Interrupt Enable in the Logical Interrupt Domain                                                                                    |              |

|           |     | 8.3.4<br>8.3.5 | GIC LDHM, Interrupt Handling mode in the Logical Interrupt Domain                                                                             |              |

|           |     |                |                                                                                                                                               | 240          |

|           |     | 8.3.6          | GIC LDPEND, Interrupt Set/Clear Pending state in the Logical Interrupt Domain                                                                 | 250          |

|           |     | 8.3.7          | GIC LDPRI, Interrupt Set priority in the Logical Interrupt Domain                                                                             |              |

|           |     | 8.3.8          | GIC LDRCFG, Request Interrupt Configuration in the Logical Interrupt                                                                          |              |

|           |     |                | Domain                                                                                                                                        |              |

|           | 8.4 |                | ynchronization barrier instructions                                                                                                           |              |

|           |     | 8.4.1          | GSB SYS, GIC Synchronization Barrier System                                                                                                   |              |

|           |     | 8.4.2          | GSB ACK, GIC Synchronization Barrier Interrupt Acknowledge                                                                                    | 258          |

| Chapter 9 |     | tem regis      |                                                                                                                                               |              |

|           | 9.1 |                | rronization requirements for GICv5 System registers                                                                                           |              |

|           | 9.2 |                | nterface registers                                                                                                                            |              |

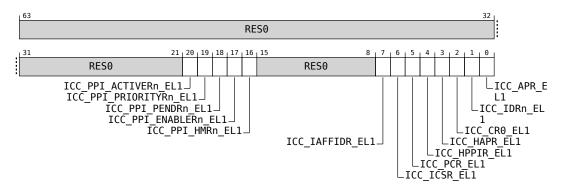

|           |     | 9.2.1          | ICC_APR_EL1, Interrupt Controller Physical Active Priorities Register .                                                                       | 262          |

|           |     | 9.2.2          | ICC_APR_EL3, Interrupt Controller Physical Active Priorities Register                                                                         |              |

|           |     |                | for EL3                                                                                                                                       |              |

|           |     | 9.2.3          | ICC_CR0_EL1, Interrupt Controller EL1 Physical Control Register                                                                               |              |

|           |     | 9.2.4          | ICC_CR0_EL3, Interrupt Controller EL3 Physical Control Register                                                                               | 271          |

|           |     | 9.2.5          | ICC_DOMHPPIR_EL3, Interrupt Controller Domain Highest Priority                                                                                |              |

|           |     |                | Pending Interrupt Register                                                                                                                    | 273          |

|           |     | 9.2.6          | ICC_HAPR_EL1, Interrupt Controller Physical Highest Active Priority                                                                           |              |

|           |     |                | Register                                                                                                                                      | 275          |

|           |     | 9.2.7          | ICC HPPIR EL1, Interrupt Controller Physical Highest Priority Pending                                                                         |              |

|           |     |                | Interrupt Register                                                                                                                            | 277          |

|           |     | 9.2.8          | ICC HPPIR EL3, Interrupt Controller Physical Highest Priority Pending                                                                         |              |

|           |     |                | Interrupt Register                                                                                                                            | 279          |

|           |     | 9.2.9          | ICC IAFFIDR EL1, Interrupt Controller PE Interrupt Affinity ID Register                                                                       |              |

|           |     | 9.2.10         | ICC ICSR EL1, Interrupt Controller Interrupt Configuration and State                                                                          | 201          |

|           |     | 0.2.10         | Register                                                                                                                                      | 282          |

|           |     | 9.2.11         | ICC IDR0 EL1, Interrupt Controller ID Register 0                                                                                              | 286          |

|           |     | 9.2.12         | ICC PCR EL1, Interrupt Controller Physical Interrupt Priority Control                                                                         | 200          |

|           |     | 9.2.12         |                                                                                                                                               | 000          |

|           |     | 0.0.10         | Register                                                                                                                                      | 200          |

|           |     | 9.2.13         |                                                                                                                                               | 001          |

|           |     | 0.0.14         | for EL3                                                                                                                                       |              |

|           |     | 9.2.14         | ID_AA64PFR2_EL1, AArch64 Processor Feature Register 2                                                                                         |              |

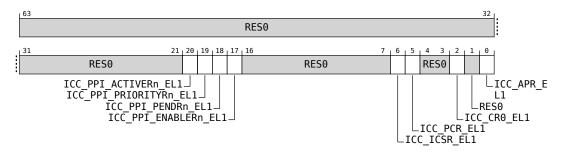

|           | 9.3 |                | I CPU interface registers                                                                                                                     |              |

|           |     | 9.3.1          | ICV_APR_EL1, Interrupt Controller Virtual Active Priorities Register                                                                          |              |

|           |     | 9.3.2          | ICV_CR0_EL1, Interrupt Controller EL1 Virtual Control Register                                                                                | 299          |

|           |     | 9.3.3          | ICV_HAPR_EL1, Interrupt Controller Virtual Highest Active Priority Reg-<br>ister                                                              | 302          |

|           |     | 9.3.4          | ICV HPPIR EL1, Interrupt Controller Virtual Highest Priority Pending                                                                          | 002          |

|           |     | 5.5.4          | Interrupt Register                                                                                                                            | 304          |

|           |     | 025            | ICV PCR EL1, Interrupt Controller Virtual Interrupt Priority Control                                                                          | 504          |

|           |     | 9.3.5          |                                                                                                                                               | 200          |

|           | 0.4 | יי וסס         |                                                                                                                                               |              |

|           | 9.4 |                |                                                                                                                                               | 309          |

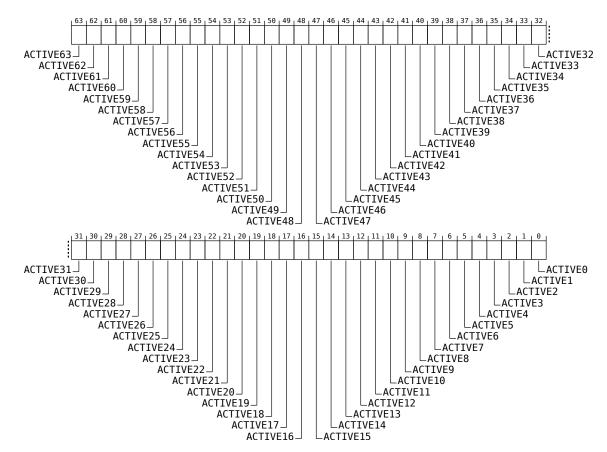

|           |     | 9.4.1          | ICC_PPI_CACTIVER <n>_EL1, Interrupt Controller Physical PPI Clear</n>                                                                         | <b>a</b> · - |

|           |     |                | Active Registers, n = 0 - 1                                                                                                                   | 310          |

|     | 9.4.2   | ICC_PPI_CPENDR <n>_EL1, Interrupt Controller Physical PPI Clear<br/>Pending State Registers, n = 0 - 1</n> | 313        |

|-----|---------|------------------------------------------------------------------------------------------------------------|------------|

|     | 9.4.3   | ICC_PPI_DOMAINR <n>_EL3, Interrupt Controller PPI Domain Registers, n = 0 - 3</n>                          | 316        |

|     | 9.4.4   | ICC_PPI_ENABLER <n>_EL1, Interrupt Controller Physical PPI Enable<br/>Registers, n = 0 - 1</n>             | 318        |

|     | 9.4.5   | ICC_PPI_HMR <n>_EL1, Interrupt Controller Physical PPI Handling mode Registers, n = 0 - 1</n>              | 321        |

|     | 9.4.6   | ICC_PPI_PRIORITYR <n>_EL1, Interrupt Controller Physical PPI Priority<br/>Registers, n = 0 - 15</n>        | 323        |

|     | 9.4.7   | ICC_PPI_SACTIVER <n>_EL1, Interrupt Controller Physical PPI Set</n>                                        |            |

|     | 9.4.8   | Active Registers, n = 0 - 1                                                                                | 325<br>328 |

| 9.5 | Virtual | PPI registers                                                                                              | 331        |

| 5.5 | 9.5.1   | ICV PPI CACTIVER <n> EL1, Interrupt Controller Virtual PPI Clear</n>                                       | 001        |

|     | 9.5.1   | Active Registers, $n = 0 - 1$                                                                              | 332        |

|     | 0 5 0   |                                                                                                            | 332        |

|     | 9.5.2   | ICV_PPI_CPENDR <n>_EL1, Interrupt Controller Virtual PPI Clear Pend-</n>                                   | 005        |

|     | 9.5.3   | ing State Registers, n = 0 - 1                                                                             | 335        |

|     |         | able Registers, n = 0 - 1                                                                                  | 338        |

|     | 9.5.4   | ICV PPI HMR <n> EL1, Interrupt Controller Virtual PPI Handling mode</n>                                    |            |

|     |         | Registers, $n = 0 - 1$                                                                                     | 341        |

|     | 9.5.5   | ICV PPI PRIORITYR <n> EL1, Interrupt Controller Virtual PPI Priority</n>                                   | 011        |

|     | 5.5.5   | Registers, $n = 0 - 15$                                                                                    | 343        |

|     | 9.5.6   | ICV_PPI_SACTIVER <n>_EL1, Interrupt Controller Virtual PPI Set Active</n>                                  | 343        |

|     | 9.5.6   | Registers, n = 0 - 1                                                                                       | 345        |

|     | 9.5.7   | ICV_PPI_SPENDR <n>_EL1, Interrupt Controller Virtual PPI Set Pend-</n>                                     |            |

|     |         | ing State Registers, n = 0 - 1                                                                             | 348        |

| 9.6 | Hyper   | visor control registers                                                                                    | 351        |

|     | 9.6.1   | ICH APR EL2, Interrupt Controller Active Virtual Priorities Register                                       |            |

|     | 9.6.2   | ICH CONTEXTR EL2, Interrupt Controller Virtual Context Register                                            | 354        |

|     | 9.6.3   | ICH HFGITR EL2, Hypervisor GIC Fine-Grained Instruction Trap Registe                                       |            |

|     | 9.6.4   | ICH HFGRTR EL2, Hypervisor GIC Fine-Grained Read Trap Register                                             | 363        |

|     |         |                                                                                                            |            |

|     | 9.6.5   | ICH_HFGWTR_EL2, Hypervisor GIC Fine-Grained Write Trap Register                                            | 369        |

|     | 9.6.6   | ICH_HPPIR_EL2, Interrupt Controller Hypervisor Highest Priority Pend-                                      |            |

|     |         | ing Interrupt Register                                                                                     | 374        |

|     | 9.6.7   | ICH_PPI_ACTIVER <n>_EL2, Interrupt Controller Virtual Interrupt Active</n>                                 |            |

|     |         | Registers, $n = 0 - 1$                                                                                     | 376        |

|     | 9.6.8   | ICH_PPI_DVIR <n>_EL2, Interrupt Controller PPI Direct-inject Virtual</n>                                   |            |

|     |         | Interrupt Registers, $n = 0 - 1$                                                                           | 379        |

|     | 9.6.9   | ICH_PPI_ENABLER <n>_EL2, Interrupt Controller Virtual Interrupt En-</n>                                    |            |

|     | / -     | able Registers, n = 0 - 1                                                                                  | 382        |

|     | 9.6.10  | ICH_PPI_PENDR <n>_EL2, Interrupt Controller Virtual Interrupt Pending<br/>State Registers, n = 0 - 1</n>   | 384        |

|     | 9.6.11  | ICH PPI PRIORITYR <n> EL2, Interrupt Controller Virtual Interrupt</n>                                      |            |

|     | 0.0     | Priority Registers, $n = 0 - 15$                                                                           | 386        |

|     | 9.6.12  | ICH_VCTLR_EL2, Interrupt Controller Virtual CPU interface Control                                          | 000        |

|     |         | Register                                                                                                   | 388        |

|     | 9.6.13  | ICH_VMCR_EL2, Interrupt Controller Virtual Machine Control Register                                        | 391        |

|     | 9.6.14  | Nested virtualization                                                                                      | 393        |

| 9.7 | Legac   |                                                                                                            |            |

|     | 9.7.1   | ICH AP0R <n> EL2, Interrupt Controller Active Virtual Priorities Regis-</n>                                |            |

|     | ·       | ters 0, n = 0 - 3                                                                                          | 396        |

|     |         |                                                                                                            |            |

|                |              | 9.7.2     | ICH_AP1R <n>_EL2, Interrupt Controller Active Virtual Priorities Regis-</n> |

|----------------|--------------|-----------|-----------------------------------------------------------------------------|

|                |              |           | ters 1, n = 0 - 3                                                           |

|                |              | 9.7.3     | ICH_EISR_EL2, Interrupt Controller End of Interrupt Status Register 401     |

|                |              | 9.7.4     | ICH_ELRSR_EL2, Interrupt Controller Empty List Register Status Register403  |

|                |              | 9.7.5     | ICH_HCR_EL2, Interrupt Controller Hyp Control Register                      |

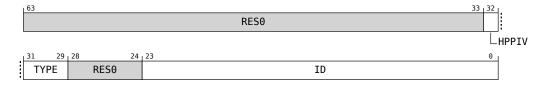

|                |              | 9.7.6     | ICH_LR <n>_EL2, Interrupt Controller List Registers, n = 0 - 15 409</n>     |

|                |              | 9.7.7     | ICH MISR EL2, Interrupt Controller Maintenance Interrupt State Register412  |

|                |              | 9.7.8     | ICH_VTR_EL2, Interrupt Controller VGIC Type Register                        |

|                |              | 9.7.9     | Nested virtualization                                                       |

|                | 9.8          |           | cy virtual CPU interface registers                                          |

|                | 0.0          | 9.8.1     | AArch64 Legacy virtual CPU interface registers                              |

|                |              | 0.0.1     |                                                                             |

| Chapter 10     | Reg          | isters a  | nd memory maps                                                              |

|                | 10.1         | Mem       | ory-mapped programmer's model                                               |

|                | 10.2         | IRS I     | register frames                                                             |

|                |              | 10.2.1    | IRS_CONFIG_FRAME, IRS configuration register frame                          |

|                |              | 10.2.2    | IRS SETLPI FRAME, IRS SETLPI register frame                                 |

|                | 10.3         |           | egister frames                                                              |

|                |              | 10.3.1    | ITS_CONFIG_FRAME, ITS configuration register frame                          |

|                |              | 10.3.2    | ITS TRANSLATE FRAME, ITS translate register frame                           |

|                | 10.4         |           | register frames                                                             |

|                | 10.4         | 10.4.1    | IWB_CONFIG_FRAME, IWB configuration registers frame                         |

|                | 10.5         |           | PMU register frame                                                          |

|                | 10.5         |           |                                                                             |

|                | 10.6         | 10.5.1    | GIC_PMU_FRAME, GIC PMU register frame                                       |

|                | 10.6         | laem      |                                                                             |

| Chapter 11     | Data         | a structu | Ires                                                                        |

| •              | 11.1         |           | Data Structures                                                             |

|                |              | 11.1.1    | L1_DTE, Level 1 device table entry                                          |

|                |              | 11.1.2    | L2_DTE, Level 2 device table entry                                          |

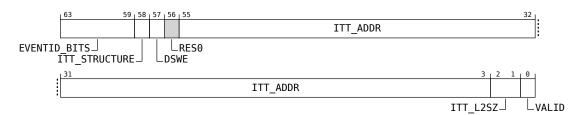

|                |              | 11.1.3    | L1_ITTE, Level 1 interrupt translation table entry                          |

|                |              | 11.1.4    | L2_ITTE, Level 2 interrupt translation table entry                          |

|                | 11.2         |           |                                                                             |

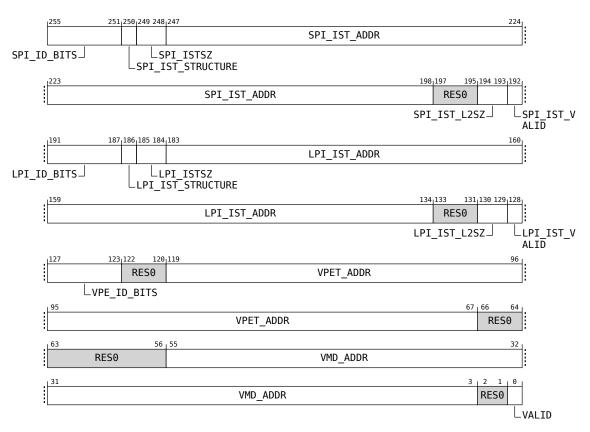

|                | 11.2         | 11.2.1    |                                                                             |

|                |              |           | L1_VMTE, Level 1 VM table entry                                             |

|                |              | 11.2.2    | L2_VMTE, Level 2 VM table entry                                             |

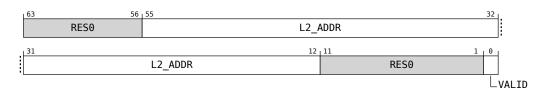

|                |              | 11.2.3    | L1_ISTE, Level 1 interrupt state table entry                                |

|                |              | 11.2.4    | L2_ISTE, Level 2 interrupt state table entry                                |

|                |              | 11.2.5    | VPETE, VPE table entry                                                      |

|                |              | 11.2.6    | VM_DESC, VM descriptor                                                      |

|                |              | 11.2.7    | VPE_DESC, VPE descriptor                                                    |

|                |              |           |                                                                             |

| Part A GICv5 S | trear        | n Prote   | ocol interface                                                              |

|                |              |           |                                                                             |

| Chapter A1     | GIC          | v5 Strea  | m Protocol overview                                                         |

| Chapter A2     | AME          | BA AXI5   | -Stream Transport Layer                                                     |

|                | A2.1         |           | als                                                                         |

|                | A2.2         |           | nel identification                                                          |

|                | A2.3         |           | status                                                                      |

|                | 712.0        | Link      | 510105                                                                      |

| Chapter A3     | Com          | nmon be   | ehaviors                                                                    |

| Chapter A4     | Inter        | rrupt Ha  | Indling channel                                                             |

|                | A4.1         |           | mand summary                                                                |

|                | A4.1<br>A4.2 |           | tanding commands                                                            |

|                | A4.2         | Outs      | Lanung commanus                                                             |

|                |              |           |                                                                             |

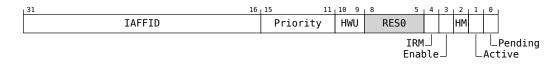

|            | A4.3<br>A4.4<br>A4.5<br>A4.6<br>A4.7 | Mana<br>A4.4.1<br>A4.4.2<br>Forwa<br>INTID | ection management                                                                                                              | 657<br>657<br>658<br>659<br>661 |

|------------|--------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Chapter A5 | Inter                                | rupt Sig                                   | Inaling channel                                                                                                                |                                 |

| •          | A5.1                                 |                                            | nand summary                                                                                                                   | 664                             |

|            | A5.2                                 |                                            | anding commands                                                                                                                |                                 |

|            | A5.3                                 | Signa                                      | ling interrupts to the IRS                                                                                                     | 666                             |

|            | A5.4                                 | Conn                                       | ection management                                                                                                              | 667                             |

| Chapter A6 | Alph                                 | abetica                                    | l list of commands                                                                                                             |                                 |

|            | A6.1                                 | Interr                                     | upt Handling channel                                                                                                           |                                 |

|            |                                      | A6.1.1                                     | Activate, Activate command (CPUIF -> IRS)                                                                                      |                                 |

|            |                                      | A6.1.2                                     | ActivateAck, Activate Acknowledge command (IRS -> CPUIF)                                                                       |                                 |

|            |                                      | A6.1.3                                     | Deactivate, Deactivate interrupt command (CPUIF -> IRS)                                                                        | 672                             |

|            |                                      | A6.1.4                                     | DeactivateAck, Deactivate interrupt Acknowledge command (IRS ->                                                                | 674                             |

|            |                                      | A6.1.5                                     | CPUIF)                                                                                                                         |                                 |

|            |                                      | A6.1.6                                     | DownstreamControlAck, Downstream Control Acknowledge command                                                                   | 075                             |

|            |                                      | / 10/ 110                                  | (CPUIF -> IRS)                                                                                                                 | 676                             |

|            |                                      | A6.1.7                                     | Forward, Forward command (IRS -> CPUIF)                                                                                        |                                 |

|            |                                      | A6.1.8                                     | Recall, Recall command (IRS -> CPUIF)                                                                                          |                                 |

|            |                                      | A6.1.9                                     | Release, Release command (CPUIF -> IRS)                                                                                        |                                 |

|            |                                      | A6.1.10                                    | RequestConfig, Request Interrupt Configuration command (CPUIF -> IRS                                                           | 682(                            |

|            |                                      | A6.1.11                                    | RequestConfigAck, Request Interrupt Configuration Acknowledge com-<br>mand (IRS -> CPUIF)                                      | 684                             |

|            |                                      | A6.1.12                                    | SetAck, Set interrupt configuration acknowledge command (IRS -> CPUIF                                                          |                                 |

|            |                                      | A6.1.13                                    | SetEnabled, Set interrupt Enabled command (CPUIF -> IRS)                                                                       |                                 |

|            |                                      | A6.1.14                                    | SetHandling, Set Interrupt Handling Mode command (CPUIF -> IRS) .                                                              |                                 |

|            |                                      | A6.1.15                                    | SetPending, Set interrupt Pending command (CPUIF -> IRS)                                                                       |                                 |

|            |                                      | A6.1.16                                    | SetPriority, Set Interrupt Priority command (CPUIF -> IRS)                                                                     |                                 |

|            |                                      | A6.1.17                                    | SetResident, Set Resident command (CPUIF -> IRS)                                                                               |                                 |

|            |                                      | A6.1.18                                    | SetResidentAck, Set Resident acknowledge command (IRS -> CPUIF)                                                                |                                 |

|            |                                      | A6.1.19<br>A6.1.20                         | SetTarget, Set Interrupt Target command (CPUIF -> IRS) Sync, synchronizes previously sent configuration changes (CPUIF -> IRS) |                                 |

|            |                                      | A6.1.21                                    | SyncAck, synchronizes previously sent configuration changes (OF OF 2 inter-                                                    | ,,,00                           |

|            |                                      |                                            | CPUIF)                                                                                                                         | 701                             |

|            |                                      | A6.1.22                                    | UpstreamControl, Upstream Control (CPUIF -> IRS)                                                                               |                                 |

|            |                                      | A6.1.23                                    | UpstreamControlAck, Upstream Control Acknowledge command (IRS -> CPUIF)                                                        |                                 |

|            |                                      | A6.1.24                                    | WakeRequest, Wake request (IRS -> CPUIF)                                                                                       |                                 |

|            | A6.2                                 |                                            | upt Signaling channel                                                                                                          |                                 |

|            |                                      | A6.2.1                                     | INT, Interrupt command (Interrupt Source -> IRS)                                                                               |                                 |

|            |                                      | A6.2.2                                     | Flush, Flush command (IRS -> Interrupt Source)                                                                                 |                                 |

|            |                                      | A6.2.3                                     | FlushAck, Flush acknowledge command (Interrupt Source -> IRS)                                                                  |                                 |

|            |                                      | A6.2.4                                     | Quiesce, Quiesce command (Interrupt Source -> IRS)                                                                             |                                 |

|            |                                      | A6.2.5                                     | QuiesceAck, Quiesce acknowledge command (IRS -> Interrupt Source)                                                              |                                 |

|            |                                      | A6.2.6                                     | Resample, Resample request command (IRS -> Interrupt Source)                                                                   | 711                             |

|            |                                      | A6.2.7                                     | ResampleAck, Resample request acknowledge command (Interrupt                                                                   | 740                             |

|            |                                      | A6.2.8                                     | Source -> IRS)                                                                                                                 |                                 |

#### A6.2.9 ResetAck, Reset acknowledge command (IRS -> Interrupt Source) . . . 714

## Chapter A7 Example sequences

| A7.1 | • | Bringing the Interrupt Handling channel online and taking it offline     | 16 |  |  |  |  |  |  |

|------|---|--------------------------------------------------------------------------|----|--|--|--|--|--|--|

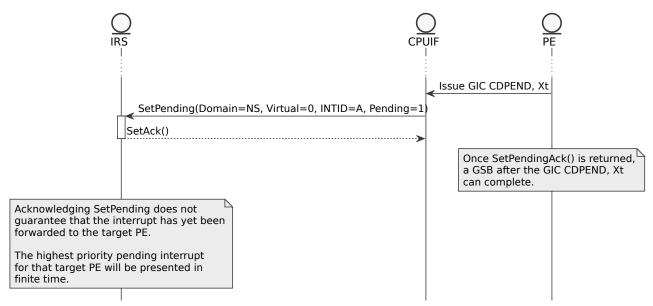

| A7.2 |   | Simple interrupt life-cycle                                              |    |  |  |  |  |  |  |

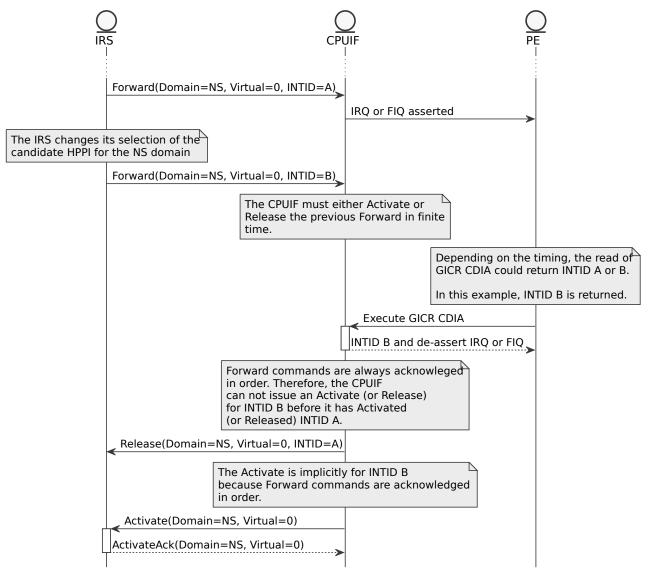

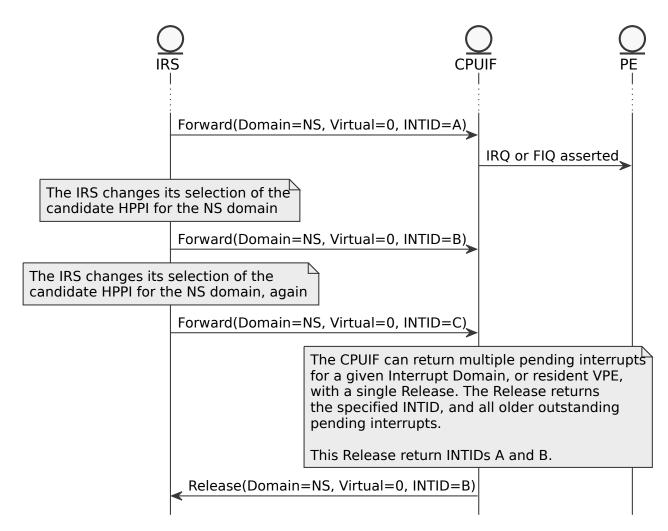

| A7.3 |   | Replacing the candidate HPPI for an Interrupt Domain, or resident VPE 72 | 22 |  |  |  |  |  |  |

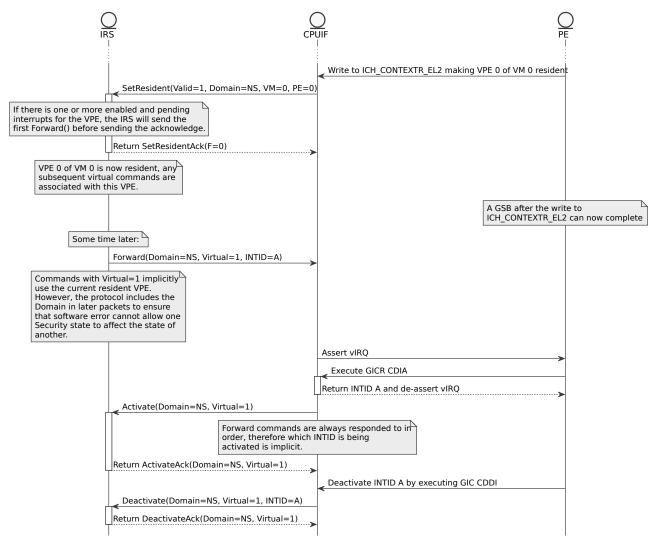

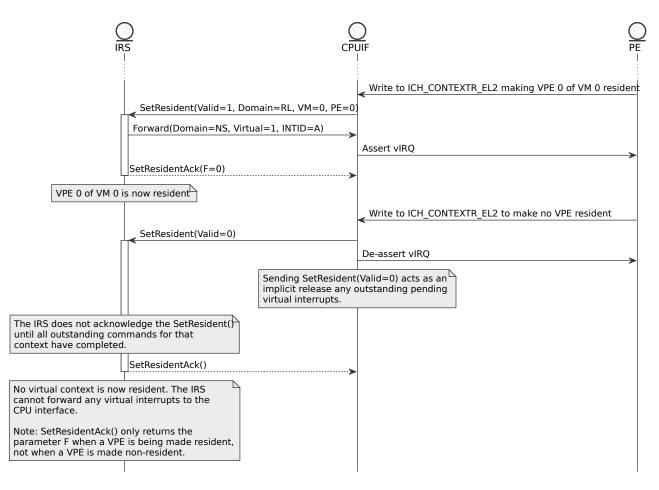

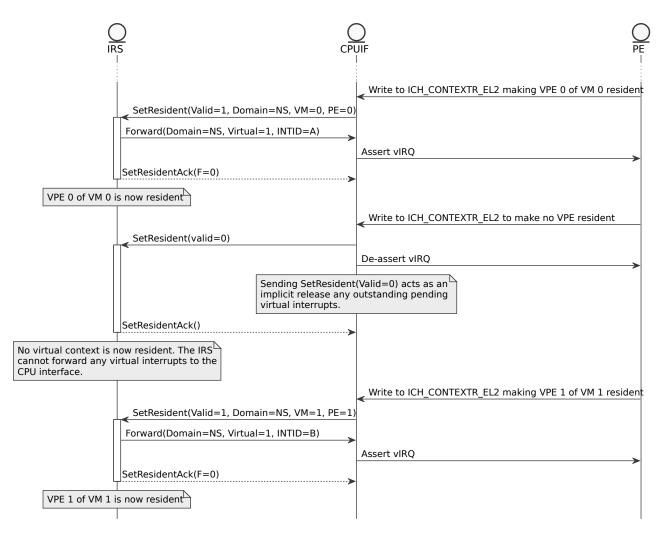

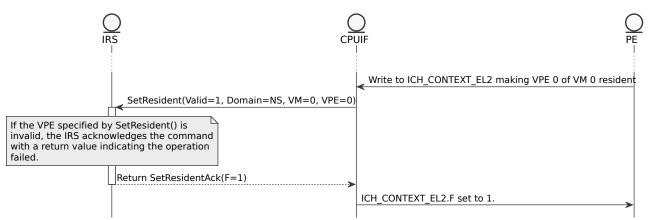

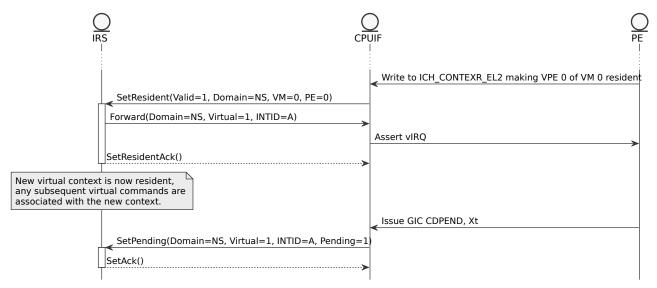

| A7.4 |   | Making a VPE resident                                                    | 25 |  |  |  |  |  |  |

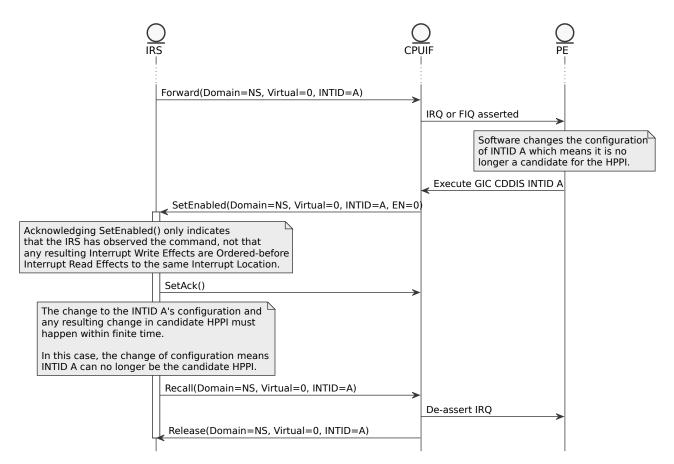

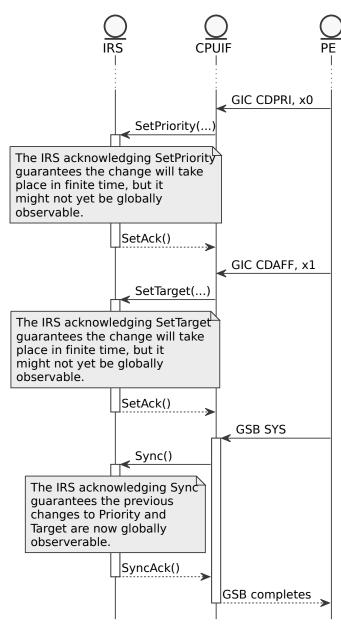

| A7.5 |   | Interrupt configuration                                                  | 28 |  |  |  |  |  |  |

| A7.6 |   | Sending IPIs                                                             | 29 |  |  |  |  |  |  |

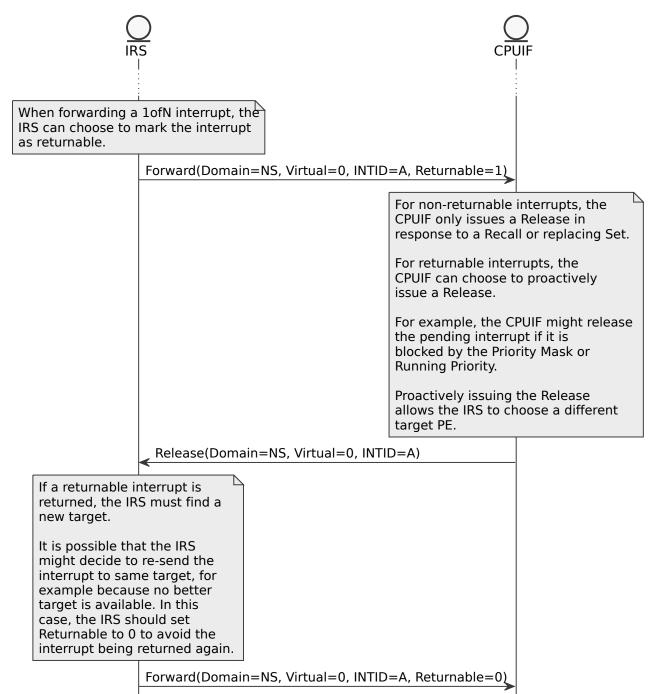

| A7.7 |   | 1 of N interrupts                                                        | 30 |  |  |  |  |  |  |

## Part B Litmus tests

| Chapter B1 | Inter | rrupt ord | dering litmus tests                                                   |

|------------|-------|-----------|-----------------------------------------------------------------------|

|            | B1.1  |           | upt litmus test assumptions                                           |

|            | B1.2  | Atom      | icity of interrupt updates by GIC system instructions                 |

|            |       | B1.2.1    | Notes                                                                 |

|            |       | B1.2.2    | Litmus test                                                           |

|            | B1.3  | Multip    | ble updates of the same Interrupt Location                            |

|            |       | B1.3.1    | Notes                                                                 |

|            |       | B1.3.2    | Litmus test with two configuration updates                            |

|            |       | B1.3.3    | Litmus test with an interrupt disable and an interrupt deactivate 735 |

|            |       | B1.3.4    | Litmus test with an interrupt deactivate and an interrupt disable 736 |

|            | B1.4  | Read      | ling back interrupt writes on a single PE                             |

|            |       | B1.4.1    | Notes                                                                 |

|            |       | B1.4.2    | Litmus test with a configuration update                               |

|            |       | B1.4.3    | Litmus test with deactivate                                           |

|            |       | B1.4.4    | Litmus test with acknowledgement                                      |

|            |       | B1.4.5    | Litmus test with two configuration updates                            |

|            | B1.5  | Read      | ling interrupt configurations and subsequent updates                  |

|            |       | B1.5.1    | Notes                                                                 |

|            |       | B1.5.2    | Litmus test with update to priority                                   |

|            |       | B1.5.3    | Litmus test with deactivate                                           |

|            |       | B1.5.4    | Litmus test with acknowledge                                          |

|            | B1.6  | Confi     | guration and acknowledgement                                          |

|            |       | B1.6.1    | Notes                                                                 |

|            |       | B1.6.2    | Litmus test using disable without explicit synchronization            |

|            |       | B1.6.3    | Litmus test using disable with explicit synchronization               |

|            |       | B1.6.4    | Litmus test with deactivate                                           |

|            |       | B1.6.5    | Litmus test using priority without explicit synchronization           |

|            |       | B1.6.6    | Litmus test using priority with explicit synchronization              |

|            | B1.7  | Ackno     | owledge followed by interrupt changes                                 |

|            |       | B1.7.1    | Notes                                                                 |

|            |       | B1.7.2    | Litmus test with deactivate                                           |

|            |       | B1.7.3    | Litmus test with make pending                                         |

|            | B1.8  | Multip    | ble updates with interleaved read                                     |

|            |       | B1.8.1    | Notes                                                                 |

|            |       | B1.8.2    | Litmus test                                                           |

|            | B1.9  | Confi     | guration write and IRQ unmask in PSTATE                               |

|            |       | B1.9.1    | Notes                                                                 |

|            |       | B1.9.2    | Litmus test                                                           |

|            |       | B1.9.3    | Litmus test with initially masked IRQs                                |

|            |       | B1.9.4    | Litmus test with disable of a PPI                                     |

|            | B1.10 | ) Confi   | guration write and exception status on a single PE                    |

|            |       |           |                                                                       |

| B1.10.1                | Notes                                                     | 750 |

|------------------------|-----------------------------------------------------------|-----|

| B1.10.2                | Litmus test without wait for IRQ exception to be signaled |     |

| B1.10.3                | Litmus test with wait for IRQ exception to be signaled    |     |

|                        | nd acknowledgement                                        |     |

| B1.11.1                | Notes                                                     |     |

| B1.11.2                | Litmus test without explicit synchronization              |     |

| B1.11.3                | Litmus test with explicit synchronization                 |     |

|                        | erving multiple writes on a different PE                  |     |

| B1.12.1                | Notes                                                     |     |

| B1.12.2                |                                                           |     |

|                        | I of the configuration of an interrupt                    |     |

| B1.13.1                | Notes                                                     |     |

| B1.13.2                |                                                           |     |

| B1.13.2                |                                                           |     |

|                        | ple reads of the same config                              |     |

| B1.14 Mulu             |                                                           |     |

| B1.14.1<br>B1.14.2     |                                                           |     |

|                        |                                                           |     |

|                        |                                                           |     |

| B1.15.1                |                                                           |     |

| B1.15.2                |                                                           |     |

|                        | bendent reads of independent writes                       |     |

| B1.16.1                | Notes                                                     |     |

| B1.16.2                |                                                           |     |

|                        | sage passing via flag in memory                           |     |

| B1.17.1                | Notes                                                     |     |

| B1.17.2                | Litmus test                                               |     |

|                        | sage passing via interrupt priority configuration         |     |

| B1.18.1                | Notes                                                     |     |

| B1.18.2                | Litmus test                                               |     |

| B1.19 Mess             | age passing with an LPI and a device read                 | 763 |

| B1.19.1                | Notes                                                     |     |

| B1.19.2                | Litmus test                                               |     |

| B1.19.3                | Litmus test with address dependency                       | 763 |

| B1.20 Mess             | age passing with an LPI and a GSB                         | 765 |

| B1.20.1                | Notes                                                     | 765 |

| B1.20.2                | Litmus test                                               | 765 |

| B1.21 Mess             | age passing with an IPI and a GSB                         | 767 |

| B1.21.1                | Notes                                                     | 767 |

| B1.21.2                | Litmus test                                               | 767 |

| B1.22 Mess             | age passing using deactivate                              | 768 |

| B1.22.1                | Notes                                                     | 768 |

| B1.22.2                | Litmus test with explicit synchronization                 |     |

| B1.22.3                | Litmus test with address dependency                       |     |

| B1.22.4                | Litmus test with control dependency                       |     |

| B1.22.5                | Litmus test without explicit synchronization              |     |

| B1.22.6                | Litmus test with a DSB but without a GSB                  |     |

| B1.22.7                | Litmus test without a DSB but with a GSB                  |     |

|                        | dge merging and message passing                           |     |

| B1.23 B1.23.1          | Notes                                                     |     |

| B1.23.2                |                                                           |     |

| -                      | ce edge merging with GSB ACK                              |     |

| В1.24 Devic<br>B1.24.1 |                                                           |     |

| B1.24.1<br>B1.24.2     |                                                           |     |

|                        | iguration read and interrupt acknowledge                  |     |

|                        |                                                           |     |

| B1.25.1                | Notes                                                     | 111 |

| B1.25.2                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| B1.25.3                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                |

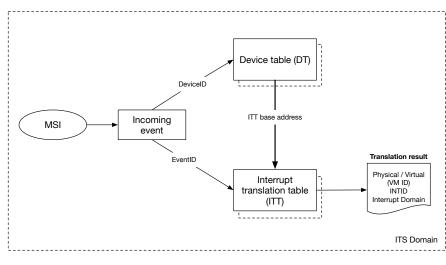

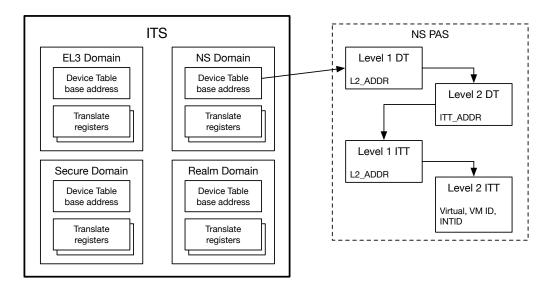

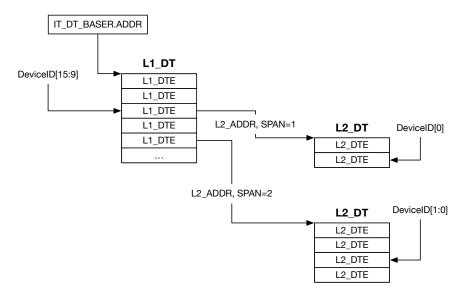

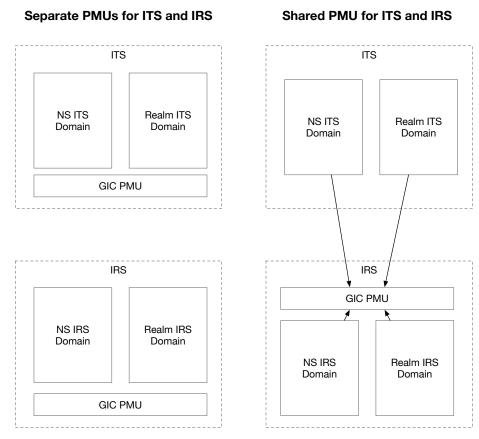

| B1.26 Atom                                                                                                                                              | nicity of interrupt acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                |