# Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification GIC architecture version 3 and version 4

# Arm Generic Interrupt Controller Architecture Specification GIC architecture version 3 and version 4

Copyright © 2008, 2011, 2015-2020 Arm Limited or its affiliates. All rights reserved.

#### Release Information

The following changes have been made to this document.

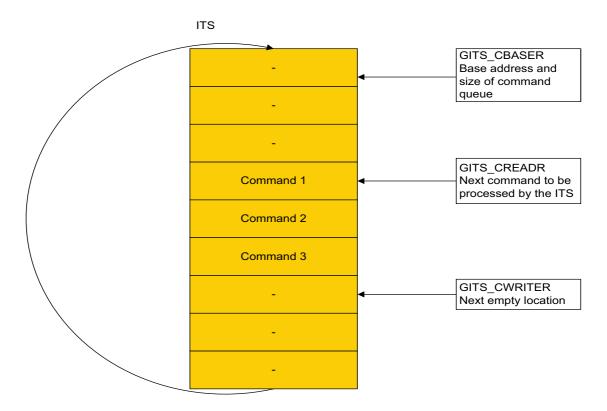

**Change History**

| Date          | Issue | Confidentiality  | Change                                      |

|---------------|-------|------------------|---------------------------------------------|

| June 2015     | A     | Non-confidential | First release of GICv3 and GICv4 issue A.   |

| December 2015 | В     | Non-confidential | First release of GICv3 and GICv4 issue B.   |

| July 2016     | C     | Non-confidential | First release of GICv3 and GICv4 issue C.   |

| August 2017   | D     | Non-confidential | First release of GICv3 and GICv4 issue D.   |

| January 2019  | Е     | Non-confidential | First release of GICv3 and GICv4 issue E.   |

| February 2020 | F     | Non-confidential | First release of GICv3 and GICv4.1 issue F. |

Some of the information in this specification was previously published in Arm\* Generic Interrupt Controller, Architecture version 2.0, Architecture Specification.

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with ARM, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The ARM corporate logo and words marked with ® or TM are registered trademarks or trademarks of ARM Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2008, 2011, 2015-2020 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### **Web Address**

http://www.arm.com

### Contents

## Arm Generic Interrupt Controller Architecture Specification GIC architecture version 3 and version 4

|           |     | Preface                                        |      |

|-----------|-----|------------------------------------------------|------|

|           |     | About this specification                       | x    |

|           |     | Using this specification                       |      |

|           |     | Conventions                                    |      |

|           |     | Additional reading                             | xiii |

|           |     | Feedback                                       |      |

| Chapter 1 |     | Introduction                                   |      |

| •         | 1.1 | About the Generic Interrupt Controller (GIC)   | 1-16 |

|           | 1.2 | Terminology                                    |      |

|           | 1.3 | Supported configurations and compatibility     |      |

| Chapter 2 |     | Distribution and Routing of Interrupts         |      |

| p         | 2.1 | The Distributor and Redistributors             | 2-30 |

|           | 2.2 | INTIDs                                         |      |

|           | 2.3 | Affinity routing                               |      |

| Chapter 3 |     | GIC Partitioning                               |      |

| onaptor o | 3.1 | The GIC logical components                     | 3_38 |

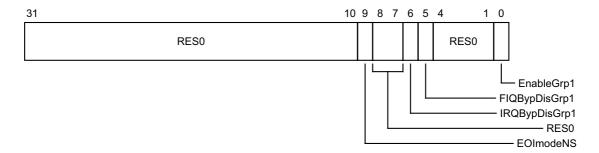

|           | 3.2 | Interrupt bypass support                       |      |

|           | 5.2 | interrupt bypass support                       | 3-40 |

| Chapter 4 |     | Physical Interrupt Handling and Prioritization |      |

|           | 4.1 | Interrupt lifecycle                            | 4-46 |

|           | 4.2 | Locality-specific Peripheral Interrupts        | 4-53 |

|           |     |                                                |      |

|            | 4.3   | Private Peripheral Interrupts                                        | 4-54   |

|------------|-------|----------------------------------------------------------------------|--------|

|            | 4.4   | Software Generated Interrupts                                        |        |

|            | 4.5   | Shared Peripheral Interrupts                                         |        |

|            | 4.6   | Interrupt grouping                                                   |        |

|            | 4.7   | Enabling the distribution of interrupts                              |        |

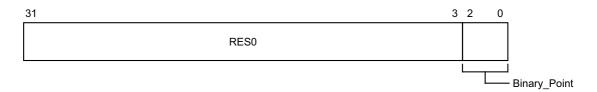

|            | 4.8   | Interrupt prioritization                                             |        |

|            | 1.0   | monapt phonezation                                                   |        |

| Chapter 5  |       | Locality-specific Peripheral Interrupts and the ITS                  |        |

|            | 5.1   | LPIs                                                                 | 5-78   |

|            | 5.2   | The Interrupt Translation Service                                    |        |

|            | 5.3   | ITS commands                                                         |        |

|            | 5.4   | Common ITS pseudocode functions                                      |        |

|            | 5.5   | ITS command error encodings                                          |        |

|            | 5.6   | ITS power management                                                 |        |

|            | 0.0   | Tro power management                                                 | 0 101  |

| Chapter 6  |       | Virtual Interrupt Handling and Prioritization                        |        |

|            | 6.1   | About GIC support for virtualization                                 | 6-154  |

|            | 6.2   | Operation overview                                                   |        |

|            | 6.3   | Configuration and control of VMs                                     |        |

|            | 6.4   | Pseudocode                                                           |        |

|            | 0.4   | 1 30000000                                                           | 0-102  |

| Chapter 7  |       | GICv4.0 Virtual LPI Support                                          |        |

|            | 7.1   | About GICv4.0 virtual Locality-specific Peripheral Interrupt support | 7-166  |

|            | 7.2   | Direct injection of virtual interrupts                               |        |

|            | 7.2   | Direct injection of virtual interrupter                              |        |

| Chapter 8  |       | GICv4.1 Virtual Interrupt Support                                    |        |

| •          | 8.1   | About GICv4.1 virtual interrupt support                              | 8-170  |

|            | 8.2   | Changes to the CPU interface                                         |        |

|            | 8.3   | ITS commands                                                         |        |

|            | 8.4   | vPEID width                                                          |        |

|            | 8.5   | Doorbells                                                            |        |

|            | 8.6   | vPE residency and locating data structures                           |        |

|            |       |                                                                      |        |

|            | 8.7   | Register based vLPI invalidation                                     |        |

|            | 8.8   | Direct injection of vSGIs                                            | 8-1/8  |

| Chapter 9  |       | Memory Partitioning and Monitoring                                   |        |

| Chapter 3  | 0.4   | Overview                                                             | 0.400  |

|            | 9.1   |                                                                      |        |

|            | 9.2   | MPAM and the Redistributors                                          |        |

|            | 9.3   | MPAM and the ITS                                                     |        |

|            | 9.4   | GIC usage of MPAM                                                    |        |

|            | 9.5   | GICv4.1 data structures and MPAM                                     | 9-186  |

| Chapter 10 |       | Power Management                                                     |        |

| Chapter 10 | 10.1  | Power management                                                     | 10_188 |

|            | 10.1  | 1 Ower management                                                    | 10 100 |

| Chapter 11 |       | Programmers' Model                                                   |        |

| •          | 11.1  | About the programmers' model                                         | 11-190 |

|            | 11.2  | AArch64 System register descriptions                                 |        |

|            | 11.3  | AArch64 System register descriptions of the virtual registers        |        |

|            | 11.4  | ·                                                                    |        |

|            |       | AArch64 virtualization control System registers                      |        |

|            | 11.5  | AArch32 System register descriptions                                 |        |

|            | 11.6  | AArch32 System register descriptions of the virtual registers        |        |

|            | 11.7  | AArch32 virtualization control System registers                      |        |

|            | 11.8  | The GIC Distributor register map                                     |        |

|            | 11.9  | The GIC Distributor register descriptions                            |        |

|            | 11.10 | The GIC Redistributor register map                                   |        |

|            | 11.11 | The GIC Redistributor register descriptions                          |        |

|            | 11.12 | The GIC CPU interface register map                                   | 11-670 |

|            | 11.13      | The GIC CPU interface register descriptions                | . 11-671 |

|------------|------------|------------------------------------------------------------|----------|

|            | 11.14      | The GIC virtual CPU interface register map                 | . 11-707 |

|            | 11.15      | The GIC virtual CPU interface register descriptions        | . 11-709 |

|            | 11.16      | The GIC virtual interface control register map             |          |

|            | 11.17      | The GIC virtual interface control register descriptions    | . 11-742 |

|            | 11.18      | The ITS register map                                       | . 11-763 |

|            | 11.19      | The ITS register descriptions                              | . 11-764 |

|            | 11.20      | Pseudocode                                                 | . 11-790 |

| Chapter 12 |            | System Error Reporting                                     |          |

| -          | 12.1       | About System Error reporting                               | . 12-812 |

| Chapter 13 |            | Legacy Operation and Asymmetric Configurations             |          |

| -          | 13.1       | Legacy support of interrupts and asymmetric configurations | . 13-814 |

|            | 13.2       | The asymmetric configuration                               | . 13-818 |

|            | 13.3       | Support for legacy operation of VMs                        | . 13-819 |

| Appendix A |            | GIC Stream Protocol interface                              |          |

|            | A.1        | Overview                                                   | A-822    |

|            | A.2        | Signals and the GIC Stream Protocol                        | A-823    |

|            | A.3        | The GIC Stream Protocol                                    | A-826    |

|            | A.4        | Alphabetic list of command and response packet formats     | A-831    |

| Appendix B |            | Pseudocode Definition                                      |          |

|            | B.1        | About Arm pseudocode                                       | B-850    |

|            | B.2        | Data types                                                 |          |

|            | B.3        | Expressions                                                | B-855    |

|            | B.4        | Operators and built-in functions                           |          |

|            | B.5        | Statements and program structure                           | B-862    |

|            |            |                                                            |          |

|            | B.6        | Pseudocode terminology                                     | B-866    |

|            | B.6<br>B.7 | Pseudocode terminology                                     |          |

Glossary

### **Preface**

This preface introduces the  $Arm^{\oplus}$  Generic Interrupt Controller Architecture Specification. It contains the following sections:

- About this specification on page x.

- Using this specification on page xi.

- Conventions on page xii.

- Additional reading on page xiii.

- Feedback on page xiv.

#### About this specification

This specification describes the *Arm Generic Interrupt Controller* (GIC) architecture. It defines versions 3.0, 3.1 (GICv3), 4.0, and 4.1 (GICv4) of the GIC architecture.

Throughout this document, references to *the GIC* or *a GIC* refer to a device that implements the GIC architecture. Unless the context makes it clear that a reference is to an IMPLEMENTATION DEFINED feature of the device, these references describe the requirements of this specification.

#### Intended audience

This specification is for users who want to design, implement, or program the GIC in a range of Arm-compliant implementations, from simple uniprocessor implementations to complex multiprocessor systems. It does not assume familiarity with previous versions of the GIC.

The specification assumes that users have some experience of Arm products, and are familiar with the terminology that describes the Armv8 architecture. See the *Armv8 Architecture Reference Manual, Armv8, for Armv8-A architecture profile* for more information.

#### Using this specification

This specification is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an overview of the GIC, and information about the terminology that this document uses

#### Chapter 2 Distribution and Routing of Interrupts

Read this for information about how the GIC uses affinity routing to distribute interrupts.

#### Chapter 3 GIC Partitioning

Read this for an overview of the GIC partitioning and information about the GIC logical components.

#### Chapter 4 Physical Interrupt Handling and Prioritization

Read this for information about how the GIC handles physical interrupts.

#### Chapter 5 Locality-specific Peripheral Interrupts and the ITS

Read this for a description of *Locality-specific Peripheral Interrupts* (LPIs) and the use of the *Interrupt Translation Service* (ITS).

#### Chapter 6 Virtual Interrupt Handling and Prioritization

Read this for information about how the GIC handles virtual interrupts.

#### Chapter 7 GICv4.0 Virtual LPI Support

Read this for information about how the GIC handles virtual interrupts.

#### Chapter 8 GICv4.1 Virtual Interrupt Support

Read this for information about changes to virtual interrupt support in GICv4.1.

#### Chapter 9 Memory Partitioning and Monitoring

Read this for a description of Memory Partitioning and Monitoring in the context of the GIC.

#### Chapter 10 Power Management

Read this for information about GIC power management.

#### Chapter 11 Programmers' Model

Read this for a description of the GIC register interfaces, and all GIC registers.

#### Chapter 12 System Error Reporting

Read this for information about GIC support for error reporting.

#### Chapter 13 Legacy Operation and Asymmetric Configurations

Read this for information about GIC support for legacy operation and asymmetric configurations.

#### Appendix A GIC Stream Protocol interface

Read this for a description of the AXI4-Stream protocol standard message-based interface that the GIC Stream Protocol interface uses.

#### Appendix B Pseudocode Definition

Read this for a definition of the pseudocode that is used in this specification.

#### Glossary

Read this for definitions of some of the terms used in this specification.

#### Conventions

The following sections describe conventions that this book can use:

- Typographic conventions.

- Signals.

- Numbers.

- Pseudocode descriptions.

#### Typographic conventions

The typographical conventions are:

*italic* Introduces special terminology, and denotes citations.

bold Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

#### SMALL CAPITALS

Used for a few terms that have specific technical meanings, and are included in the *Glossary*.

Colored text Indicates a link. This can be:

- A URL, for example https://developer.arm.com.

- A cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, About the Generic Interrupt Controller (GIC) on page 1-16.

- A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example, *Banked register* or GICC CTLR.

#### **Signals**

In general this specification does not define processor signals, but it does include some signal examples and recommendations. The signal conventions are:

**Signal level** The level of an asserted signal depends on whether the signal is active-HIGH or

active-LOW. Asserted means:

- · HIGH for active-HIGH signals

- LOW for active-LOW signals.

**Lowercase n** At the start or end of a signal name denotes an active-LOW signal.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

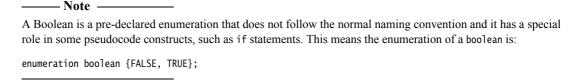

#### Pseudocode descriptions

This specification uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font, and follows the conventions described in the *Arm*\* *Architecture Reference Manual, Armv8, for Armv8-A architecture profile* and the *Arm*\* *Architecture Reference Manual, Armv7-A and Armv7-R edition.*

#### Additional reading

This section lists relevant publications from Arm and third parties.

See Arm Developer, https://developer.arm.com for access to Arm documentation.

#### **Arm publications**

- AMBA® 4 AXI4-Stream Protocol Specification (ARM IHI 0051).

- Arm® Architecture Reference Manual, Armv7-A and Armv7-R edition (ARM DDI 0406).

- Arm® Architecture Reference Manual, Armv8, for Armv8-A architecture profile (ARM DDI 0487).

- Arm® Architecture Reference Manual Supplement, Memory System Resource Partitioning and Monitoring (MPAM), for Armv8-A (ARM DDI 0598).

- Arm® Generic Interrupt Controller, Architecture version 2.0, Architecture Specification (ARM IHI 0048).

- *Arm® CoreSight™ Architecture Specification v3.0* (ARM IHI 0029).

- Arm® Server Base System Architecture (SBSA) (ARM-DEN-0029).

- GICv3 and GICv4 Software Overview (DAI 0492).

- Application Note GIC Stream Protocol Interface (ARM-ECM-0495013).

#### Other publications

The following books are referred to in this manual, or provide more information:

JEDEC Solid State Technology Association, Standard Manufacture's Identification Code, JEP106.

#### **Feedback**

Arm welcomes feedback on its documentation.

#### Feedback on this manual

If you have comments on the content of this manual, send an e-mail to errata@arm.com. Provide:

- The title.

- The number, Arm IHI 0069F.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

# Chapter 1 **Introduction**

This chapter provides an introduction to the GIC architecture. It provides an overview of the GIC architecture, and the features that are new to the architecture. It also provides definitions of the terminology that this document uses. It contains the following sections:

- About the Generic Interrupt Controller (GIC) on page 1-16.

- Terminology on page 1-20.

- Supported configurations and compatibility on page 1-24.

#### 1.1 About the Generic Interrupt Controller (GIC)

The GICv3 architecture is designed to operate with Armv8-A and Armv8-R compliant processing elements, PEs.

The Generic Interrupt Controller (GIC) architecture defines:

- The architectural requirements for handling all interrupt sources for any PE connected to a GIC.

- A common interrupt controller programming interface applicable to uniprocessor or multiprocessor systems.

The GIC is an architected resource that supports and controls interrupts. It provides:

- Registers for managing interrupt sources, interrupt behavior, and the routing of interrupts to one or more PEs.

- Support for:

- The Armv8 architecture.

- Locality-specific Peripheral Interrupts (LPIs).

- Private Peripheral Interrupts (PPIs).

- Software Generated Interrupts (SGIs).

- Shared Peripheral Interrupts (SPIs).

- Interrupt masking and prioritization.

- Uniprocessor and multiprocessor systems.

- Wakeup events in power management environments.

For each PE, the GIC architecture describes how IRQ and FIQ interrupts can be generated from different types of interrupts within the system. The Armv8-A Exception model describes how the PE handles these IRQ and FIQ interrupts.

Interrupt handling also depends on other aspects of the Armv8 architecture, such as the Security state and support for virtualization. The Arm architecture provides two Security states, each with an associated physical memory address space:

- Secure state.

- Non-secure state.

The GIC architecture supports the routing and handling of interrupts that are associated with both Security states. See *Interrupt grouping and security on page 4-59* for more information.

The GIC architecture supports the Armv8 model for handling virtual interrupts that are associated with a *virtual machine*, VM. A virtualized system has:

- A hypervisor that must include a component executing at EL2, that is responsible for switching between VMs.

- Several VMs executing at EL1.

- Applications executing at EL0 on a VM.

For more information about the Armv8 architecture, see Arm® Architecture Reference Manual, Armv8, for Armv8-A architecture profile. For more information about VMs, see About GIC support for virtualization on page 6-154.

This specification defines version 3.0, version 3.1 (GICv3), version 4.0 (GICv4), and version 4.1 (GICv4.1) of the GIC architecture. Version 2.0 (GICv2) is only described in terms of the GICv3 optional support for legacy operation, see *GICv3 with legacy operation on page 1-28*. For detailed information about the GICv2 architecture, see the *Arm*\* *Generic Interrupt Controller, Architecture version 2.0, Architecture Specification*.

| Note |                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|

|      | v3.0 and GICv3.1, all references to GICv3 in this manual apply equally to rwise. Any changes to the architecture specification for GICv4.1 are |

#### 1.1.1 Changes to the GIC architecture from GICv2

#### GIC scalability

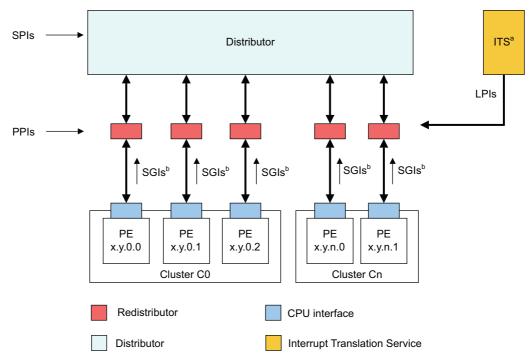

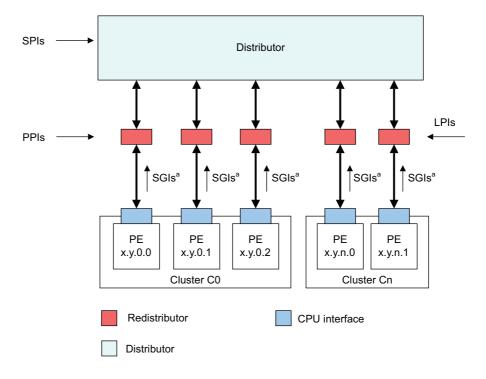

The GICv2 architecture only supports a maximum of eight PEs, and so has features that do not scale to a large system. GICv3 addresses this by changing the mechanism by which interrupts are routed, called *affinity routing*, and by introducing a new component to the interrupt distribution, called a *Redistributor*. See Chapter 3 *GIC Partitioning* for more information.

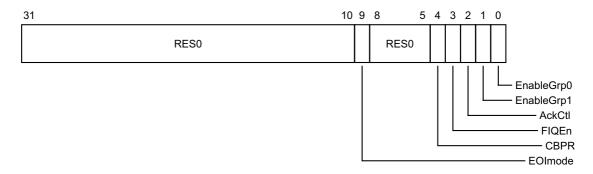

Affinity routing for a Security state is enabled by setting GICD\_CTLR.ARE\_S or GICD\_CTLR.ARE\_NS to 1.

#### Interrupt grouping

*Interrupt grouping* is the mechanism that is used by GICv3 to align interrupt handling with the Armv8 Exception model:

- Group 0 physical interrupts are expected to be handled at the highest implemented Exception level.

- Secure Group 1 physical interrupts are expected to be handled at Secure EL1 or EL2.

- Non-secure Group 1 physical interrupts are excepted to be handled at Non-secure EL2 in systems using virtualization, or at Non-secure EL1 in systems not using virtualization.

These interrupt groups can be mapped onto the Armv8 FIQ and IRQ signals as described in *Interrupt grouping on page 4-58*, using configuration bits from the Armv8 architecture and configuration bits within the GICv3 architecture.

In GICv3, interrupt grouping supports:

- Configuring each interrupt as Group 0, Secure Group 1, or Non-secure Group 1.

- Signaling Group 0 physical interrupts to the target PE using the FIQ exception request.

- Signaling Group 1 physical interrupts to the target PE in a manner that allows them to be handled using the IRQ handler in their own Security state. The exact handling of Group 1 interrupts depends on the current Exception level and Security state, as described in Chapter 4 Physical Interrupt Handling and Prioritization.

- A unified scheme for handling the priority of Group 0 and Group 1 interrupts.

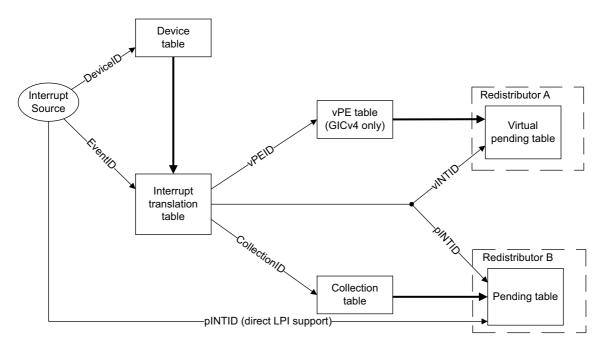

#### **Interrupt Translation Service (ITS)**

The Interrupt Translation Service, ITS, provides functionality that allows software to control how interrupts that are forwarded to the ITS are translated into:

- Physical interrupts, in GICv3 and GICv4.

- Virtual interrupts, in GICv4 only.

The ITS also allows software to determine the target Redistributor for a translated interrupt. Software can control the ITS through a command interface and associated table-based structures in memory. The outputs of the Interrupt Translation Service (ITS) are always LPIs, which are a form of message-based interrupt. See *The Interrupt Translation Service on page 5-85*.

#### Locality-specific Peripheral Interrupts (LPIs)

LPIs are a new class of interrupt that significantly extends the interrupt ID space that the GIC can handle. LPIs are optional, and, if implemented, can be generated and supported by an Interrupt Translation Service, ITS. See *LPIs on page 5-78*.

#### **Software Generated Interrupts (SGIs)**

With the ability of GICv3 to support large-scale systems, the context of an SGI is modified and no longer includes the identity of the source PE. See *Software Generated Interrupts on page 4-55*.

| Note                            |                                                      |           |

|---------------------------------|------------------------------------------------------|-----------|

| The original SGI format is only | available in GIC implementations that support legacy | operation |

#### **Shared Peripheral Interrupts (SPIs)**

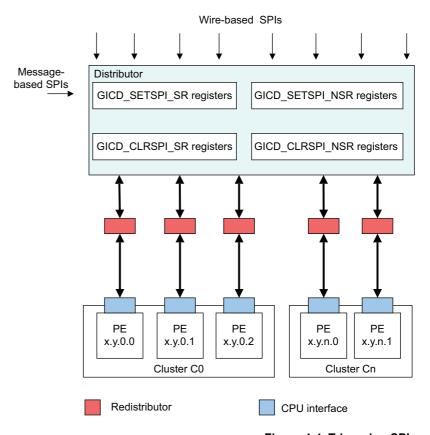

A new set of registers in the Distributor is added to support the setting and clearing of message-based SPIs. See *Shared Peripheral Interrupts on page 4-56*.

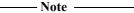

#### System register interface

This interface uses System register instructions in an Armv8-A or Armv8-R PE to provide a closely-coupled interface for the CPU interface registers. This interface is used for registers that are associated directly with interrupt handling and priority masking to minimize access latency. For virtualization, the registers that are accessed in this manner include both the registers that are accessed by a VM interrupt handler, and the registers that forward virtual interrupts from a hypervisor to a VM. All other registers are memory-mapped.

For AArch64 state, access to the System register interface is enabled by the following settings:

- ICC SRE EL1.SRE == 1.

- ICC\_SRE\_EL2.SRE == 1.

- ICC SRE EL3.SRE == 1.

For AArch32 state, access to the System register interface is enabled by the following settings:

- ICC SRE.SRE == 1.

- ICC HSRE.SRE == 1.

- ICC MSRE.SRE == 1.

Other behavior, which is backwards compatible with GICv2, is described in Chapter 13 *Legacy Operation and Asymmetric Configurations*.

In a GIC that supports legacy operation, memory-mapped access is available for all architected GIC registers.

Unless indicated otherwise, this manual describes the GICv3 architecture in a system with affinity routing, System register access, and two Security states, enabled. This means that:

- GICD CTLR.ARE NS == 1.

- GICD CTLR.ARE S == 1.

- GICD CTLR.DS == 0.

For operation in AArch64 state:

- ICC\_SRE\_EL1.SRE == 1, for both the Secure and the Non-secure copy of this register.

- ICC SRE EL2.SRE == 1.

- ICC SRE EL3.SRE == 1.

For operation in AArch32 state:

- ICC SRE.SRE == 1.

- ICC HSRE.SRE == 1.

- ICC MSRE.SRE == 1.

From GICv3 onwards, legacy operation with the ARE and SRE control bits set to 0 is deprecated, and removed if the PE implements Secure EL2. See Chapter 13 *Legacy Operation and Asymmetric Configurations* for more information about legacy operation.

#### Changes specific to GICv3.1

GICv3.1 adds support for Memory Partitioning and Monitoring, an extended SPI range, an extended PPI range, and support for Secure EL2.

#### Changes specific to GICv4

GICv4 adds support for the direct injection of virtual interrupts to a VM, without involving the hypervisor. Direct injections are only supported by systems that implement at least one ITS that translates interrupts into LPIs.

#### Changes specific to GICv4.1

GICv4.1 extends direct injection support to also handle virtual SGIs. GICv4.1 changes the way some GICv4 data structures are handled.

#### 1.2 Terminology

The architecture descriptions in this manual use the same terminology that is used for the Armv8 architecture. For more information about this terminology, see the introduction to Part A of the Arm® Architecture Reference Manual, Armv8, for Armv8-A architecture profile.

In addition, the AArch64 System register names are used where appropriate, in preference to listing both the AArch32 and AArch64 System register names. The ELx suffix on the AArch64 register name indicates the lowest Exception level at which the register can be accessed. The individual AArch64 System register descriptions contain a reference to the AArch32 System register that provides the same functionality.

The following sections define the architectural terms used in this manual:

- Interrupt types.

- *Interrupt states on page 1-21.*

- Models for handling interrupts on page 1-21.

- Additional terms on page 1-22.

#### 1.2.1 Interrupt types

A device that implements the GIC architecture can control *peripheral interrupts*. Peripheral interrupts are typically asserted by a physical signal to the GIC. The GIC architecture defines the following types of peripheral interrupt:

#### Locality-specific Peripheral Interrupt (LPI)

An LPI is a targeted peripheral interrupt that is routed to a specific PE within the affinity hierarchy:

- LPIs are always Non-secure Group 1 interrupts, in a system where two Security states are enabled.

- LPIs have edge-triggered behavior.

- LPIs can be routed using an ITS.

- LPIs do not have an active state, and therefore do not require explicit deactivation.

- LPIs are always message-based interrupts.

See LPIs on page 5-78 for more information.

#### Private Peripheral Interrupt (PPI)

This is a peripheral interrupt that targets a single, specific PE, and different PEs can use the same interrupt number to indicate different events:

- PPIs can be Group 0 interrupts, Secure Group 1 interrupts, or Non-secure Group 1 interrupts.

- PPIs can support either edge-triggered or level-sensitive behavior.

- PPIs are never routed using an ITS.

- PPIs have an active state and therefore require explicit deactivation.

Commonly, it is expected that PPIs are used by different instances of the same interrupt source on each PE, thereby allowing a common interrupt number to be used for PE-specific events, such as the interrupts from a private timer.

#### Shared Peripheral Interrupt (SPI)

This is a peripheral interrupt that the Distributor can route to a specified PE that can handle the interrupt, or to a PE that is one of a group of PEs in the system that has been configured to accept this type of interrupt:

- SPIs can be Group 0 interrupts, Secure Group 1 interrupts, or Non-secure Group 1 interrupts.

- SPIs can support either edge-triggered or level-sensitive behavior.

- SPIs are never routed using an ITS.

- SPIs have an active state and therefore require explicit deactivation.

See *Shared Peripheral Interrupts on page 4-56* for more information. For more information about the Distributor, see Chapter 3 *GIC Partitioning*.

#### Software Generated Interrupt (SGI)

SGIs are typically used for inter-processor communication, and are generated by a write to an SGI register in the GIC:

- SGIs can be Group 0 interrupts, Secure Group 1 interrupts, or Non-secure Group 1 interrupts.

- SGIs have edge-triggered behavior.

- SGIs are never routed using an ITS.

- SGIs have an active state and therefore require explicit deactivation.

See Software Generated Interrupts on page 4-55 for more information.

An interrupt that is edge-triggered has the following property:

It is asserted on detection of a rising edge of an interrupt signal and then, regardless of the state of the signal, remains asserted until the interrupt is acknowledged by software.

For information about edge-triggered message-based interrupts, see Message-based interrupt.

An interrupt that is level-sensitive has the following properties:

- It is asserted whenever the interrupt signal level is active, and deasserted whenever the level is not active.

- It is explicitly deasserted by software.

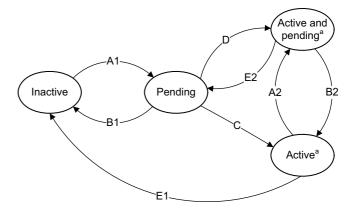

#### 1.2.2 Interrupt states

The following states apply at each interface between the GIC and a connected PE:

**Inactive** An interrupt that is not active or pending.

**Pending** An interrupt that is recognized as asserted in hardware, or generated by software, and is

waiting to be handled by the target PE.

Active An interrupt that has been acknowledged by a PE and is being handled, so that another

assertion of the same interrupt is not presented as an interrupt to a PE, until the initial

interrupt is no longer active.

LPIs do not have an active state, and transition to the inactive state on being acknowledged

by a PE.

Active and pending An interrupt that is active from one assertion of the interrupt, and is pending from a

subsequent assertion.

LPIs do not have an active and pending state, and transition to the inactive state on being

acknowledged by a PE.

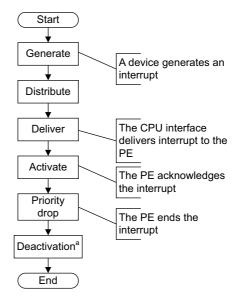

The GIC maintains state for each supported interrupt. The state machine defines the possible transitions between interrupt states, and, for each interrupt type, the conditions that cause a transition. See *Interrupt handling state machine on page 4-51* for more information.

#### 1.2.3 Models for handling interrupts

In a multiprocessor implementation, the following models exist for handling interrupts:

#### Targeted distribution model

This model applies to all PPIs and to all LPIs. It also applies to:

- SPIs during non-legacy operation, if GICD IROUTER<n>.Interrupt Routing Mode == 0.

- During legacy operation, when GICD\_CTLR.ARE\_\* == 0, if only one bit in the appropriate GICD\_ITARGETSR<n> field == 1.

A target PE that has been specified by software receives the interrupt.

#### Targeted list model

This model applies to SGIs only. Multiple PEs receive the interrupt independently. When a PE acknowledges the interrupt, the interrupt pending state is cleared only for that PE. The interrupt remains pending for each PE independently until it has been acknowledged by the PE.

#### 1 of N model

This model applies to SPIs only. The interrupt is targeted at a specified set of PEs, and is taken on only one PE in that set. The PE that takes the interrupt is selected in an IMPLEMENTATION DEFINED manner. The architecture applies restrictions on which PEs can be selected, see *Enabling the distribution of interrupts on page 4-63*.

- The Arm GIC architecture guarantees that a 1 of N interrupt is presented to only one PE listed in the target PE set.

- A 1 of N interrupt might be presented to a PE where the interrupt is not the highest priority interrupt, or where the interrupt is masked by ICC\_PMR\_EL1 or within the PE. See *Interrupt lifecycle on page 4-46*.

For SPIs during legacy operation, this model applies when more than one target PE is specified in the target registers.

The hardware implements a mechanism to determine which PE activates the interrupt, if more than one PE can handle the interrupt.

#### 1.2.4 Additional terms

The following additional terms are used throughout this manual:

#### Idle priority

In GICv3, the idle priority, 0xFF, is the running priority read from ICC\_RPR\_EL1 on the CPU interface when no interrupts are active on that interface. During legacy operation, the idle priority, as read from GICC\_RPR, is IMPLEMENTATION DEFINED, as in GICv2.

#### **Interrupt Identifier (INTID)**

The number space that uniquely identifies an interrupt with an associated event and its source. The interrupt is then routed to one or more PEs for handling. PPI and SGI interrupt numbers are local to each PE. SPIs and LPIs have global interrupt numbers for the physical domain. See *INTIDs on page 2-31* for more information.

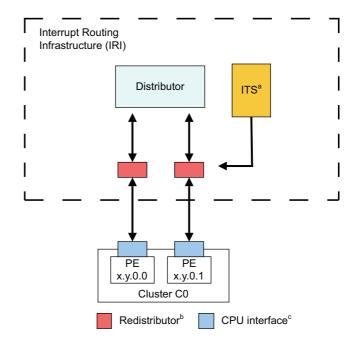

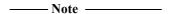

#### **Interrupt Routing Infrastructure (IRI)**

The Distributor, Redistributors and, optionally, one or more ITSs. See *The GIC logical components on page 3-38* for more information.

#### Message-based interrupt

A message-based interrupt is an interrupt that is asserted because of a memory write access to an assigned address. Physical interrupts can be converted to message-based interrupts. Message-based interrupts can support either level-sensitive or edge-triggered behavior, although LPIs are always edge-triggered.

GICv3 supports two mechanisms for message-based interrupts:

- A mechanism for communicating an SPI, where the assigned address is held in the Distributor. In this case the message-based interrupt can be either level-sensitive or edge-triggered.

- A mechanism for communicating an LPI, where the assigned address is held in an ITS, if an ITS is implemented, or in the Redistributor.

Arm recommends the use of LPIs to provide support for MSI and MSI-X capabilities in systems that support PCIe. See Chapter 5 *Locality-specific Peripheral Interrupts and the ITS* for more information. GICv3 also includes architected support for signaling SPIs using message-based interrupts, see *Shared Peripheral Interrupts on page 4-56*.

#### Physical interrupt

An interrupt that targets a physical PE is a physical interrupt. It is signaled to the PE by the physical CPU interface to which the PE is connected.

#### Running priority

At any given time, the running priority of a CPU interface is either:

- The group priority of the active interrupt, for which there has not been a priority drop on that interface.

- If there is no active interrupt for which there has not been a priority drop on the interface, the running priority is the idle priority 0xFF.

#### **Sufficient priority**

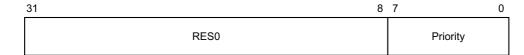

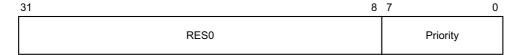

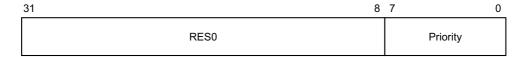

The GIC CPU interface compares the priority of an enabled, pending interrupt with all of the following, to determine whether the interrupt has sufficient priority:

- The Priority Mask Register, ICC\_PMR\_EL1.

- The preemption settings for the interface, as indicated by ICC\_BPR0\_EL1 and ICC\_BPR1\_EL1.

- The current running priority, as indicated by ICC\_RPR\_EL1 for the CPU interface.

If the interrupt has sufficient priority it is signaled to the connected PE.

#### Virtual interrupt

An interrupt that targets a VM is a virtual interrupt. It is signaled by the associated virtual CPU interface. See Chapter 6 *Virtual Interrupt Handling and Prioritization* for more information.

#### Maintenance interrupt

A physical interrupt that signals key events associated with interrupt handling on a VM to allow the hypervisor to track those events. These events are processed by the hypervisor, and include enabling and disabling a particular group of interrupts. See *Maintenance interrupts on page 6-161* for more information.

#### 1.3 Supported configurations and compatibility

In Armv8-A, EL2 and EL3 are optional, and a PE can support one, both, or neither of these Exception levels. However:

- A PE requires EL3 to support both Secure and Non-secure state.

- A PE requires EL2 to support virtualization.

- If EL3 is not implemented, there is only a single Security state. This Security state is either Secure state or Non-secure state.

GICv3 supports interrupt handling for all of these configurations, and for execution in both AArch32 state and AArch64 state, in accordance with the *interprocessing* rules described in *Arm® Architecture Reference Manual, Armv8, for Armv8-A architecture profile.*

#### 1.3.1 Affinity routing configuration

The GICv3 architecture supports affinity routing. It provides optional support for:

- An asymmetric configuration, where affinity routing is enabled for Non-secure state and disabled for Secure state. This provides support for a Secure legacy environment.

- A legacy-only environment where affinity routing is disabled for both Secure state and Non-secure state.

#### 1.3.2 System register configuration

When affinity routing is enabled for execution in both Security states, the GIC must be configured to use System register access to handle physical interrupts. The architecture does not support having affinity routing enabled for a Security state, and not having System register access configured for that Security state. Configuring the GIC this way results in UNPREDICTABLE behavior. When affinity routing is enabled for execution in Non-secure state, the GIC architecture optionally supports legacy operation for virtual interrupts, that is legacy interrupt handling at Non-secure EL1 under the control of a hypervisor executing at EL2.

#### 1.3.3 GIC control and configuration

Many of the GIC registers are available in different forms, to permit effective interrupt handling:

- For two Security states.

- For different interrupt groups.

- Using System register access for GICv3 or memory-mapped access for legacy operation.

When System register access is enabled, control and configuration of the GIC architecture is handled by architected System registers and the associated accesses that define the GIC programmers' model. See Chapter 11 *Programmers' Model* for more information.

Some registers are always memory-mapped, while others use System register access in GICv3, and memory-mapped access for legacy operations.

Table 1-1 shows the registers that are always memory-mapped.

Table 1-1 Memory-mapped registers

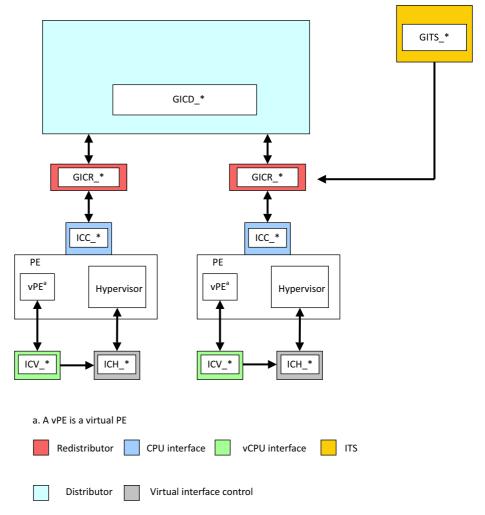

| Prefix in short register name | Registers                            |  |  |

|-------------------------------|--------------------------------------|--|--|

| GICD                          | Distributor registers                |  |  |

| GICR                          | Redistributor registers <sup>a</sup> |  |  |

| GITS                          | ITS registers <sup>b</sup>           |  |  |

- a. There is one copy of each of the Redistributor registers per PE.

- There can be more than one ITS in an implementation. Each ITS has its own copy of the GITS registers.

Table 1-2 shows the registers that are memory-mapped for legacy operations, but are replaced by System register access in GICv3 when System register access is enabled.

Table 1-2 Memory-mapped registers for legacy operation

| Prefix in short register name | Registers                           |

|-------------------------------|-------------------------------------|

| GICC                          | Physical CPU interface registers    |

| GICV                          | Virtual CPU interface registers     |

| GICH                          | Virtual interface control registers |

#### ----- Note ------

- An operating system executing at Non-secure EL1 uses either the GICC\_\* or the GICV\_\* registers to control

interrupts, and is unaware of the difference.

- The GICR\_\* and GITS\_\* registers are introduced in GICv3.

Table 1-3 shows the registers that GICv3 supports when System register access is enabled.

Table 1-3 System registers

| Prefix in short register name | System registers accessed           |

|-------------------------------|-------------------------------------|

| ICC                           | Physical CPU interface registers    |

| ICV                           | Virtual CPU interface registers     |

| ICH                           | Virtual interface control registers |

The Armv8 support for virtualization and the Exception level at which a PE is operating determine whether the physical CPU interface registers or the virtual CPU interface registers are accessed.

For more information about register names and the factors that affect which register to use, see *GIC System register* access on page 11-197.

#### 1.3.4 References to the Armv8 architectural state

Table 1-4 shows the Armv8 architectural state that is used with or affects the operation of the GIC.

Table 1-4 Armv8 architectural state affecting GIC operation

| AArch64             | Field     | AArch32<br>State    |           | Purpose                                                                                               |

|---------------------|-----------|---------------------|-----------|-------------------------------------------------------------------------------------------------------|

| State               |           |                     | Field     |                                                                                                       |

| PSTATE <sup>a</sup> | A         | PSTATE <sup>a</sup> | A         | SError interrupt mask bit (AArch64 state) Asynchronous Abort mask bit (AArch32 state)                 |

|                     | I         |                     | I         | IRQ mask bit                                                                                          |

|                     | F         | <del></del>         | F         | FIQ mask bit                                                                                          |

| -                   | -         | DFSR                | STATUS/FS | Fault status                                                                                          |

|                     | -         |                     | ExT       | External abort type                                                                                   |

| ESR_ELx             | EC        | HSR                 | EC        | Exception class                                                                                       |

|                     | IL        | <del></del>         | IL        | Instruction length for synchronous exceptions                                                         |

|                     | ISS       | <del></del>         | ISS       | Instruction Specific Syndrome                                                                         |

| HCR_EL2             | AMO       | HCR                 | AMO       | SError interrupt routing (AArch64 state)                                                              |

|                     |           |                     |           | Asynchronous External Abort interrupt routing (AArch32 state)                                         |

|                     | IMO       | <del></del>         | IMO       | Physical IRQ routing                                                                                  |

|                     | FMO       | <del></del>         | FMO       | Physical FIQ routing                                                                                  |

|                     | RW        | <u> </u>            | RESO      | Execution state control for lower Exception level (AArch64 state)                                     |

|                     | VSE       |                     | VA        | Virtual SError Abort exception (AArch64 state)<br>Virtual Asynchronous Abort exception (AArch3 state) |

|                     | VI        |                     | VI        | Virtual IRQ interrupt                                                                                 |

|                     | VF        |                     | VF        | Virtual FIQ interrupt                                                                                 |

|                     | TGE       | <del></del>         | TGE       | Trap General Exceptions                                                                               |

| HSTR_EL2            | T <n></n> | HSTR                | T <n></n> | Hypervisor system traps                                                                               |

|                     | I         |                     | I         | IRQ pending                                                                                           |

|                     | F         |                     | F         | FIQ pending                                                                                           |

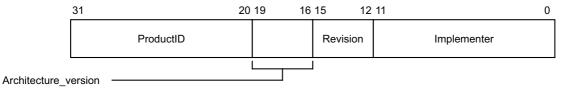

| ID_AA64PFR0_EL1     | GIC       | -                   | -         | System register GIC interface support                                                                 |

| ID_PFR1_EL1         | GIC       | ID_PFR1             | GIC       | System register GIC CPU interface support                                                             |

| ISR_EL1             | A         | ISR                 | A         | SError pending (AArch64 state) External Abort pending (AArch32 state)                                 |

Table 1-4 Armv8 architectural state affecting GIC operation (continued)

| AArch64   |       | AArch32     |      | 2                                                                                         |  |

|-----------|-------|-------------|------|-------------------------------------------------------------------------------------------|--|

| State     | Field | State Field |      | Purpose                                                                                   |  |

| MPIDR_EL1 | Aff3  | MPIDR       | -    | Affinity level 3                                                                          |  |

|           | Aff2  | <del></del> | Aff2 | Affinity level 2                                                                          |  |

|           | Aff1  | <del></del> | Aff1 | Affinity level 1                                                                          |  |

|           | Aff0  | <del></del> | Aff0 | Affinity level 0                                                                          |  |

| SCR_EL3   | RW    | SCR         | RES0 | Execution state control for lower Exception levels (AArch64 state only)                   |  |

|           | EA    | <u> </u>    | EA   | SError interrupt routing (AArch64 state) External Abort interrupt routing (AArch32 state) |  |

|           | FIQ   | <del></del> | FIQ  | Physical FIQ routing                                                                      |  |

|           | IRQ   | <del></del> | IRQ  | Physical IRQ routing                                                                      |  |

|           | NS    | <del></del> | NS   | Non-secure bit                                                                            |  |

|           | EEL2  | <del></del> | -    | Secure EL2 enable                                                                         |  |

a. Process state, PSTATE, is an abstraction of the process state information. For more information, see Arm® Architecture Reference Manual, Armv8, for Armv8-A architecture profile.

For more information about these registers and fields, see  $Arm^{\circ}$  Architecture Reference Manual, Armv8, for Armv8-A architecture profile.

#### 1.3.5 GICv3 with no legacy operation

In an implementation that does not support legacy operation, affinity routing and System register access are permanently enabled. This means that the associated control bits are RAO/WI. Table 1-5 shows the register fields that are affected by this.

Table 1-5 Control bits for affinity routing and System register access

| AArch32 registers | Memory-mapped registers               |

|-------------------|---------------------------------------|

| ICC_SRE.SREa      | -                                     |

| ICC_HSRE.SRE      | -                                     |

| ICC_MSRE.SRE      | -                                     |

| -                 | GICD_CTLR.ARE_S                       |

| -                 | GICD_CTLR.ARE_NS                      |

|                   | ICC_SRE.SRE <sup>a</sup> ICC_HSRE.SRE |

a. There is a Secure copy and a Non-secure copy of this register.

If Secure Virtualization is supported, this is the only permitted configuration.

#### 1.3.6 GICv3 with legacy operation

Legacy operation is a form of limited backwards compatibility with GICv2 that is provided to allow systems using GICv3 to run code using GICv2, provided that this code meets the restrictions described in this section. Legacy operation is optional in GICv3. See Legacy support of interrupts and asymmetric configurations on page 13-814.

In a GICv3 implementation that supports legacy operation, a maximum of eight PEs, whose individual support for a memory-mapped register interface is IMPLEMENTATION DEFINED, are available as physical or virtual interrupt targets within a given VM. It is IMPLEMENTATION DEFINED:

- Whether legacy operation applies to execution in both Security states, or to execution in Secure state only.

- Whether legacy operation is available only in the virtual CPU interface when executing in Non-secure EL1.

In GICv3, the following restrictions apply to legacy operation:

| Correspondin  | gly, even in legacy mode, the behave | rior is as if the GICC_CT | LR.AckCtl bit described i   | n GICv2 |

|---------------|--------------------------------------|---------------------------|-----------------------------|---------|

| is RAZ/WI.    |                                      |                           |                             |         |

| ——Note        | <u> </u>                             |                           |                             |         |

| In a GICv3 in | plementation that supports legacy    | operation, a VM is perm   | nitted to control Non-secur | re      |

interrupts when GICV CTLR.AckCtl set to 1. However, Arm deprecates the use of GICV CTLR.AckCtl.

The GICv2 feature GICC CTLR.AckCtl was deprecated in GICv2 and is not supported in GICv3.

- The GICv2 configuration lockdown feature and the associated CFGSDISABLE input signal are not supported.

- A hypervisor executing at EL2 can control virtual interrupts only for the PE on which the EL2 software is

executing and cannot control virtual interrupts on other PEs.

For legacy operation, an asymmetric configuration is supported where:

- Affinity routing and System register access are enabled in Non-secure state and at EL3.

- Affinity routing and System register access are disabled at Secure EL1.

This allows a secure operating system, running at Secure EL1, to use legacy functionality, provided that it does not configure Non-secure interrupts.

In GICv2 software executing in Secure state could use GICC\_AIAR, GICC\_AEOIR, GICC\_AHPPIR, and GICC\_ABPR to control interrupts in Non-secure state. There is no equivalent functionality in asymmetric configurations.

# **Chapter 2 Distribution and Routing of Interrupts**

This chapter describes the distribution and routing of interrupts to a target PE using affinity routing, and the assignment of interrupt IDs. It contains the following sections:

- The Distributor and Redistributors on page 2-30.

- INTIDs on page 2-31.

- Affinity routing on page 2-35.

#### 2.1 The Distributor and Redistributors

The Distributor provides the routing configuration for SPIs, and holds all the associated routing and priority information.

The Redistributor provides the configuration settings for PPIs and SGIs.

A Redistributor always presents the pending interrupt with the highest priority to the CPU interface in finite time. For more information about interrupt prioritization, see *Interrupt prioritization on page 4-65*.

The highest priority pending interrupt might change because:

- The previous highest priority interrupt has been acknowledged.

- The previous highest priority interrupt has been preempted.

- The previous highest priority interrupt is removed and no longer valid.

- The group interrupt enable has been modified.

- The PE is no longer a participating PE. See *Participating nodes on page 2-36*.

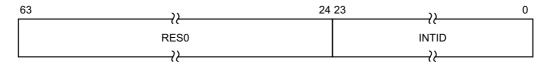

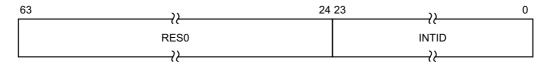

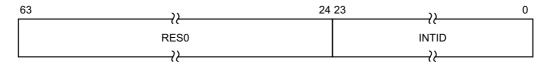

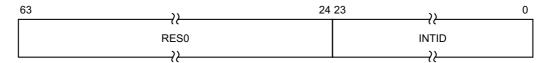

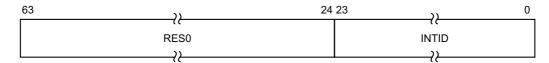

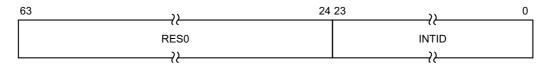

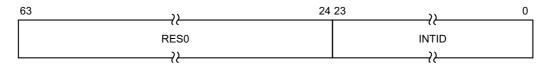

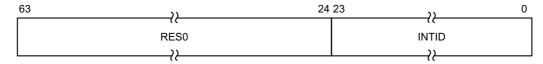

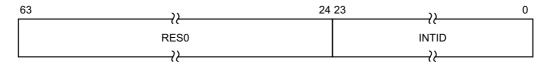

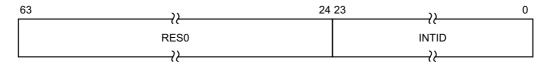

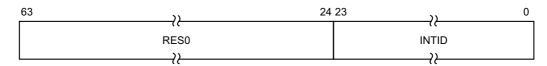

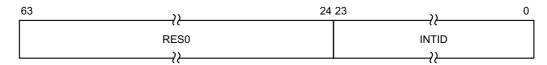

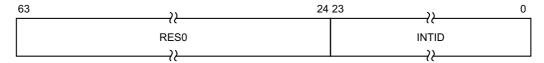

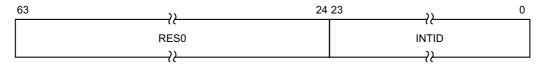

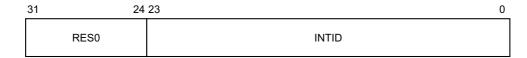

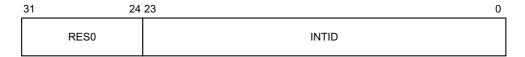

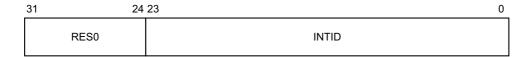

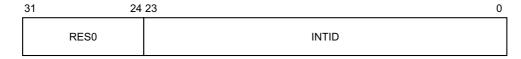

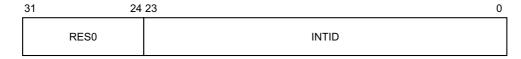

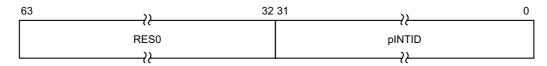

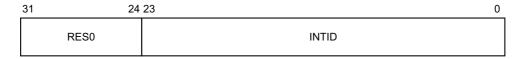

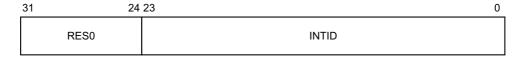

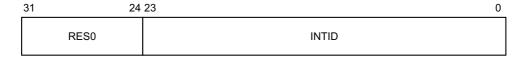

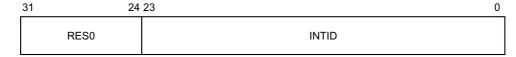

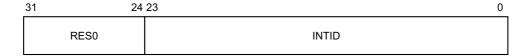

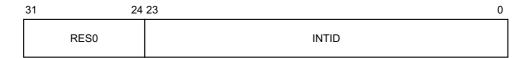

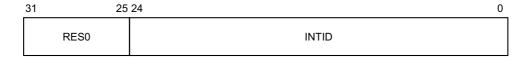

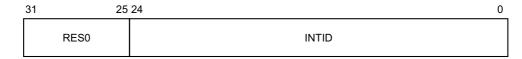

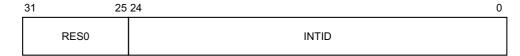

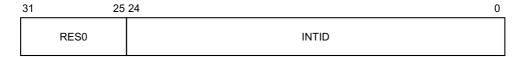

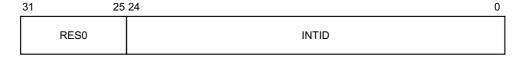

#### 2.2 INTIDs

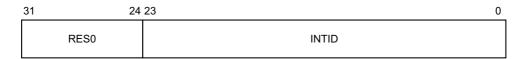

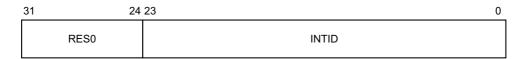

Interrupts are identified using *ID numbers* (INTIDs). The range of INTIDs supported by GICv3 is IMPLEMENTATION DEFINED, according to the following rules:

- For the number of INTID bits supported in the Distributor and Redistributor:

- If LPIs are not supported, the ID space in the Distributor is limited to 10 bits. This is the same as in earlier versions of the GIC architecture.

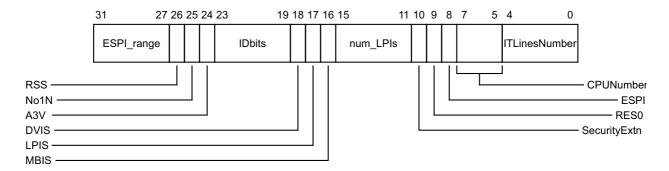

- If LPIs are supported, the INTID field is IMPLEMENTATION DEFINED in the range of 14-24 bits, as

described in the register description for GICD TYPER.

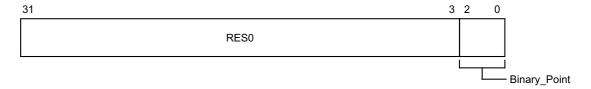

A Redistributor can be configured through GICR\_PROPBASER to use fewer bits than specified by GICD\_TYPER.

- For the number of INTID bits supported in the ITS:

- If LPIs are supported, the INTID field is IMPLEMENTATION DEFINED in the range of 14-24 bits.

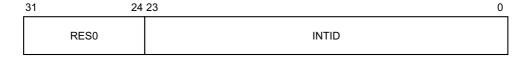

- The size of the INTID field is defined by GITS TYPER.IDbits.

The ITS must be programmed so that interrupts that are forwarded to a Redistributor are in the range of interrupts that are supported by that Redistributor, otherwise the behavior is UNPREDICTABLE.

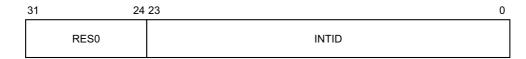

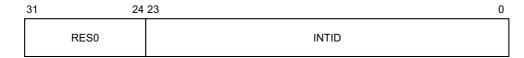

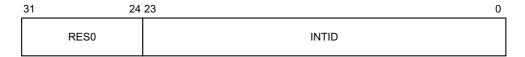

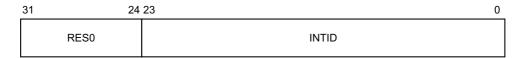

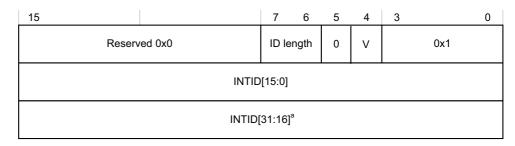

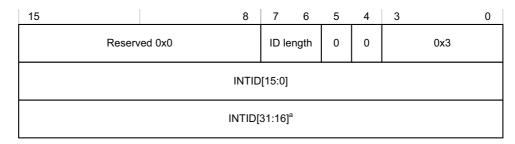

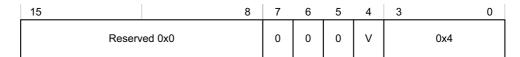

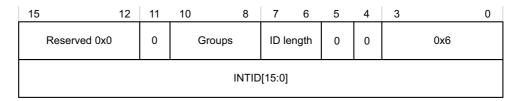

- For the number of INTID bits supported in the CPU interface:

- The GICv3 CPU interface supports either a 16-bit or a 24-bit INTID field, the choice being IMPLEMENTATION DEFINED. The number of physical interrupt identifier bits that are supported is indicated by ICC\_CTLR\_EL1.IDbits and ICC\_CTLR\_EL3.IDbits.

The valid INTID space is governed by the implemented size in the CPU interface and the Distributor. It is a programming error to forward an INTID that is greater than the supported size to a CPU interface.

Unused INTID bits are RAZ. This means that any affected bit field is zero-extended.

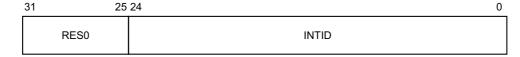

Table 2-1 shows how the INTID space is partitioned by interrupt type.

Table 2-1 INTIDs

| INTID       | Interrupt type           | Details                                                                                                                                                                                                 | Notes                                                                                                                                   |

|-------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0 – 15      | SGI                      | These interrupts are local to a CPU interface.                                                                                                                                                          | INTIDs 0-1023 are compatible                                                                                                            |

| 16 – 31     | PPI                      | -                                                                                                                                                                                                       | with earlier versions of the GIC architecture.                                                                                          |

| 32 – 1019   | SPI                      | Shared peripheral interrupts that the Distributor can route to either a specific PE, or to any one of the PEs in the system that is a participating node, see <i>Participating nodes on page 2-36</i> . |                                                                                                                                         |

| 1020 – 1023 | Special interrupt number | Interrupt IDs that are reserved for special purposes, as <i>Special INTIDs on page 2-32</i> describes.                                                                                                  | -                                                                                                                                       |

| 1024 – 1055 | -                        | Reserved                                                                                                                                                                                                | -                                                                                                                                       |

| 1056 – 1119 | PPI                      | Extended PPI. The interrupts are local to a CPU interface.                                                                                                                                              | INTIDs 1056-1119 are not compatible with earlier versions of the GIC architecture. This range is supported by the GICv3.1 architecture. |

| 1120 – 4095 | -                        | Reserved                                                                                                                                                                                                | -                                                                                                                                       |

Table 2-1 INTIDs (continued)

| INTID                               | Interrupt type | Details                                                          | Notes                                  |

|-------------------------------------|----------------|------------------------------------------------------------------|----------------------------------------|

| 4096 – 5119                         | SPI            | Extended SPI.                                                    | Supported by the GICv3.1 architecture. |

| 5120 - 8191                         | -              | Reserved                                                         |                                        |

| 8192 –<br>IMPLEMENTATION<br>DEFINED | LPI            | Peripheral hardware interrupts that are routed to a specific PE. | -                                      |

The Arm recommended PPI INTID assignments are provided by the Server Base System Architecture, see *Arm*\* *Server Base System Architecture (SBSA)*.

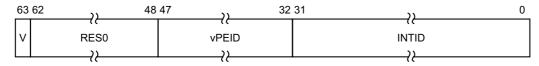

The GICv4 architecture provides a unique INTID space for each VM by supporting a vPEID in addition to the INTID space. See *About GIC support for virtualization on page 6-154* for more information about VMs and *The Interrupt Translation Service on page 5-85* for more information about vPEIDs.

Arm strongly recommends that implemented interrupts are grouped to use the lowest INTID numbers and as small a range of INTIDs as possible. This reduces the size of the associated tables in memory that must be implemented, and that discovery routines must check.

Arm strongly recommends that software reserves:

- INTID0 INTID7 for Non-secure interrupts.

- INTID8 INTID15 for Secure interrupts.

#### 2.2.1 Special INTIDs

The list of the INTIDs that the GIC architecture reserves for special purposes is as follows:

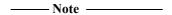

The GIC returns this value in response to a read of ICC\_IAR0\_EL1 or ICC\_HPPIR0\_EL1 at EL3, to indicate that the interrupt being acknowledged is one which is expected to be handled at Secure EL1. This INTID is only returned when the PE is executing at EL3 using AArch64 state, or when the PE is executing in AArch32 state in Monitor mode.

This value can also be returned by reads of ICC\_IAR1\_EL1 or ICC\_HPPIR1\_EL1 at EL3 when ICC\_CTLR\_EL3.RM == 1, see *Asymmetric operation and the use of ICC\_CTLR\_EL3.RM on page 13-818*.

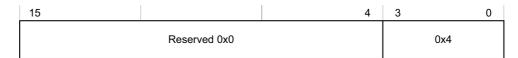

The GIC returns this value in response to a read of ICC\_IAR0\_EL1 or ICC\_HPPIR0\_EL1 at EL3, to indicate that the interrupt being acknowledged is one which is expected to be handled at Non-secure EL1 or EL2. This INTID is only returned when the PE is executing at EL3 using AArch64 state, or when the PE is executing in AArch32 state in Monitor mode.

This value can also be returned by reads of ICC\_IAR1\_EL1 or ICC\_HPPIR1\_EL1 at EL3 when ICC\_CTLR\_EL3.RM == 1, see Asymmetric operation and the use of ICC\_CTLR\_EL3.RM on page 13-818

- This value applies to legacy operation only. For more information, see *Use of the special INTID* 1022 on page 13-815.

- This value is returned in response to an interrupt acknowledge, if there is no pending interrupt with sufficient priority for it to be signaled to the PE, or if the highest priority pending interrupt is not appropriate for the:

- Current Security state.

- Interrupt group that is associated with the System register.

| ——Note |  |

|--------|--|

| 11016  |  |

These INTIDs do not require an end of interrupt or deactivation.

For more information about the use of special INTIDs, see the descriptions for the following registers:

- ICC IAR0 EL1.

- ICC IAR1 EL1.

- ICC HPPIR0 EL1.

- ICC HPPIR1 EL1.

#### 2.2.2 Implementations with mixed INTD sizes

Implementations might choose to implement different INTID sizes for different parts of the GIC, subject to the following rules:

• PEs might implement either 16 or 24 bits of INTID.

A system might include a mixture of PEs that support 16 bits of INTID and PEs that support 24 bits of INTID.

- The Distributor and Redistributors must all implement the same number of INTID bits.

- In systems that support LPIs, the Distributors and all Redistributors must implement at least 14 bits of INTID. The number of bits that is implemented in the Distributor and Redistributors must not exceed the minimum number that is implemented on any PE in the system.

Because interrupts might target any PE, each PE must be able to receive the maximum INTID that can be sent by a Redistributor. This means that the INTID size that is supported by the Redistributors cannot exceed the minimum INTID size that is supported by each PE in the system.

- In systems that do not support LPIs, the Distributor and all Redistributors must implement at least 5 bits of INTID and cannot implement more than 10 bits of INTID. For GIC version 3.1, no more than 13 bits of INTID can be implemented.

- In systems that include one or more ITSs, an ITS might implement any value up to and including the number of bits that are supported by the Distributor and the Redistributors down to a minimum of 14 bits, which is the minimum number that is required for LPI support.

#### 2.2.3 Valid interrupt ID check pseudocode

The following pseudocode describes how the GIC checks whether an INTID for a physical interrupt is valid:

```

// Now check for special identifiers

if IsSpecial(intID) then

return FALSE;

// It is a special ID

// All the checks pass so the identifier is valid

return TRUE;

The following pseudocode describes how the GIC checks whether an INTID for a virtual interrupt is valid:

// VirtualIdentifierValid()

// ========

boolean VirtualIdentifierValid(bits(64) data, boolean lpiAllowed)

// First check whether any out of range bits are set

integer N = VIDBits();

if !IsZero(data<63:N>) then

if ICH_VTR_EL2.SEIS == '1' then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

intID = data<INTID_SIZE-1:0>;

if !lpiAllowed && IsLPI(intID) then

// LPIs are not supported

if ICH_VTR_EL2.SEIS == '1' then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

// Now check for special identifiers

if IsSpecial(intID) then

return FALSE;

// It is a special ID

// All the checks pass so the identifier is valid

return TRUE;

The following pseudocode describes CPU interface ID size function.

// CPUInterfaceIDSize()

// =======

// Returns the number of Interrupt ID bits implemented at the CPU interface. This value is an

// IMPLEMENTATION DEFINED choice of 16 or 24 and is discoverable from ICC_CTLR_EL1/EL3.IDbits

integer CPUInterfaceIDSize()

return integer IMPLEMENTATION_DEFINED "CPU interface INTID size 16 or 24";

```

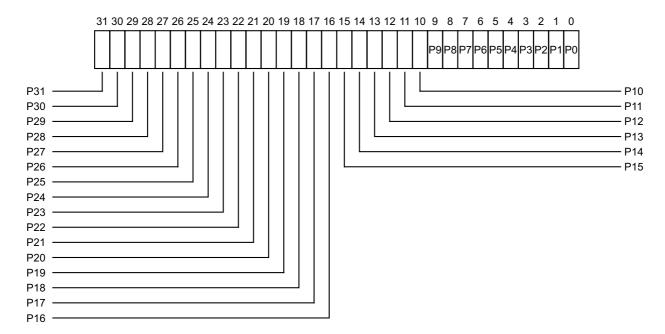

#### 2.3 Affinity routing

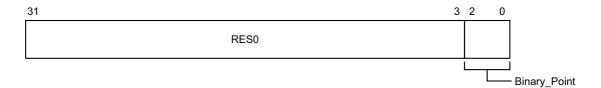

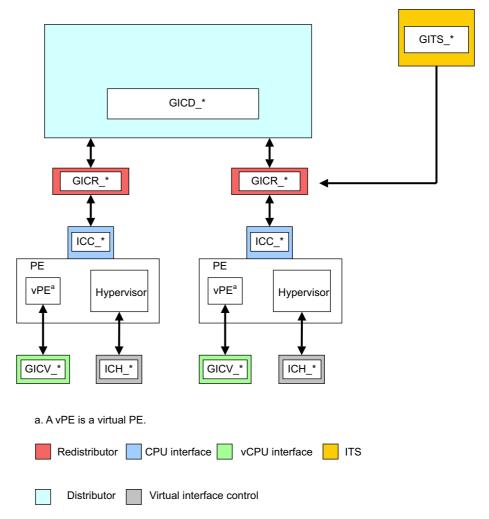

Affinity routing is a hierarchical address-based scheme to identify specific PE nodes for interrupt routing.

For a PE, the affinity value is defined in MPIDR EL1 for AArch64 state, and in MPIDR for AArch32 state:

- Affinity routing is a 32-bit value that is composed of four 8-bit affinity fields. These fields are the nodes a, b, c, and d.

- GICv3 using AArch64 state can support:

- A four level routing hierarchy, a.b.c.d.

- A three level routing hierarchy, 0.b.c.d.

- GICv3 using AArch32 state only supports three affinity levels.

- ICC\_CTLR\_EL3.A3V, ICC\_CTLR\_EL1.A3V, and GICD\_TYPER.A3V indicate whether four levels or three levels of affinity are implemented.

| ——Note — |  |

|----------|--|

|----------|--|

An implementation that requires four levels of affinity must only support AArch64 state.

The enumeration notation for specifying nodes in an affinity hierarchy is of the following form, where Affx is Affinity level x:

Aff3.Aff2.Aff1.Aff0

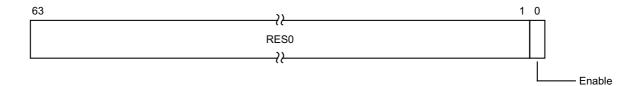

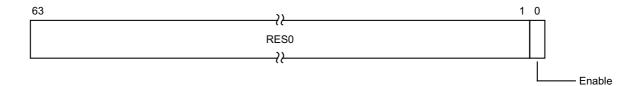

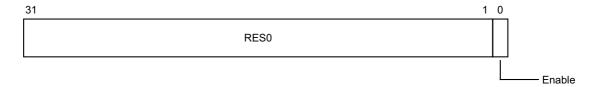

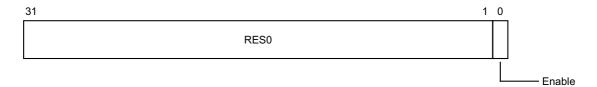

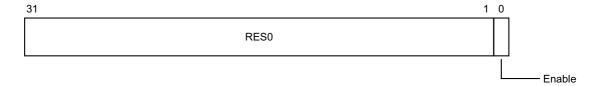

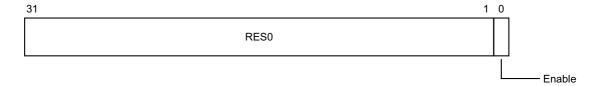

Affinity routing for a Security state is enabled in the Distributor, using the *Affinity Routing Enable* (ARE) bits. Affinity routing is enabled:

- For Secure interrupts, if GICD CTLR.ARE S is set to 1.

- For Non-secure interrupts, if the GICD CTLR.ARE NS bit is set to 1.

GICD CTLR.ARE S and GICD CTLR.ARE NS are RAO/WI if affinity routing is permanently enabled.

For the handling of physical interrupts when affinity routing is enabled, System register access must also be enabled, see *GIC System register access on page 11-197*. For the other cases, see Chapter 13 *Legacy Operation and Asymmetric Configurations*.

#### 2.3.1 Routing SPIs and SGIs by PE affinity

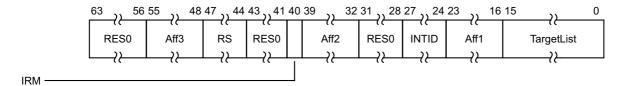

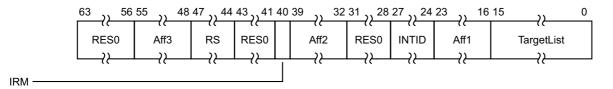

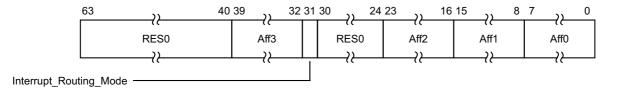

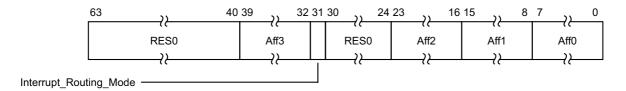

SPIs are routed using an affinity address and the routing mode information that is held in GICD\_IROUTER<n>. SGIs are routed using the affinity address and routing mode information that is written by software when it generates the SGI.

SGIs are generated using the following registers:

- ICC SGIOR EL1.

- ICC SGI1R EL1.

- ICC\_ASGI1R\_EL1.

Arm strongly recommends that only values in the range 0-15 are used at affinity level 0 to align with the SGI target list capability. See *Software Generated Interrupts on page 4-55*.

SPIs and SGIs are routed using different registers:

- SPIs are routed using GICD IROUTER<n>.Interrupt Routing Mode:

- If GICD\_IROUTER<n>.Interrupt\_Routing\_Mode is cleared to 0, SPIs are routed to a single PE specified by a.b.c.d.

- If GICD\_IROUTER<n>.Interrupt\_Routing\_Mode is set to 1, SPIs are routed to any PE defined as a participating node:

- The mechanisms by which the IRI is selects the target PE is IMPLEMENTATION DEFINED.

- When ICC\_CTLR\_EL3.PMHE == 1, or ICC\_CTLR\_EL1.PMHE == 1, the ICC\_PMR\_EL1 register associated with the PE might be used by the IRI to determine the target PE.

For more information about participating nodes, see *Participating nodes on page 2-36*.

- SGIs are routed using ICC SGI0R EL1.IRM, and ICC SGI1R EL1.IRM:

- If the IRM bit is set to 1, SGIs are routed to all participating PEs in the system, excluding the originating PE.

- If the IRM bit is cleared to 0, SGIs are routed to a group of PEs, specified by a.b.c.targetlist.

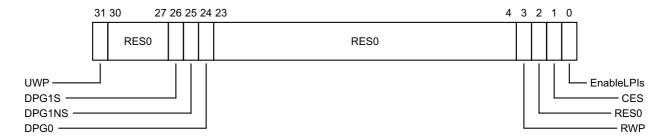

#### 2.3.2 Participating nodes

An enabled SPI configured to use the 1 of N distribution model can target a PE when:

- GICR\_WAKER.ProcessorSleep == 0 and the interrupt group of the interrupt is enabled on the PE.

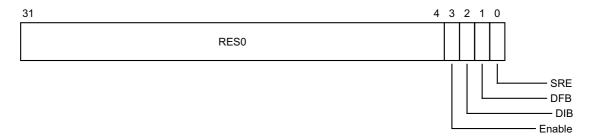

- GICD CTLR.E1NWF == 1.

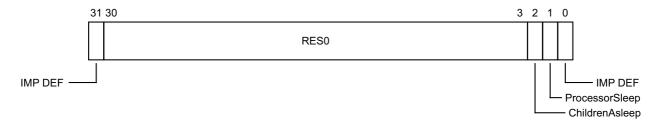

- GICR\_TYPER.DPGS == 1, and for the interrupt group of the interrupt, GICR\_CTLR.{DPG1S, DPG1NS, DPG0} == 0.