# Arm<sup>®</sup> System Memory Management Unit Architecture Specification SMMU architecture version 3

Document number ARM IHI 0070

Document version G.a

Document confidentiality Non-confidential

Copyright © 2016-2024 Arm Limited or its affiliates. All rights reserved.

# **Arm® System Memory Management Unit Architecture Specification**

# **Release information**

| Date        | Version | Changes                                                                                       |

|-------------|---------|-----------------------------------------------------------------------------------------------|

| 2024/Aug/15 | G.a     | Update with SMMUv3.4 architecture                                                             |

| 2024/Feb/22 | F.b     | <ul><li>Amendments and clarifications</li><li>Amendments and clarifications</li></ul>         |

| 2023/Sep/12 | F.a     | <ul> <li>Update with SMMU for RME DA architecture</li> </ul>                                  |

| 2023/Jan/31 | E.a     | <ul><li>Amendments and clarifications</li><li>Update with SMMU for RME architecture</li></ul> |

| 2021/Apr/30 | D.b     | <ul><li>Amendments and clarifications</li><li>Amendments and clarifications</li></ul>         |

| 2020/Aug/31 | D.a     | <ul> <li>Update with SMMUv3.3 architecture</li> </ul>                                         |

| 2019/Jul/18 | C.a     | <ul><li>Amendments and clarifications</li><li>Amendments and clarifications</li></ul>         |

| 2018/Mar/16 | C       | <ul> <li>Update with SMMUv3.2 architecture</li> </ul>                                         |

| 2017/Jun/15 | В       | <ul><li>Further amendments and clarifications</li><li>Amendments and clarifications</li></ul> |

| 2016/Oct/15 | A       | • First release                                                                               |

### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the use or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm Limited ("Arm"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether the subject matter of this document infringes any third party patents.

The content of this document is informational only. Any solutions presented herein are subject to changing conditions, information, scope, and data. This document was produced using reasonable efforts based on information available as of the date of issue of this document. The scope of information in this document may exceed that which Arm is required to provide, and such additional information is merely intended to further assist the recipient and does not represent Arm's view of the scope of its obligations. You acknowledge and agree that you possess the necessary expertise in system security and functional safety and that you shall be solely responsible for compliance with all legal, regulatory, safety and security related requirements concerning your products, notwithstanding any information or support that may be provided by Arm herein. In addition, you are responsible for any applications which are used in conjunction with any Arm technology described in this document, and to minimize risks, adequate design and operating safeguards should be provided for by you.

This document may include technical inaccuracies or typographical errors. THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, any patents, copyrights, trade secrets, trademarks, or other rights.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Reference by Arm to any third party's products or services within this document is not an express or implied approval or endorsement of the use thereof.

This document consists solely of commercial items. You shall be responsible for ensuring that any permitted use, duplication, or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of this document shall prevail.

The validity, construction and performance of this notice shall be governed by English Law.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its affiliates) in the US and/or elsewhere. Please follow Arm's trademark usage guidelines at https://www.arm.com/company/policies/trademarks . All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners.

Copyright © 2016-2024 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

PRE-20349

8 March 2024

# Arm<sup>®</sup> System Memory Management Unit Architecture Specification

|           | Arm€              | Release        | Memory Management Unit Architecture Specification                     | ii<br>ii |

|-----------|-------------------|----------------|-----------------------------------------------------------------------|----------|

| Chapter 1 | <b>Abo</b><br>1.1 |                | specification erences                                                 | 15       |

|           | 1.2               | Tern           | ns and abbreviations                                                  | 16       |

|           |                   | 1.2.1          | Inclusive Terminology Commitment                                      | 20       |

|           | 1.3               | Spe            | cification Scope                                                      | 21       |

|           | 1.4               | Fee            | dback                                                                 | 22       |

| Chapter 2 | Intro             | ductio         | n                                                                     |          |

|           | 2.1               |                | ory                                                                   | 25       |

|           | 2.2               |                | MÚv3.0 features                                                       | 26       |

|           | 2.3               | SMN            | MUv3.1 features                                                       | 28       |

|           | 2.4               | SMN            | MUv3.2 features                                                       | 29       |

|           | 2.5               |                | MUv3.3 features                                                       | 30       |

|           | 2.6               |                | MU for RME features                                                   | 31       |

|           | 2.7               |                | MU for RME DA features                                                | 32       |

|           |                   | 2.7.1          | Required features                                                     | 32       |

|           | 2.8               |                | MUv3.4 features                                                       | 33       |

|           | 2.9               | _              | mitted implementation of subsets of SMMUv3.x and SMMUv3.(x+1) archi-  |          |

|           |                   |                | ural features                                                         | 34       |

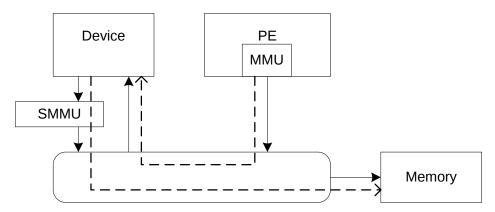

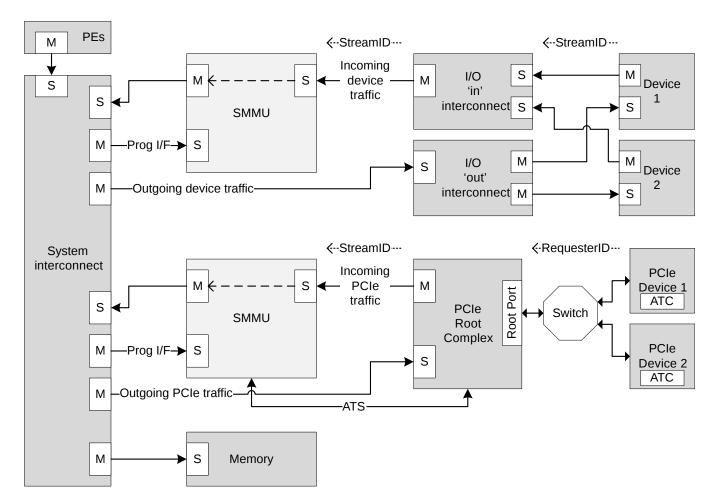

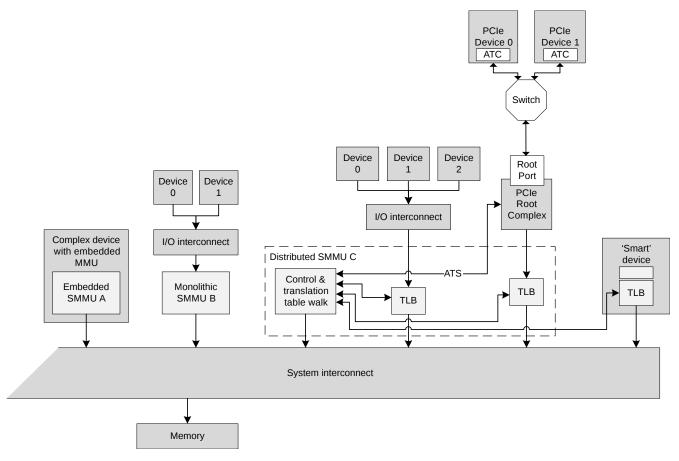

|           | 2.10              |                | tem placement                                                         | 35       |

| Chapter 3 | One               | ration         |                                                                       |          |

| Onapter 5 | 3.1               |                | ware interface                                                        | 38       |

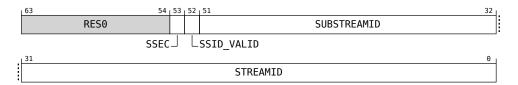

|           | 3.2               |                | am numbering                                                          | 40       |

|           | 3.3               |                | a structures and translation procedure                                | 41       |

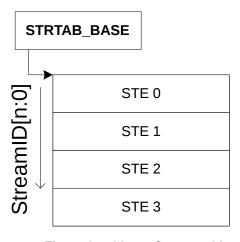

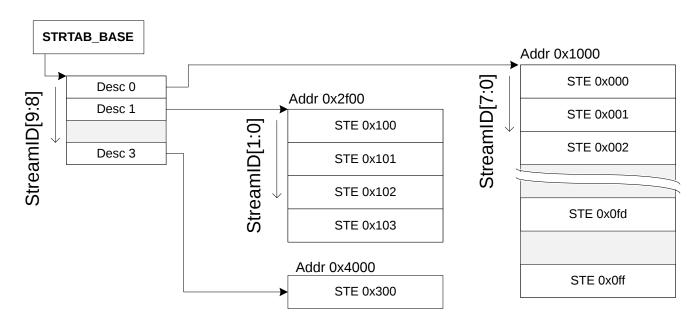

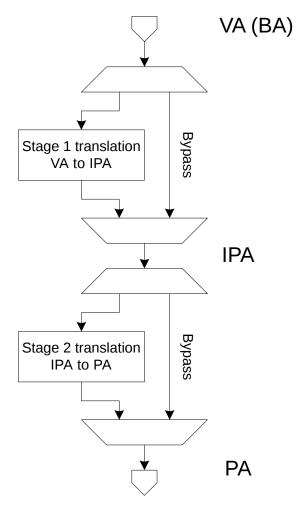

|           | 3.3               | 3.3.1          |                                                                       | 41       |

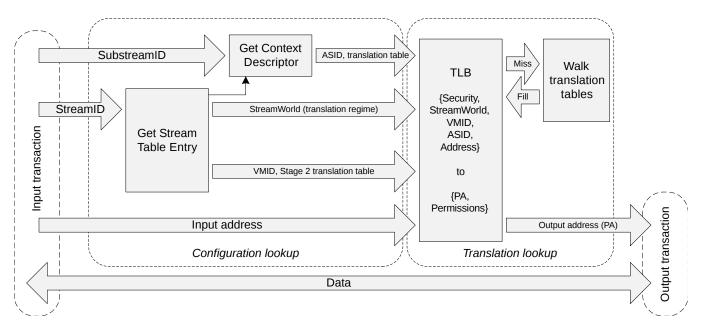

|           |                   | 3.3.2          | Stream IDe to Contact Descriptors                                     | 43       |

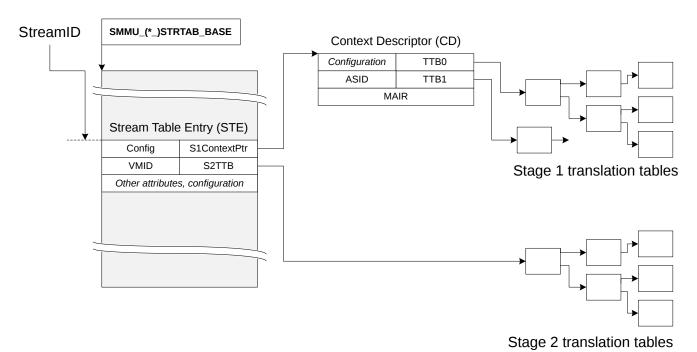

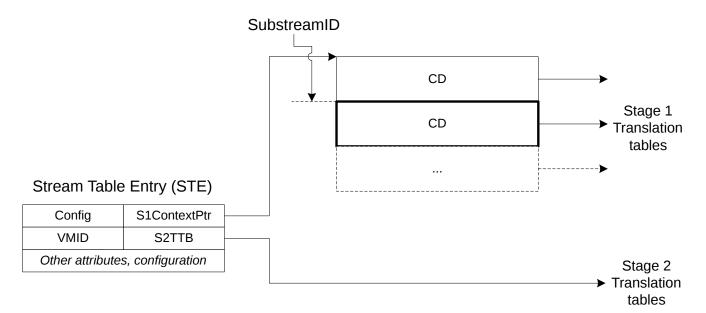

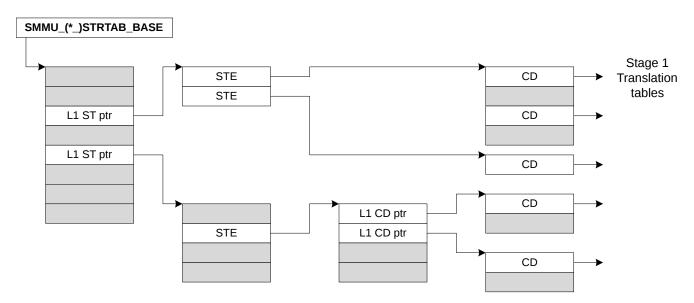

|           |                   | 3.3.2          | StreamIDs to Context Descriptors                                      | 48       |

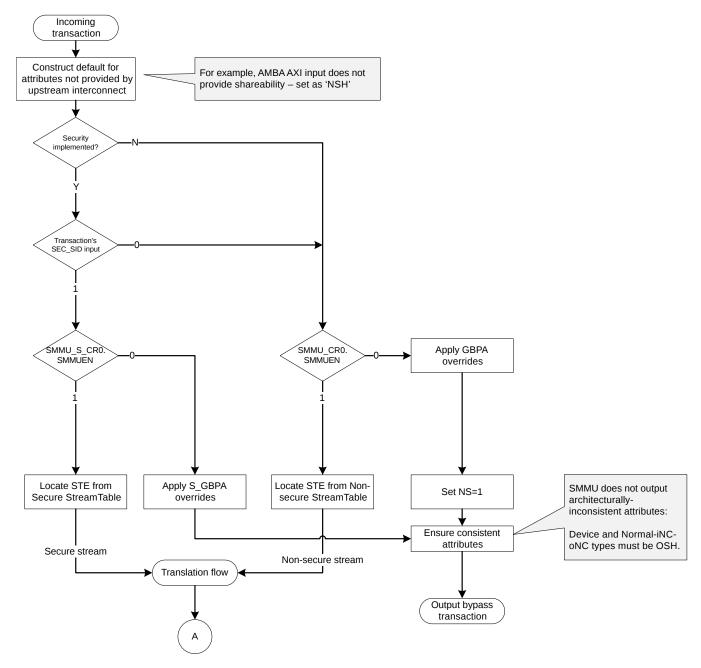

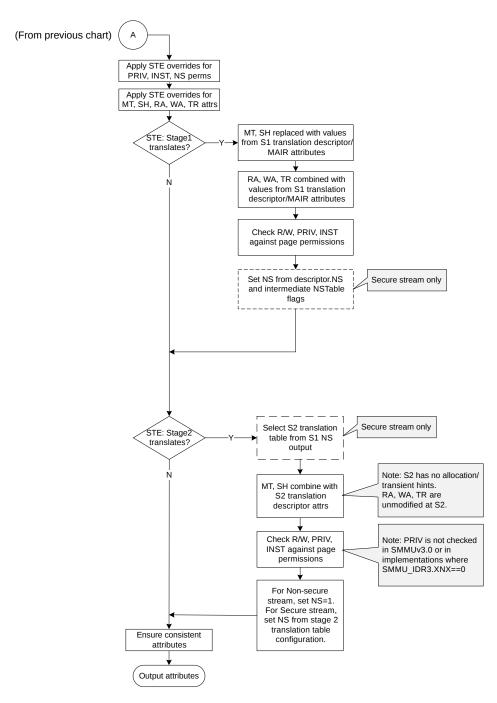

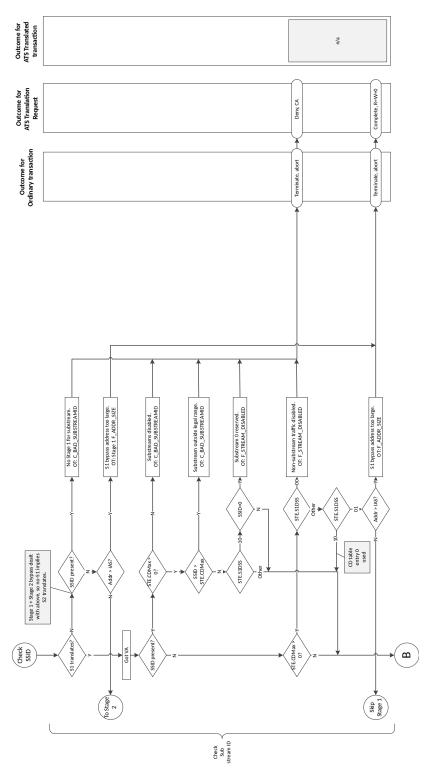

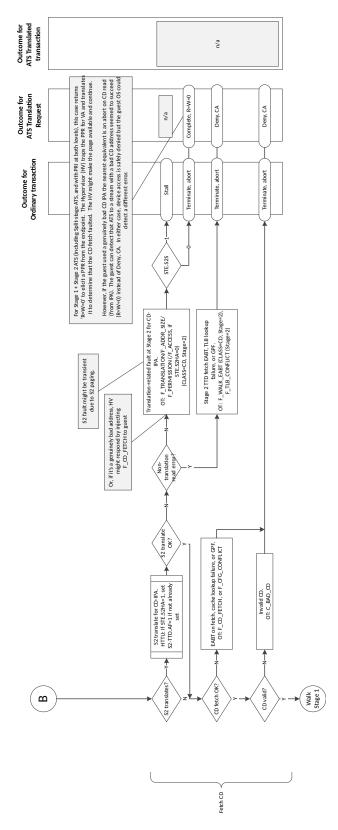

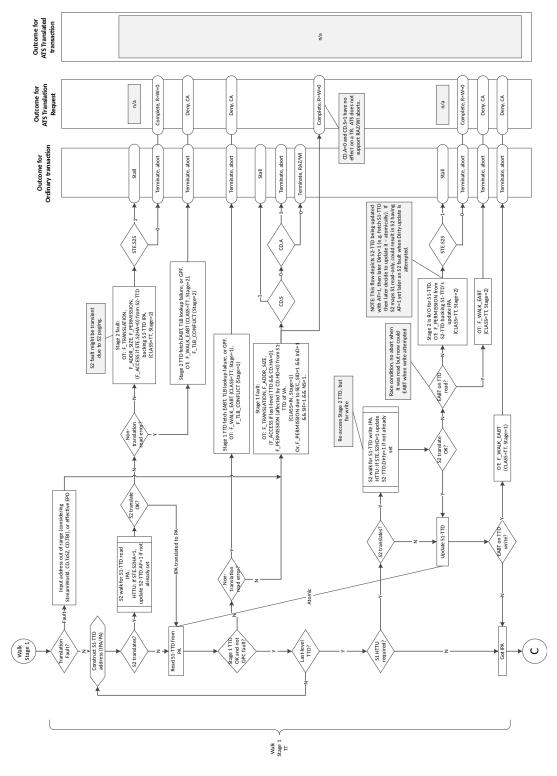

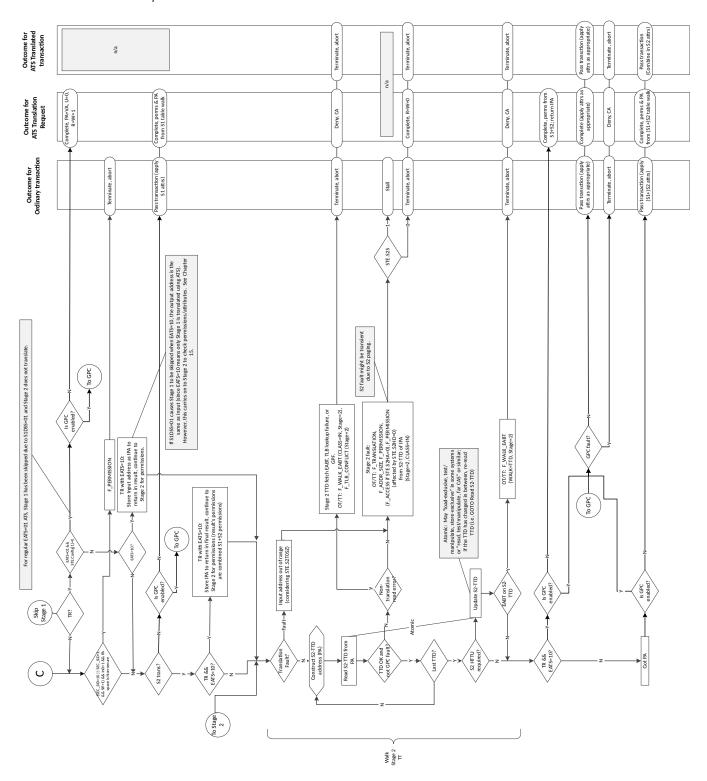

|           |                   |                | Configuration and Translation lookup                                  |          |

|           |                   | 3.3.4<br>3.3.5 | Transaction attributes: incoming, two-stage translation and overrides | 51<br>52 |

|           | 0.4               |                | Translation table descriptors                                         |          |

|           | 3.4               |                | ress sizes                                                            | 53       |

|           |                   | 3.4.1          | Input address size and Virtual Address size                           | 55       |

|           |                   | 3.4.2          | Address alignment checks                                              | 56       |

|           | 0.5               | 3.4.3          | Address sizes of SMMU-originated accesses                             | 56       |

|           | 3.5               |                | nmand and Event queues                                                | 59       |

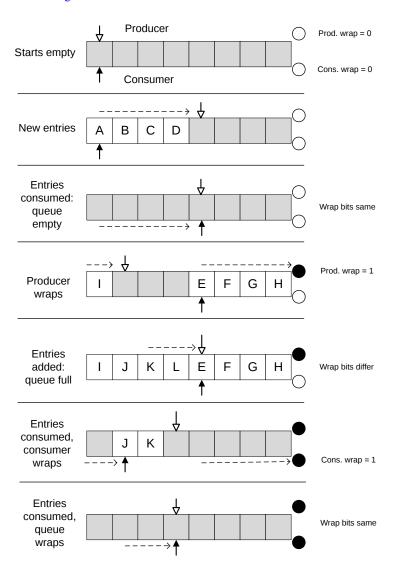

|           |                   | 3.5.1          | SMMU circular queues                                                  | 59       |

|           |                   | 3.5.2          | Queue entry visibility semantics                                      | 61       |

|           |                   | 3.5.3          | Event queue behavior                                                  | 61       |

|           |                   | 3.5.4          | Definition of event record write "Commit"                             | 62       |

|           |                   | 3.5.5          | Event merging                                                         | 62       |

|           |                   | 3.5.6          | Enhanced Command queue interfaces                                     | 63       |

|           | 3.6               |                | cture and queue ownership                                             | 66       |

|           | 3.7               | Prog           | gramming registers                                                    | 67       |

| 3.8   | Virtua | alization                                                                 | 68  |

|-------|--------|---------------------------------------------------------------------------|-----|

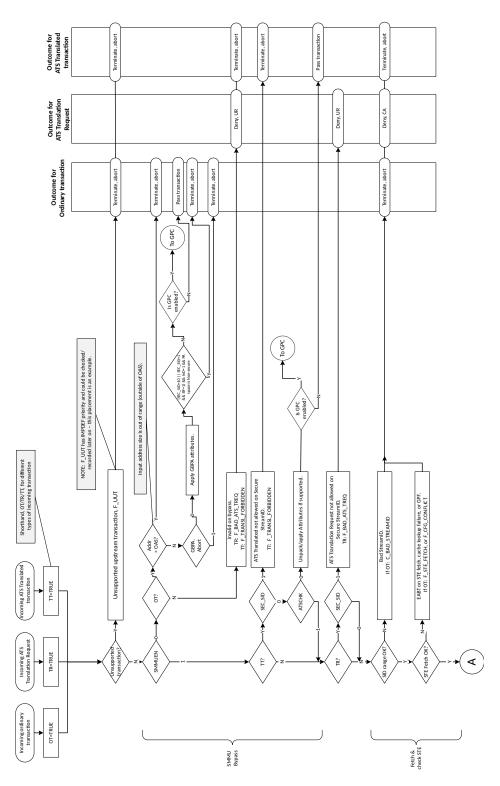

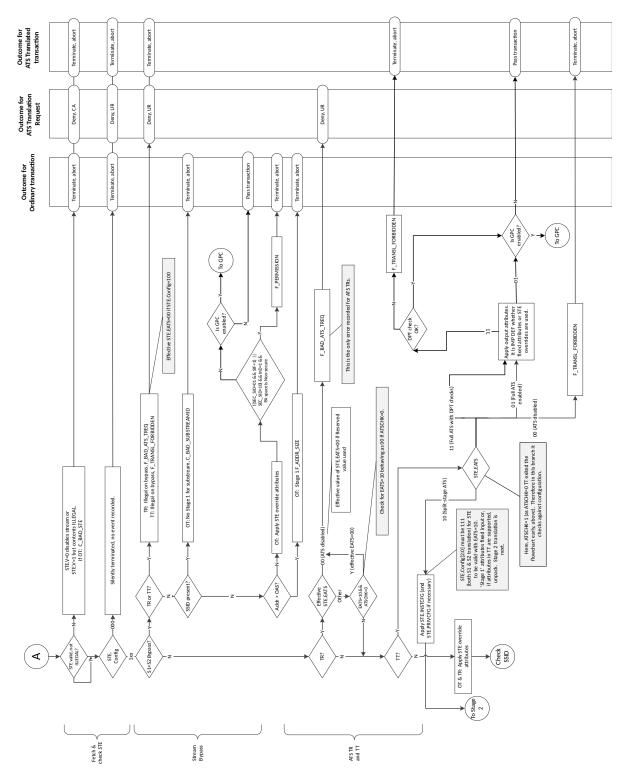

| 3.9   | Supp   | ort for PCI Express, PASIDs, PRI, and ATS                                 | 69  |

|       | 3.9.1  | ATS Interface                                                             | 69  |

|       | 3.9.2  | Changing ATS configuration                                                | 78  |

|       | 3.9.3  | SMMU interactions with CXL                                                | 79  |

|       | 3.9.4  | SMMU interactions with the PCIe IDE TLP prefix fields                     | 79  |

| 3.10  | Secu   | rity states support                                                       | 81  |

|       | 3.10.1 | StreamID Security state (SEC_SID)                                         | 81  |

|       | 3.10.2 | Support for Secure state                                                  | 82  |

|       | 3.10.3 | Support for Realm state                                                   | 86  |

| 3.11  |        | t, Enable and initialization                                              | 88  |

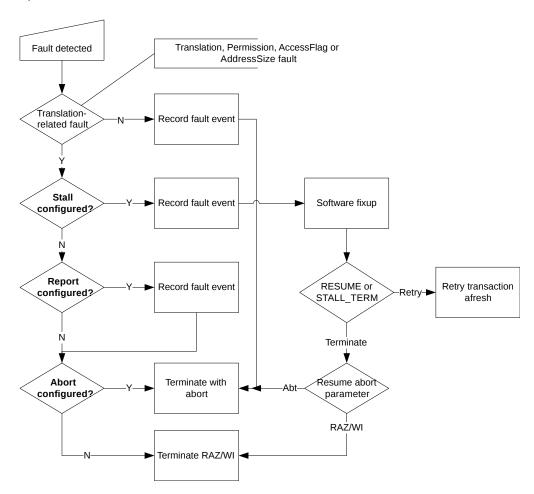

| 3.12  |        | models, recording and reporting                                           | 91  |

| J     | 3.12.1 | Terminate model                                                           | 93  |

|       | 3.12.2 | Stall model                                                               | 94  |

|       | 3.12.3 | Considerations for client devices using the Stall fault model             | 97  |

|       | 3.12.4 | Virtual Memory paging with SMMU                                           | 97  |

|       | 3.12.4 | Combinations of fault configuration with two stages                       | 98  |

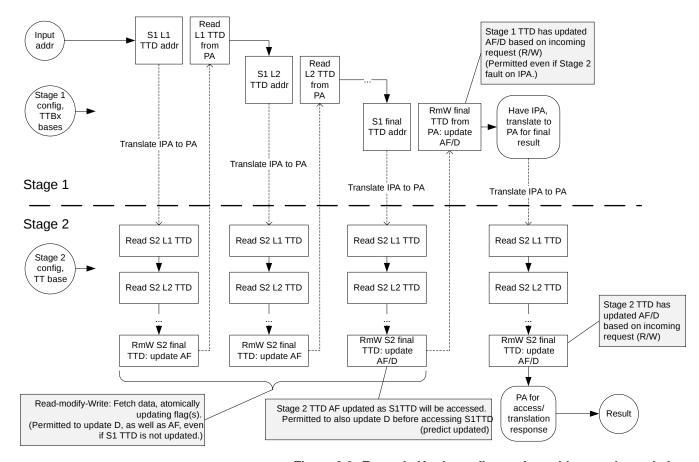

| 3.13  |        | lation tables and Access flag/Dirty state                                 |     |

| 3.13  | 3.13.1 |                                                                           | 100 |

|       |        | Software update of flags                                                  |     |

|       | 3.13.2 | Access flag hardware update                                               | 101 |

|       | 3.13.3 | Dirty state hardware update                                               | 101 |

|       | 3.13.4 | HTTU behavior summary                                                     | 103 |

|       | 3.13.5 | HTTU with two stages of translation                                       |     |

|       | 3.13.6 | Access flag in Table descriptors                                          |     |

|       | 3.13.7 | ATS, PRI and translation table flag update                                | 105 |

|       | 3.13.8 | Hardware flag update for Cache Maintenance Operations and Destruc-        |     |

|       | _      | tive Reads                                                                |     |

| 3.14  |        | ulative accesses                                                          |     |

| 3.15  |        | rency considerations and memory access types                              |     |

|       | 3.15.1 | Client devices                                                            |     |

| 3.16  | Embe   | edded Implementations                                                     | 110 |

|       | 3.16.1 | Changes to structure and queue storage behavior when fixed/preset $ . $ . | 110 |

| 3.17  |        | agging, VMIDs, ASIDs and participation in broadcast TLB maintenance.      |     |

|       | 3.17.1 | The Global flag in the translation table descriptor                       | 115 |

|       | 3.17.2 | Broadcast TLB maintenance from Armv8-A PEs with EL3 in AArch64 .          | 115 |

|       | 3.17.3 | Broadcast TLB maintenance from ARMv7-A PEs or Armv8-A PEs with            |     |

|       |        | EL3 using AArch32                                                         |     |

|       | 3.17.4 | Broadcast TLB maintenance in mixed AArch32 and AArch64 systems            |     |

|       |        | and with mixed ASID or VMID sizes                                         | 117 |

|       | 3.17.5 | EL2 ASIDs and TLB maintenance in EL2 Host (E2H) mode                      | 117 |

|       | 3.17.6 | VMID Wildcards                                                            | 118 |

|       | 3.17.7 | Broadcast TLB maintenance for GPT information                             | 119 |

|       | 3.17.8 | TLBInXS maintenance operations                                            | 119 |

| 3.18  | Interr | upts and notifications                                                    | 121 |

|       | 3.18.1 | MSI synchronization                                                       | 122 |

|       | 3.18.2 | Interrupt sources                                                         | 122 |

| 3.19  |        | r control                                                                 | 124 |

| 0     | 3.19.1 | Dormant state                                                             | 124 |

| 3.20  |        | and configuration cache conflict                                          | 125 |

| 5.20  | 3.20.1 | TLB conflict                                                              | 125 |

|       | 3.20.1 | Configuration cache conflicts                                             | 125 |

| 3.21  |        | ture access rules and update procedures                                   |     |

| J.Z I | 3.21.1 | Translation tables and TLB invalidation completion behavior               |     |

|       |        | ·                                                                         |     |

|       | 3.21.2 | Queues                                                                    |     |

|       | 3.21.3 | Configuration structures and configuration invalidation completion        | 130 |

|           | 3.22              | Destr<br>3.22.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ructive reads and directed cache prefetch transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135                                                                                                                                             |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                   | 3.22.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Permissions model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

|           | 0.00              | 3.22.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory types and Shareability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

|           | 3.23              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ory Tagging Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

|           | 0.04              | 3.23.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SMMU support for FEAT_MTE_PERM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

|           | 3.24              | 3.24.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ce Permission Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

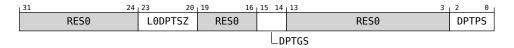

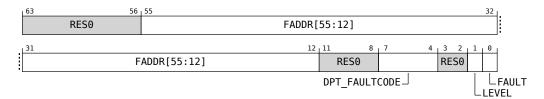

|           |                   | 3.24.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DPT caching behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |

|           |                   | 3.24.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DPT format and lookup process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

|           |                   | 3.24.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DPT lookup errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

|           |                   | 3.24.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DPT maintenance operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

|           |                   | 3.24.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Software guidance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

|           |                   | 3.24.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Considerations for configuring Split-stage ATS versus Full ATS with DPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 173                                                                                                                                             |

|           |                   | 0.24.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | checking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 150                                                                                                                                             |

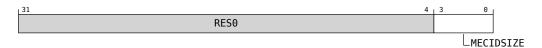

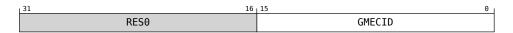

|           | 3.25              | Gran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ule Protection Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

|           | 0.20              | 3.25.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Client-originated accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

|           |                   | 3.25.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interactions with PCIe ATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                               |

|           |                   | 3.25.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SMMU-originated accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

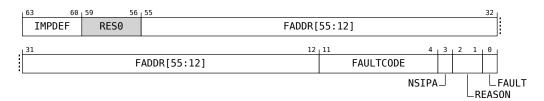

|           |                   | 3.25.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reporting of GPC faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

|           |                   | 3.25.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SMMU behavior if a GPC fault is active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |