# ARM® Architecture Reference Manual Supplement The Scalable Vector Extension (SVE), for ARMv8-A

**ARM**<sup>®</sup>

# ARM Architecture Reference Manual Supplement The Scalable Vector Extension (SVE), for ARMv8-A

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

**Change History**

| Date             | Issue | Confidentiality       | Change                  |

|------------------|-------|-----------------------|-------------------------|

| 31 March 2017    | A.a   | Non-Confidential Beta | Beta release            |

| 21 August 2017   | A.b   | Non-Confidential EAC  | EAC release             |

| 15 December 2017 | A.c   | Non-confidential      | EAC maintenance release |

| 21 December 2017 | A.d   | Non-confidential      | EAC maintenance release |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. You must follow the Arm's trademark usage guidelines http://www.arm.com/company/policies/trademarks.

Copyright © 2013-2017 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

In this document, where the term ARM is used to refer to the company it means "Arm or any of its subsidiaries as appropriate".

- The term ARM can refer to versions of the ARM architecture, for example ARMv8 refers to version 8 of the ARM architecture. The context makes it clear when the term is used in this way.

- This document describes only the ARMv8-A architecture profile. For the behaviors required by the previous version of this architecture profile, ARMv7-A, see the ARM® Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents

# ARM Architecture Reference Manual Supplement The Scalable Vector Extension (SVE), for ARMv8-A

|           | Prefa | ace                                       |      |

|-----------|-------|-------------------------------------------|------|

|           |       | About this book                           | viii |

|           |       | Using this book                           |      |

|           |       | Conventions                               |      |

|           |       | Additional reading                        |      |

|           |       | Feedback                                  |      |

| Chapter 1 | Intro | oduction                                  |      |

| Onapici i | 1.1   | About the SVE supplement                  | 1 1/ |

|           | 1.1   | About the Scalable Vector Extension       |      |

|           |       |                                           |      |

|           | 1.3   | Terminology                               | 1-10 |

| Chapter 2 | SVE   | Application Level Programmers' Model      |      |

|           | 2.1   | Registers                                 | 2-18 |

|           | 2.2   | Process state, PSTATE                     | 2-22 |

|           | 2.3   | SVE half-precision floating-point support | 2-24 |

| Chapter 3 | SVE   | System Level Programmers' Model           |      |

| •         | 3.1   | Exception model                           | 3-26 |

|           | 3.2   | Configurable vector length                |      |

| Chapter 4 | SVF   | Memory Model                              |      |

| Onaptor 4 | 4.1   | Atomicity                                 | 1_32 |

|           | 4.2   | Alignment support                         |      |

|           | 4.2   |                                           |      |

|           | _     | Endian support                            |      |

|           | 4.4   | Memory ordering                           | 4-35 |

|            | 4.5  | Device memory                               | 4-36 |

|------------|------|---------------------------------------------|------|

|            | 4.6  | Constrained unpredictable memory accesses   |      |

| Chapter 5  | SVE  | Instruction Set                             |      |

| -          | 5.1  | SVE assembler language                      | 5-40 |

|            | 5.2  | Instruction set overview                    |      |

| Chapter 6  | Syst | tem Registers                               |      |

| •          | 6.1  | System registers                            | 6-66 |

| Chapter 7  | SVE  | Debug                                       |      |

| •          | 7.1  | Self-hosted debug                           | 7-70 |

|            | 7.2  | External debug                              |      |

| Chapter 8  | SVE  | Performance Monitors Extension              |      |

| •          | 8.1  | Introduction                                | 8-74 |

|            | 8.2  | New performance monitor events              | 8-75 |

|            | 8.3  | Existing ARMv8-A PMU events affected by SVE | 8-76 |

| Appendix A | Reco | ommended SVE PMU events                     |      |

| • •        | A.1  | List of recommended PMU events              | A-78 |

|            | A.2  | Interesting combinations of SVE events      |      |

|            | A.3  | Instruction categories                      |      |

|            | Glos | ssary                                       |      |

# **Preface**

This preface introduces the ARM® Architecture Reference Manual Supplement, The Scalable Vector Extension (SVE), for ARMv8-A. It contains the following sections:

- About this book on page viii.

- Using this book on page ix.

- *Conventions* on page x.

- Additional reading on page xi.

- Feedback on page xii.

### **About this book**

This book is the ARM® Architecture Reference Manual Supplement, The Scalable Vector Extension (SVE), for ARMv8-A. This book describes the changes and additions to the ARMv8-A AArch64 architecture that are introduced by SVE, and therefore must be read in conjunction with the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.

# Using this book

This book is a supplement to the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile (DDI0487), and is intended to be used with it. The ARMv8-A ARM is the definitive source of information about ARMv8-A.

It is assumed that the reader is familiar with the ARMv8-A architecture.

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an overview of the SVE extension and definitions of key terminology. It outlines the key features of SVE and introduces the terminology used to describe the extension.

#### Chapter 2 SVE Application Level Programmers' Model

Read this for a description of the SVE Application Level Programmers' Model. This section must be read in conjunction with the section titled *The AArch64 Application Level Programmers' Model* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Chapter 3 SVE System Level Programmers' Model

Read this for a description of the SVE System Level Programmers' Model. This section must be read in conjunction with the section titled *The AArch64 System Level Programmers' Model* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Chapter 4 SVE Memory Model

Read this for a description of the SVE Memory Model. This section must be read in conjunction with the sections titled *The AArch64 Application Level Memory Model* and *The AArch64 System Level Memory Model* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Chapter 5 SVE Instruction Set

Read this for a description of the SVE Instruction Set Architecture. This section must be read in conjunction with the section titled *The AArch64 Instruction Set* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Chapter 6 System Registers

Read this for a description of the new SVE System registers and the pre-existing AArch64 System registers that are modified by SVE. This section must be read in conjunction with the section titled AArch64 System Register Descriptions in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.

#### Chapter 7 SVE Debug

Read this for a description of the SVE additions to the ARMv8-A AArch64 Debug Architecture. This section must be read in conjunction with the sections titled *AArch64 Self-hosted Debug* and *Debug State* in the *ARM*<sup>®</sup> *Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Chapter 8 SVE Performance Monitors Extension

Read this for a description of the SVE additions to the ARMv8-A AArch64 Performance Monitors Extension. This section must be read in conjunction with the section titled *The Performance Monitor Extension* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.*

#### Appendix A Recommended SVE PMU events

Read this for a list of the recommended PMU events for SVE and their descriptions.

## **Conventions**

The following sections describe conventions that this book can use:

- Typographical conventions.

- Numbers.

## **Typographical conventions**

The following table describes the typographical conventions:

#### Typographical conventions

| Style          | Purpose                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic         | Introduces special terminology, and denotes citations.                                                                                                                                                                                                                                                                                                                 |

| bold           | Denotes signal names, and is used for terms in descriptive lists, where appropriate.                                                                                                                                                                                                                                                                                   |

| monospace      | Used for assembler syntax descriptions, pseudocode, and source code examples.  Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.                                                                                                                |

| <and></and>    | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                                                                                                                                        |

| SMALL CAPITALS | Used for a few terms that have specific technical meanings, and are included in the glossary.                                                                                                                                                                                                                                                                          |

| Colored text   | <ul> <li>Indicates a link. This can be:</li> <li>A URL, for example http://developer.arm.com.</li> <li>A cross-reference, that includes the page number of the referenced information if it is not on the current page.</li> <li>A link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term.</li> </ul> |

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

# **Additional reading**

This section lists relevant publications from ARM and third parties.

See developer.arm.com, http://developer.arm.com, and the Infocenter, http://infocenter.arm.com, for access to ARM documentation.

## **ARM** publications

- ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile (ARM DDI 0487).

- System Register XML for ARMv8.3.

- A64 ISA XML for ARMv8.3.

## **Feedback**

ARM welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0584A.d.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

| Note                                                                                                        |

|-------------------------------------------------------------------------------------------------------------|

| ARM tests PDFs only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the appearance or behavior of |

| any document when viewed with any other PDF reader.                                                         |

# Chapter 1 **Introduction**

This chapter provides an introduction to the Scalable Vector Extension for the ARMv8-A architecture. This chapter contains the following sections:

- About the SVE supplement on page 1-14.

- About the Scalable Vector Extension on page 1-15.

- *Terminology* on page 1-16.

# 1.1 About the SVE supplement

This supplement must be read with the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile. Together, the manual and this supplement provide a full description of the ARMv8-A architecture, including the Scalable Vector Extension.

In general, this supplement describes only the architectural changes that are introduced by the Scalable Vector Extension.

This supplement does not contain any detailed instruction descriptions, pseudocode, or System register descriptions. Instead, this information is provided in a separate format, with links to this information appearing throughout the supplement.

#### 1.2 About the Scalable Vector Extension

The Scalable Vector Extension (SVE) is an optional extension to the ARMv8-A architecture, with a base requirement of ARMv8.2-A. SVE complements and does not replace AArch64 Advanced SIMD and floating-point functionality. If SVE is implemented, all SVE instructions are mandatory and the ARMv8.2-FP16 half-precision floating-point and the ARMv8.3-CompNum complex number instructions must be implemented.

SVE is defined for the AArch64 Execution state only, and adds:

- Support for wide vector and predicate registers.

- A set of instructions that operate on wide vectors and predicates.

- Some minor additions to the configuration and identification registers.

The key features that SVE provides are:

- Scalable vector length. See *Configurable vector length* on page 3-28.

- Predication. See *Predicate registers* on page 2-19.

- Gather-load and scatter-store. See *Load*, *store*, *and prefetch instructions* on page 5-41.

- Software-managed speculative vectorization. See First Fault Register, FFR on page 2-20.

# 1.3 Terminology

The following is an alphabetical list of key terminology and phrases that are used throughout this supplement.

#### **Active element**

An Active element is a vector element or predicate element that has been identified, by the value of the corresponding element of an instruction's Governing predicate being TRUE, as a source register element or destination register element to be used by the instruction. If an instruction is unpredicated, all of the vector elements or predicate elements are implicitly treated as active.

#### First active element

The First active element of a vector or predicate register is defined as the lowest numbered element that is an Active element.

#### First-fault load

SVE provides a First-fault option for some SVE vector load instructions. This option causes memory access faults to be suppressed if they do not occur as a result of the First active element of the vector. Instead, the FFR is updated to indicate which of the active vector elements were not successfully loaded. See *First Fault Register, FFR* on page 2-20 for more information about the FFR

#### Governing predicate

A Governing predicate defines the Active elements and Inactive elements of the source and destination registers for the corresponding instruction.

#### **Inactive element**

An Inactive element is a vector element or predicate element that has been identified, by the value of the corresponding element of an instruction's Governing predicate being FALSE, as an unused source register element or destination register element for the associated instruction.

#### Last active element

The Last active element of a vector or predicate register is defined as the highest numbered element that is an Active element.

#### Non-fault load

SVE provides a Non-fault option for some SVE vector load instructions. This option causes all memory access faults to be suppressed. Instead, the FFR is updated to indicate which of the active vector elements were not successfully loaded. See *First Fault Register*, *FFR* on page 2-20 for more information about the FFR.

# Chapter 2 SVE Application Level Programmers' Model

This chapter introduces the SVE Application Level Programmers' model. This chapter contains the following sections:

- Registers on page 2-18.

- *Process state, PSTATE* on page 2-22.

- SVE half-precision floating-point support on page 2-24.

# 2.1 Registers

#### 2.1.1 Vector registers

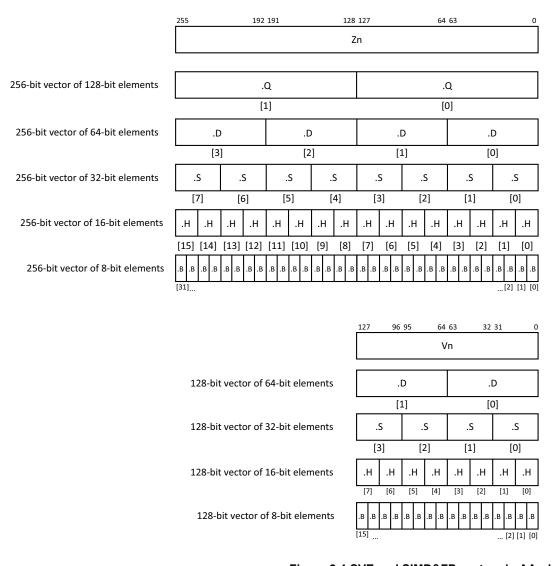

SVE includes 32 scalable vector registers, Z0-Z31. The SVE vector registers are all of equal size, where the size is an IMPLEMENTATION DEFINED multiple of 128 bits, up to an architectural maximum of 2048 bits. Each vector register can be subdivided into a number of 8-bit, 16-bit, 32-bit, 64-bit, or 128-bit vector elements. The vector element size for a given instruction is encoded in the opcode of the instruction. If the order in which operations are performed on vector elements has observable significance, then the vector elements must be processed in order of increasing element number.

Bits[127:0] of the SVE vector registers, Z0-Z31, are shared with the AArch64 SIMD&FP registers, V0-V31, so that Vn maps to Zn[127:0], as shown in Figure 2-1. If the SVE vector length at the current Exception level is greater than 128 bits, then any AArch64 instruction that writes to V0-V31 sets all the accessible bits above bit[127] of the corresponding SVE vector register to zero. See *Configurable vector length* on page 3-28 for more information.

Figure 2-1 SVE and SIMD&FP vectors in AArch64 state

#### 2.1.2 **Predicate registers**

SVE includes 16 scalable predicate registers, P0-P15. Each predicate register holds one bit per byte of a vector register, meaning that each predicate register is one-eighth of the size of a vector register. Therefore, each predicate register is an IMPLEMENTATION DEFINED multiple of 16 bits. Each predicate register can be subdivided into a number of 1, 2, 4, or 8-bit elements, where each predicate element corresponds to a vector element. If the lowest-numbered bit of a predicate element has a value of 1, the predicate element is TRUE, otherwise it is FALSE. For all instructions other than those listed in *Predicate permute* on page 5-62, the other bits of the predicate element are IGNORED on reads and set to zero on writes. A predicate element value with zeroes in all bits except the lowest-numbered bit is said to be in canonical form.

See *Predicate operations* on page 5-55 for descriptions of instructions that operate on predicate registers.

#### Governing predicate

Where an instruction supports predication, it is known as a predicated instruction. The predicate register that is used to determine the Active elements of a predicated instruction is known as the Governing predicate for that instruction. Predicated instructions can only use P0-P7 as the Governing predicate.

When a Governing predicate element is TRUE, then the corresponding vector or predicate register element is Active and is processed by the instruction, otherwise it is Inactive and takes no part in the operation of the instruction.

When a predicated instruction writes to a vector or predicate destination register, either:

- The Inactive elements in the destination are set to zero. This is known as zeroing predication.

- The Inactive elements in the destination retain their previous value. This is known as merging predication.

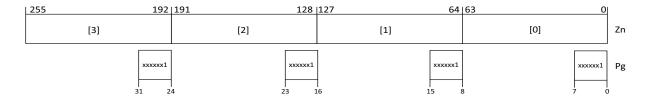

Figure 2-2 and Figure 2-3 show the relationship between a 256-bit implementation of an SVE vector register, Zn, and the associated 32-bit Governing predicate register, Pg. Figure 2-2 shows an SVE vector register of four 64-bit elements, with an associated Governing predicate register of four 8-bit elements. In this case, the lowest-numbered bit of each predicate element is 1, indicating that all elements of the vector register are Active.

Figure 2-2 256-bit vector, 4x64-bit packed elements

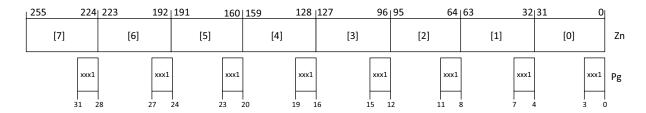

Figure 2-3 shows an SVE vector register of eight 32-bit elements, with an associated Governing predicate register of eight 4-bit elements. In this case, the lowest-numbered bit of each predicate element is 1, indicating that all elements of the vector register are Active.

Figure 2-3 256-bit vector, 8x32-bit packed elements

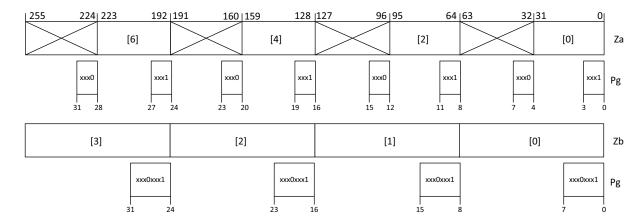

Figure 2-4 on page 2-20 shows a property of SVE predicates that allows a Governing predicate register to be interpreted differently when used for different vector element sizes. As defined in *Predicate registers*, an SVE predicate register contains one bit per byte of the corresponding SVE vector register and the predicate elements are numbered to match the equivalent vector elements.

Figure 2-4 shows Za, a 256-bit vector of 32-bit elements, where the values of the 4-bit Governing predicate elements indicate that the even-numbered vector elements are Active and the odd-numbered vector elements are Inactive. When the same Governing predicate register is used for Zb, a 256-bit vector of 64-bit elements, Pg is interpreted differently. Now, the values of the 8-bit Governing predicate elements indicate that all 64-bit elements of Zb are Active.

Figure 2-4 Governing predicate interpretation for different vector organizations

#### 2.1.3 First Fault Register, FFR

The First Fault Register, FFR, is a dedicated register that captures the cumulative fault status of a sequence of SVE First-fault and Non-fault vector load instructions. The format of the FFR is the same as the predicate registers. Bits in FFR are initialized to TRUE using the SETFFR instruction, and are indirectly cleared to FALSE as a result of an unsuccessful load of the corresponding, or lower-numbered, vector element. After a sequence of one or more SVE First-fault or Non-fault loads that follow a SETFFR instruction, the FFR contains a sequence of zero or more TRUE elements followed by zero or more FALSE elements. Bits in the FFR are never set to TRUE as a result of a vector load instruction, therefore the TRUE elements in the FFR indicate the shortest sequence of consecutive elements that could contain valid data loaded from memory.

The only instructions that read the FFR are:

- RDFFR

- RDFFRS

The only instructions that directly write the FFR are:

- WRFFR

- SETFFR

The FFR is a Special-purpose register as defined in the section titled *Special-purpose registers* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile*. This means that all direct and indirect reads and writes to the FFR appear to occur in program order relative to other instructions, without the need for explicit synchronization.

See Synchronous memory faults on page 3-26 for more information on SVE First-fault and Non-fault loads.

#### 2.1.4 Scalar registers

Certain SVE instructions generate a scalar result that is written to an AArch64 general-purpose register or to element[0] of a vector register. If an SVE instruction generates a scalar result that is narrower than the maximum destination register width, the upper bits of the destination register are set to zero.

| Note                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| See Registers in AArch64 Execution state in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile for more information about the AArch64 general-purpose and SIMD&FP registers. |

# 2.2 Process state, PSTATE

SVE overloads the AArch64 PSTATE condition flags. See the section titled *Process state*, *PSTATE* in the *ARM*\* *Architecture Reference Manual*, *ARMv8-A*, *for ARMv8-A architecture profile* for more information about the PSTATE condition flags. The condition flags can be set either by an explicit test of a predicate register or based on the result of an SVE predicate-generating and flag-setting instruction. Where present, a Governing predicate determines which predicate elements are to be tested. Some instructions use the condition flags to signal different events, but the most common SVE interpretations of the condition flags are shown in Table 2-1.

Table 2-1 SVE condition flags

| Flag | SVE Name | SVE Interpretation                                                                                                          |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| N    | First    | Has a value of 1 if the First active element was TRUE, otherwise has a value of 0.                                          |

| Z    | None     | Has a value of 1 if no Active element was TRUE, otherwise has a value of 0.                                                 |

| С    | Not last | Has a value of 0 if the Last active element was TRUE, otherwise has a value of 1.                                           |

| V    | -        | Cleared to 0 by the SVE flag-setting instructions, except <a href="CTERMEQ">CTERMEQ</a> and <a href="CTERMNE">CTERMNE</a> . |

The SVE assembler syntax defines a new set of condition code aliases. The condition code aliases and their associated meanings are described in Table 2-2.

**Table 2-2 Predicate condition flags**

| Condition test   | AArch64 name | SVE alias | SVE interpretation                                               |

|------------------|--------------|-----------|------------------------------------------------------------------|

| Z == 1           | EQ           | NONE      | No Active elements were TRUE                                     |

| Z == 0           | NE           | ANY       | An Active element was TRUE                                       |

| C == 1           | HS/CS        | NLAST     | The Last active element was not TRUE                             |

| C == 0           | L0/CC        | LAST      | The Last active element was TRUE                                 |

| N == 1           | MI           | FIRST     | The First active element was TRUE                                |

| N == 0           | PL           | NFRST     | The First active element was not TRUE                            |

| C == 1 && Z == 0 | HI           | PMORE     | An Active element was TRUE but not the Last active element       |

| C == 0    Z == 1 | LS           | PLAST     | The Last active element was TRUE or no Active elements were TRUE |

| V == 1           | VS           | -         | CTERM comparison failed, but end of partition reached            |

| V == 0           | VC           | -         | CTERM comparison succeeded, or end of partition not reached      |

| N == V           | GE           | TCONT     | CTERM termination condition not detected                         |

| N != V           | LT           | TST0P     | CTERM termination condition detected                             |

—— Note ———

For predicated instructions, it is the Governing predicate for the instruction that determines the Active and Inactive elements in the predicate source and destination registers. Any unpredicated SVE flag-setting instructions have an implicit Governing predicate, with all elements set to TRUE. This means that all elements in the predicate source and destination registers are considered Active for the purpose of setting the condition flags.

| 15   | [7 | 7] | [6 | 5] | [5 | 5] | [4 | 4] | [3 | 3] | [2 | 2] | [: | 1] | [( | D] OJ |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| Pd.H | х  | 0  | x  | 1  | х  | 0  | х  | 1  | х  | 1  | х  | 1  | х  | 0  | х  | 0     |

| Pg   | х  | 0  | х  | 0  | х  | 0  | х  | 1  | х  | 1  | х  | 1  | х  | 1  | х  | 0     |

| 15   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 0     |

Figure 2-5 First active element

In Figure 2-5, Pd. H is a predicate register containing eight 2-bit predicate elements and Pg is the Governing predicate In this case, element[1] of Pd. H is the First active element, not element[0].

# 2.3 SVE half-precision floating-point support

SVE inherits the following behaviors from ARMv8.2-FP16:

- The half-precision instructions are subject to the same floating-point exception traps and enables as apply to the equivalent SVE single-precision or double-precision instructions.

- FPCR.FZ has no effect on the half-precision instructions.

- FPCR.FZ16 enables Flush-to-zero mode for all of the half-precision instructions, but not for conversions between half-precision and single or double-precision.

- A half-precision value that is flushed to zero as a result of FPCR.FZ16 will not generate an Input Denormal exception that sets FPSR.IDC to 1.

SVE half-precision floating-point instructions support only IEEE 754-2008 half-precision format and ignore the value of the FPCR.AHP bit, behaving as if it has an Effective value of 0.

# Chapter 3 **SVE System Level Programmers' Model**

This chapter introduces the SVE System Level Programmers' model. This chapter contains the following sections:

- Exception model on page 3-26

- Configurable vector length on page 3-28

# 3.1 Exception model

SVE adds hierarchical trap and enable controls at EL3, EL2, and EL1. These controls are implemented using the following System register fields:

- <u>CPTR EL3</u>.EZ.

- <u>CPTR EL2.TZ</u>, when <u>HCR EL2.E2H</u> == 0.

- CPTR EL2.ZEN, when HCR EL2.E2H == 1.

- CPACR EL1.ZEN.

#### 3.1.1 SVE exception class

SVE defines the 0b011001 Exception class value, in <u>ESR\_ELx</u>.EC. The 0b011001 value is reported for exceptions that are due to attempted execution of SVE instructions and MRS/MSR instructions that access the ZCR\_ELx System registers when trapped due to the controls described in *Exception model*.

See ESR ELx for more details.

#### 3.1.2 SVE floating-point exception traps

SVE floating-point instructions only generate floating-point exceptions in response to floating-point operations performed on Active elements, but these are otherwise consistent with the behaviors described in the section titled Floating-point exceptions and exception traps in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile.

#### 3.1.3 MOVPRFX exception behavior

For detailed information about the SVE MOVPRFX (predicated) and MOVPRFX (unpredicated) instructions, see *Move prefix* on page 5-63. When a MOVPRFX instruction is used as described in *Move prefix* on page 5-63 and execution of the pair of instructions generates a synchronous exception or causes entry to Debug state, then the restart address that is recorded in ESR ELx or DLR EL0 is a CONSTRAINED UNPREDICTABLE choice of:

- If the MOVPRFX instruction has caused no change to the architectural state, the address of the MOVPRFX instruction.

- Otherwise, the address of the prefixed instruction.

Irrespective of the address that is recorded in <u>ESR\_ELx</u> or DLR\_EL0, if the prefixed instruction generates an Instruction Abort due to an MMU fault or synchronous External abort and the MOVPRFX does not generate an Instruction Abort, then the appropriate ESR\_ELx, FAR\_ELx, or HPFAR\_EL2 registers will record the syndrome information and address that is associated with the erroneous prefixed instruction fetch and not the MOVPRFX instruction fetch. If both instruction fetches would cause an Instruction abort, then the address of the MOVPRFX instruction is recorded in the appropriate FAR\_ELx register.

#### 3.1.4 Synchronous memory faults

The following mechanism is used to report a synchronous fault that is generated by a memory access that was performed as a result of an SVE load or store instruction. That is:

- The appropriate <u>ESR\_ELx</u>.EC field is updated with 0b100100 or 0b100101, depending on the Exception level from which the fault occurred.

- Depending on the Exception level handling the fault, the FAR\_EL1, FAR\_EL2, FAR\_EL3, or HPFAR\_EL2

System register is updated with the lowest address applicable to the Active element that the fault is reported

against.

- A Data Abort exception is then taken.

Where multiple faults arise from different addresses that are generated by the same instruction, the architecture does not prioritize between the different faults.

The SVE load and store instructions can generate a sequence of accesses that might not be completed as a result of an exception being taken during that sequence of accesses. On return from such an exception, a load or store instruction that has not been architecturally executed is restarted, meaning that one or more of the memory locations might be accessed multiple times. This can result in repeated accesses to a location that has been changed between the accesses, or that might be sensitive to the number of accesses.

SVE vector load and store instructions that generate a fault obey the sections titled *Definition of a precise exception* and *Effect of Data Aborts* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile*, with the following SVE-specific modifications:

- For SVE predicated vector stores, memory locations that are associated with Active elements that do not generate a fault are set to an UNKNOWN value. Memory locations that are associated with Inactive elements, or with Active elements that do generate a fault, are preserved.

- For SVE predicated vector loads that are not a First-fault or Non-fault load, all elements in the destination vector registers return an UNKNOWN value, irrespective of any predication, unless the destination register is a vector register that is also used as a base or index register by the instruction, in which case the original value of the register is preserved.

- For SVE Non-fault vector loads, an exception is not taken and the ESR\_ELx exception syndrome and FAR\_ELx and HPFAR\_EL2 fault address registers are not updated. When a Non-fault memory element access generates a fault or is suppressed for any other reason, the FFR predicate elements starting from that element number, up to and including the highest-numbered element, are set to FALSE. Since an FFR predicate element is never set to TRUE by an SVE vector load instruction, the fault indications are cumulative. Following execution of an SVE Non-fault vector load, each destination vector element contains either:

- If the corresponding FFR element is FALSE and it was an Active element, a CONSTRAINED UNPREDICTABLE choice of either zero, the value read from memory if the memory access for that element did not generate a fault and was not an access to Device memory, or the previous value of that vector element.

- If the corresponding FFR element is FALSE and it was an Inactive element, a CONSTRAINED UNPREDICTABLE choice of either zero, or the previous value of that vector element.

- If the corresponding FFR element is TRUE and it was an Active element, the value read from memory.

- If the corresponding FFR element is TRUE and it was an Inactive element, zero.

- For SVE First-fault vector loads, memory accesses due to the First active element are handled in the same way as for SVE predicated vector loads. If a memory access due to the First active element does not generate a fault, then the other elements are handled in the same way as for an SVE Non-fault vector load.

#### \_\_\_\_ Note \_\_\_\_\_

The term *fault* in this section includes any of the following results of a data access performed as a result of the execution of SVE vector load and store instructions:

- MMU fault

- Synchronous External abort, including synchronous parity or ECC error.

- Watchpoint debug event

Furthermore, an implementation is permitted to suppress the read of any Active element for an SVE Non-fault vector load, and any Active element other than the First active element for an SVE First-fault vector load.

#### 3.1.5 Asynchronous exception behavior

It is IMPLEMENTATION DEFINED whether SVE instructions can be interrupted by asynchronous exceptions. An interrupted SVE instruction on return from an asynchronous exception will restart and cannot resume.

# 3.2 Configurable vector length

Privileged Exception levels can use the ZCR\_EL1.LEN, ZCR\_EL2.LEN, and ZCR\_EL3.LEN System register fields to constrain the vector length at that Exception level and at less privileged Exception levels. SVE requires that an implementation must allow the vector length to be constrained to any power of two that is less than the maximum implemented vector length, but also permits an implementation to allow the vector length to be constrained to multiples of 128 that are not a power of two. It is IMPLEMENTATION DEFINED which of the permitted multiples of 128 are supported. See Table 3-1 for more information.

Table 3-1 Configurable vector lengths

|                                    | Additionally configurable vector lengths |                                                              |  |  |  |  |  |  |  |

|------------------------------------|------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| Maximum configurable vector length | Required                                 | Permitted                                                    |  |  |  |  |  |  |  |

| 128                                | -                                        | -                                                            |  |  |  |  |  |  |  |

| 256                                | 128                                      | -                                                            |  |  |  |  |  |  |  |

| 384                                | 128, 256                                 | -                                                            |  |  |  |  |  |  |  |

| 512                                | 128, 256                                 | 384                                                          |  |  |  |  |  |  |  |

| 640                                | 128, 256, 512                            | 384                                                          |  |  |  |  |  |  |  |

| 768                                | 128, 256, 512                            | 384, 640                                                     |  |  |  |  |  |  |  |

| 896                                | 128, 256, 512                            | 384, 640, 768                                                |  |  |  |  |  |  |  |

| 1024                               | 128, 256, 512                            | 384, 640, 768, 896                                           |  |  |  |  |  |  |  |

| 1152                               | 128, 256, 512, 1024                      | 384, 640, 768, 896                                           |  |  |  |  |  |  |  |

| 1280                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152                                     |  |  |  |  |  |  |  |

| 1408                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280                               |  |  |  |  |  |  |  |

| 1536                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280, 1408                         |  |  |  |  |  |  |  |

| 1664                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280, 1408, 1536                   |  |  |  |  |  |  |  |

| 1792                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280, 1408, 1536, 1664             |  |  |  |  |  |  |  |

| 1920                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280, 1408, 1536, 1664, 1792       |  |  |  |  |  |  |  |

| 2048                               | 128, 256, 512, 1024                      | 384, 640, 768, 896, 1152, 1280, 1408, 1536, 1664, 1792, 1920 |  |  |  |  |  |  |  |

If an unsupported vector length is requested in ZCR\_ELx, the implementation is required to select the largest supported vector length that is less than the requested length. This does not alter the value of ZCR\_ELx.LEN.

When executing at an Exception level that is constrained to use a vector length that is less than the maximum implemented vector length, then the bits beyond the constrained length of the vector registers, predicate registers, and FFR are inaccessible. On taking an exception from an Exception level that is more constrained to a target Exception level that is less constrained, or on writing a larger value to ZCR\_ELx.LEN, then the previously inaccessible bits of these registers that become accessible have a value of either zero or the value they had before executing at the more constrained size. The choice between these options is IMPLEMENTATION DEFINED and can vary dynamically.

If SVE instructions are disabled or trapped at ELx, or not available because that Exception level is in AArch32 state, then for all purposes other than a direct read, the ZCR\_ELx.LEN field has an Effective value of 0, which implies an SVE vector length of 128 bits.

If floating-point and SVE are both disabled, trapped, or not available at all Exception levels below the target Exception level, in the current Security state, then the accessible SVE register state at the target Exception level is preserved.

The ZCR\_ELx.LEN field constrains the SVE vector length to be no greater than (LEN+1)×128 bits, at Exception level ELx and below. See the ZCR\_EL1, ZCR\_EL2, and ZCR\_EL3 System register descriptions for more details.

An indirect read of ZCR\_EL1.LEN, ZCR\_EL2.LEN, or ZCR\_EL3.LEN appears to occur in program order relative to a direct write of the same register, without the need for explicit synchronization.

# Chapter 4 **SVE Memory Model**

This chapter introduces the changes to the ARMv8-A memory model introduced by SVE. This chapter contains the following sections:

- *Atomicity* on page 4-32.

- *Alignment support* on page 4-33.

- Endian support on page 4-34.

- *Memory ordering* on page 4-35.

- Device memory on page 4-36.

- Constrained unpredictable memory accesses on page 4-37.

# 4.1 Atomicity

SVE vector loads and stores are performed as a sequence of element accesses.

Further to the rules relating to the atomicity of SIMD loads and stores in the section titled *Atomicity in the ARM* architecture in the *ARM*<sup>®</sup> Architecture Reference Manual, *ARMv8-A, for ARMv8-A architecture profile*, the following behaviors are specific to accesses generated by SVE loads and stores:

- For predicated SVE vector element or structure loads, where an element address is aligned to the size of the element in memory, that access is treated as a single-copy atomic read.

- For predicated SVE vector element or structure stores, where an element address is aligned to the size of the element in memory, that access is treated as a single-copy atomic write.

- Unpredicated loads and stores of a vector or predicate register are regarded as a stream of byte accesses.

Single-copy atomicity of any access that is larger than a byte, within the series of byte accesses, is not guaranteed by the architecture.

# 4.2 Alignment support

Further to the rules relating to alignment of SIMD loads and stores in the sections titled *Alignment Support* and *Memory types and attributes* in the ARM\* Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile, the following behaviors are specific to accesses generated by SVE loads or stores when alignment checking is enabled. Alignment checking is enabled when SCTLR\_ELx.A has a value of 1 at the current Exception level or because the access is to any type of Device memory:

- For predicated SVE vector element and structure loads and stores:

- Alignment checks are based on the memory element access size, not the vector element size. See

Table 5-1 on page 5-41 for more information on SVE memory element access sizes.

- Inactive elements cannot cause an Alignment fault.

- For unpredicated SVE vector register loads or stores, the base address is checked for 16-byte alignment.

- For unpredicated SVE predicate register loads or stores, the base address is checked for 2-byte alignment.

Where an SVE load or store uses the current stack pointer, SP, as the base address, and stack alignment checking is enabled in SCTLR\_ELx at the current Exception level, then the stack pointer is checked for 16-byte alignment even when there are no Active elements to be transferred.

# 4.3 Endian support

Further to the rules relating to the byte and element order of SIMD loads and stores in the section titled *Data* endianness in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile, the following behaviors are specific to accesses generated by SVE loads and stores:

- For predicated SVE vector element and structure loads and stores, the data size that is used for endianness conversions is the memory element access size, not the vector element size.

- For unpredicated SVE vector register loads and stores, the vector is treated as containing byte elements that

are transferred in increasing element number order without any endianness conversion.

- For unpredicated SVE predicate register loads and stores, the predicate is treated as if each 8 predicate bits

in increasing element number order are held in a byte that is transferred without any endianness conversion.

- The endian conversion for SVE loads occurs before any sign-extension or zero-extension into a vector element. For SVE stores, the endian conversion occurs after any truncation from the vector element to the memory element access size.

#### 4.4 **Memory ordering**

The ARMv8 memory model described in the section titled Definition of the ARMv8 memory model in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile is relaxed for reads and writes generated by SVE load and store instructions as follows:

- An address dependency between two reads generated by SVE vector load instructions does not contribute to the Dependency-ordered-before relation.

- For a given observer, a pair of reads from the same location is not required to satisfy the internal visibility requirement if at least one of the reads was generated by an SVE load instruction.

- A single SVE vector store instruction that generates multiple writes to the same location ensures that those writes appear in the Coherence order for that location, in order of increasing vector element number. No other ordering restrictions apply to memory effects generated by the same SVE vector store instruction.

For all SVE instructions that load or store vector registers or predicate registers, there is no requirement for the memory system beyond the PE to be able to identify the size of the elements that are accessed by that load or store instruction, and, except for multiple writes to the same location, the order in which elements and registers are accessed is not architecturally defined. This applies to accesses to Normal memory and accesses to Device memory. See the section titled Memory types and attributes in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile for more information.

# 4.5 Device memory

For accesses by SVE instructions to a memory location with any Device memory type, the following additional exceptions apply:

- SVE vector prefetch instructions are guaranteed not to access Device memory.

- SVE Non-fault vector load instructions are guaranteed not to access Device memory, and an attempt by any

Active element to access Device memory is suppressed and reported in the FFR as described in Synchronous

memory faults on page 3-26.

- SVE First-fault vector load instructions can access Device memory only for the First active element. If that access does not generate a fault, then an attempt by any other Active element to access Device memory is suppressed and reported in the FFR as described in *Synchronous memory faults* on page 3-26.

- Hardware speculation of data accesses performed to a Device memory location is not permitted by the architecture, with the following exceptions:

- Explicit reads that are performed by an SVE load instruction are permitted to access bytes that are not explicitly accessed by the instruction, provided that the bytes accessed are in a naturally-aligned 64-byte window that contains at least 1 byte that is explicitly accessed by the instruction.

- Explicit reads that are performed by an SVE non-temporal load instruction from memory locations with the Gathering attributes are permitted to access bytes that are not explicitly accessed by the instruction, provided that the bytes accessed are in a naturally-aligned 128-byte window that contains at least 1 byte that is explicitly accessed by the instruction.

#### 4.6 CONSTRAINED UNPREDICTABLE memory accesses

The sections titled Crossing a page boundary with different memory types or Shareability attributes and Crossing a peripheral boundary with a Device access in the ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile define CONSTRAINED UNPREDICTABLE behaviors associated with memory accesses due to loads and stores. These behaviors also apply to SVE vector loads and stores as follows:

- An SVE unpredicated contiguous load or store instruction has the described constrained unpredictable behaviors if it accesses an address range that crosses a boundary between memory types, Shareability attributes, or peripherals.

- An SVE predicated contiguous load or store instruction has the described constrained unpredictable behaviors only if there are accesses associated with Active elements on both sides of a boundary between different memory types, Shareability attributes, or peripherals.

- An SVE predicated non-contiguous gather-load or scatter-store instruction has the described constrained unpredictable behaviors only if there is a memory access associated with any Active element that crosses a boundary between different memory types, Shareability attributes, or peripherals.

- Memory addresses associated with Inactive elements cannot trigger the constrained unpredictable behaviors described in this section.

- 4 SVE Memory Model 4.6 Constrained unpredictable memory accesses

## Chapter 5 **SVE Instruction Set**

This chapter introduces the SVE instruction set. This chapter contains the following sections:

- SVE assembler language on page 5-40.

- *Instruction set overview* on page 5-41.

## 5.1 SVE assembler language

The SVE assembler language extends the A64 assembler language, as described in the section titled *Structure of the A64 assembler language* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile*, as follows:

- SVE vector register names Z0-Z31 and predicate register names P0-P15 are added.

- The number of elements in a vector or predicate register is not specified as part of a vector register shape qualifier. For example, Z1.B is used rather than V1.16B.

- An element size qualifier is not required for the Governing predicate, Pg, except in the cases where the element size cannot be inferred from the source and destination element sizes. However, an assembler must accept a predicate element size qualifier, if provided, and check it for consistency with the other operands.

- Where appropriate, predicated instructions must indicate whether the inactive destination vector elements are to undergo zeroing predication or merging predication. The type of predication is indicated by use of a qualifier suffix to the Governing predicate, where:

- Pg/Z indicates zeroing predication.

- Pg/M indicates merging predication.

Some instructions identify Active and Inactive elements, but do not write to a destination vector register. For these instructions, the Governing predicate operand is used with no zeroing or merging qualifier.

- Many SVE instructions have destructive instruction encodings. To avoid ambiguity, the assembler language

frequently uses a constructive notation for these instructions, where the destination register is repeated in the

appropriate source operand position.

- The AArch64 load/store address syntax is extended to allow for vector register operands within the address specifier. See *Load, store, and prefetch instructions* on page 5-41 for more information.

- A set of SVE aliases is defined for the AArch64 condition codes. See Table 2-2 on page 2-22 for further details.

## 5.2 Instruction set overview

#### 5.2.1 Introduction

SVE adds a set of instructions to the existing ARMv8-A A64 instruction set. For details on the A64 instruction set, see the section titled *The A64 instruction set* in the *ARM® Architecture Reference Manual, ARMv8-A, for ARMv8-A architecture profile*. For a detailed listing of the instructions that are introduced by SVE, see the <u>SVE instruction index</u>. The SVE instructions break down into the following functional groups:

- Load, store, and prefetch instructions.

- Integer operations.

- Vector address calculation.

- Bitwise operations.

- Floating-point operations.

- Predicate operations.

- Move operations.

- Reduction operations.

The following sections provide an overview of these functional groups. For detailed information on each instruction, see the individual instruction descriptions.

## 5.2.2 Load, store, and prefetch instructions

SVE vector load and store instructions transfer data in memory to or from elements of one or more vector or predicate transfer registers. SVE also includes vector prefetch instructions that provide read and write hints to the memory system.

For SVE predicated load, store, and prefetch instructions, the memory element access size and type that is associated with each vector element is specified by a suffix to the instruction mnemonic, independently of the element size of the transfer registers. For example, LDISH. Table 5-1 shows the supported instruction suffixes for SVE load, store, and prefetch instructions.

Table 5-1 SVE memory element access instruction suffixes

| Instruction suffix | Memory element access size and type                    |

|--------------------|--------------------------------------------------------|

| В                  | Unsigned byte                                          |

| Н                  | Unsigned halfword or half-precision floating-point     |

| W                  | Unsigned word or single-precision floating-point       |

| D                  | Unsigned doubleword or double-precision floating-point |

| SB                 | Signed byte                                            |

| SH                 | Signed halfword                                        |

| SW                 | Signed word                                            |

The element size of the transfer registers is always greater than or equal to the memory element access size. When the element size of the transfer registers is strictly greater than the memory element access size, then these are referred to as unpacked data accesses. In the case of unpacked data accesses:

- For load instructions, each element access is sign-extended or zero-extended to fill the vector element, according to its size and type in Table 5-1.

- For store instructions, each vector element is truncated to the memory element access size.

Where the vector element size and the memory element access size are the same, then these are referred to as packed data accesses. Signed access types are not supported for packed data accesses. Packed and unpacked access sizes and types relate to the vector element size of the transfer registers, as defined in Table 5-2.

Table 5-2 Relationship between vector element size and memory element access size and type

| Vector element | Packed access suffix | Unpacked access suffixes |

|----------------|----------------------|--------------------------|

| .B             | В                    | -                        |

| .Н             | Н                    | B, SB                    |

| .S             | W                    | H, SH, B, SB             |

| .D             | D                    | W, SW, H, SH, B, SB      |

\_\_\_\_\_Note \_\_\_\_\_

For gather-load and scatter-store instructions, the vector element size can only be .S or .D. This means that any non-contiguous memory element access of less than a word is unpacked. Non-contiguous memory element accesses of a word can be either packed or unpacked, depending on the vector element size.

Load, store, and prefetch instructions consist of the following:

- Predicated single vector contiguous element accesses.

- Predicated multiple vector contiguous structure load/store on page 5-43.

- Predicated non-contiguous element accesses on page 5-44.

- *Predicated replicating element loads* on page 5-44.

- *Unpredicated vector register load/store* on page 5-45.

- *Unpredicated predicate register load/store* on page 5-45.

All predicated load instructions zero the Inactive elements of the destination vector, except for Non-fault loads and First-fault loads when the corresponding FFR element is FALSE.

Prefetch instructions provide hints to hardware and do not change architectural state. Therefore, a Governing predicate for a prefetch instruction provides an additional hint which indicates the memory locations to be prefetched. Prefetch instructions require an additional prfop> operand to be specified. SVE prefetch instructions support all of the prfop> listed in the section titled Prefetch memory in the ARMv8-A, for ARMv8-A architecture profile, except for the PLI prefetch operand types.

Load, store, and prefetch instructions that multiply a scalar index register or an index vector element by the memory element access size specify a shift type, followed by a shift amount in bits. The shift type can be one of LSL, SXTW, or UXTW. The shift amount is always Log<sub>2</sub> of the memory element access size, in bytes. The shift amount defaults to zero when the memory element access size is a byte. The shift type of LSL must be omitted if the shift amount is omitted.

When included as part of the assembler syntax for an instruction, MUL VL indicates that the specified immediate index value is multiplied by the size of the addressed vector or predicate in memory, measured in bytes, irrespective of predication. For a detailed description of the meaning of this assembler syntax for each instruction, see the appropriate subsection below.

——Note ——

When used in pseudocode, the symbol VL represents the vector length, measured in bits.

SVE load, store, and prefetch instructions do not support pre-indexed or post-indexed addressing.

#### Predicated single vector contiguous element accesses

Predicated contiguous load and store instructions access memory locations starting from an address that is defined by a scalar base register plus either:

- A scalar index register.

- An immediate index value that is in the range -8 to 7, inclusive. This defaults to zero if omitted.

Predicated contiguous prefetch instructions address memory locations in a similar manner, with the index being either:

- A scalar index register.

- An immediate index value that is in the range of -32 to 31, inclusive. This defaults to zero if omitted.

#### For this group of instructions:

- The immediate index value is a vector index, not an element index. The immediate index value is multiplied

by the number of vector elements, irrespective of predication, and then multiplied by the memory element

access size in bytes. The resulting offset is incremented following each element access by the memory

element access size.

- The scalar index register value is multiplied by the memory element access size in bytes. The index value is

incremented by one after each element access, but the scalar index register is not updated by the instruction.

- Load, LD1, and store, ST1, instructions support both packed and unpacked data accesses, with a scalar index register or an immediate index value.

- First-fault load, LDFF1, instructions support both packed and unpacked data accesses, with a scalar index register that defaults to XZR if omitted.

- Non-fault load, LDNF1, instructions support both packed and unpacked data accesses, with an immediate index

value.

- Non-temporal load, LDNT1, and store, STNT1, instructions support only packed data accesses, with a scalar index register or an immediate index value.

- Prefetch, PRF, instructions support only packed data accesses, with a scalar index register or an immediate index value.

- When alignment checking is enabled for loads and stores, the value of the base address register must be aligned to the memory element access size.

| Supported addressing modes    | Assembler syntax                                |

|-------------------------------|-------------------------------------------------|

| Scalar base + scalar index    | [ <xn sp>, <xm>{, LSL #<sh>}]</sh></xm></xn sp> |

| Scalar base + immediate index | [ <xn sp>{, #<simm>, MUL VL}]</simm></xn sp>    |

## Predicated multiple vector contiguous structure load/store

Structure load, LD2, LD3, LD4, instructions read N consecutive memory locations to the same-numbered element in each of the N vector transfer registers, where N = 2, 3, or 4, respectively. Structure store, ST2, ST3, ST4, instructions write from the same-numbered element in each of the N consecutive vector transfer registers to N consecutive memory locations. The starting address is defined by a scalar base register plus either:

- A scalar index register.

- An immediate index that is a multiple of N, in the range -8×N to 7×N, inclusive. This defaults to zero if omitted.

#### For this group of instructions:

- The immediate index value is a vector index, not an element index. The immediate index value is multiplied by the number of vector elements, irrespective of predication, and then multiplied by the memory element access size in bytes. The resulting offset is incremented following each element access by the memory element access size.

- The scalar index register value is multiplied by the memory element access size in bytes. Following each

element access, the index value is incremented by one but the instruction does not update the scalar index

register.

- Each predicate element applies to a single structure in memory, or equivalently to the same element number within each of the two, three, or four transferred vector registers.

- These instructions support packed data accesses only.

When alignment checking is enabled for loads and stores, the base address must be aligned to the element access size.

| Supported addressing modes    | Assembler syntax                                |

|-------------------------------|-------------------------------------------------|

| Scalar base + scalar index    | [ <xn sp>, <xm>{, LSL #<sh>}]</sh></xm></xn sp> |

| Scalar base + immediate index | [ <xn sp>{, #<simm>, MUL VL}]</simm></xn sp>    |

#### Predicated non-contiguous element accesses

Predicated non-contiguous element accesses address non-contiguous memory locations that are specified by either:

- A scalar base register plus a vector of indices or offsets.

- A vector of base addresses plus an immediate byte offset. The immediate byte offset is a multiple of the

memory element access size, in the range 0 to 31 times the memory element access size, inclusive, and

defaults to zero if omitted.

For this group of instructions:

- Vector registers used as part of the address must specify a vector element size of 32 bits or 64 bits, .S or .D. For load and store instructions, the transfer register must specify the same vector element size.

- If the index vector register contains 32-bit index values then the lowest 32 bits of each index vector element can either be zero-extended or sign-extended to 64 bits.

- For load and store instructions, the index vector elements are then optionally multiplied by the memory element access size, in bytes, if a shift amount is specified. For prefetch instructions the index vector elements are always multiplied by the memory element access size, in bytes.

- Load, LD1, store, ST1, and First-fault load, LDFF1, instructions support packed and unpacked data accesses. Prefetch, PRF, instructions only specify the memory element access size.

- When alignment checking is enabled for loads and stores, the computed virtual address of each element must be aligned to the memory element access size.

|                                   | Assembler syntax                                       |                                                        |

|-----------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| Supported addressing modes        | 64-bit elements                                        | 32-bit elements                                        |

| Scalar base + 64-bit vector index | [ <xn sp>, <zm>.D{, LSL #<sh>}]</sh></zm></xn sp>      | -                                                      |

| Scalar base + 32-bit vector index | [ <xn sp>, <zm>.D, (S U)XTW{ #<sh>}]</sh></zm></xn sp> | [ <xn sp>, <zm>.S, (S U)XTW{ #<sh>}]</sh></zm></xn sp> |

| Vector base + immediate offset    | [ <zn>.D{, #<uimm>}]</uimm></zn>                       | [ <zn>.S{, #<uimm>}]</uimm></zn>                       |

## Predicated replicating element loads

The load and replicate instructions read one or more contiguous memory locations starting from an address that is defined by a scalar base register plus either:

- A scalar index register.

- An immediate byte offset.

This defaults to zero if omitted.

For this group of instructions:

The LD1R instructions load a single element value and replicate it into all Active elements of the destination

vector. These instructions support packed and unpacked data accesses. These instructions use an immediate

byte offset that is a multiple of the memory element access size, in the range 0 to 63 times the memory

element access size, inclusive.

- The LD1RQ instructions load a predicated 128-bit quadword vector segment from contiguous element values and replicate that segment into all segments of the destination vector. These instructions support only packed data accesses. These instructions can use a scalar index register that is multiplied by the memory element access size, or an immediate byte offset that is a multiple of 16, in the range of -128 to 112, inclusive.

- When alignment checking is enabled for loads and stores, the base address must be aligned to the memory element access size.

| Supported addressing modes     | Assembler syntax                                |

|--------------------------------|-------------------------------------------------|

| Scalar base + scalar index     | [ <xn sp>, <xm>{, LSL #<sh>}]</sh></xm></xn sp> |

| Scalar base + immediate offset | [ <xn sp>{, #<imm>}]</imm></xn sp>              |

#### Unpredicated vector register load/store

The unpredicated vector register load, LDR, and store, STR, instructions transfer a single vector register from or to memory locations that are specified by a scalar base register plus an immediate index value that is in the range -256 to 255, inclusive. The immediate index value defaults to zero if omitted. For this group of instructions:

- The immediate index value is a vector index, not an element index. The immediate index value is multiplied by the current vector register length in bytes.

- The data transfer is performed as a contiguous stream of byte accesses in ascending element order, without endianness conversion.

- When alignment checking is enabled for loads and stores, the base address must be 16-byte aligned.

| Supported addressing mode     | Assembler syntax                             |

|-------------------------------|----------------------------------------------|

| Scalar base + immediate index | [ <xn sp>{, #<simm>, MUL VL}]</simm></xn sp> |

#### Unpredicated predicate register load/store

The unpredicated predicate register load, LDR, and store, STR, instructions transfer a single predicate register from or to memory locations that are specified by a scalar base register plus an immediate index value that is in the range -256 to 255, inclusive. The immediate index value defaults to zero if omitted. For this group of instructions:

- The immediate index value is a predicate index, not an element index. The immediate index value is multiplied by the current predicate register length, in bytes.

- The data transfer is performed as a contiguous stream of byte accesses, each byte containing 8 consecutive predicate bits, in ascending bit and element order, without endian conversion.

- When alignment checking is enabled for loads and stores, the base address must be 2-byte aligned.

| Supported addressing mode     | Assembler syntax                             |

|-------------------------------|----------------------------------------------|

| Scalar base + immediate index | [ <xn sp>{, #<simm>, MUL VL}]</simm></xn sp> |

## 5.2.3 Vector move operations

#### Element move and broadcast

These instructions copy data from scalar registers, immediate values, and other vectors to selected vector elements. The copied data might be in an integer or floating-point format.

Table 5-3 Element move and broadcast instructions

| Mnemonic | Instruction                                                           | See         |

|----------|-----------------------------------------------------------------------|-------------|

| СРҮ      | Copy signed integer immediate to vector elements                      | CPY         |

|          | Copy general-purpose register to vector elements                      | <u>CPY</u>  |

|          | Copy SIMD&FP scalar register to vector elements                       | <u>CPY</u>  |

| DUP      | Broadcast signed immediate to vector elements                         | DUP         |

|          | Broadcast general-purpose register to vector elements                 | DUP         |

| FCPY     | Copy 8-bit floating-point immediate to vector elements                | <u>FCPY</u> |

| FDUP     | Broadcast 8-bit floating-point immediate to vector elements           | <u>FDUP</u> |

| FMOV     | Move floating-point +0.0 to vector elements (unpredicated)            | <u>FMOV</u> |

|          | Move floating-point +0.0 to vector elements (predicated)              | <u>FMOV</u> |

|          | Move 8-bit floating-point immediate to vector elements (unpredicated) | <u>FMOV</u> |

|          | Move 8-bit floating-point immediate to vector element (predicated)    | <u>FMOV</u> |

| MOV      | Move signed integer immediate to vector elements (unpredicated)       | MOV         |

|          | Move signed integer immediate to vector elements (predicated)         | MOV         |

|          | Move general-purpose register to vector elements (unpredicated)       | MOV         |

|          | Move general-purpose register to vector elements (predicated)         | MOV         |

|          | Move SIMD&FP scalar register to vector elements (unpredicated)        | MOV         |

|          | Move SIMD&FP scalar register to vector elements (predicated)          | MOV         |

|          | Move vector register (unpredicated)                                   | MOV         |

|          | Move vector register (predicated)                                     | MOV         |

| SEL      | Select vector elements from two vectors                               | <u>SEL</u>  |