Microsystem Components Handbook, Volume I

## Microsystem Components Handbook

Microprocessors and Peripherals Volume I

1985

### LITERATURE

p.

In addition to the product line handbooks listed below, the INTEL PRODUCT GUIDE (no charge, Order No. 210846-003) provides an overview of Intel's complete product lines and customer services.

Consult the INTEL LITERATURE GUIDE (Order No. 210620) for a listing of Intel literature. TO ORDER literature in the U.S., write or call the INTEL LITERATURE DEPARTMENT, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only). TO ORDER literature from international locations, contact the nearest Intel sales office or distributor (see listings in the back of most any Intel literature).

Use the order blank on the facing page or call our TOLL FREE number listed above to order literature. Remember to add your local sales tax.

### **1985 HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| <b>QUALITY/RELIABILITY HANDBOOK (Order No. 210997-001)</b><br>Contains technical details of both quality and reliability programs and principles.     | *U.S. PRICE<br>\$15.00 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| CHMOS HANDBOOK (Order No. 290005-001)<br>Contains data sheets only on all microprocessor, peripheral, microcontroller and<br>memory CHMOS components. | \$12.00                |

| MEMORY COMPONENTS HANDBOOK (Order No. 210830-004)                                                                                                     | \$18.00                |

| TELECOMMUNICATION PRODUCTS HANDBOOK (Order No. 230730-003)                                                                                            | \$12.00                |

| MICROCONTROLLER HANDBOOK (Order No. 210918-003)                                                                                                       | \$18.00                |

| MICROSYSTEM COMPONENTS HANDBOOK (Order No. 230843-002)<br>Microprocessors and peripherals—2 Volume Set                                                | \$25.00                |

| DEVELOPMENT SYSTEMS HANDBOOK (Order No. 210940-003)                                                                                                   | \$15.00                |

| OEM SYSTEMS HANDBOOK (Order No. 210941-003)                                                                                                           | \$18.00                |

| SOFTWARE HANDBOOK (Order No. 230786-002)                                                                                                              | \$12.00                |

| MILITARY HANDBOOK (Order No. 210461-003)<br>Not available until June.                                                                                 | \$15.00                |

| <b>COMPLETE SET OF HANDBOOKS (Order No. 231003-002)</b><br>Get a 25% discount off the retail price of \$160.                                          | \$120.00               |

\*U.S. Price Only

## intel®

| U.S. LITERATURE ORDER FORM                                                                                                                                                                                                            |                                                                        |                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|

| NAME:                                                                                                                                                                                                                                 |                                                                        | TITLE:                                                           |

| COMPANY:                                                                                                                                                                                                                              |                                                                        |                                                                  |

| ADDRESS:                                                                                                                                                                                                                              |                                                                        |                                                                  |

| CITY:                                                                                                                                                                                                                                 | STATE:                                                                 | ZIP:                                                             |

| COUNTRY:                                                                                                                                                                                                                              |                                                                        |                                                                  |

| PHONE NO.: ()                                                                                                                                                                                                                         |                                                                        |                                                                  |

| ORDER NO.                                                                                                                                                                                                                             | TITLE                                                                  | QTY. PRICE TOTAL                                                 |

| POSTAGE AND HANDLING:         Add appropriate postage         and handling to subtotal         10% U.S.         20% Canada                                                                                                            | Your Loca                                                              | <pre> × =</pre>                                                  |

| Pay by Visa, MasterCard, Check or Mor<br>have a \$50.00 minimum.                                                                                                                                                                      | ey Order, payable to fille                                             | I Literature. Furchase Orders                                    |

| Visa Account No MasterCard Signature:                                                                                                                                                                                                 |                                                                        | Expiration<br>Date                                               |

| Mail To: Intel Literature Distribution<br>Mail Stop SC6-714<br>3065 Bowers Avenue<br>Santa Clara, CA 95051.<br>For information on quantity discounts,<br>TOLL-FREE NUMBER: (800) 548-4725<br>Prices good until 12/31/85.<br>Source HB | Customers outside the tact the local Intel Sale the back of this book. | U.S. and Canada should con-<br>s Office or Distributor listed in |

Mail To: Intel Literature Distribution Mail Stop SC6-714 3065 Bowers Avenue Santa Clara, CA 95051.

## intel

### MICROSYSTEM COMPONENTS HANDBOOK

1985

1

About Our Cover: The design on our front cover is an abstract portrayal of microprocessors and associated peripherals as the building blocks which provide total systems development solutions. Intel superior technology and reliability provide easier solutions to specific development problems thereby cutting "time-to-market" and creating a greater market share. Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, <sup>2</sup>, ICE, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, I<sub>m</sub>, iMDDX, IMMX, Insite, Intel, int<sub>e</sub>I, BOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, IPDS, iRMX, ISBC, iSBX, iSDM, ISXM, KEPROM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, OpeNET, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Ripplemode, RMX/80, RUPI, Seamless, SLD, SYSTEM 2000, and UPI, and the combination of ICE, ICS, IRMX, ISBC, iSBX, MCS, or UPI and a numerical suffix

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

©INTEL CORPORATION 1984

### **Table of Contents**

### CHAPTER 1 OVERVIEW

٦

| Introduction | · · · · · · · · · · · · · · · · · · · | 1-1 |

|--------------|---------------------------------------|-----|

### **CHAPTER 2**

| MCS®-80/85 MICROPROCESSORS                                                    |       |

|-------------------------------------------------------------------------------|-------|

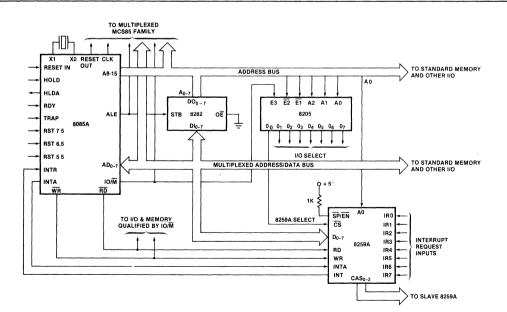

| 8080A/8080A-1/8080A-2, 8-Bit N-Channel Microprocessor                         | 2-1   |

| 8085AH/8085AH-2/8085AH-1 8-Bit HMOS Microprocessors                           | 2-10  |

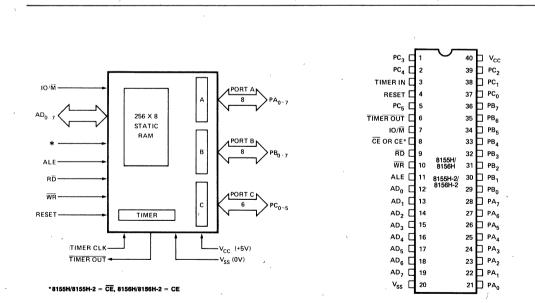

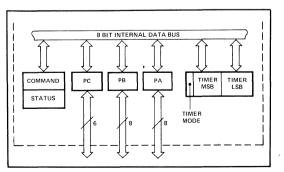

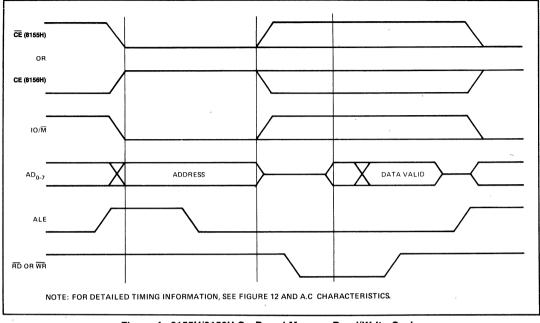

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and Timer | 2-26  |

| 8185/8185-2 1024 x 8-Bit Static RAM for MCS-85                                | 2-38  |

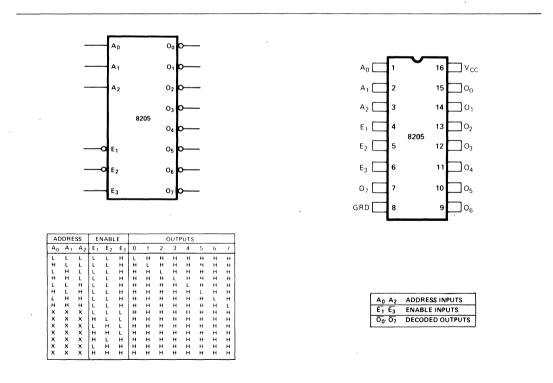

| 8205 High Speed 1 out of 8 Binary Decoder                                     | 2-43  |

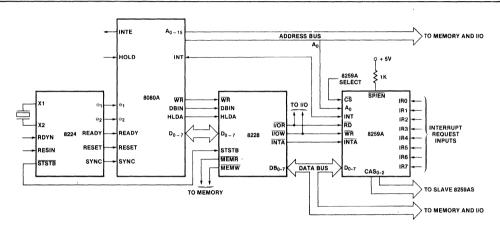

| 8224 Clock Generator and Driver for 8080A CPU                                 | 2-48  |

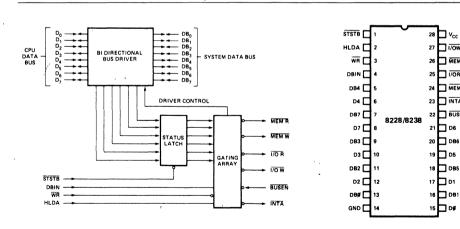

| 8228/8238 System Controller and Bus Driver for 8080A CPU                      | 2-53  |

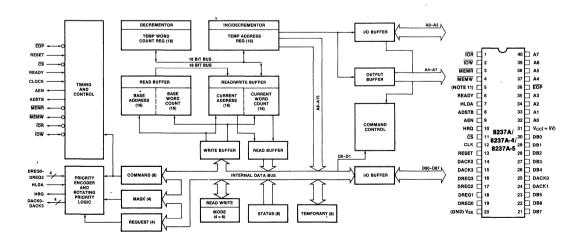

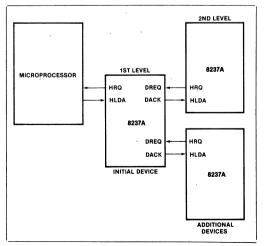

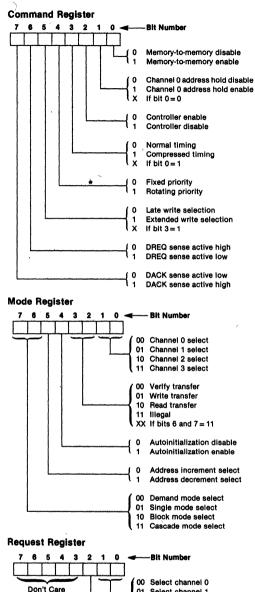

| 8237A/8237A-4/8237A-5 High Performance Programmable DMA Controller            | 2-57  |

| 8257/8257-5 Programmable DMA Controller                                       | 2-72  |

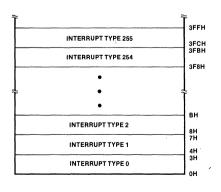

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller                       | 2-89  |

| 8755A/8755A-2 16, 384-Bit EPROM with I/O                                      | 2-107 |

| AP-59 Using the 8259A Programmable Interrupt Controller                       |       |

|                                                                               |       |

### **CHAPTER 3**

### iAPX 86, 88, 186, 188 MICROPROCESSORS

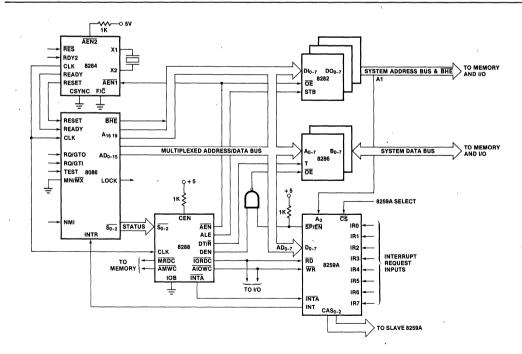

|   | iAPX 86/10 16-Bit HMOS Microprocessor                                                             | 3-1   |

|---|---------------------------------------------------------------------------------------------------|-------|

|   | iAPX 186 High Integration 16-Bit Microprocessor                                                   |       |

|   | iAPX 88/10 8-Bit HMOS Microprocessor                                                              | 3-79  |

|   | iAPX 188 High Integration 8-Bit Microprocessor                                                    |       |

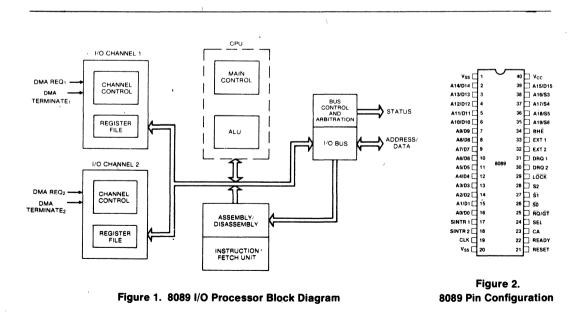

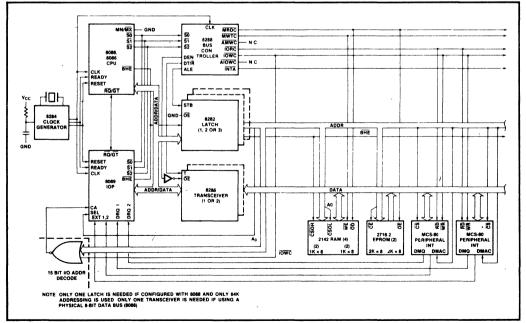

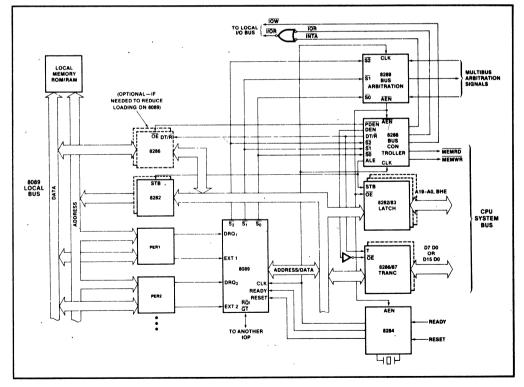

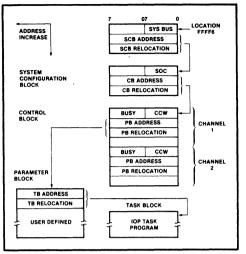

|   | 8089 8 & 16-Bit HMOS I/O Processor                                                                |       |

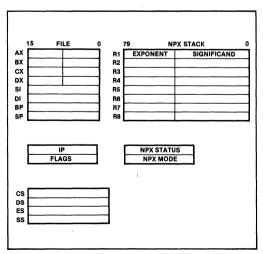

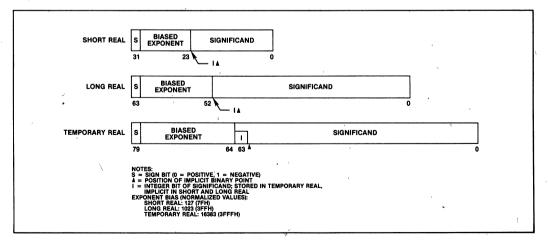

|   | 8087/8087-2/8087-1 Numeric Data Coprocessor                                                       | 3-175 |

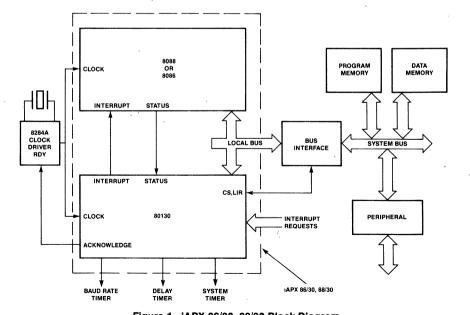

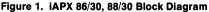

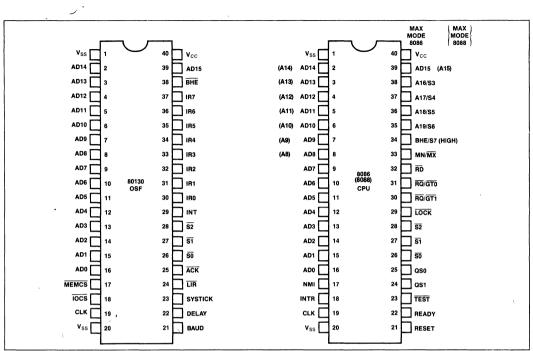

|   | 80130/80130-2 iAPX 86/30, 88/30, 186/30, 188/30 iRMX <sup>**</sup> 86 Operating System Processors | 3-198 |

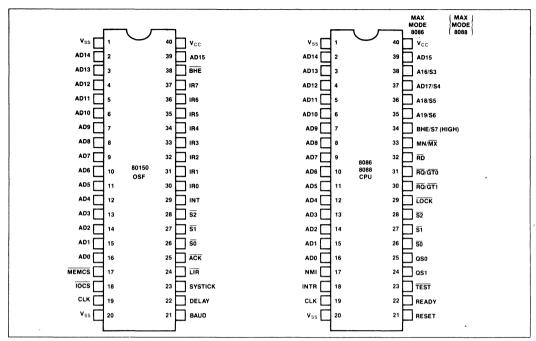

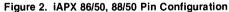

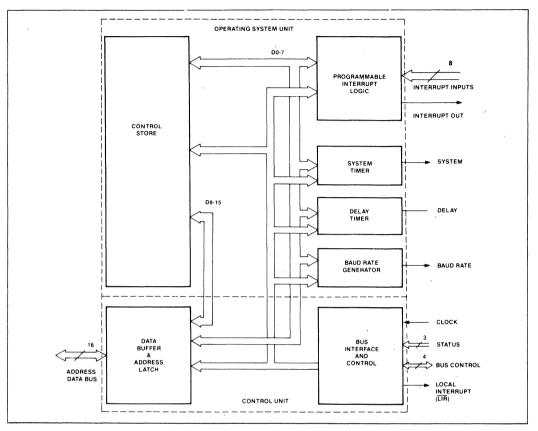

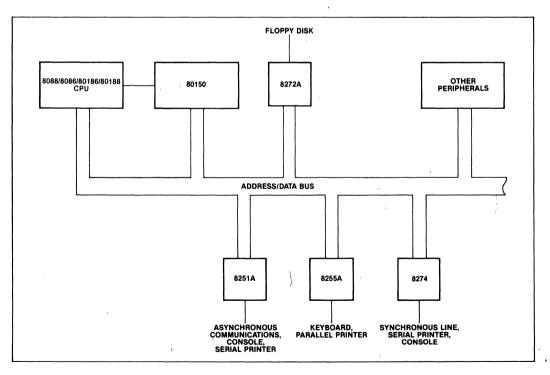

|   | 80150/80150-2 iAPX 86/50, 88/50, 186/50, 188/50 CP/M*-86 Operating System Processors              |       |

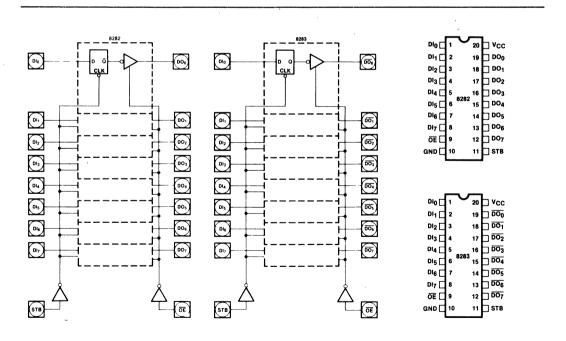

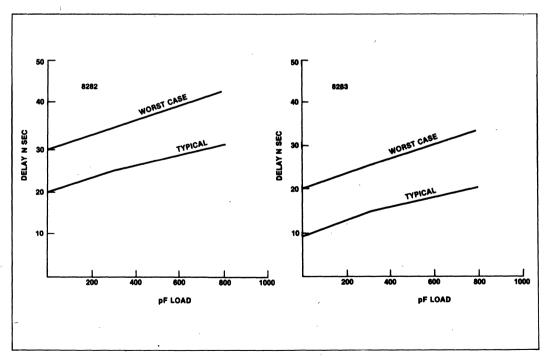

|   | 8282/8283 Octal Latch                                                                             | 3-232 |

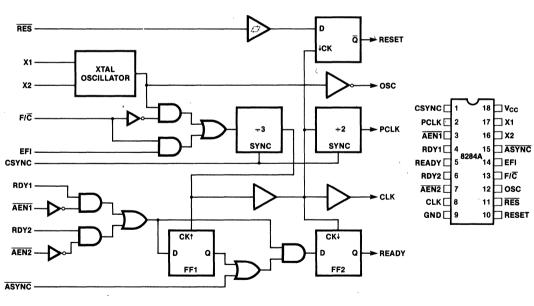

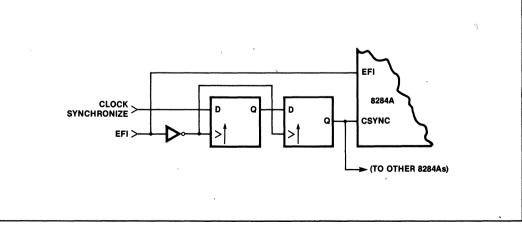

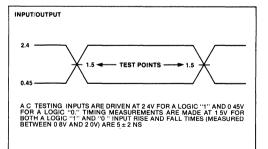

|   | 8284A/8284A-1 Clock Generator and Driver for iAPX 86, 88 Processors                               | 3-237 |

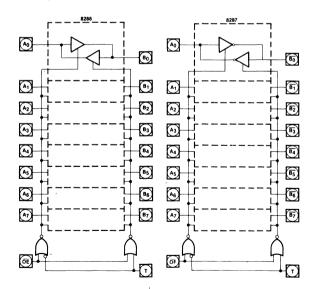

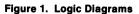

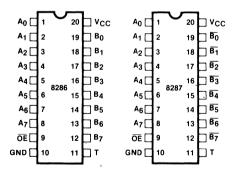

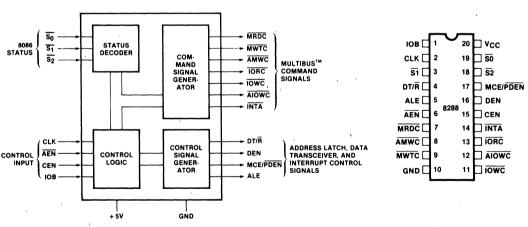

|   | 8286/8287 Octal Bus Transceiver                                                                   | 3-245 |

|   | 8288 Bus Controller for iAPX 86, 88 Processors                                                    |       |

|   | 82188 Integrated Bus Controller for iAPX 86, 88, 186, 188 Processors                              |       |

|   | 8289/8289-1 Bus Arbiter                                                                           |       |

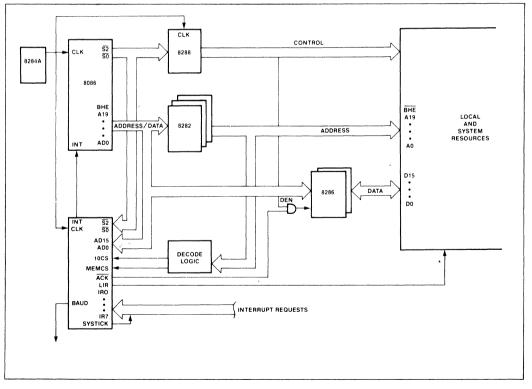

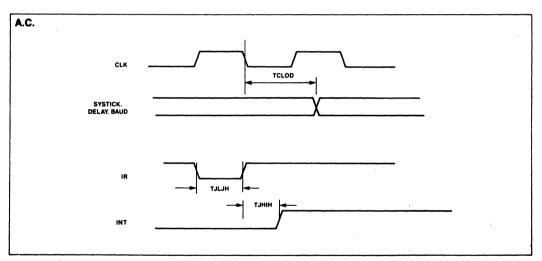

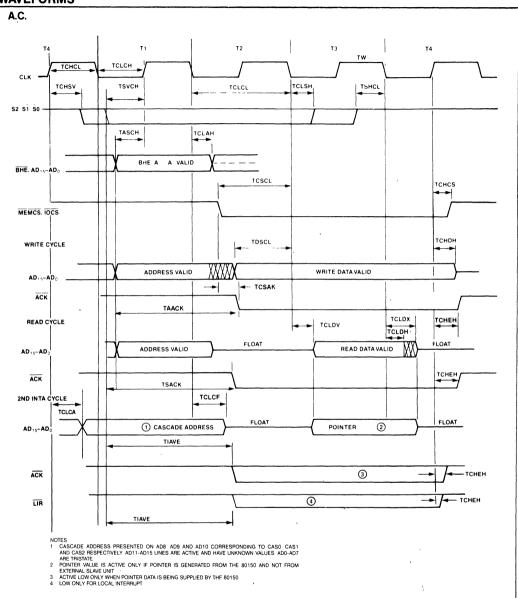

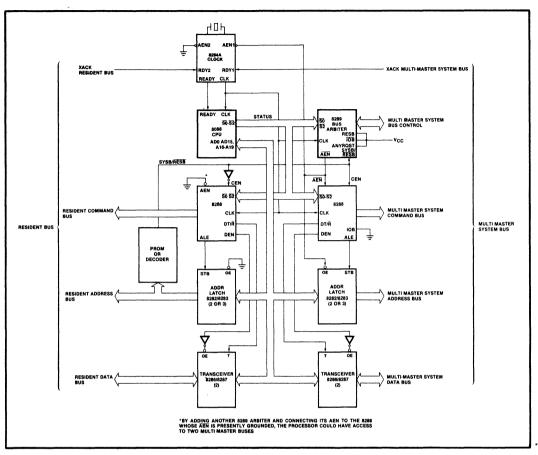

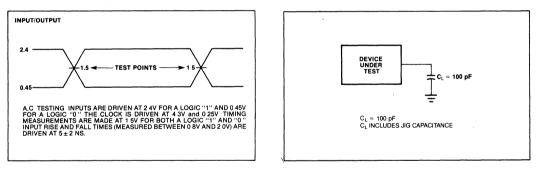

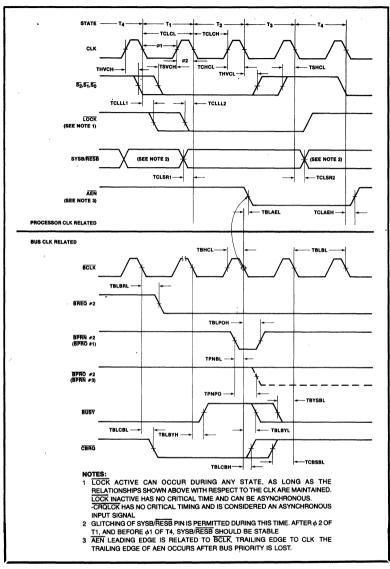

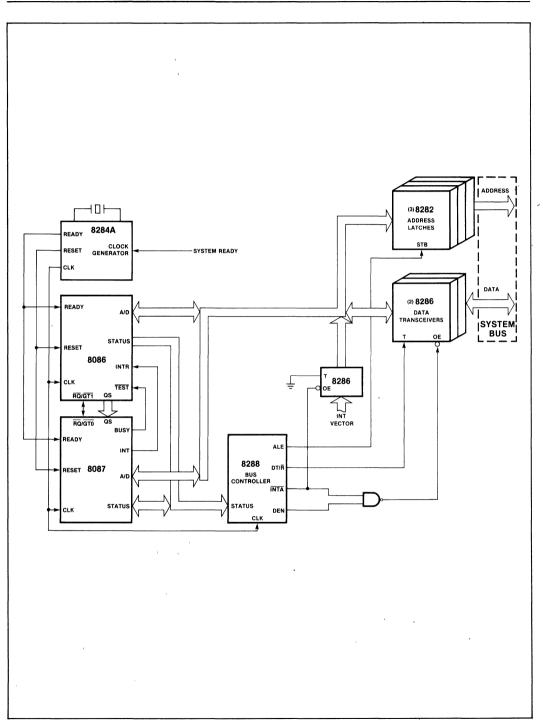

|   | AP-67 8086 System Design                                                                          | 3-285 |

|   | AP-123 Graphic CRT Design Using the Intel 8089                                                    | 3-348 |

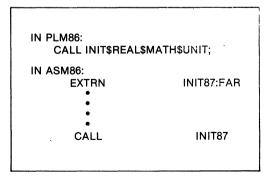

| , | AP-113 Getting Started with the Numeric Data Processor                                            |       |

|   | AP-143 Using the iAPX 86/20 Numeric Data Processor in a Small Business Computer                   |       |

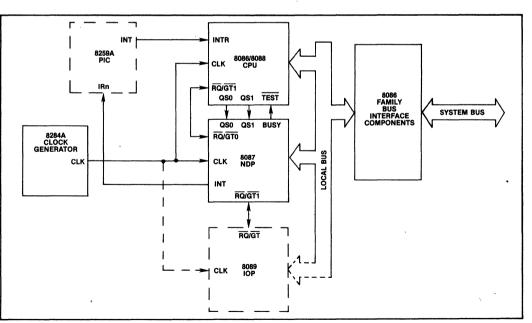

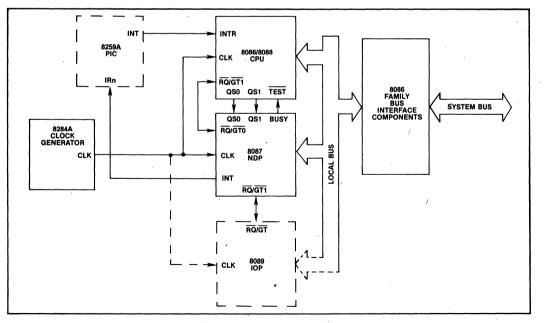

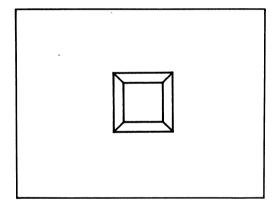

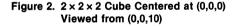

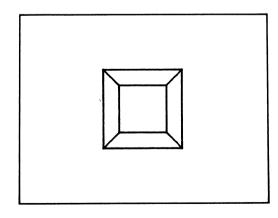

|   | AP-144 Three Dimensional Graphics Application of the iAPX 86/20                                   |       |

|   | Numeric Data Processor                                                                            | 3-504 |

|   | AP-186 Introduction to the 80186                                                                  |       |

|   |                                                                                                   |       |

### **CHAPTER 4**

### **iAPX 286 MICROPROCESSORS**

| iAPX 286/10 High Performance Microprocessor with Memory Management and Protection | 4-1   |

|-----------------------------------------------------------------------------------|-------|

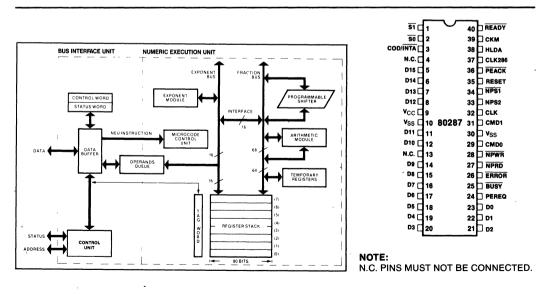

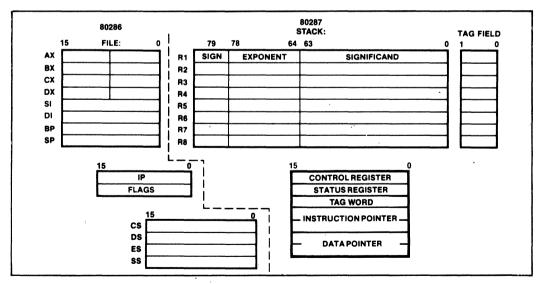

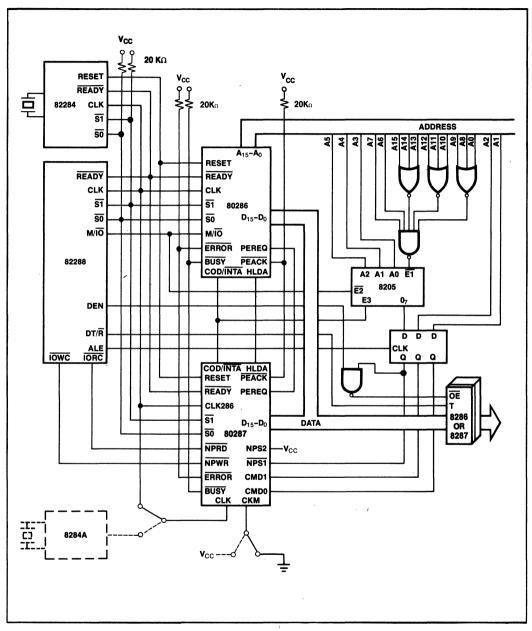

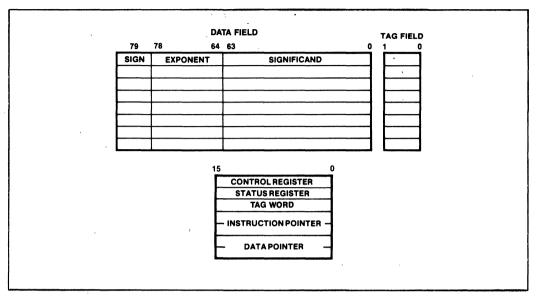

| 80287 80-Bit HMOS Numeric Processor Extension                                     | 4-54  |

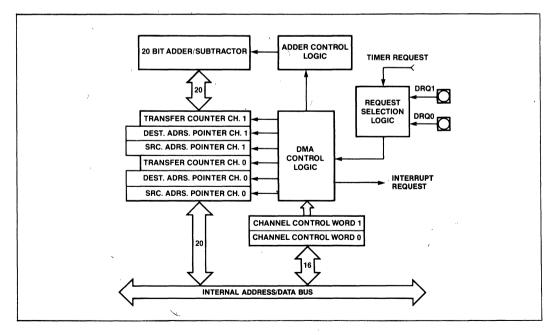

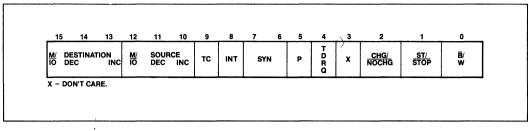

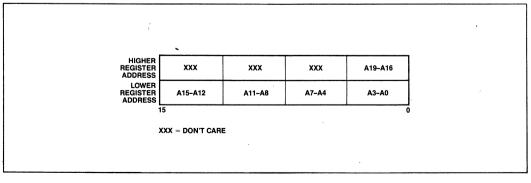

| 82258 Advanced DMA Controller Architectural Overview                              | 4-79  |

| 82284 Clock Generator and Ready Interface for iAPX 286 Processors                 | 4-92  |

| 82288 Bus Controller for iAPX 286 Processors                                      | 4-100 |

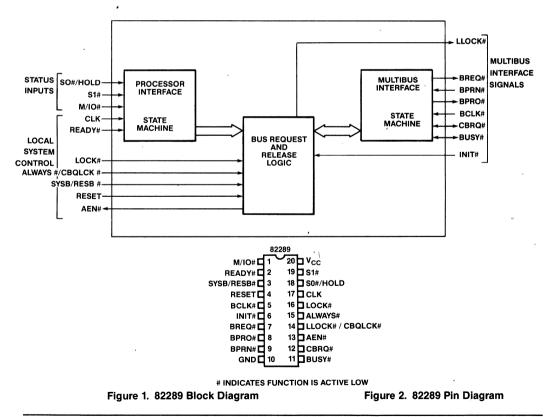

| 82289 Bus Arbiter for iAPX 286 Processor Family                                   | 4-118 |

## CHAPTER 5 MEMORY CONTROLLERS

| DATA SHEETS                                                                 |       |

|-----------------------------------------------------------------------------|-------|

| 8202A Dynamic RAM Controller                                                | 5-1   |

| 8203 64K Dynamic RAM Controller                                             |       |

| 8206/8206-2 Error Detection and Correction Unit                             | 5-30  |

| 8207 Dual-Port Dynamic RAM Controller                                       |       |

| 8208 Dynamic RAM Controller                                                 | 5-98  |

| ÜSERS MANUAL                                                                |       |

| Introduction                                                                | 5-117 |

| Programming the 8207                                                        |       |

| RAM Interface                                                               |       |

| Microprocessor Interfaces                                                   |       |

| 8207 with ECC (8206)                                                        |       |

| Appendix                                                                    |       |

| APPLICATION NOTES                                                           |       |

| AP-97A Interfacing Dynamic RAM to iAPX 86/88 Using the 8202A and 8203       | 5-147 |

| AP-141 8203/8206/2164A Memory Design                                        | 5-183 |

| AP-167 Interfacing the 8207 Dynamic RAM Controller to the iAPX 186          | 5-189 |

| AP-168 Interfacing the 8207 Advanced Dynamic RAM Controller to the iAPX 286 | 5-194 |

| ARTICLE REPRINTS                                                            |       |

| AR-364 FAE News 1/84 "8208 with 186"                                        | 5-201 |

| AR-231 Dynamic RAM Controller Orchestrates Memory Systems                   | 5-212 |

### - VOLUME 2 -

### SUPPORT PERIPHERALS

| DATA SHEETS                                                                  |       |

|------------------------------------------------------------------------------|-------|

| 8231A Arithmetic Processing Unit                                             | 5-219 |

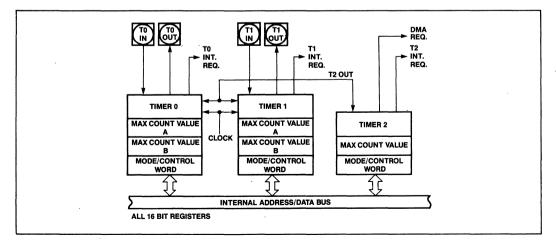

| 8253/8253-5 Programmable Interval Timer                                      |       |

| 8254 Programmable Interval Timer                                             |       |

| 82C54 CHMOS Programmable Interval Timer                                      | 5-256 |

| 8255A/8255A-5 Programmable Peripheral Interface                              |       |

| 82C55A CHMOS Programmable Peripheral Interface                               |       |

| 8256AH Multifunction Microprocessor Support Controller                       |       |

| 8279/8279-5 Programmable Keyboard/Display Interface                          |       |

| APPLICATION NOTES                                                            |       |

| AP-153 Designing with the 8256                                               | 5-352 |

| AP-183 8256AH Application Note                                               |       |

| FLOPPY DISK CONTROLLERS                                                      |       |

| DATA SHEETS                                                                  |       |

| 8272A Single/Double Density Floppy Disk Controller                           | 5-444 |

| APPLICATION NOTES                                                            |       |

| AP-116 An Intelligent Data Base System Using the 8272                        | 5-463 |

| AP-121 Software Design and Implementation of Floppy Disk Systems             | 5-504 |

| HARD DISK CONTROLLERS                                                        |       |

| DATA SHEETS                                                                  |       |

| 82062 Winchester Disk Controller                                             | 5-574 |

| 82064 Winchester Disk Controller with On-Chip Error Detection and Correction | 5-601 |

| UPI USERS MANUAL                                                             |       |

| Introduction                                                                 |       |

| Functional Description                                                       | 5-639 |

| Instruction Set                                                              | 5-656 |

| Single-Step, Programming, and Power-Down Modes                               | 5-683 |

| System Operation                                                             |       |

| Applications                                                                 | 5-694 |

| AP-161 Complex Peripheral Control with the UPI-42                            |       |

| AP-90 An 8741A/8041A Digital Cassette Controller                             | 5-806 |

| DATA SHEETS                                                          |        |

|----------------------------------------------------------------------|--------|

| 8041A/8641A/8741A Universal Peripheral Interface 8-Bit Microcomputer | 5-814  |

| 8042/8742 Universal Peripheral Interface 8-Bit Microcomputer         |        |

| 8243 MCS-48 Input/Output Expander                                    |        |

| APPLICATION NOTES                                                    | 0 0 10 |

| AP-182 Multimode Winchester Controller Using the 82062               | 5-846  |

| SYSTEM SUPPORT                                                       | 0.040  |

| ICE-42 8042 In-Circuit Emulator                                      | 5-010  |

| MCS-48 Diskette-Based Software Support Package                       |        |

| iUP-200/iUP-201 Universal PROM Programmers                           |        |

|                                                                      | 5-920  |

| CHAPTER 6                                                            |        |

| DATA COMMUNICATIONS                                                  |        |

|                                                                      |        |

|                                                                      | 0.1    |

| Intel Data Communications Family Overview                            | 6-1    |

| GLOBAL COMMUNICATIONS                                                |        |

| DATA SHEETS                                                          |        |

| 8251A Programmable Communication Interface                           |        |

| 8273/8273-4 Programmable HDLC/SDLC Protocol Controller               |        |

| 8274 Multi-Protocol Serial Controller (MPSC)                         |        |

| 82530/82530-6 Serial Communications Controller (SCC)                 | 6-85   |

| APPLICATION NOTES                                                    |        |

| AP-16 Using the 8251 Universal Synchronous/Asynchronous              |        |

| Receiver/Transmitter                                                 | 6-113  |

| AP-36 Using the 8273 SDLC/HDLC Protocol Controller                   | 6-144  |

| AP-134 Asynchronous Communications with the 8274 Multiple            |        |

| Protocol Serial Controller                                           | 6-191  |

| AP-145 Synchronous Communications with the 8274 Multiple             |        |

| Protocol Serial Controller                                           | 6-228  |

| AP-222 Asynchronous SDLC Communications with 82530                   |        |

| LOCAL AREA NETŴORKS                                                  |        |

| DATA SHEETS                                                          |        |

| 82501 Ethernet Serial Interface                                      | 6-288  |

| 82C502 Ethernet Tranceiver Chip Data Sheet                           |        |

| 82586 Local Area Network Coprocessor                                 |        |

| 82588 Personal Workstation Lan Control                               |        |

| ARTICLE REPRINTS                                                     |        |

| AR-345 Build a VLSI-Based Workstation for the Ethernet               |        |

| Environment                                                          | 6-362  |

| AR-346 VLSI Solutions for Tiered Office Networks                     |        |

| AR-342 Chips Support Two Local Area Networks                         |        |

| OTHER DATA COMMUNICATIONS                                            | 0 000  |

| DATA SHEETS                                                          |        |

| <sup>4</sup> 8291A GPIB Talker/Listener                              | 6-386  |

| 8292 GPIB Controller                                                 |        |

| 8294A Data Encryption Unit                                           |        |

| APPLICATION NOTES                                                    | 0.400  |

| AP-66 Using the 8292 GPIB Controller                                 | 6-442  |

| AP-166 Using the 8291A GPIB Talker/Listener                          | 6-496  |

| ARTICLE REPRINTS                                                     | 0-400  |

| AR-208 SLI Transceiver Chips Complete GPIB Interface                 | 6-529  |

| AR-200 SLT transceiver Chips Complete GPIB Interface                 |        |

| TUTORIAL                                                             | 0-000  |

|                                                                      | C EAC  |

| Data Encryption Tutorial                                             | 0-040  |

### **CHAPTER 7**

### ALPHANUMERIC TERMINAL CONTROLLERS DATA SHEETS

| BAIAGHEETO                                                 |       |

|------------------------------------------------------------|-------|

| 8275H Programmable CRT Controller                          | 7-1   |

| 8276H Small System CRT Controller                          | 7-25  |

| APPLICATION NOTES                                          | 1-20  |

| AP-62 A Low Cost CRT Terminal Using the 8275               | 7-42  |

| ARTICLE REPRINTS                                           |       |

| AR-178 A Low Cost CRT Terminal Does More with Less         | 7-84  |

| GRAPHICS DISPLAY PRODUCTS                                  |       |

| DATA SHEETS                                                |       |

| 82720 Graphics Display Controller                          | 7-91  |

| ARTICLE REPRINTS                                           |       |

| AR-255 Dedicated VLSI Chip Lightens Graphic Display        |       |

| Design Load                                                | 7-128 |

| AR-298 Graphics Chip Makes Low Cost High Resolution, Color |       |

| Displays Possible                                          | 7-136 |

| TEXT PROCESSING PRODUCTS                                   |       |

| DATA SHEETS                                                |       |

| 82730 Text Coprocessor                                     | 7-143 |

| 82731 Video Interface Controller                           | 7-187 |

| ARTICLE REPRINTS                                           |       |

| AR-305 Text Coprocessor Brings Quality to CRT Displays     | 7-206 |

| AR-297 VLSI Coprocessor Delivers High Quality Displays     |       |

| AR-296 Mighty Chips                                        |       |

|                                                            |       |

### **Numeric Index**

| 80130/81030-2 iAPX 86/30, 88/30, 186/30, 188/30 iRMX <sup>™</sup> 86 Operating System Processors 3-198 |

|--------------------------------------------------------------------------------------------------------|

| 80150/80150-2 iAPX 86/50, 88/50, 186/50, 188/50 C/PM*-86 Operating System Processors 3-220             |

| 80186 (iAPX 186) High Integration 16-Bit Microprocessor                                                |

| 80188 (iAPX 188) High Integration 8-Bit Microprocessor 3-106                                           |

| 80286 (iAPX 286/10) High Performance Microprocessor with Memory Management                             |

| and Protection                                                                                         |

| 80287 80-Bit HMOS Numeric Processor Extension                                                          |

| 8041A/8641A/8741A Universal Peripheral Interface 8-Bit Microcomputer 5-814, 5-635, 5-639               |

| 8042/8742 Universal Peripheral Interface 8-Bit Microcomputer 5-826, 5-635, 5-639, 5-910                |

| 8080A/8080A-1/8080A-2, 8-Bit N-Channel Microprocessor                                                  |

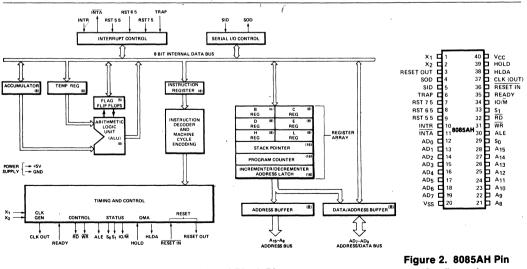

| 8085AH/8085AH-2/8085AH-1 8-Bit HMOS Microprocessors                                                    |

| 8086 (iAPX 86/10) 16-Bit HMOS Microprocessor                                                           |

| 8087/8087-2/8087-1 Numeric Data Coprocessor                                                            |

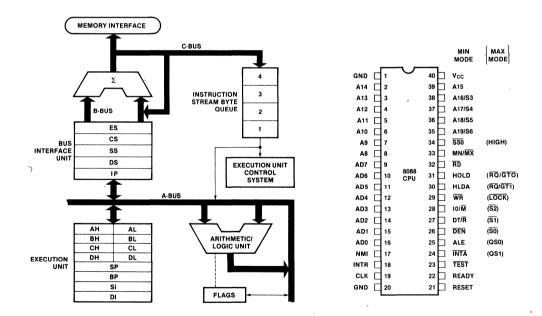

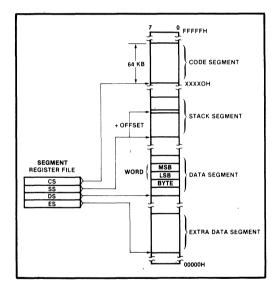

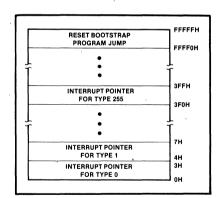

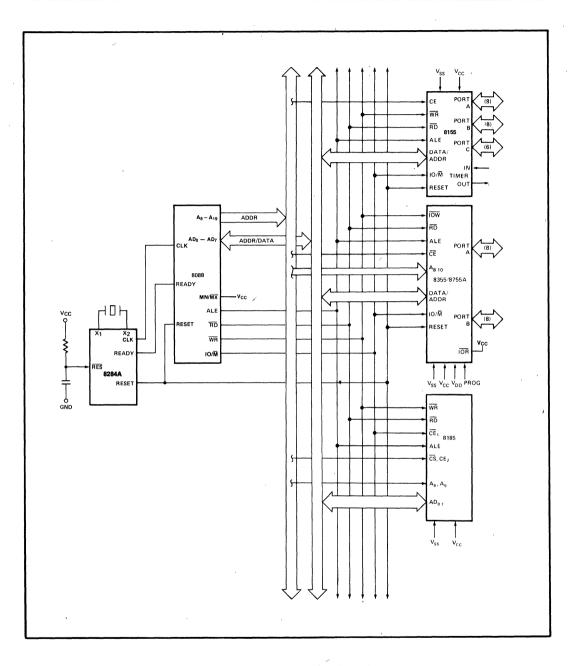

| 8088 (iAPX 88/10) 8-Bit HMOS Microprocessor                                                            |

| 8089 8 & 16-Bit HMOS I/O Processor                                                                     |

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and Timer 2-26                     |

| 8185/8185-2 1024 x 8-Bit Static RAM for MCS®-85 2-38                                                   |

| 8202A Dynamic RAM Controller                                                                           |

| 8203 64K Dynamic RAM Controller 5-183                                                                  |

| 8205 High Speed 1 out of 8 Binary Decoder                                                              |

| 8206/8206-2 Error Detection and Correction Unit                                                        |

| 82062 Winchester Disk Controller                                                                       |

| 82064 Winchester Disk Controller with On-Chip Error Detection and Correction                           |

| 8207 Dual-Port Dynamic RAM Controller                                                                  |

| 5-143, 5-183, 5-189, 5-194, 5-212                                                                      |

| 8208 Dynamic RAM Controller                                                                            |

| 82188 Integrated Bus Controller for iAPX 86, 88, 186, 188 Processors                                   |

| 8224 Clock Generator And Driver for 8080A CPU 2-48                                                     |

| 82258 Advanced DMA Controller Architectural Overview                                                   |

| 8228/8238 System Controller and Bus Driver for 8080A CPU                                               |

| 82284 Clock Generator and Ready Interface for iAPX 286 Processors                                      |

| 82288 Bus Controller for iAPX 286 Processors                                                           |

| 82289 Bus Arbiter for iAPX 286 Processor Family 4-118                                                  |

| 8231A Arithmetic Processing Unit                                                                       |

| 8237A/8237A-4/8237A-5 High Performance Programmable DMA Controller                                     |

| 8243 MCS-48 Input/Output Expander                                                                      |

| 82501 Ethernet Serial Interface                                                                        |

| 82C502 Ethernet Tranceiver Chip                                                                        |

| 8251A Programmable Communication Interface                                                             |

| 8253/8253-5 Programmable Interval Timer                                                                |

| 82530/82530-6 Serial Communications Controller (SCC)                                                   |

•

| 8254 Programmable Interval Timer                                    | 5-240                        |

|---------------------------------------------------------------------|------------------------------|

| 82C54 CHMOS Programmable Interval Timer                             | 5-256                        |

| 8255A/8255A-5 Programmable Peripheral Interface                     | 5-273, 7-84                  |

| 82C55 CHMOS Programmable Peripheral Interface                       | 5-294                        |

| 8256AH Multifunction Microprocessor Support Controller              | 5-317, 5-352, 5-427          |

| 8257/8257-5 Programmable DMA Controller                             | 2-72 <sup>j</sup>            |

| 82586 Local Area Network Coprocessor                                | 6-302, 6-362, 6-370, 6-380   |

| 82588 Personal Workstation Lan Control                              |                              |

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller             |                              |

| 8272A Single/Double Density Floppy Disk Controller                  | 5-444, 5-463, 5-504, 7-128   |

| 82720 Graphics Display Controller 7-91, 7-128,                      | , 7-136, 7-206, 7-214, 7-217 |

| 8273/8273-4 Programmable HDLC/SDLC Protocol Controller              |                              |

| 82730 Text Coprocessor 6-262, 7-136,                                | , 7-143, 7-206, 7-214, 7-217 |

| 82731 Video Interface Controller                                    | 7-187, 7-206                 |

| 8274 Multi-Protocol Serial Controller (MPSC)                        | 6-48, 6-191, 6-228, 6-380    |

| 8275H Programmable CRT Controller                                   |                              |

| 8276H Small System CRT Controller                                   |                              |

| 8279/8279-5 Programmable Keyboard/Display Interface                 | 5-340                        |

| 8282/8283 Octal Latch                                               |                              |

| 8284A/8284A-1 Clock Generator and Driver for iAPX 86, 88 Processors |                              |

| 8286/8287 Octal Bus Transceiver                                     |                              |

| 8288 Bus Controller for iAPX 86, 88 Processors,                     |                              |

| 8289/8989-1 Bus Arbiter                                             |                              |

| 8291A GPIB Talker/Listener                                          | 6-386, 6-496, 6-528, 6-536   |

| 8292 GPIB Controller                                                | 6-415, 6-442, 6-528, 6-536   |

| 8294A Data Encryption Unit                                          |                              |

| 8755A/8755A-2 16,384-Bit EPROM with I/O                             |                              |

e;

# Overview

.

1 . . . . х х

### INTRODUCTION

Intel microprocessors and peripherals provide a complete solution in increasingly complex application environments. Quite often, a single peripheral device will replace anywhere from 20 to 100 TTL devices (and the associated design time that goes with them).

Built-in functions and a standard Intel microprocessor/ peripheral interface deliver very real *time* and *performance* advantages to the designer of microprocessorbased systems.

### **REDUCED TIME TO MARKET**

When you can purchase an off-the-shelf solution that replaces a number of discrete devices, you're also replacing all the design, testing, and debug *time* that goes with them.

### **INCREASED RELIABILITY**

At Intel, the rate of failure for devices is carefully tracked. Highest reliability is a tangible goal that translates to higher reliability for your product, reduced downtime, and reduced repair costs. And as more and more functions are integrated on a single VLSI device, the resulting system requires less power, produces less heat, and requires fewer mechanical connections—again resulting in greater system reliability.

### LOWER PRODUCT, COST

By minimizing design time, increasing reliability, and

replacing numerous parts, microprocessor and peripheral solutions can contribute dramatically to lower product costs.

#### **HIGHER SYSTEM PERFORMANCE**

Intel microprocessors and peripherals provide the highest system performance for the demands of today's (and tomorrow's) microprocessor-based applications. For example, the iAPX 286 CPU, with its on-chip memory management and protection, offers the highest performance for multitasking, multiuser systems.

### HOW TO USE THE GUIDE

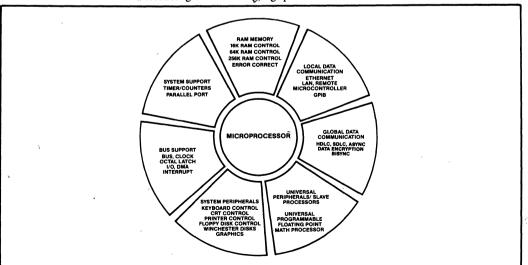

The following application guide illustrates the range of microprocessors and peripherals that can be used for the applications in the vertical column on the left. The peripherals are grouped by the I/O function they control: CRT, datacommunication, universal (user programmable), mass storage dynamic RAM controllers, and CPU/ bus support.

An "X" in a horizontal application row indicates a potential peripheral or CPU, depending upon the features desired. For example, a conversational terminal could use either of the three display controllers, depending upon features like the number of characters per row or font capability. A "Y" indicates a likely candidate, for example, the 8272A Floppy Disk Controller in a small business computer.

The Intel microprocessor and peripherals family provides a broad range of time-saving, high performance solutions.

| ~                             | . /           | uPRO        | OCES       | SOF          | 7       | D       | SPL   | AY            |               |       |      | DAT     | ACC         | MM       |       | ,                         |                 | UPI         | DIS        | SKS       | DRA  | MC            | ONT             | ROL              | , si   | JPPC  | )RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|---------------|-------------|------------|--------------|---------|---------|-------|---------------|---------------|-------|------|---------|-------------|----------|-------|---------------------------|-----------------|-------------|------------|-----------|------|---------------|-----------------|------------------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPLICATION                   | 8088          | 8086        | 188        | 186          | 286     | 8275/76 | 82720 | 82730/731     | 8251A         | 8256  | 8273 | 8274    | 8291A/92/93 | 82530    | 82588 | 82586/501/502             | 8044/8744       | 8042/8742   | 8272A      | 82062/064 | 8203 | 8206          | 8207            | 8208             | 8254   | 8255  | 8231A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PERIPHERALS                   |               | a cast of a | COMPANY OF |              |         |         |       |               |               |       |      |         |             | home her |       |                           | THE OWNER AND A |             |            |           |      |               |                 |                  |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Printers                      | X<br>X        | x           | X          |              | 1.1     |         | X     | X             | X             | X     |      |         | X<br>X      |          | 14    |                           | XX              | X<br>X      |            |           |      |               |                 |                  | X      | X     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Plotters                      | X             | X           | X          | X            | Γ       | I       |       | I             |               |       |      | I       | X           |          | Ι     | I                         | X               | X           | [          | Γ         |      |               |                 | part of one of a | Γ      | X     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Keyboards                     |               |             |            |              |         | 1.1     |       |               | X             |       |      | -       |             |          |       |                           | X               | X           |            |           |      |               |                 | 0.00             | 1. 1   | X     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MAŚS STORAGE                  |               |             |            |              |         |         |       |               |               |       |      |         |             |          |       |                           |                 |             |            |           |      |               | •               |                  |        |       | [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Hard Disk                     | X             | X           | Y          |              | · · · . |         |       |               |               | el an |      | - 1     |             |          |       |                           |                 |             | 00.72      | X         |      |               |                 |                  |        | X     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Mini Winchester               |               |             | Y          |              | 1       |         |       |               | Ι             |       |      |         |             |          |       |                           |                 |             |            | Y         |      |               |                 |                  |        | Τ     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Таре                          | 5             | 6.5         | X          |              |         |         |       |               |               |       |      |         |             |          |       | Contraction of the second | X               | X<br>X      |            | 1.10      |      |               |                 |                  |        | X     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Cassette                      |               |             |            |              |         |         |       | I             |               |       |      |         |             |          |       |                           |                 | X           |            |           |      |               |                 |                  |        | X     | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Floppy/Mini                   | -             |             | 1000       |              |         |         |       |               |               |       |      |         |             |          |       |                           |                 |             | Y          | 1.1       | 37   | 2.5           |                 |                  |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| COMMUNICATIONS                |               | Pine and a  |            |              | 1000    |         |       | and and an or | samuli sin /7 |       |      |         |             |          |       |                           |                 |             | the second |           |      | 005.5-000.000 |                 |                  |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PBX                           |               |             |            | X            | Y       |         | 1.    |               |               | X     | X    |         |             | X        |       |                           | X<br>X          |             |            |           | X    | Х             | X               | X                | X<br>X | X     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LANS                          | X             | X           | X          | X            |         |         |       |               |               |       |      | X       |             | X        | X     | Y                         | X               |             |            |           |      |               |                 |                  | X      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

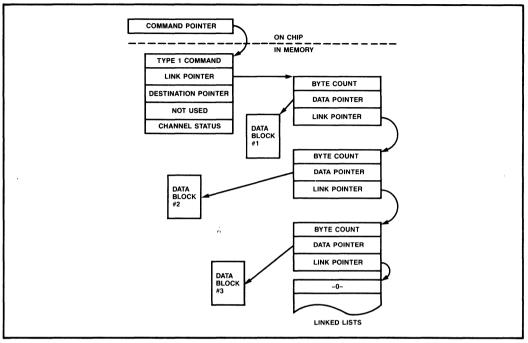

| Modems                        |               |             |            |              |         |         |       |               | X             |       |      | X       | ÷.          | X        |       | 14                        | X               | X           | 1 34       | 1         |      | · *•          |                 |                  | 1.1    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |