# Intel<sup>®</sup> Architecture Instruction Set Extensions and Future Features

**Programming Reference**

*September 2022* 319433-046

#### **Notices & Disclaimers**

# This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

All product plans and roadmaps are subject to change without notice.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, with the sole exception that a) you may publish an unmodified copy and b) code included in this document is licensed subject to the Zero-Clause BSD open source license (0BSD), https://opensource.org/licenses/0BSD. You may create software implementations based on this document and in compliance with the foregoing that are intended to execute on the Intel product(s) referenced in this document. No rights are granted to create modifications or derivatives of this document.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

# **Revision History**

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -025     | <ul> <li>Removed instructions that now reside in the Intel<sup>®</sup> 64 and IA-32<br/>Architectures Software Developer's Manual.</li> <li>Minor updates to chapter 1.</li> <li>Updates to Table 2-1, Table 2-2 and Table 2-8 (leaf 07H) to indicate<br/>support for AVX512_4VNNIW and AVX512_4FMAPS.</li> <li>Minor update to Table 2-8 (leaf 15H) regarding ECX definition.</li> <li>Minor updates to Section 4.6.2 and Section 4.6.3 to clarify the effects of<br/>"suppress all exceptions".</li> <li>Footnote addition to CLWB instruction indicating operand encoding<br/>requirement.</li> <li>Removed PCOMMIT.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             | September 2016 |

| -026     | <ul> <li>Removed CLWB instruction; it now resides in the Intel<sup>®</sup> 64 and IA-32<br/>Architectures Software Developer's Manual.</li> <li>Added additional 512-bit instruction extensions in chapter 6.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | October 2016   |

| -027     | <ul> <li>Added TLB CPUID leaf in chapter 2.</li> <li>Added VPOPCNTD/Q instruction in chapter 6,and CPUID details in chapter 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | December 2016  |

| -028     | Updated intrinsics for VPOPCNTD/Q instruction in chapter 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | December 2016  |

| -029     | <ul> <li>Corrected typo in CPUID leaf 18H.</li> <li>Updated operand encoding table format; extracted tuple information from operand encoding.</li> <li>Added VPERMB back into chapter 5; inadvertently removed.</li> <li>Moved all instructions from chapter 6 to chapter 5.</li> <li>Updated operation section of VPMULTISHIFTQB.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | April 2017     |

| -030     | <ul> <li>Removed unnecessary information from document (chapters 2, 3 and 4).</li> <li>Added table listing recent instruction set extensions introduction in Intel 64 and IA-32 Processors.</li> <li>Updated CPUID instruction with additional details.</li> <li>Added the following instructions: GF2P8AFFINEINVQB, GF2P8AFFINEQB, GF2P8MULB, VAESDEC, VAESDECLAST, VAESENC, VAESENCLAST, VPCLMULQDQ, VPCOMPRESS, VPDPBUSD, VPDPBUSDS, VPDPWSSD, VPDPWSSDS, VPEXPAND, VPOPCNT, VPSHLDV, VPSHRDV, VPSHRDV, VPSHUFBITQMB.</li> <li>Removed the following instructions: VPMADD52HUQ, VPMADD52LUQ, VPERMB, VPERMI2B, VPERMT2B, and VPMULTISHIFTQB. They can be found in the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 2A, 2B, 2C &amp; 2D.</li> <li>Moved instructions unique to processors based on the Knights Mill microarchitecture to chapter 3.</li> <li>Added chapter 4: EPT-Based Sub-Page Permissions.</li> <li>Added chapter 5: Intel<sup>®</sup> Processor Trace: VMX Improvements.</li> </ul> | October 2017   |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| -031     | <ul> <li>Updated change log to correct typo in changes from previous release.</li> <li>Updated instructions with imm8 operand missing in operand encoding table.</li> <li>Replaced "VLMAX" with "MAXVL" to align terminology used across documentation.</li> <li>Added back information on detection of Intel AVX-512 instructions.</li> <li>Added Intel<sup>®</sup> Memory Encryption Technologies instructions PCONFIG and WBNOINVD. These instructions are also added to Table 1-1 "Recent Instruction Set Extensions Introduction in Intel 64 and IA-32 Processors". Added Section 1.5 "Detection of Intel<sup>®</sup> Memory Encryption Technologies (Intel<sup>®</sup> MKTME) Instructions".</li> <li>CPUID instruction updated with PCONFIG and WBNOINVD details.</li> <li>CPUID instruction updated with additional details on leaf 07H: Intel<sup>®</sup> Xeon Phi<sup>™</sup> only features identified and listed.</li> <li>CPUID instruction updated with new Intel<sup>®</sup> SGX features in leaf 12H.</li> <li>CPUID instruction updated with new PCONFIG information sub-leaf 1BH.</li> <li>Updated short descriptions in the following instructions: VPDPBUSD, VPDPBUSDS, VPDPWSSD and VPDPWSSDS.</li> <li>Corrections and clarifications in Chapter 4 "EPT-Based Sub-Page Permissions".</li> <li>Corrections and clarifications in Chapter 5 "Intel® Processor Trace: VMX Improvements".</li> </ul> | January 2018 |

| -032     | <ul> <li>Corrected PCONFIG CPUID feature flag on instruction page.</li> <li>Minor updates to PCONFIG instruction pages: Changed Table 2-2 to use<br/>Hex notation; changed "RSVD, MBZ" to "Reserved, must be zero" in two<br/>places in Table 2-3.</li> <li>Minor typo correction in WBNOINVD instruction description.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | January 2018 |

| -033     | <ul> <li>Updated Table 1-2 "Recent Instruction Set Extensions / Features<br/>Introduction in Intel® 64 and IA-32 Processors".</li> <li>Added Section 1.4, "Detection of Future Instructions and Features".</li> <li>Added CLDEMOTE, MOVDIRI, MOVDIR64B, TPAUSE, UMONITOR and<br/>UMWAIT instructions.</li> <li>Updated the CPUID instruction with details on new instructions/features<br/>added, as well as new power management details and information on<br/>hardware feedback interface ISA extensions.</li> <li>Corrections to PCONFIG instruction.</li> <li>Moved instructions unique to processors based on the Knights Mill<br/>microarchitecture to the Intel<sup>®</sup> 64 and IA-32 Architectures Software<br/>Developer's Manual.</li> <li>Added Chapter 5 "Hardware Feedback Interface ISA Extensions".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | March 2018   |

| -034     | <ul> <li>Added clarification to leaf 07H in the CPUID instruction.</li> <li>Added MSR index for IA32_UMWAIT_CONTROL MSR.</li> <li>Updated registers in TPAUSE and UMWAIT instructions.</li> <li>Updated TPAUSE and UMWAIT intrinsics.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | May 2018     |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Date         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| -035     | <ul> <li>Updated Table 1-2 "Recent Instruction Set Extensions / Features<br/>Introduction in Intel® 64 and IA-32 Processors" to list the AVX512_VNNI<br/>instruction set architecture on a separate line due to presence on future<br/>processors available sooner than previously listed.</li> <li>Updated CPUID instruction in various places.</li> <li>Removal of NDD/DDS/NDS terms from instructions. Note: Previously, the<br/>terms NDS, NDD and DDS were used in instructions with an EVEX (or<br/>VEX) prefix. These terms indicated that the vvvv field was valid for<br/>encoding, and specified register usage. These terms are no longer<br/>necessary and are redundant with the instruction operand encoding<br/>tables provided with each instruction. The instruction operand encoding<br/>tables give explicit details on all operands, indicating where every<br/>operand is stored and if they are read or written. If vvvv is not listed as<br/>an operand in the instruction operand encoding table, then EVEX (or<br/>VEX) vvvv must be 0b1111.</li> <li>Added additional #GP exception condition to TPAUSE and UMWAIT.</li> <li>Updated Chapter 5 "Hardware Feedback Interface ISA Extensions" as<br/>follows: changed scheduler/software to operating system or OS, changed<br/>LP0 Scheduler Feedback to LP0 Capability Values, various description<br/>updates, clarified that capability updates are independent, and added an<br/>update to clarify that bits 0 and 1 will always be set together in Section<br/>5.1.4.</li> <li>Added IA32_CORE_CAPABILITY MSR to Chapter 6 "AC Split Lock<br/>Detection".</li> </ul> | October 2018 |

| -036     | <ul> <li>Added AVX512_BF16 instructions in chapter 2; related CPUID information updated in chapter 1.</li> <li>Added new section to chapter 1 describing bfloat16 format.</li> <li>CPUID leaf updates to align with the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Removed CLDEMOTE, TPAUSE, UMONITOR, and UMWAIT instructions; they now reside in the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Changes now marked by green change bars and green font in order to view changes at a text level.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | April 2019   |

| -037     | <ul> <li>Removed chapter 3, "EPT-Based Sub-Page Permissions", chapter 4,<br/>"Intel<sup>®</sup> Processor Trace: VMX Improvements", and chapter 6, "Split Lock<br/>Detection"; this information is in the Intel<sup>®</sup> 64 and IA-32 Architectures<br/>Software Developer's Manual.</li> <li>Removed MOVDIRI and MOVDIR64B instructions; they now reside in the<br/>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Updated Table 1-2 with new features in future processors.</li> <li>Updated Table 1-3 with support for AVX512_VP2INTERSECT.</li> <li>Updated Table 1-5 with support for ENQCMD: Enqueue Stores.</li> <li>Added ENQCMD/ENQCMDS and VP2INTERSECTD/VP2INTERSECTQ<br/>instructions, and updated CPUID accordingly.</li> <li>Added new chapter: Chapter 4, Enqueue Stores and Process Address<br/>Space Identifiers (PASIDs).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | May 2019     |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| -038     | <ul> <li>Removed instruction extensions/features from Table 1-2 "Recent<br/>Instruction Set Extensions / Features Introduction in Intel<sup>®</sup> 64 and IA-32<br/>Processors" that are available in processors covered in the Intel<sup>®</sup> 64 and<br/>IA-32 Architectures Software Developer's Manual. This information can<br/>be found in Chapter 5 "Instruction Set Summary", of Volume 1.</li> <li>In Section 1.7, "Detection of Future Instructions", removed instructions<br/>from Table 1-5 "Future Instructions" that are available in processors<br/>covered in the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's<br/>Manual.</li> <li>Removed instructions with the following CPUID feature flags:<br/>AVX512_VNNI, VAES, GFNI (AVX/AVX512), AVX512_VBMI2,<br/>VPCLMULQDQ, AVX512_BITALG; they now reside in the Intel<sup>®</sup> 64 and<br/>IA-32 Architectures Software Developer's Manual.</li> <li>CPUID instruction updated with Hybrid information sub-leaf 1AH,<br/>SERIALIZE and TSXLDTRK support, updates to the L3 Cache Intel RDT<br/>Monitoring Capability Enumeration Sub-leaf.</li> <li>Replaced ← with := notation in operation sections of instructions. These<br/>changes are not marked with change bars.</li> <li>Added the following instructions: SERIALIZE, XRESLDTRK, XSUSLDTRK.</li> <li>Updates to Chapter 4, "Hardware Feedback Interface ISA Extensions".</li> <li>Added Chapter 5, "TSX Suspend Load Address Tracking".</li> <li>Added Chapter 7, "Architectural Last Branch Records (LBRs)".</li> <li>Added Chapter 7, "Architectural Last Branch Records (LBRs)".</li> <li>Added Chapter 9, "Intel<sup>®</sup> Resource Director Technology Feature<br/>Updates".</li> </ul> | March 2020 |

| -039     | <ul> <li>Updated Section 1.1 "About this Document" to reflect chapter changes in this release.</li> <li>Added Section 1.2 "DisplayFamily and DisplayModel for Future Processors".</li> <li>Updated Table 1-2 "Recent Instruction Set Extensions / Features Introduction in Intel® 64 and IA-32 Processors".</li> <li>CPUID instruction updated.</li> <li>Removed Chapter 4 "Hardware Feedback Interface". This information is now in the Intel® 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Updated Figure 5-1 "Example HLAT Software Usage".</li> <li>Added Table 6-5 "Encodings for 64-Bit Guest-State Fields (0010_10xx_xxxx_xxAb)" to Chapter 6.</li> <li>Added Chapter 8 "Bus Lock and VM Notify".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | June 2020  |

| -040     | <ul> <li>Updated Section 1.1 "About this Document" to reflect chapter changes in this release.</li> <li>Updated Table 1-2 "Recent Instruction Set Extensions / Features Introduction in Intel® 64 and IA-32 Processors".</li> <li>CPUID instruction updated.</li> <li>Added notation updates to the beginning of Chapter 2. Updated ENQCMD and ENQCMDS instructions to use this notation.</li> <li>Added Chapter 3, "Intel® AMX Instruction Set Reference, A-Z".</li> <li>Minor updates to Chapter 6, "Hypervisor-managed Linear Address Translation".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | June 2020  |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Date          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| -041     | <ul> <li>Updated Section 1.1 "About this Document" to reflect chapter changes in this release.</li> <li>Updated Table 1-2 "Recent Instruction Set Extensions / Features Introduction in Intel® 64 and IA-32 Processors".</li> <li>CPUID instruction updated for enumeration of several new features.</li> <li>PCONFIG instruction updated.</li> <li>Added CLUI, HRESET, SENDUIPI, STUI, TESTUI, UIRET, VPDPBUSD, VPDPBUSDS, VPDPWSSD, and VPDPWSSDS instructions to Chapter 2.</li> <li>Updated Figure 3-2, "The TMUL Unit".</li> <li>Update to pseudocode of TILELOADD/TILELOADDT1 instruction.</li> <li>Addition to Section 6.2, "VMCS Changes".</li> <li>Update to Section 9.1 "Bus Lock Debug Exception".</li> <li>Added Chapter 12, "Performance Monitoring Updates".</li> <li>Added Chapter 13, "Enhanced Hardware Feedback Interface".</li> </ul> | October 2020  |

| -042     | <ul> <li>CPUID instruction updated.</li> <li>Removed the following instructions: VCVTNE2PS2BF16,<br/>VCVTNEPS2BF16, VDPBF16PS, VP2INTERSECTD/VP2INTERSECTQ, and<br/>WBNOINVD. They can be found in the Intel<sup>®</sup> 64 and IA-32 Architectures<br/>Software Developer's Manual, Volume 2C.</li> <li>Updated bit positions in Section 6.12, "Changes to VMX Capability<br/>Reporting".</li> <li>Typo correction in Chapter 8, "Non-Write-Back Lock Disable<br/>Architecture".</li> <li>Several updates to Chapter 13, "Enhanced Hardware Feedback Interface<br/>(EHFI)".</li> <li>Added Chapter 14, "Linear Address Masking (LAM)".</li> <li>Added Chapter 15, "Error Codes for Processors Based on Sapphire Rapids<br/>Microarchitecture".</li> </ul>                                                                                               | December 2020 |

| -043     | <ul> <li>Updated CPUID instruction.</li> <li>Typo correction in Table 8-2, "TEST_CTRL MSR".</li> <li>Typo corrections in Section 14.1, "Enumeration, Enabling, and<br/>Configuration".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | February 2021 |

| -044     | <ul> <li>Updated Table 1-2, "Recent Instruction Set Extensions / Features<br/>Introduction in Intel® 64 and IA-32 Processors".</li> <li>Updated CPUID instruction.</li> <li>Updates to the ENQCMD and ENQCMDS instructions.</li> <li>Removed the PCONFIG instruction; it can be found in the Intel<sup>®</sup> 64 and<br/>IA-32 Architectures Software Developer's Manual, Volume 2B.</li> <li>Corrected typo in the VPDPBUSD instruction.</li> <li>Updates to Table 3-1, "Intel® AMX Exception Classes ".</li> <li>Change in terminology updates in Chapter 7, "Architectural Last Branch<br/>Records (LBRs)".</li> <li>Updated Chapter 6 to introduce the official technology name: Intel®<br/>Virtualization Technology - Redirect Protection.</li> <li>Added Chapter 16, "IPI Virtualization".</li> </ul>                                            | May 2021      |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -045     | <ul> <li>Chapter 1: Updated the CPUID instruction.</li> <li>Chapter 2: Updated ENQCMD and ENQCMDS to remove statements that these instructions ignore unused bits; this is incorrect. Removed HRESET, SERIALIZE, VPDPBUSD, VPDPBUSDS, VPDPWSSD, and VPDPWSSDS instructions; these instructions can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual. Updates to SENDUIPI instruction operand encoding and 64-bit mode exceptions. Update to UIRET pseudocode.</li> <li>Chapter 3: Updated Section 3.3., "Recommendations for System Software".</li> <li>Removed Chapter 6, "Intel<sup>®</sup> Virtualization Technology: Redirect Protection"; this information can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Removed Chapter 7, "Architectural Last Branch Records (LBRs)"; this information can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Removed Chapter 12, "Performance Monitoring Updates"; this information can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Removed Chapter 13, "Enhanced Hardware Feedback Interface (EHFI)"; this information can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Removed Chapter 13, "Enhanced Hardware Feedback Interface (EHFI)"; this information can be found in the Intel 64 and IA-32 Architectures Software Developer's Manual.</li> <li>Updated Section 7.1.1, "Bus Lock VM Exit" to provide additional clarity and details.</li> <li>Updated Chapter 8, "Intel<sup>®</sup> Resource Director Technology Feature Updates" to update to Chapter 10, "Linear Address Masking (LAM)", to provide additional clarity.</li> <li>Corrected two typos in the current Table 11-1, "Intel IMC MC Error Codes for IA32_MCi_STATUS (i= 13-20)."</li> <li>Added Chapter 13, "Asynchronous Enclave Exit Notify and the EDECCSSA User Leaf Function."</li> </ul> | June 2022      |

| -046     | <ul> <li>Chapter 1: Updated Table 1-1, "CPUID Signature Values of<br/>DisplayFamily_DisplayModel." Updated Table 1-2, "Recent Instruction Set<br/>Extensions / Features Introduction in Intel® 64 and IA-32 Processors."<br/>Updated the CPUID instruction.</li> <li>Chapter 2: Added the following instructions: AADD, AAND, AOR, AXOR,<br/>CMPccXADD, RDMSRLIST, VBCSTNEBF162PS, VBCSTNESH2PS,<br/>VCVTNEEBF162PS, VCVTNEEPH2PS, VCVTNEOBF162PS,<br/>VCVTNEOPH2PS, VCVTNEPS2BF16, VPDPB[SU,UU,SS]D[,S],<br/>VPMADD52HUQ, VPMADD52LUQ, WRMSRLIST, and WRMSRNS.</li> <li>Chapter 3: Added section 3.4, "Operand Restrictions," and added the<br/>TDPFP16PS instruction.</li> <li>Added Chapter 14, "Code Prefetch Instruction Updates."</li> <li>Added Chapter 15, "Next Generation Performance Monitoring Unit<br/>(PMU)."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | September 2022 |

# **REVISION HISTORY**

### **CHAPTER 1**

# FUTURE INTEL® ARCHITECTURE INSTRUCTION EXTENSIONS AND FEATURES

|     | About This Document                                                                   |      |

|-----|---------------------------------------------------------------------------------------|------|

| 1.2 | DisplayFamily and DisplayModel for Future Processors                                  | 1-1  |

| 1.3 | Instruction Set Extensions and Feature Introduction in Intel® 64 and IA-32 Processors | 1-2  |

| 1.4 | Detection of Future Instructions and Features                                         | 1-3  |

| 1.5 | CPUID Instruction                                                                     | 1-3  |

|     | CPUID—CPU Identification                                                              | .1-3 |

| 1.6 | Compressed Displacement (disp8*N) Support in EVEX                                     | 1-47 |

|     | bfloat16 Floating-Point Format.                                                       |      |

|     | 5                                                                                     |      |

# CHAPTER 2

# INSTRUCTION SET REFERENCE, A-Z

| 2.1 | Instruction Set Reference                                                                         | 2-1  |

|-----|---------------------------------------------------------------------------------------------------|------|

|     | AADD—Atomically Add                                                                               |      |

|     | AAND—Atomically AND                                                                               | 2-4  |

|     | AOR—Atomically OR                                                                                 |      |

|     | AXOR—Atomically XOR                                                                               |      |

|     | CLUI—Clear User Interrupt Flag                                                                    | 2-10 |

|     | CMPccXADD—Compare and Add if Condition is Met                                                     | 2-11 |

|     | ENQCMD—Enqueue Command                                                                            | 2-16 |

|     | ENQCMDS—Enqueue Command Supervisor                                                                | 2-19 |

|     | RDMSRLIST—Read List of Model Specific Registers                                                   |      |

|     | SENDUIPI—Send User Interprocessor Interrupts                                                      |      |

|     | STUI—Set User Interrupt Flag                                                                      |      |

|     | TESTUI—Determine User Interrupt Flag                                                              | 2-29 |

|     | UIRET—User-Interrupt Return                                                                       |      |

|     | VBCSTNEBF162PS—Load BF16 Element and Convert to FP32 Element With Broadcast                       |      |

|     | VBCSTNESH2PS—Load FP16 Element and Convert to FP32 Element with Broadcast                         | 2-33 |

|     | VCVTNEEBF162PS—Convert Even Elements of Packed BF16 Values to FP32 Values                         | 2-34 |

|     | VCVTNEEPH2PS—Convert Even Elements of Packed FP16 Values to FP32 Values                           | 2-35 |

|     | VCVTNEOBF162PS—Convert Odd Elements of Packed BF16 Values to FP32 Values                          | 2-36 |

|     | VCVTNEOPH2PS—Convert Odd Elements of Packed FP16 Values to FP32 Values                            |      |

|     | VCVTNEPS2BF16—Convert Packed Single-Precision Floating-Point Values to BF16 Values                | 2-38 |

|     | VPDPB[SU,UU,SS]D[,S]—Multiply and Add Unsigned and Signed Bytes With and Without Saturation       |      |

|     | VPMADD52HUQ—Packed Multiply of Unsigned 52-Bit Integers and Add the High 52-Bit Products to Qword |      |

|     | Accumulators                                                                                      | 2-43 |

|     | VPMADD52LUQ—Packed Multiply of Unsigned 52-Bit Integers and Add the Low 52-Bit Products to Qword  |      |

|     | Accumulators                                                                                      | 2-44 |

|     | WRMSRLIST—Write List of Model Specific Registers                                                  | 2-45 |

|     | WRMSRNS—Non-Serializing Write to Model Specific Register                                          |      |

|     | XRESLDTRK—Resume Tracking Load Addresses                                                          |      |

|     | XSUSLDTRK—Suspend Tracking Load Addresses                                                         |      |

|     | · · · · · · · · · · · · · · · · · · ·                                                             |      |

# CHAPTER 3

# INTEL® AMX INSTRUCTION SET REFERENCE, A-Z

| 3.1   | Introduction                                    | 3-1  |

|-------|-------------------------------------------------|------|

| 3.1.1 | Tile Architecture Details                       | .3-3 |

| 3.1.2 | TMUL Architecture Details                       | .3-4 |

| 3.1.3 | Handling of Tile Row and Column Limits          | .3-4 |

| 3.1.4 | Exceptions and Interrupts                       | .3-5 |

| 3.2   | Intel® AMX and the XSAVE Feature Set            | 3-5  |

| 3.2.1 | State Components for Intel® AMX                 | .3-5 |

| 3.2.2 | XSAVE-Related Enumeration for Intel® AMX        | .3-6 |

| 3.2.3 | Enabling Intel® AMX As an XSAVE-Enabled Feature |      |

| 3.2.4 | Loading of XTILECFG and XTILEDATA by XRSTOR and XRSTORS                                      | 3-7  |

|-------|----------------------------------------------------------------------------------------------|------|

| 3.2.5 | Saving of XTILEDATA by XSAVE, XSAVEC, XSAVEOPT, and XSAVES                                   |      |

| 3.2.6 | Extended Feature Disable (XFD)                                                               |      |

| 3.3   | Recommendations for System Software                                                          | 3-8  |

| 3.4   | Operand Restrictions                                                                         | 3-8  |

| 3.5   | Implementation Parameters                                                                    |      |

| 3.6   | Helper Functions                                                                             |      |

| 3.7   | Notation                                                                                     |      |

| 3.8   | Exception Classes                                                                            | 3-10 |

| 3.9   | Instruction Set Reference                                                                    |      |

|       | LDTILECFG—Load Tile Configuration                                                            | 3-13 |

|       | STTILECFG—Store Tile Configuration                                                           |      |

|       | TDPBF16PS—Dot Product of BF16 Tiles Accumulated into Packed Single Precision Tile            | 3-18 |

|       | TDPBSSD/TDPBSUD/TDPBUSD/TDPBUUD—Dot Product of Signed/Unsigned Bytes with Dword Accumulation | 3-20 |

|       | TDPFP16PS—Dot Product of FP16 Tiles Accumulated into Packed Single Precision Tile            | 3-22 |

|       | TILELOADD/TILELOADDT1—Load Tile                                                              |      |

|       | TILERELEASE—Release Tile                                                                     | 3-26 |

|       | TILESTORED—Store Tile                                                                        | 3-27 |

|       | TILEZERO—Zero Tile                                                                           | 3-28 |

|       |                                                                                              |      |

### CHAPTER 4

# ENQUEUE STORES AND PROCESS ADDRESS SPACE IDENTIFIERS (PASIDS)

| 4.1   | The IA32_PASID MSR                                  | . 4-1 |

|-------|-----------------------------------------------------|-------|

| 4.2   | The PASID State Component for the XSAVE Feature Set | . 4-1 |

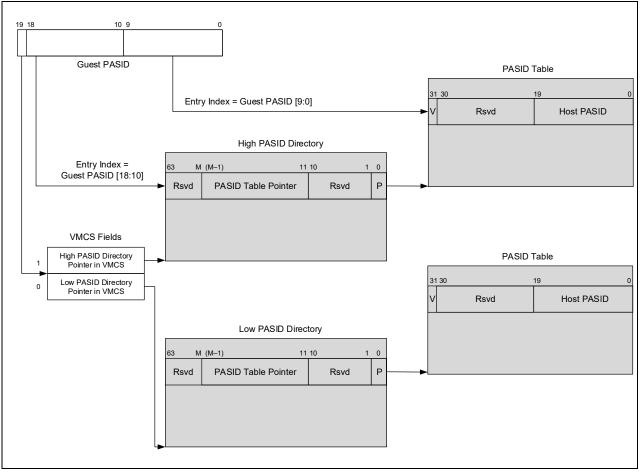

| 4.3   | PASID Translation                                   | . 4-2 |

| 4.3.1 | PASID Translation Structures                        | . 4-2 |

| 4.3.2 | The PASID Translation Process                       | . 4-3 |

| 4.3.3 | VMX Support                                         | . 4-4 |

# CHAPTER 5 INTEL® TSX SUSPEND LOAD ADDRESS TRACKING

# CHAPTER 6

### NON-WRITE-BACK LOCK DISABLE ARCHITECTURE

|     | Enumeration                                                    | 6-1 |

|-----|----------------------------------------------------------------|-----|

| 6.2 | Enabling                                                       | 6-1 |

| 6.3 | Interaction with Intel® Software Guard Extensions (Intel® SGX) | 6-2 |

| 6.4 | Interaction with VMX Architecture                              |     |

|     | Expected Software Behavior                                     | 6-2 |

| 6.6 | Bus Locks                                                      | 6-3 |

# CHAPTER 7

# BUS LOCK AND VM NOTIFY

| 7.1   | Bus Lock Debug Exception | 7- | 1 |

|-------|--------------------------|----|---|

| 7.1.1 | Bus Lock VM Exit         | 7- | 1 |

| 7.2   | Notify VM Exit           | 7- | 1 |

# CHAPTER 8

| INTEL | " RESOURCE DIRECTOR TECHNOLOGY FEATURE UPDATES                             |       |

|-------|----------------------------------------------------------------------------|-------|

| 8.1   | Intel® RDT Feature Changes                                                 |       |

| 8.1.1 | Intel® RDT on Processors Based on Ice Lake Server Microarchitecture        | . 8-1 |

| 8.1.2 | Intel® RDT on Intel Atom® Processors Based on Tremont Microarchitecture    | . 8-1 |

| 8.1.3 | Intel® RDT in Processors Based on Sapphire Rapids Server Microarchitecture | . 8-1 |

| 8.1.4 | Intel® RDT in Processors Based on Emerald Rapids Server Microarchitecture  | . 8-2 |

| 8.1.5 | Future Intel® RDT                                                          | . 8-2 |

| 8.2   | Enumerable Memory Bandwidth Monitoring Counter Width.                      | . 8-2 |

| 8.2.1 | Memory Bandwidth Monitoring (MBM) Enabling                                 |       |

|       |                                                                            |       |

| 8.2.2 | Augmented MBM Enumeration and MSR Interfaces for Extensible Counter Width | . 8-2 |

|-------|---------------------------------------------------------------------------|-------|

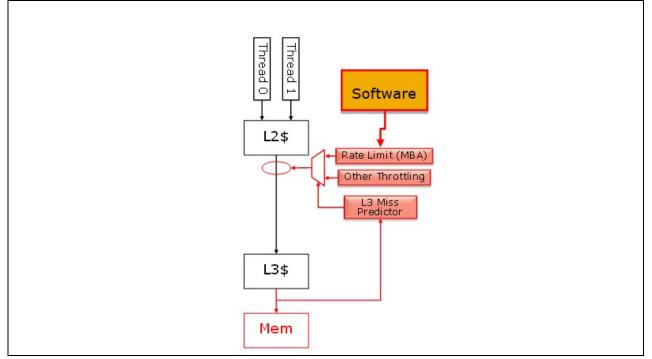

| 8.3   | Second Generation Memory Bandwidth Allocation                             | . 8-3 |

| 8.3.1 | MBA 2.0 Advantages.                                                       |       |

| 8.3.2 | MBA 2.0 Software-Visible Changes                                          | . 8-4 |

| 8.4   | Third Generation Memory Bandwidth Allocation                              |       |

| 8.4.1 | MBA 3.0 Hardware Changes                                                  | . 8-5 |

| 8.4.2 | MBA 3.0 Software-Visible Changes                                          | . 8-5 |

# CHAPTER 9

| CHAPI            | IER 9                                                      |                 |

|------------------|------------------------------------------------------------|-----------------|

| <b>USER I</b>    | INTERRUPTS                                                 |                 |

| 9.1              | Introduction                                               | <del>)</del> -1 |

| 9.2              | Enumeration and Enabling                                   | <del>)</del> -1 |

| 9.3              | User-Interrupt State and User-Interrupt MSRs               | <del>)</del> -2 |

| 9.3.1            | User-Interrupt State                                       |                 |

| 9.3.2            | User-Interrupt MSRs                                        |                 |

| 9.4              | Evaluation and Delivery of User Interrupts                 |                 |

| 9.4.1            | User-Interrupt Recognition                                 |                 |

| 9.4.2            | User-Interrupt Delivery S                                  |                 |

| 9.5              | User-Interrupt Notification Identification and Processing. |                 |

| 9.5.1            | User-Interrupt Notification Identification                 |                 |

| 9.5.2            | User-Interrupt Notification Processing                     |                 |

| 9.6              | New Instructions 9                                         |                 |

| 9.7              | User IPIs S                                                |                 |

| 9.8              | Legacy Instruction Support                                 |                 |

| 9.8.1            | Support by RDMSR and WRMSR                                 |                 |

| 9.8.2            | Support by the XSAVE Feature Set                           |                 |

| 9.8.2.1          | User-Interrupt State Component                             |                 |

| 9.8.2.2          | XSAVE-Related Enumeration                                  |                 |

| 9.8.2.3          | XSAVES                                                     |                 |

| 9.8.2.4<br>9.9   | XRSTORS                                                    |                 |

| 9.9<br>9.9.1     | VMX Support                                                |                 |

| 9.9.2            | Changes to VMX Non-Root Operation                          |                 |

| 9.9.2.1          | Treatment of Ordinary Interrupts                           |                 |

| 9.9.2.1          | Treatment of Virtual Interrupts                            |                 |

| 9.9.2.2          | VM Exits Incident to New Operations                        |                 |

| 9.9.2.4          | Access to the User-Interrupt MSRs                          |                 |

| 9.9.2.5          | Operation of SENDUIPI                                      |                 |

| 9.9.3            | Changes to VM Entries                                      |                 |

| 9.9.3.1          | Checks on the Guest-State Area9-                           | 13              |

| 9.9.3.2          | Loading MSRs9-                                             |                 |

| 9.9.3.3          | Event Injection                                            | 13              |

| 9.9.3.4          | User-Interrupt Recognition After VM Entry9-                | 14              |

| 9.9.4            | Changes to VM Exits                                        |                 |

| 9.9.4.1          | Recording VM-Exit Information                              | 14              |

| 9.9.4.2          | Saving Guest State                                         |                 |

| 9.9.4.3          | Saving MSRs                                                |                 |

| 9.9.4.4          | Loading Host State                                         |                 |

| 9.9.4.5          | 9-User-Interrupt Recognition After VM Exit                 | 14              |

| 9.9.4.6<br>9.9.5 | Changes to VMX Capability Reporting                        |                 |

| 2.2.2            | changes to vrink capability Reporting                      | IJ              |

# CHAPTER 10 LINEAR ADDRESS MASKING (LAM)

| 10.1   | Enumeration, Enabling, and Configuration                                       | 10-1 |

|--------|--------------------------------------------------------------------------------|------|

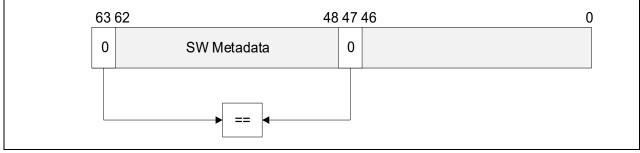

| 10.2   | Treatment of Data Accesses with LAM Active for User Pointers                   | 10-1 |

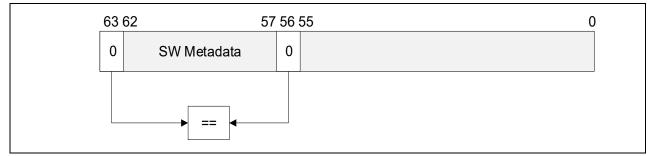

| 10.3   | Treatment of Data Accesses with LAM Active for Supervisor Pointers             | 10-3 |

|        | Canonicality Checking for Data Addresses Written to Control Registers and MSRs | 10-4 |

| 10.5   | Paging Interactions                                                            | 10-4 |

|        | VMX Interactions                                                               |      |

| 10.6.1 | Guest Linear Address                                                           | 10-4 |

| 10.6.2 | VM-Entry Checking of Values of CR3 and CR4           | 10-5 |

|--------|------------------------------------------------------|------|

| 10.6.3 | CR3-Target Values.                                   |      |

| 10.6.4 | Hypervisor-Managed Linear Address Translation (HLAT) | 10-5 |

| 10.7   | Debug and Tracing Interactions.                      | 10-5 |

| 10.7.1 | Debug Registers                                      | 10-5 |

| 10.7.2 | Intel® Processor Trace                               | 10-5 |

| 10.8   | Intel® SGX Interactions                              |      |

| 10.9   | System Management Mode (SMM) Interactions            | 10-6 |

#### CHAPTER 11 ERROR CODES FOR PROCESSORS BASED ON SAPPHIRE RAPIDS MICROARCHITECTURE

| CITICOL |                                                   |      |

|---------|---------------------------------------------------|------|

| 11.1    | Integrated Memory Controller Machine Check Errors | 11-1 |

# CHAPTER 12 IPI VIRTUALIZATION

| 12.1   | Introduction                                                | 12-1   |

|--------|-------------------------------------------------------------|--------|

| 12.2   | Interprocessor Interrupts                                   | 12-1   |

| 12.3   | Existing Features to Virtualize APIC and Interrupts         | 12-1   |

| 12.3.1 | Virtual-APIC Page and Virtualizing Writes to APIC Registers | 12-2   |

| 12.3.2 | Virtual-Interrupt Posting                                   | 12-3   |

| 12.4   | Changes to VMCS and Related Structures                      | 12-3   |

| 12.4.1 | New VM-Execution Control                                    | . 12-3 |

| 12.4.2 | PID-Pointer Table                                           | 12-3   |

| 12.5   | Changes to VM Entries                                       | 12-4   |

| 12.6   | VMX Non-Root Operation                                      | 12-4   |

| 12.6.1 | Virtualizing Memory-Mapped Writes to ICR_LO                 | . 12-4 |

| 12.6.2 | Virtualizing WRMSR to ICR                                   |        |

| 12.6.3 | Virtualizing SENDUIPI                                       | 12-5   |

| 12.6.4 | IPI Virtualization                                          | 12-6   |

| 12.6.5 | Other Accesses to APIC Registers                            | 12-7   |

| 12.7   | Changes to VMX Capability Reporting                         | 12-7   |

|        |                                                             |        |

### CHAPTER 13 ASYNCHRONOUS ENCLAVE EXIT NOTIFY AND THE EDECCSSA USER LEAF FUNCTION

| 13.1   | Introduction                                                                     | . 13-1 |

|--------|----------------------------------------------------------------------------------|--------|

| 13.2   | Enumeration and Enabling                                                         | . 13-2 |

| 13.3   | Changes to Enclave Data Structures                                               | . 13-2 |

| 13.3.1 | TČS.FLAGS Changes                                                                | 13-2   |

| 13.3.2 | SSA.GPRSGX Changes                                                               | 13-2   |

| 13.3.3 | ATTRIBUTES Changes.                                                              | 13-2   |

| 13.4   | Changes to Intel <sup>®</sup> SGX User Leaf Functions                            |        |

| 13.5   | New Intel® SGX User Leaf Function: EDECCSSA                                      | . 13-3 |

|        | EDECCSSA—Decrements TCS.CSSA                                                     |        |

| 13.6   | Implications for Enclave Code Debug and Profiling                                | . 13-6 |

| 13.7   | Implications for Enclave Code Debug and Profiling<br>Interaction with Intel® CET | . 13-6 |

| 13.8   | Changes to Intel <sup>®</sup> SGX User Leaf Function Operation                   |        |

| 13.8.1 | Changes to EENTER Operation                                                      | 13-7   |

| 13.8.2 | Changes to ERESUME Operation                                                     | .13-14 |

|        |                                                                                  |        |

# CHAPTER 14

| CODE PREFETCH INSTRUCTION UPDATES           |  |

|---------------------------------------------|--|

| DDEEETCHb Drofotsh Data or Code Into Cashor |  |

| PREFETCHh—Prefetch Data or Code Into Caches1 | 4 | -1 |

|----------------------------------------------|---|----|

|----------------------------------------------|---|----|

#### CHAPTER 15

| NEXT   | GENERATION PERFORMANCE MONITORING UNIT (PMU) |      |

|--------|----------------------------------------------|------|

| 15.1   | New Enumeration Architecture                 | 15-1 |

| 15.1.1 | CPUID Sub-Leafing                            | 15-1 |

| Reporting of Hybrid Resources                       | . 15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fixed-Function Counters Hybrid Bitmap               | . 15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Architectural Performance Monitoring Events Bitmap. | . 15-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| New Architectural Events                            | . 15-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Topdown Microarchitecture Analysis Level 1          | . 15-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Topdown Backend Bound-Event Select A4H, Umask 02H   | . 15-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Topdown Bad Speculation-Event Select 73H, Umask 00H | . 15-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Topdown Frontend Bound-Event Select 9CH, Umask 01H  | . 15-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

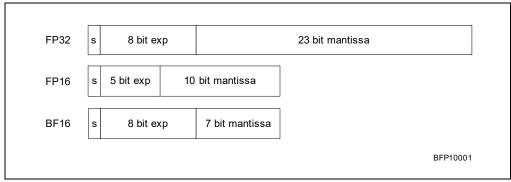

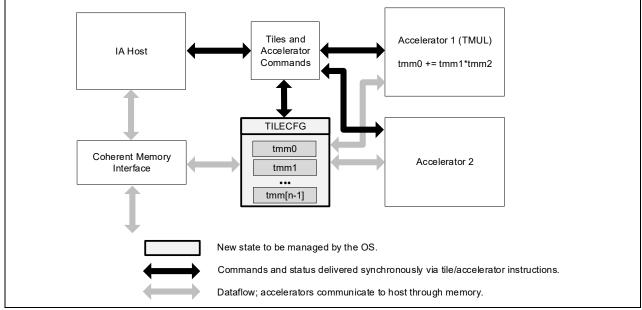

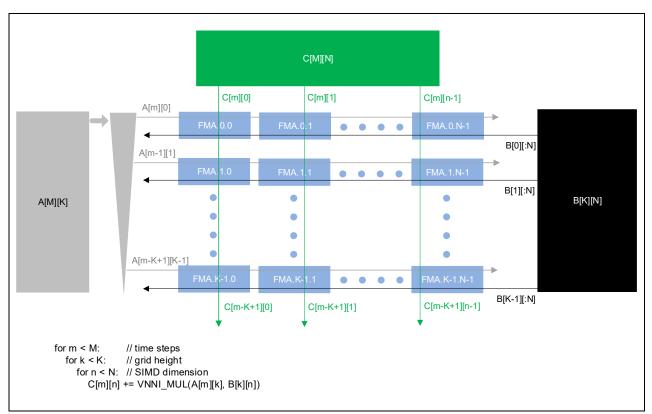

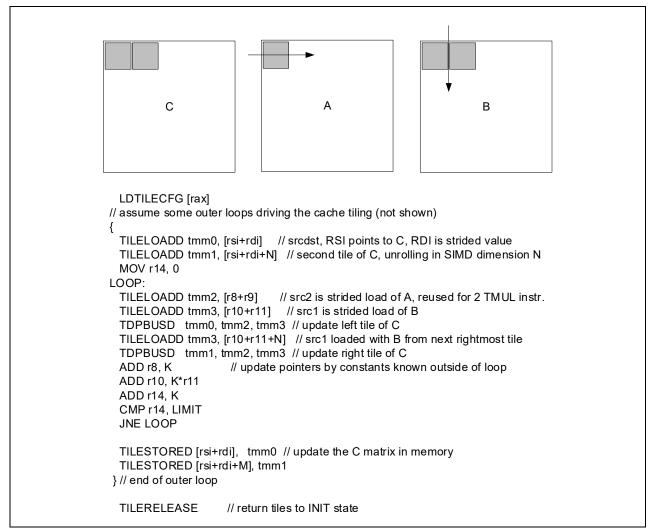

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |