# **Intel® IA-64 Architecture Software Developer's Manual**

**Volume 3: Instruction Set Reference**

January 2000

Order Number: 245319-001

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel® IA-64 processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's website at http://developer.intel.com/design/litcentr.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

# intel。 Contents

| 1 | About | t this Manual                                               | 1-1  |

|---|-------|-------------------------------------------------------------|------|

|   | 1.1   | Overview of Volume 1: IA-64 Application Architecture        | 1-1  |

|   |       | 1.1.1 Part 1: IA-64 Application Architecture Guide          |      |

|   |       | 1.1.2 Part 2: IA-64 Optimization Guide                      | 1-2  |

|   | 1.2   | Overview of Volume 2: IA-64 System Architecture             | 1-2  |

|   |       | 1.2.1 Part 1: IA-64 System Architecture Guide               | 1-2  |

|   |       | 1.2.2 Part 2: IA-64 System Programmer's Guide               |      |

|   |       | 1.2.3 Appendices                                            | 1-4  |

|   | 1.3   | Overview of Volume 3: Instruction Set Reference             |      |

|   |       | 1.3.1 Part 1: IA-64 Instruction Set Descriptions            |      |

|   |       | 1.3.2 Part 2: IA-32 Instruction Set Descriptions            |      |

|   | 1.4   | Overview of Volume 4: Itanium™ Processor Programmer's Guide |      |

|   | 1.5   | Terminology                                                 |      |

|   | 1.6   | Related Documents                                           | 1-6  |

| 2 | IA-64 | Instruction Reference                                       | 2-1  |

|   | 2.1   | Instruction Page Conventions                                |      |

|   | 2.2   | Instruction Descriptions                                    | 2-2  |

| 3 | IA-64 | Pseudo-Code Functions                                       | 3-1  |

| 4 | IA-64 | Instruction Formats                                         | 4-1  |

|   | 4.1   | Format Summary                                              | 4-3  |

|   | 4.2   | A-Unit Instruction Encodings                                | 4-9  |

|   |       | 4.2.1 Integer ALU                                           | 4-9  |

|   |       | 4.2.2 Integer Compare                                       | 4-12 |

|   |       | 4.2.3 Multimedia                                            |      |

|   | 4.3   | I-Unit Instruction Encodings                                |      |

|   |       | 4.3.1 Multimedia and Variable Shifts                        |      |

|   |       | 4.3.2 Integer Shifts                                        |      |

|   |       | 4.3.3 Test Bit                                              |      |

|   |       | 4.3.4 Miscellaneous I-Unit Instructions                     |      |

|   |       | 4.3.5 GR/BR Moves                                           |      |

|   |       | 4.3.6 GR/Predicate/IP Moves                                 |      |

|   |       | 4.3.7 GR/AR Moves (I-Unit)                                  |      |

|   |       | 4.3.8 Sign/Zero Extend/Compute Zero Index                   |      |

|   | 4.4   | M-Unit Instruction Encodings                                |      |

|   |       | 4.4.1 Loads and Stores                                      |      |

|   |       | 4.4.2 Line Prefetch                                         |      |

|   |       | 4.4.3 Semaphores                                            |      |

|   |       | 4.4.4 Set/Get FR                                            |      |

|   |       | 4.4.5 Speculation and Advanced Load Checks                  |      |

|   |       | 4.4.6 Cache/Synchronization/RSE/ALAT                        |      |

|   |       | 4.4.7 GR/AR Moves (M-Unit)                                  |      |

|   |       | 4.4.8 GR/CR Moves                                           |      |

|   |       | 4.4.9 Miscellaneous M-Unit Instructions                     |      |

|   |       | 4.4.10 System/Memory Management                             | 4-58 |

#### intط<sub>®</sub>

|   | 4.5     | B-Unit Instruction Encodings                           | 4-63 |

|---|---------|--------------------------------------------------------|------|

|   |         | 4.5.1 Branches                                         | 4-63 |

|   |         | 4.5.2 Branch Predict and Nop                           | 4-68 |

|   |         | 4.5.3 Miscellaneous B-Unit Instructions                | 4-70 |

|   | 4.6     | F-Unit Instruction Encodings                           | 4-71 |

|   |         | 4.6.1 Arithmetic                                       | 4-73 |

|   |         | 4.6.2 Parallel Floating-point Select                   | 4-74 |

|   |         | 4.6.3 Compare and Classify                             | 4-74 |

|   |         | 4.6.4 Approximation                                    |      |

|   |         | 4.6.5 Minimum/Maximum and Parallel Compare             |      |

|   |         | 4.6.6 Merge and Logical                                |      |

|   |         | 4.6.7 Conversion                                       |      |

|   |         | 4.6.8 Status Field Manipulation                        |      |

|   |         | 4.6.9 Miscellaneous F-Unit Instructions                |      |

|   | 4.7     | X-Unit Instruction Encodings                           |      |

|   |         | 4.7.1 Miscellaneous X-Unit Instructions                |      |

|   |         | 4.7.2 Move Long Immediate <sub>64</sub>                |      |

|   |         | 4.7.3 Long Branches                                    | 4-82 |

|   | 4.8     | Immediate Formation                                    |      |

| _ |         |                                                        |      |

| 5 |         | A-32 Instruction Reference                             | 5-1  |

|   | 5.1     | IA-64 Additional Faults                                |      |

|   | 5.2     | Interpreting the IA-32 Instruction Reference Pages     |      |

|   |         | 5.2.1 IA-32 Instruction Format                         |      |

|   |         | 5.2.2 Operation                                        |      |

|   |         | 5.2.3 Flags Affected                                   |      |

|   |         | 5.2.4 FPU Flags Affected                               |      |

|   |         | 5.2.5 Protected Mode Exceptions                        |      |

|   |         | 5.2.6 Real-address Mode Exceptions                     |      |

|   |         | 5.2.7 Virtual-8086 Mode Exceptions                     | 5-10 |

|   |         | 5.2.8 Floating-point Exceptions                        |      |

|   | 5.3     | IA-32 Base Instruction Reference                       | 5-10 |

| 6 | IA-32 N | IMX™ Technology Instruction Reference                  | 6-1  |

| 7 | IA-32 S | Streaming SIMD Extension Instruction Reference         | 7-1  |

|   | 7.1     | IA-32 Streaming SIMD Extension Instructions            | 7-1  |

|   | 7.2     | About the Intel Architecture Streaming SIMD Extensions |      |

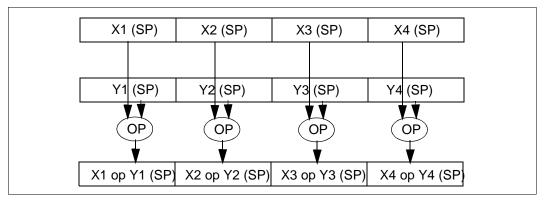

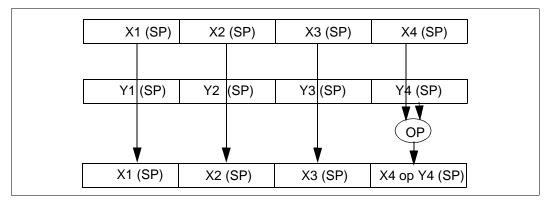

|   | 7.3     | Single Instruction Multiple Data                       | 7-2  |

|   | 7.4     | New Data Types                                         |      |

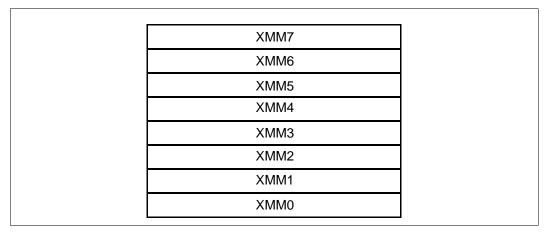

|   | 7.5     | Streaming SIMD Extension Registers                     |      |

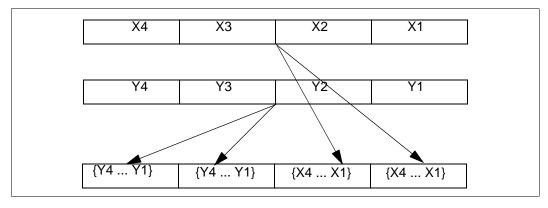

|   | 7.6     | Extended Instruction Set                               |      |

|   |         | 7.6.1 Instruction Group Review                         |      |

|   | 7.7     | IEEE Compliance                                        |      |

|   |         | 7.7.1 Real Number System                               |      |

|   |         | 7.7.2 Operating on NaNs                                |      |

|   | 7.8     | Data Formats                                           |      |

|   |         | 7.8.1 Memory Data Formats                              |      |

|   |         | 7.8.2 Streaming SIMD Extension Register Data Formats   |      |

|   | 7.9     | Instruction Formats                                    |      |

|   | 7.10    | Instruction Prefixes                                   |      |

|   | _       | Reserved Behavior and Software Compatibility           |      |

|   |         |                                                        |      |

## int<sub>el®</sub>

|      | 7.12 Notations                                     |       |

|------|----------------------------------------------------|-------|

|      | 7.13 SIMD Integer Instruction Set Extensions       | 7-98  |

|      | 7.14 Cacheability Control Instructions             | 7-112 |

|      |                                                    |       |

| Fig  | ures                                               |       |

| 9    |                                                    |       |

| 2-1  | Add Pointer                                        | 2-4   |

| 2-2  | Stack Frame                                        |       |

| 2-3  | Operation of br.ctop and br.cexit                  |       |

| 2-4  | Operation of br.wtop and br.wexit                  |       |

| 2-5  | Deposit Example                                    |       |

| 2-6  | Extract Example                                    |       |

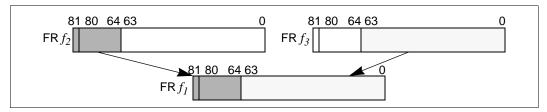

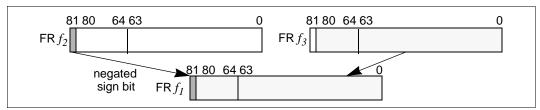

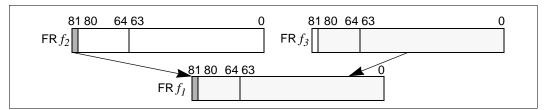

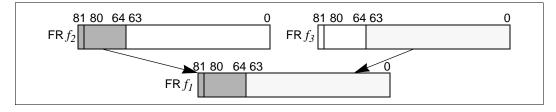

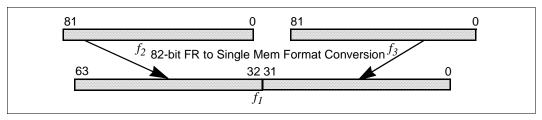

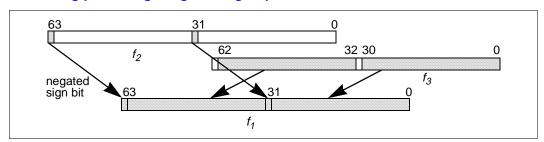

| 2-7  | Floating-point Merge Negative Sign Operation       |       |

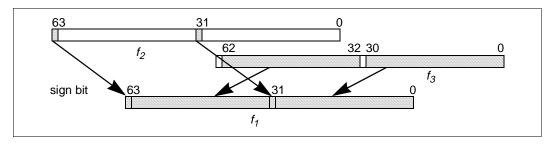

| 2-8  | Floating-point Merge Sign Operation                |       |

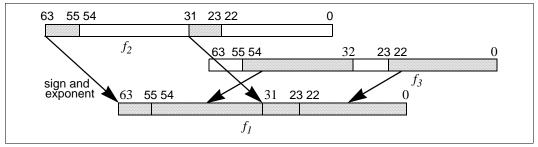

| 2-9  | Floating-point Merge Sign and Exponent Operation   |       |

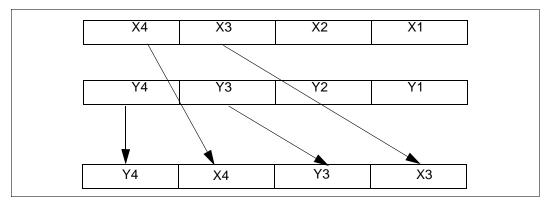

| 2-9  | Floating-point Mix Left                            |       |

| 2-10 | <b>.</b>                                           |       |

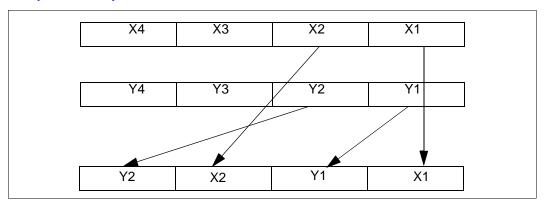

|      | Floating-point Mix Right                           |       |

| 2-12 | Floating-point Mix Left-Right                      |       |

| 2-13 | Floating-point Pack                                |       |

| 2-14 | Floating-point Merge Negative Sign Operation       |       |

| 2-15 | Floating-point Merge Sign Operation                |       |

| 2-16 | Floating-point Merge Sign and Exponent Operation   |       |

| 2-17 | Floating-point Swap                                |       |

| 2-18 | Floating-point Swap Negate Left or Right           |       |

| 2-19 | Floating-point Sign Extend Left                    |       |

| 2-20 | Floating-point Sign Extend Right                   |       |

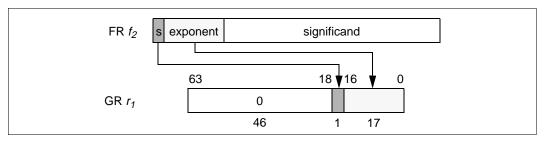

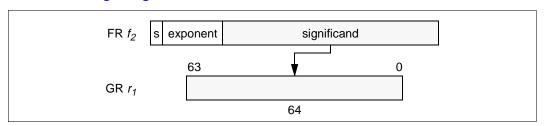

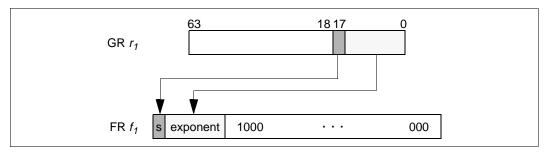

| 2-21 | Function of getf.exp                               |       |

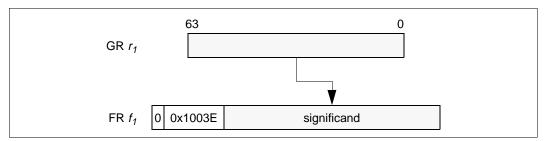

| 2-22 | Function of getf.sig                               |       |

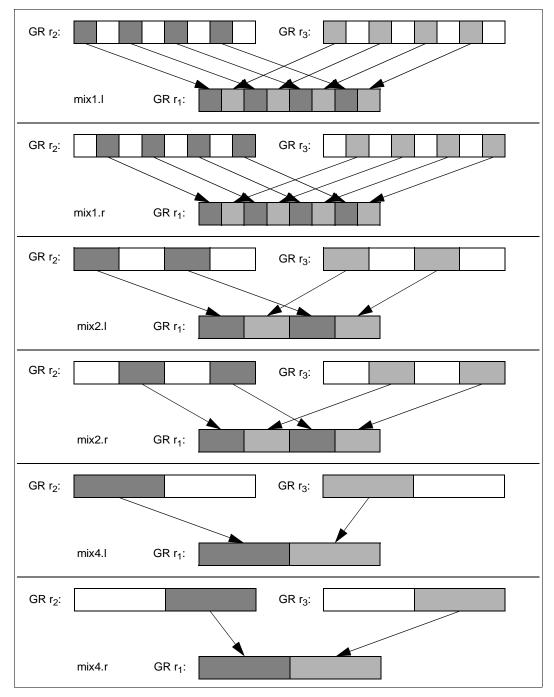

| 2-23 | Mix Example                                        |       |

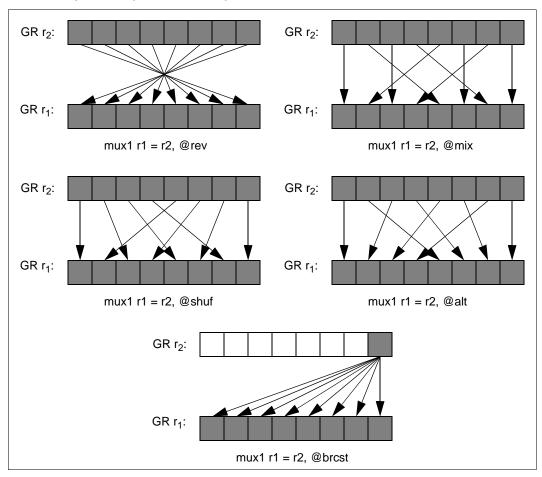

| 2-24 | Mux1 Operation (8-bit elements)                    |       |

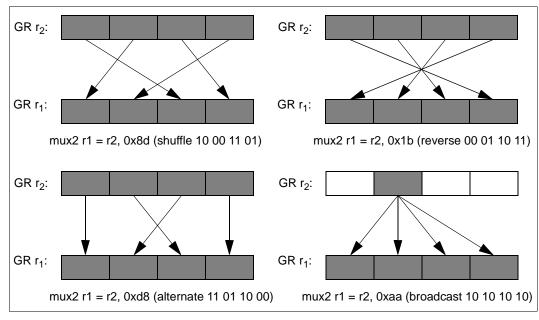

| 2-25 | Mux2 Examples (16-bit elements)                    |       |

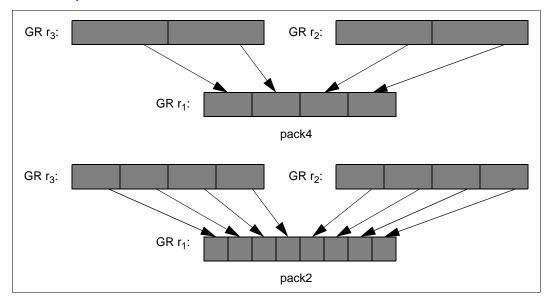

| 2-26 | Pack Operation                                     |       |

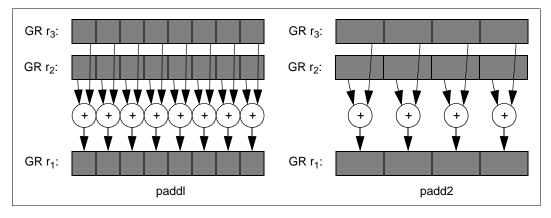

| 2-27 | Parallel Add Examples                              | 2-165 |

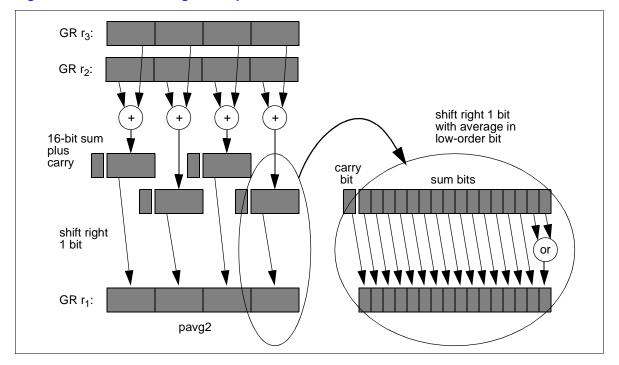

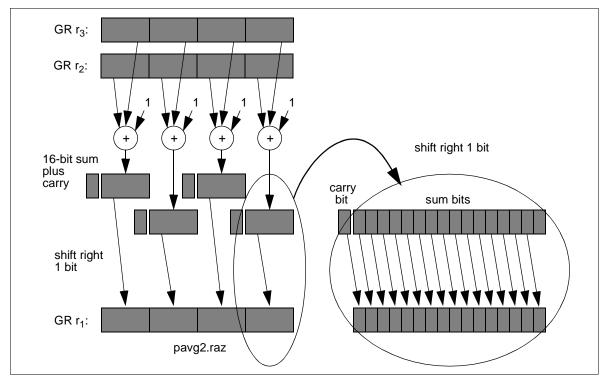

| 2-28 | Parallel Average Example                           | 2-168 |

| 2-29 | Parallel Average with Round Away from Zero Example | 2-169 |

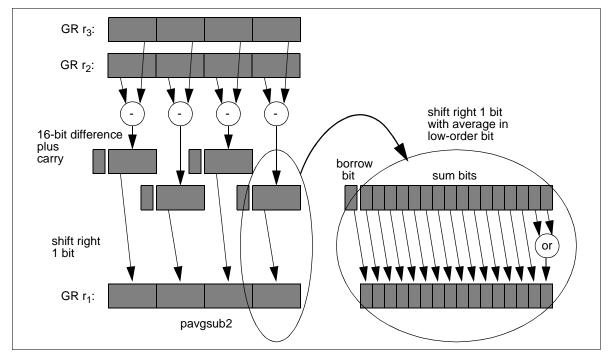

| 2-30 | Parallel Average Subtract Example                  | 2-171 |

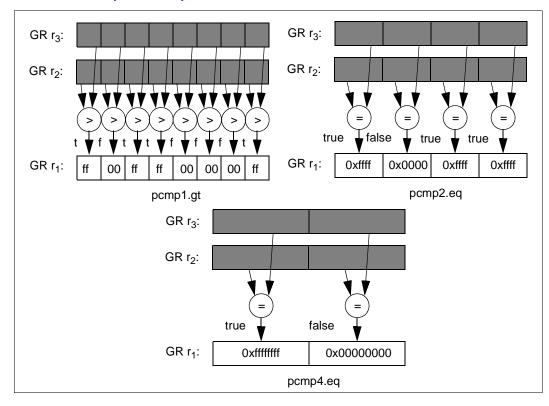

| 2-31 | Parallel Compare Example                           | 2-173 |

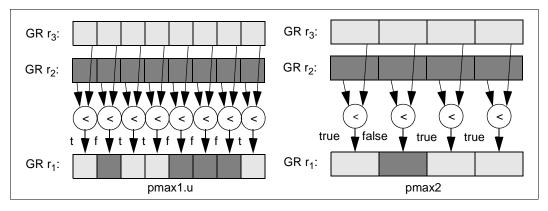

| 2-32 | Parallel Maximum Example                           | 2-175 |

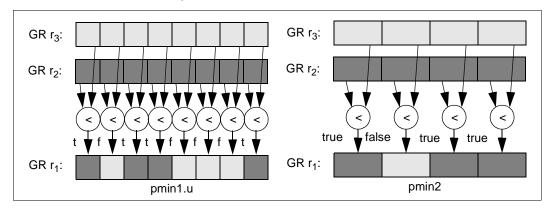

| 2-33 | Parallel Minimum Example                           | 2-176 |

| 2-34 | Parallel Multiply Operation                        |       |

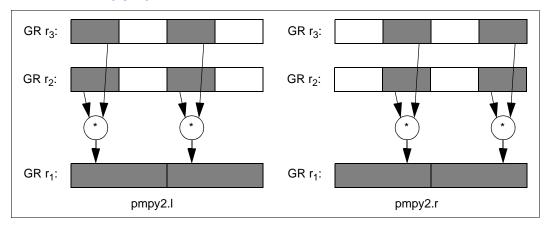

| 2-35 | Parallel Multiply and Shift Right Operation        |       |

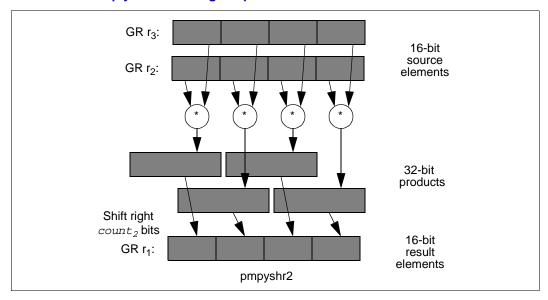

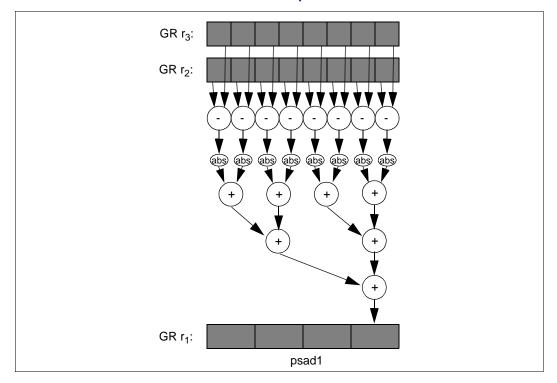

| 2-36 | Parallel Sum of Absolute Difference Example        |       |

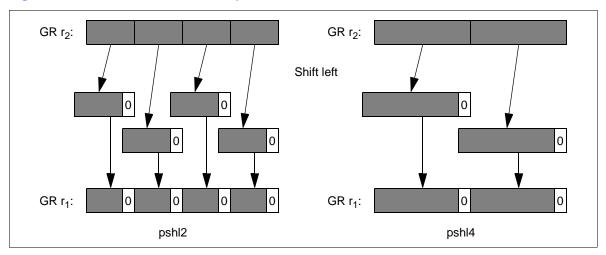

| 2-37 | Parallel Shift Left Example                        |       |

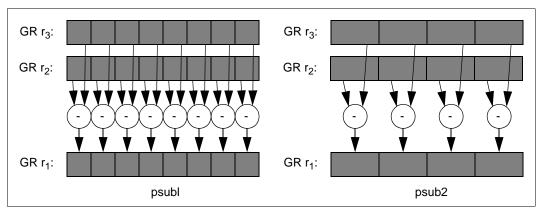

| 2-38 | Parallel Subtract Example                          |       |

| 2-39 | Function of setf.exp                               |       |

| 2-40 | Function of setf.sig                               |       |

| 2-41 | Shift Left and Add Pointer                         |       |

| 2-42 | Shift Right Pair                                   |       |

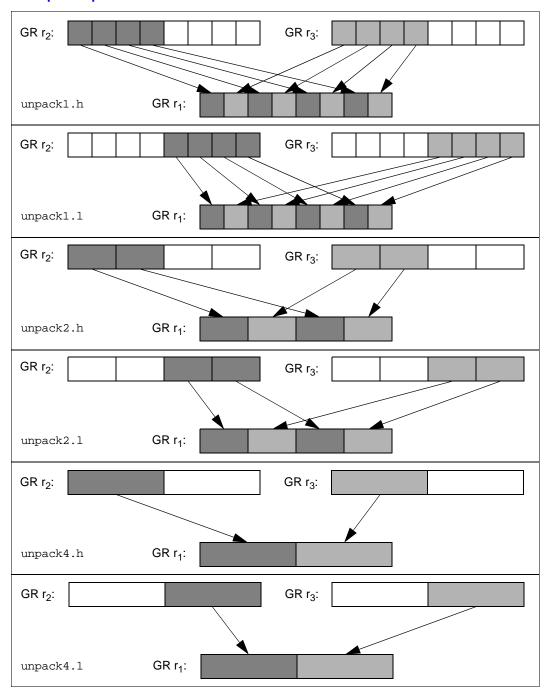

| 2-43 | Unpack Operation                                   |       |

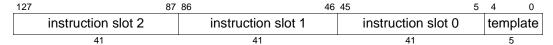

| 4-1  | Bundle Format                                      |       |

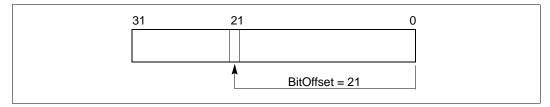

| 5-1  | Bit Offset for BIT[EAX,21]                         |       |

| 5 1  | Dit 01100t 101 Dit[L/W,21]                         | 5-0   |

#### int<sub>el®</sub>

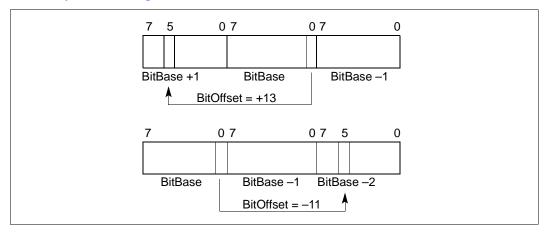

| 5-2  | Memory Bit Indexing                                                           | 5_9  |

|------|-------------------------------------------------------------------------------|------|

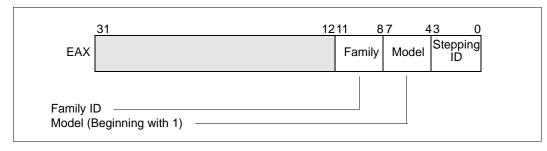

| 5-3  | Version Information in Registers EAX                                          |      |

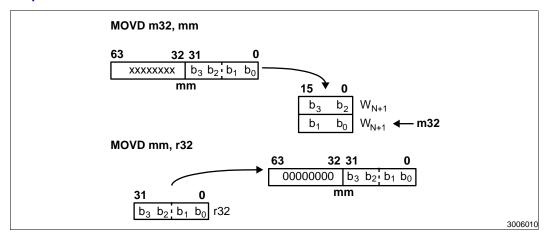

| 6-1  | Operation of the MOVD Instruction                                             |      |

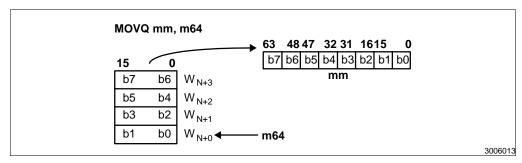

| 6-2  | Operation of the MOVQ Instruction                                             |      |

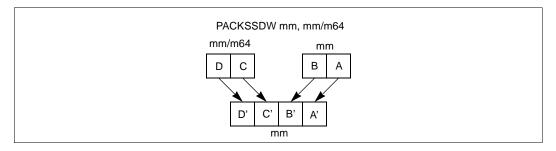

| 6-3  | Operation of the PACKSSDW Instruction                                         |      |

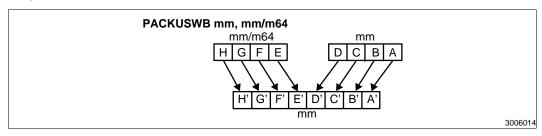

| 6-4  | Operation of the PACKUSWB Instruction                                         |      |

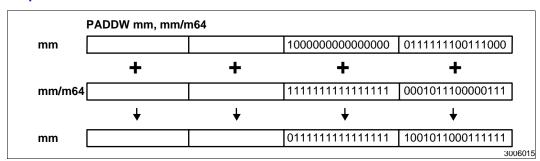

| 6-5  | Operation of the PADDW Instruction                                            |      |

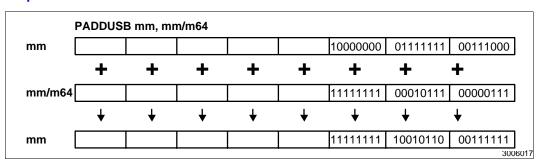

| 6-6  | Operation of the PADDSW Instruction                                           |      |

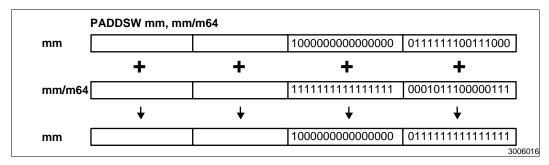

| 6-7  | Operation of the PADDUSB Instruction                                          |      |

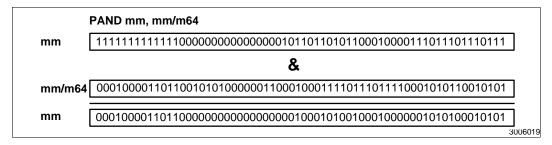

| 6-8  | Operation of the PAND Instruction                                             |      |

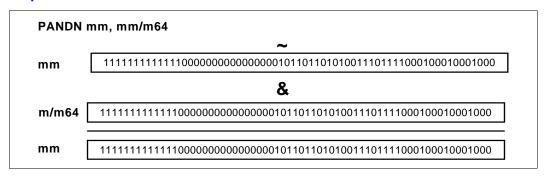

| 6-9  | Operation of the PANDN Instruction.                                           |      |

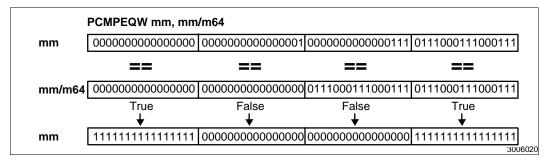

| 6-10 | Operation of the PCMPEQW Instruction                                          |      |

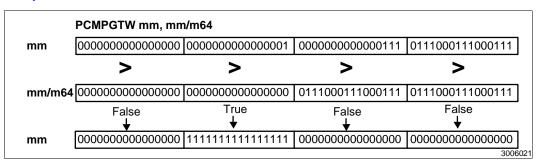

| 6-11 | Operation of the PCMPGTW Instruction                                          |      |

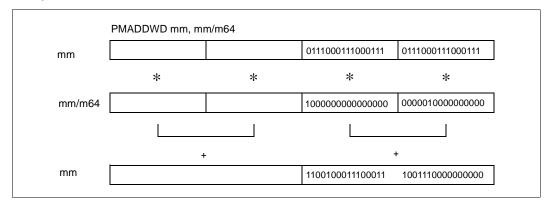

| 6-12 | Operation of the PMADDWD Instruction                                          |      |

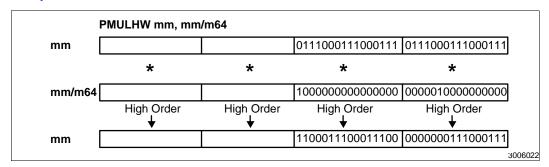

| 6-13 | Operation of the PMULHW Instruction                                           |      |

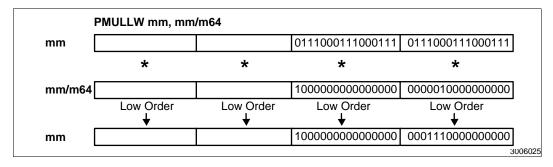

| 6-14 | Operation of the PMULLW Instruction                                           |      |

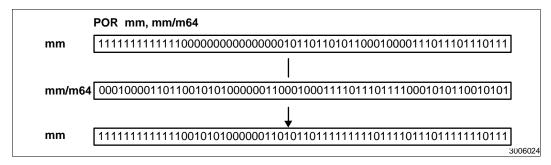

| 6-15 | Operation of the POR Instruction.                                             |      |

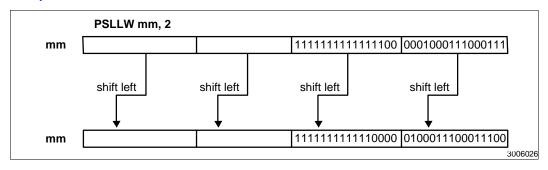

| 6-16 | Operation of the PSLLW Instruction                                            |      |

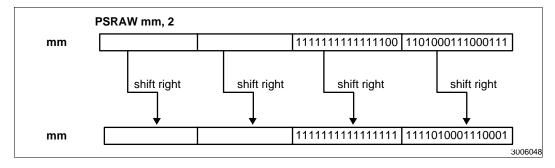

| 6-17 | Operation of the PSRAW Instruction                                            |      |

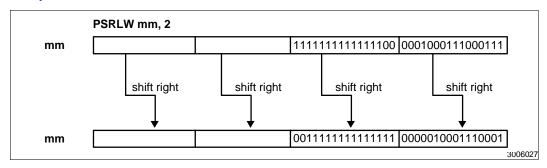

| 6-18 | Operation of the PSRLW Instruction                                            |      |

| 6-19 | Operation of the PSUBW Instruction                                            |      |

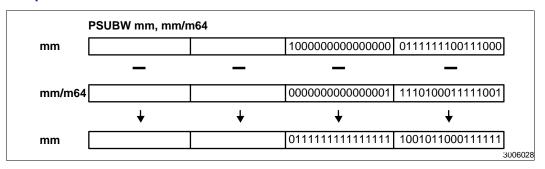

| 6-20 | Operation of the PSUBSW Instruction                                           |      |

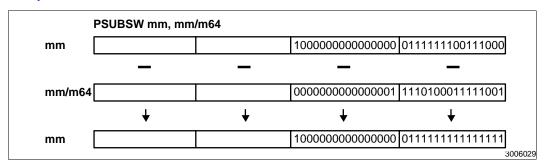

| 6-21 | Operation of the PSUBUSB Instruction                                          | 6-54 |

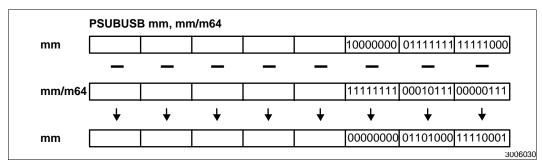

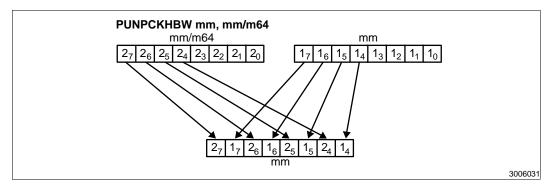

| 6-22 | High-order Unpacking and Interleaving of Bytes with the PUNPCKHBW Instruction | 6-57 |

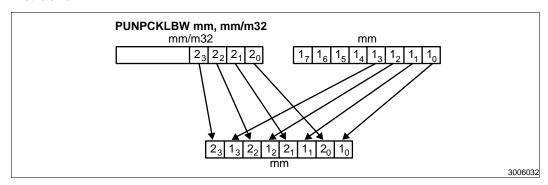

| 6-23 | Low-order Unpacking and Interleaving of Bytes with the PUNPCKLBW Instruction  | 6-60 |

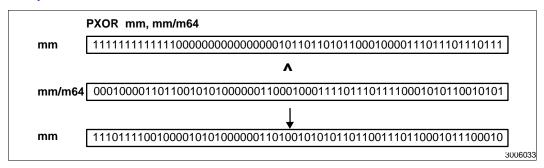

| 6-24 | Operation of the PXOR Instruction                                             | 6-63 |

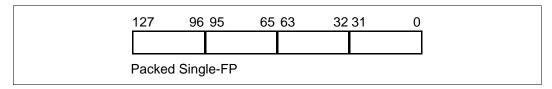

| 7-1  | Packed Single-FP Data Type                                                    | 7-2  |

| 7-2  | Streaming SIMD Extension Register Set                                         |      |

| 7-3  | Packed Operation                                                              |      |

| 7-4  | Scalar Operation                                                              |      |

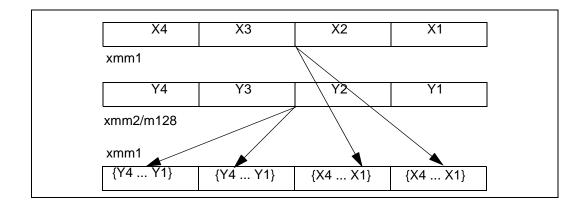

| 7-5  | Packed Shuffle Operation                                                      |      |

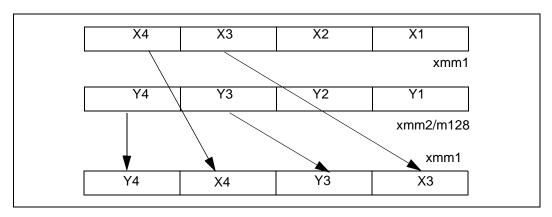

| 7-6  | Unpack High Operation                                                         |      |

| 7-7  | Unpack Low Operation                                                          |      |

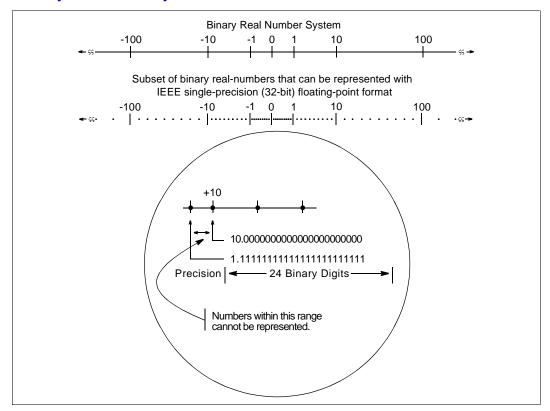

| 7-8  | Binary Real Number System                                                     |      |

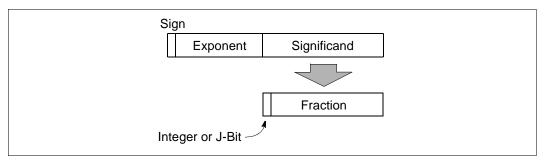

| 7-9  | Binary Floating-point Format                                                  |      |

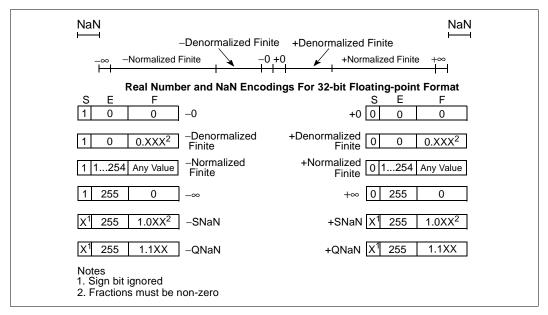

| 7-10 | Real Numbers and NaNs                                                         |      |

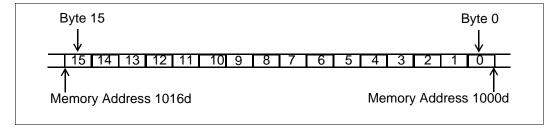

| 7-11 | Four Packed FP Data in Memory (at address 1000H)                              | 7-18 |

| Tabl | loe                                                                           |      |

| Iabi |                                                                               |      |

| 2-1  | Instruction Page Description                                                  | 2-1  |

| 2-2  | Instruction Page Font Conventions                                             |      |

| 2-3  | Register File Notation                                                        |      |

| 2-4  | C Syntax Differences                                                          |      |

| 2-5  | Branch Types                                                                  |      |

| 2-6  | Branch Whether Hint                                                           |      |

| 2-7  | Sequential Prefetch Hint                                                      |      |

| 2-8  | Branch Cache Deallocation Hint                                                |      |

| 2-9  | Long Branch Types                                                             |      |

| 2-10 | IP-relative Branch Predict Whether Hint                                       |      |

| 2-11 | Indirect Branch Predict Whether Hint                                          | 2-20 |

#### intها

| 2-12 | Importance Hint                                               | 2-20  |

|------|---------------------------------------------------------------|-------|

| 2-13 | ALAT Clear Completer                                          | 2-23  |

| 2-14 | Comparison Types                                              |       |

| 2-15 | 64-bit Comparison Relations for Normal and unc Compares       | 2-27  |

| 2-16 | 64-bit Comparison Relations for Parallel Compares             | 2-27  |

| 2-17 | Immediate Range for 32-bit Compares                           | 2-29  |

| 2-18 | Memory Compare and Exchange Size                              | 2-32  |

| 2-19 | Compare and Exchange Semaphore Types                          | 2-32  |

| 2-20 | Result Ranges for czx                                         | 2-35  |

| 2-21 | Specified pc Mnemonic Values                                  |       |

| 2-22 | sf Mnemonic Values                                            |       |

| 2-23 | Floating-point Class Relations                                |       |

| 2-24 | Floating-point Classes                                        | 2-49  |

| 2-25 | Floating-point Comparison Types                               | 2-52  |

| 2-26 | Floating-point Comparison Relations                           | 2-52  |

| 2-27 | Fetch and Add Semaphore Types                                 | 2-58  |

| 2-28 | Floating-point Parallel Comparison Results                    | 2-82  |

| 2-29 | Floating-point Parallel Comparison Relations                  | 2-82  |

| 2-30 | sz Completers                                                 | 2-126 |

| 2-31 | Load Types                                                    | 2-126 |

| 2-32 | Load Hints                                                    | 2-127 |

| 2-33 | fsz Completers                                                | 2-130 |

| 2-34 | FP Load Types                                                 | 2-130 |

| 2-35 | Iftype Mnemonic Values                                        | 2-137 |

| 2-36 | Ifhint Mnemonic Values                                        | 2-138 |

| 2-37 | Move to BR Whether Hints                                      | 2-145 |

| 2-38 | Indirect Register File Mnemonics                              | 2-150 |

| 2-39 | Mux Permutations for 8-bit Elements                           | 2-158 |

| 2-40 | Pack Saturation Limits                                        | 2-163 |

| 2-41 | Parallel Add Saturation Completers                            | 2-165 |

| 2-42 | Parallel Add Saturation Limits                                | 2-165 |

| 2-43 | Pcmp Relations                                                |       |

| 2-44 | PMPYSHR Shift Options                                         | 2-178 |

| 2-45 | Parallel Subtract Saturation Completers                       |       |

| 2-46 | Parallel Subtract Saturation Limits                           |       |

| 2-47 | Store Types                                                   |       |

| 2-48 | Store Hints                                                   |       |

| 2-49 | xsz Mnemonic Values                                           |       |

| 2-50 | Test Bit Relations for Normal and unc tbits                   |       |

| 2-51 | Test Bit Relations for Parallel tbits                         |       |

| 2-52 | Test NaT Relations for Normal and unc tnats                   |       |

| 2-53 | Test NaT Relations for Parallel tnats                         | 2-225 |

| 2-54 | Memory Exchange Size                                          | 2-231 |

| 3-1  | Pseudo-Code Functions                                         |       |

| 4-1  | Relationship between Instruction Type and Execution Unit Type |       |

| 4-2  | Template Field Encoding and Instruction Slot Mapping          |       |

| 4-3  | Major Opcode Assignments                                      |       |

| 4-4  | Instruction Format Summary                                    | 4-4   |

| 4-5  | Instruction Field Color Key                                   |       |

| 4-6  | Instruction Field Names                                       | 4-8   |

| 1-7  | Special Instruction Notations                                 | 1-0   |

#### intطِ®

| 4-8  | Integer ALU 2-bit+1-bit Opcode Extensions                          |      |

|------|--------------------------------------------------------------------|------|

| 4-9  | Integer ALU 4-bit+2-bit Opcode Extensions                          | 4-10 |

| 4-10 | Integer Compare Opcode Extensions                                  | 4-12 |

| 4-11 | Integer Compare Immediate Opcode Extensions                        | 4-13 |

| 4-12 | Multimedia ALU 2-bit+1-bit Opcode Extensions                       | 4-17 |

| 4-13 | Multimedia ALU Size 1 4-bit+2-bit Opcode Extensions                | 4-17 |

| 4-14 | Multimedia ALU Size 2 4-bit+2-bit Opcode Extensions                |      |

| 4-15 | Multimedia ALU Size 4 4-bit+2-bit Opcode Extensions                | 4-18 |

| 4-16 | Multimedia and Variable Shift 1-bit Opcode Extensions              | 4-20 |

| 4-17 | Multimedia Opcode 7 Size 1 2-bit Opcode Extensions                 | 4-21 |

| 4-18 | Multimedia Opcode 7 Size 2 2-bit Opcode Extensions                 |      |

| 4-19 | Multimedia Opcode 7 Size 4 2-bit Opcode Extensions                 |      |

| 4-20 | Variable Shift Opcode 7 2-bit Opcode Extensions                    |      |

| 4-21 | Integer Shift/Test Bit/Test NaT 2-bit Opcode Extensions            |      |

| 4-22 | Deposit Opcode Extensions                                          |      |

| 4-23 | Test Bit Opcode Extensions                                         |      |

| 4-24 | Misc I-Unit 3-bit Opcode Extensions                                |      |

| 4-25 | Misc I-Unit 6-bit Opcode Extensions                                |      |

| 4-26 | Move to BR Whether Hint Completer                                  |      |

| 4-27 | Integer Load/Store/Semaphore/Get FR 1-bit Opcode Extensions        |      |

| 4-28 | Floating-point Load/Store/Load Pair/Set FR 1-bit Opcode Extensions |      |

| 4-29 | Integer Load/Store Opcode Extensions                               |      |

| 4-30 | Integer Load +Reg Opcode Extensions                                |      |

| 4-31 | Integer Load/Store +Imm Opcode Extensions                          |      |

| 4-32 | Semaphore/Get FR Opcode Extensions                                 |      |

| 4-33 | Floating-point Load/Store/Lfetch Opcode Extensions                 |      |

| 4-34 | Floating-point Load/Lfetch +Reg Opcode Extensions                  |      |

| 4-35 | Floating-point Load/Store/Lfetch +Imm Opcode Extensions            |      |

| 4-36 | Floating-point Load Pair/Set FR Opcode Extensions                  |      |

| 4-37 | Floating-point Load Pair +Imm Opcode Extensions                    |      |

| 4-38 | Load Hint Completer                                                |      |

| 4-39 | Store Hint Completer                                               |      |

| 4-40 | Line Prefetch Hint Completer                                       |      |

| 4-41 | Opcode 0 System/Memory Management 3-bit Opcode Extensions          |      |

| 4-42 | Opcode 0 System/Memory Management 4-bit+2-bit Opcode Extensions    |      |

| 4-43 | Opcode 1 System/Memory Management 3-bit Opcode Extensions          |      |

| 4-44 | Opcode 1 System/Memory Management 6-bit Opcode Extensions          |      |

| 4-45 | IP-relative Branch Types                                           |      |

| 4-46 | Indirect/Miscellaneous Branch Opcode Extensions                    | 4-64 |

| 4-47 | Indirect Branch Types                                              |      |

| 4-48 | Indirect Return Branch Types                                       |      |

| 4-49 | Sequential Prefetch Hint Completer                                 |      |

| 4-50 | Branch Whether Hint Completer                                      |      |

| 4-51 | Indirect Call Whether Hint Completer                               |      |

| 4-52 | Branch Cache Deallocation Hint Completer                           |      |

| 4-53 | Indirect Predict/Nop Opcode Extensions                             |      |

| 4-54 | Branch Importance Hint Completer                                   |      |

| 4-55 | IP-relative Predict Whether Hint Completer                         |      |

| 4-56 | Indirect Predict Whether Hint Completer                            |      |

| 4-57 | Miscellaneous Floating-point 1-bit Opcode Extensions               |      |

| 4-58 | Opcode 0 Miscellaneous Floating-point 6-bit Opcode Extensions      |      |

## int<sub>el®</sub>

| 4-59 | Opcode 1 Miscellaneous Floating-point 6-bit Opcode Extensions         | 4-72  |

|------|-----------------------------------------------------------------------|-------|

| 4-60 | Reciprocal Approximation 1-bit Opcode Extensions                      | 4-72  |

| 4-61 | Floating-point Status Field Completer                                 | 4-72  |

| 4-62 | Floating-point Arithmetic 1-bit Opcode Extensions                     | 4-73  |

| 4-63 | Fixed-point Multiply Add and Select Opcode Extensions                 |       |

| 4-64 | Floating-point Compare Opcode Extensions                              |       |

| 4-65 | Floating-point Class 1-bit Opcode Extensions                          | 4-75  |

| 4-66 | Misc X-Unit 3-bit Opcode Extensions                                   | 4-81  |

| 4-67 | Misc X-Unit 6-bit Opcode Extensions                                   | 4-81  |

| 4-68 | Move Long 1-bit Opcode Extensions                                     | 4-82  |

| 4-69 | Long Branch Types                                                     | 4-83  |

| 4-70 | Immediate Formation                                                   | 4-84  |

| 5-1  | Register Encodings Associated with the +rb, +rw, and +rd Nomenclature | 5-3   |

| 5-2  | Exception Mnemonics, Names, and Vector Numbers                        | 5-9   |

| 5-3  | Floating-point Exception Mnemonics and Names                          | 5-10  |

| 5-4  | Information Returned by CPUID Instruction                             | 5-68  |

| 5-5  | Feature Flags Returned in EDX Register                                | 5-69  |

| 5-6  | FPATAN Zeros and NaNs                                                 | 5-138 |

| 5-7  | FPREM Zeros and NaNs                                                  | 5-140 |

| 5-8  | FPREM1 Zeros and NaNs                                                 | 5-143 |

| 5-9  | FSUB Zeros and NaNs                                                   | 5-172 |

| 5-10 | FSUBR Zeros and NaNs                                                  | 5-175 |

| 5-11 | FYL2X Zeros and NaNs                                                  |       |

| 5-12 | FYL2XP1 Zeros and NaNs                                                | 5-190 |

| 5-13 | IDIV Operands                                                         | 5-193 |

| 5-14 | INT Cases                                                             |       |

| 5-15 | LAR Descriptor Validity                                               |       |

| 5-16 | LEA Address and Operand Sizes                                         |       |

| 5-17 | Repeat Conditions                                                     |       |

| 7-1  | Real Number Notation                                                  |       |

| 7-2  | Denormalization Process                                               |       |

| 7-3  | Results of Operations with NAN Operands                               |       |

| 7-4  | Precision and Range of Streaming SIMD Extension Datatype              |       |

| 7-5  | Real Number and NaN Encodings                                         |       |

| 7-6  | Streaming SIMD Extension Instruction Behavior with Prefixes           |       |

| 7-7  | SIMD Integer Instructions – Behavior with Prefixes                    |       |

| 7-8  | Cacheability Control Instruction Behavior with Prefixes               |       |

| 7-9  | Key to Streaming SIMD Extension Naming Convention                     | 7-22  |

### int<sub>el®</sub>

# Part I: IA-64 Instruction Set Descriptions

The IA-64 architecture is a unique combination of innovative features such as explicit parallelism, predication, speculation and more. The architecture is designed to be highly scalable to fill the ever increasing performance requirements of various server and workstation market segments. The IA-64 architecture features a revolutionary 64-bit instruction set architecture (ISA) which applies a new processor architecture technology called EPIC, or Explicitly Parallel Instruction Computing. A key feature of the IA-64 architecture is IA-32 instruction set compatibility.

The *Intel IA-64 Architecture Software Developer's Manual* provides a comprehensive description of the programming environment, resources, and instruction set visible to both the application and system programmer. In addition, it also describes how programmers can take advantage of IA-64 features to help them optimize code. This manual replaces the *IA-64 Application Developer's Architecture Guide* (Order Number 245188) which contains a subset of the information presented in this four-volume set.

# 1.1 Overview of *Volume 1: IA-64 Application Architecture*

This volume defines the IA-64 application architecture, including application level resources, programming environment, and the IA-32 application interface. This volume also describes optimization techniques used to generate high performance software.

#### 1.1.1 Part 1: IA-64 Application Architecture Guide

Chapter 1, "About this Manual" provides an overview of all volumes in the *Intel IA-64 Architecture Software Developer's Manual*.

Chapter 2, "Introduction to the IA-64 Processor Architecture" provides an overview of the IA-64 architecture system environments.

Chapter 3, "IA-64 Execution Environment" describes the IA-64 register set used by applications and the memory organization models.

Chapter 4, "IA-64 Application Programming Model" gives an overview of the behavior of IA-64 application instructions (grouped into related functions).

Chapter 5, "IA-64 Floating-point Programming Model" describes the IA-64 floating-point architecture (including integer multiply).

Chapter 6, "IA-32 Application Execution Model in an IA-64 System Environment" describes the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an application programmer.

#### 1.1.2 Part 2: IA-64 Optimization Guide

Chapter 7, "About the IA-64 Optimization Guide" gives an overview of the IA-64 optimization guide.

Chapter 8, "Introduction to IA-64 Programming" provides an overview of the IA-64 application programming environment.

Chapter 9, "Memory Reference" discusses features and optimizations related to control and data speculation.

Chapter 10, "Predication, Control Flow, and Instruction Stream" describes optimization features related to predication, control flow, and branch hints.

Chapter 11, "Software Pipelining and Loop Support" provides a detailed discussion on optimizing loops through use of software pipelining.

Chapter 12, "Floating-point Applications" discusses current performance limitations in floating-point applications and IA-64 features that address these limitations.

#### 1.2 Overview of Volume 2: IA-64 System Architecture

This volume defines the IA-64 system architecture, including system level resources and programming state, interrupt model, and processor firmware interface. This volume also provides a useful system programmer's guide for writing high performance system software.

#### 1.2.1 Part 1: IA-64 System Architecture Guide

Chapter 1, "About this Manual" provides an overview of all volumes in the *Intel IA-64 Architecture Software Developer's Manual*.

Chapter 2, "IA-64 System Environment" introduces the environment designed to support execution of IA-64 operating systems running IA-32 or IA-64 applications.

Chapter 3, "IA-64 System State and Programming Model" describes the IA-64 architectural state which is visible only to an operating system.

Chapter 4, "IA-64 Addressing and Protection" defines the resources available to the operating system for virtual to physical address translation, virtual aliasing, physical addressing, and memory ordering.

Chapter 5, "IA-64 Interruptions" describes all interruptions that can be generated by an IA-64 processor.

Chapter 6, "IA-64 Register Stack Engine" describes the IA-64 architectural mechanism which automatically saves and restores the stacked subset (GR32 – GR 127) of the general register file.

Chapter 7, "IA-64 Debugging and Performance Monitoring" is an overview of the performance monitoring and debugging resources that are available in the IA-64 architecture.

Chapter 8, "IA-64 Interruption Vector Descriptions" lists all IA-64 interruption vectors.

Chapter 9, "IA-32 Interruption Vector Descriptions" lists IA-32 exceptions, interrupts and intercepts that can occur during IA-32 instruction set execution in the IA-64 System Environment.

Chapter 10, "IA-64 Operating System Interaction Model with IA-32 Applications" defines the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an IA-64 operating system.

Chapter 11, "IA-64 Processor Abstraction Layer" describes the firmware layer which abstracts IA-64 processor implementation-dependent features.

#### 1.2.2 Part 2: IA-64 System Programmer's Guide

Chapter 12, "About the IA-64 System Programmer's Guide" gives an introduction to the second section of the system architecture guide.

Chapter 13, "MP Coherence and Synchronization" describes IA-64 multi-processing synchronization primitives and the IA-64 memory ordering model.

Chapter 14, "Interruptions and Serialization" describes how the processor serializes execution around interruptions and what state is preserved and made available to low-level system code when interruptions are taken.

Chapter 15, "Context Management" describes how operating systems need to preserve IA-64 register contents and state. This chapter also describes IA-64 system architecture mechanisms that allow an operating system to reduce the number of registers that need to be spilled/filled on interruptions, system calls, and context switches.

Chapter 16, "Memory Management" introduces various IA-64 memory management strategies.

Chapter 17, "Runtime Support for Control and Data Speculation" describes the operating system support that is required for control and data speculation.

Chapter 18, "Instruction Emulation and Other Fault Handlers" describes a variety of instruction emulation handlers that IA-64 operating system are expected to support.

Chapter 19, "Floating-point System Software" discusses how IA-64 processors handle floating-point numeric exceptions and how the IA-64 software stack provides complete IEEE-754 compliance.

Chapter 20, "IA-32 Application Support" describes the support an IA-64 operating system needs to provide to host IA-32 applications.

Chapter 21, "External Interrupt Architecture" describes the IA-64 external interrupt architecture with a focus on how external asynchronous interrupt handling can be controlled by software.

Chapter 22, "I/O Architecture" describes the IA-64 I/O architecture with a focus on platform issues and support for the existing IA-32 I/O port space platform infrastructure.

Chapter 23, "Performance Monitoring Support" describes the IA-64 performance monitor architecture with a focus on what kind of operating system support is needed from IA-64 operating systems.

Chapter 24, "Firmware Overview" introduces the IA-64 firmware model, and how various firmware layers (PAL, SAL, EFI) work together to enable processor and system initialization, and operating system boot.

#### 1.2.3 Appendices

Appendix, "IA-64 Resource and Dependency Semantics" summarizes the dependency rules that are applicable when generating code for IA-64 processors.

Appendix, "Code Examples" provides OS boot flow sample code.

#### 1.3 Overview of Volume 3: Instruction Set Reference

This volume is a comprehensive reference to the IA-64 and IA-32 instruction sets, including instruction format/encoding.

#### 1.3.1 Part 1: IA-64 Instruction Set Descriptions

Chapter 1, "About this Manual" provides an overview of all volumes in the *Intel IA-64 Architecture Software Developer's Manual*.

Chapter 2, "IA-64 Instruction Reference" provides a detailed description of all IA-64 instructions, organized in alphabetical order by assembly language mnemonic.

Chapter 3, "IA-64 Pseudo-Code Functions" provides a table of pseudo-code functions which are used to define the behavior of the IA-64 instructions.

Chapter 4, "IA-64 Instruction Formats" describes the encoding and instruction format instructions.

#### 1.3.2 Part 2: IA-32 Instruction Set Descriptions

Chapter 5, "Base IA-32 Instruction Reference" provides a detailed description of all base IA-32 instructions, organized in alphabetical order by assembly language mnemonic.

Chapter 6, "IA-32 MMX<sup>TM</sup> Technology Instruction Reference" provides a detailed description of all IA-32 MMX<sup>TM</sup> technology instructions designed to increase performance of multimedia intensive applications. Organized in alphabetical order by assembly language mnemonic.

Chapter 7, "IA-32 Streaming SIMD Extension Instruction Reference" provides a detailed description of all IA-32 Streaming SIMD Extension instructions designed to increase performance of multimedia intensive applications, and is organized in alphabetical order by assembly language mnemonic.

# 1.4 Overview of Volume 4: *Itanium™ Processor Programmer's Guide*

This volume describes model-specific architectural features incorporated into the Intel® Itanium<sup>TM</sup> processor, the first IA-64 processor.

Chapter 1, "About this Manual" provides an overview of four volumes in the *Intel IA-64* Architecture Software Developer's Manual.

Chapter 2, "Register Stack Engine Support" summarizes Register Stack Engine (RSE) support provided by the Itanium processor.

Chapter 3, "Virtual Memory Management Support" details size of physical and virtual address, region register ID, and protection key register implemented on the Itanium processor.

Chapter 4, "Processor Specific Write Coalescing (WC) Behavior" describes the behavior of write coalesce (also known as Write Combine) on the Itanium processor.

Chapter 5, "Model Specific Instruction Implementation" describes model specific behavior of IA-64 instructions on the Itanium processor.

Chapter 6, "Processor Performance Monitoring" defines the performance monitoring features which are specific to the Itanium processor. This chapter outlines the targeted performance monitor usage models and describes the Itanium processor specific performance monitoring state.

Chapter 7, "Performance Monitor Events" summarizes the Itanium processor events and describes how to compute commonly used performance metrics for Itanium processor events.

Chapter 8, "Model Specific Behavior for IA-32 Instruction Execution" describes some of the key differences between an Itanium processor executing IA-32 instructions and the Pentium III processor.

#### 1.5 Terminology

The following definitions are for terms related to the IA-64 architecture and will be used throughout this document:

**Instruction Set Architecture (ISA)** – Defines application and system level resources. These resources include instructions and registers.

**IA-64 Architecture** – The new ISA with 64-bit instruction capabilities, new performance-enhancing features, and support for the IA-32 instruction set.

**IA-32 Architecture** – The 32-bit and 16-bit Intel Architecture as described in the *Intel Architecture Software Developer's Manual*.

**IA-64 Processor** – An Intel 64-bit processor that implements both the IA-64 and the IA-32 instruction sets.

**IA-64 System Environment** – The IA-64 operating system privileged environment that supports the execution of both IA-64 and IA-32 code.

**IA-32 System Environment** – The operating system privileged environment and resources as defined by the *Intel Architecture Software Developer's Manual*. Resources include virtual paging, control registers, debugging, performance monitoring, machine checks, and the set of privileged instructions.

IA-64 Firmware – The Processor Abstraction Layer (PAL) and System Abstraction Layer (SAL).

**Processor Abstraction Layer (PAL)** – The IA-64 firmware layer which abstracts IA-64 processor features that are implementation dependent.

**System Abstraction Layer (SAL)** – The IA-64 firmware layer which abstracts IA-64 system features that are implementation dependent.

#### 1.6 Related Documents

The following documents contain additional material related to the *Intel*® *IA-64 Architecture Software Developer's Manual*:

- *Intel Architecture Software Developer's Manual* This set of manuals describes the Intel 32-bit architecture. They are readily available from the Intel Literature Department by calling 1-800-548-4725 and requesting Order Numbers 243190, 243191and 243192, or can be downloaded at http://developer.intel.com/design/litcentr.

- *IA-64 Software Conventions and Runtime Architecture Guide* This document defines general information necessary to compile, link, and execute a program on an IA-64 operating system. It can be downloaded at http://developer.intel.com/design/ia64.

- *IA-64 System Abstraction Layer Specification* This document specifies requirements to develop platform firmware for IA-64 processor systems.

- *Extensible Firmware Interface Specification* This document defines a new model for the interface between operating systems and platform firmware. It can be downloaded at http://developer.intel.com/technology/efi.

This chapter describes the function of each IA-64 instruction. The pages of this chapter are sorted alphabetically by assembly language mnemonic.

#### 2.1 Instruction Page Conventions

The instruction pages are divided into multiple sections as listed in Table 2-1. The first three sections are present on all instruction pages. The last three sections are present only when necessary. Table 2-2 lists the font conventions which are used by the instruction pages.

**Table 2-1. Instruction Page Description**

| Section Name  | Contents                                                                |

|---------------|-------------------------------------------------------------------------|

| Format        | Assembly language syntax, instruction type and encoding format          |

| Description   | Instruction function in English                                         |

| Operation     | Instruction function in C code                                          |

| FP Exceptions | IEEE floating-point traps                                               |

| Interruptions | Prioritized list of interruptions that may be caused by the instruction |

| Serialization | Serializing behavior or serialization requirements                      |

**Table 2-2. Instruction Page Font Conventions**

| Font        | Interpretation                                                                                                                          |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| regular     | (Format section) Required characters in an assembly language mnemonic                                                                   |  |

| italic      | (Format section) Assembly language field name that must be filled with one of a range of legal values listed in the Description section |  |

| code        | (Operation section) C code specifying instruction behavior                                                                              |  |

| code_italic | (Operation section) Assembly language field name corresponding to a <i>italic</i> field listed in the Format section                    |  |

In the Format section, register addresses are specified using the assembly mnemonic field names given in the third column of Table 2-3. For instructions that are predicated, the Description section assumes that the qualifying predicate is true (except for instructions that modify architectural state when their qualifying predicate is false). The test of the qualifying predicate is included in the Operation section (when applicable).

In the Operation section, registers are addressed using the notation reg[addr].field. The register file being accessed is specified by reg, and has a value chosen from the second column of Table 2-3. The addr field specifies a register address as an assembly language field name or a register mnemonic. For the general, floating-point, and predicate register files which undergo register renaming, addr is the register address prior to renaming and the renaming is not shown. The field option specifies a named bit field within the register. If field is absent, then all fields

of the register are accessed. The only exception is when referencing the data field of the general registers (64-bits not including the NaT bit) where the notation <code>GR[addr]</code> is used. The syntactical differences between the code found in the Operation section and ANSI C is listed in Table 2-4.

**Table 2-3. Register File Notation**

| Register File                               | C Notation | Assembly<br>Mnemonic | Indirect<br>Access |

|---------------------------------------------|------------|----------------------|--------------------|

| Application registers                       | AR         | ar                   |                    |

| Branch registers                            | BR         | b                    |                    |

| Control registers                           | CR         | cr                   |                    |

| CPU identification registers                | CPUID      | cpuid                | Y                  |

| Data breakpoint registers                   | DBR        | dbr                  | Y                  |

| Instruction breakpoint registers            | IBR        | ibr                  | Y                  |

| Data TLB translation cache                  | DTC        | n/a                  |                    |

| Data TLB translation registers              | DTR        | dtr                  | Y                  |

| Floating-point registers                    | FR         | f                    |                    |

| General registers                           | GR         | r                    |                    |

| Instruction TLB translation cache           | ITC        | n/a                  |                    |

| Instruction TLB translation registers       | ITR        | itr                  | Y                  |

| Protection key registers                    | PKR        | pkr                  | Y                  |

| Performance monitor configuration registers | PMC        | pmc                  | Υ                  |

| Performance monitor data registers          | PMD        | pmd                  | Υ                  |

| Predicate registers                         | PR         | р                    |                    |

| Region registers                            | RR         | rr                   | Υ                  |

**Table 2-4. C Syntax Differences**

| Syntax           | Function                                                                                                                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| {msb:lsb}, {bit} | Bit field specifier. When appended to a variable, denotes a bit field extending from the most significant bit specified by "msb" to the least significant bit specified by "lsb" including bits "msb" and "lsb". If "msb" and "lsb" are equal then a single bit is accessed. The second form denotes a single bit. |

| u>, u>=, u<, u<= | Unsigned inequality relations. Variables on either side of the operator are treated as unsigned.                                                                                                                                                                                                                   |

| u>>, u>>=        | Unsigned right shift. Zeroes are shifted into the most significant bit position.                                                                                                                                                                                                                                   |

| u+               | Unsigned addition. Operands are treated as unsigned, and zero-extended.                                                                                                                                                                                                                                            |

| u*               | Unsigned multiplication. Operands are treated as unsigned.                                                                                                                                                                                                                                                         |

#### 2.2 Instruction Descriptions

The remainder of this chapter provides a description of each of the IA-64 instructions.

#### Add

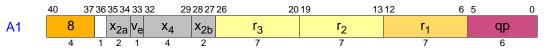

Format: (qp) add  $r_1 = r_2$ ,  $r_3$  register\_form A1 (qp) add  $r_1 = r_2$ ,  $r_3$ , 1 plus1\_form, register\_form A1 (qp) add  $r_1 = imm$ ,  $r_3$  pseudo-op (qp) adds  $r_1 = imm_{14}$ ,  $r_3$  imm14\_form A4 (qp) addl  $r_1 = imm_{22}$ ,  $r_3$  imm22\_form A5

#### **Description:**

The two source operands (and an optional constant 1) are added and the result placed in GR  $r_1$ . In the register form the first operand is GR  $r_2$ ; in the imm\_14 form the first operand is taken from the sign-extended  $imm_{14}$  encoding field; in the imm22\_form the first operand is taken from the sign-extended  $imm_{22}$  encoding field. In the imm22\_form, GR  $r_3$  can specify only GRs 0, 1, 2 and 3.

The plus1\_form is available only in the register\_form (although the equivalent effect in the immediate forms can be achieved by adjusting the immediate).

The immediate-form pseudo-op chooses the imm14\_form or imm22\_form based upon the size of the immediate operand and the value of  $r_3$ .

#### Operation:

```

if (PR[qp]) {

check_target_register(r_1);

if (register_form)

// register form

tmp\_src = GR[r_2];

// 14-bit immediate form

else if (imm14_form)

tmp\_src = sign\_ext(imm_{14}, 14);

// 22-bit immediate form

else

{\tt tmp\_src = sign\_ext(\it imm_{22}, \ 22);}

tmp_nat = (register_form ? GR[r_2].nat : 0);

if (plus1_form)

GR[r_1] = tmp\_src + GR[r_3] + 1;

else

GR[r_1] = tmp\_src + GR[r_3];

GR[r_1].nat = tmp_nat \mid \mid GR[r_3].nat;

```

Interruptions: Illegal Operation fault

#### **Add Pointer**

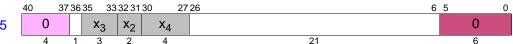

Format: (qp) addp4  $r_1 = r_2$ ,  $r_3$  register\_form A1 (qp) addp4  $r_1 = imm_{14}$ ,  $r_3$  imm14\_form A4

**Description:**

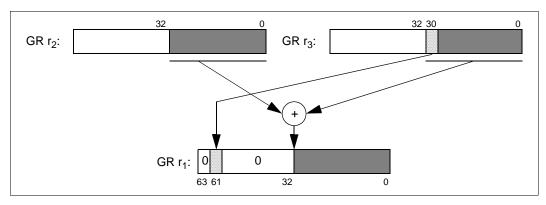

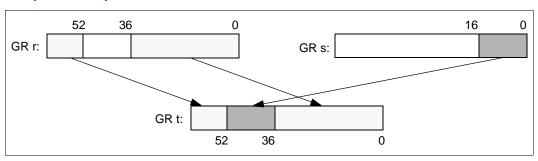

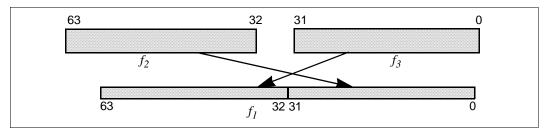

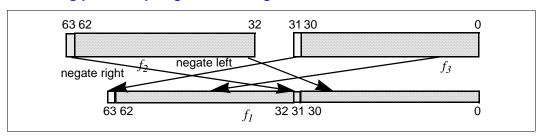

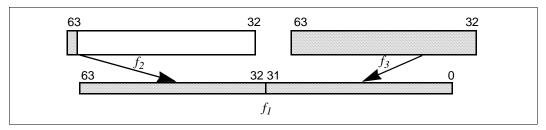

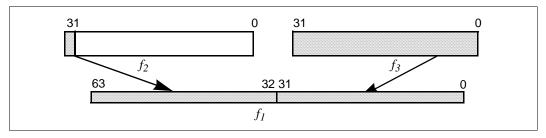

The two source operands are added. The upper 32 bits of the result are forced to zero, and then bits  $\{31:30\}$  of GR  $r_3$  are copied to bits  $\{62:61\}$  of the result. This result is placed in GR  $r_1$ . In the register\_form the first operand is GR  $r_2$ ; in the imm14\_form the first operand is taken from the sign-extended  $imm_{14}$  encoding field.

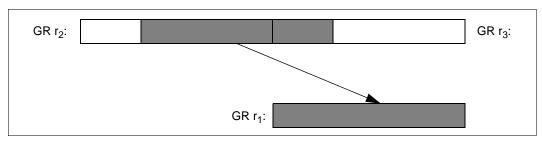

Figure 2-1. Add Pointer

Interruptions: Illegal Operation fault

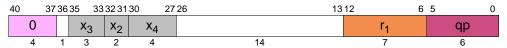

#### **Allocate Stack Frame**

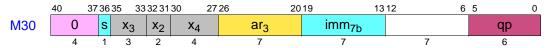

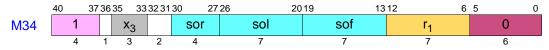

Format: alloc  $r_1$  = ar.pfs, i, l, o, r M34

**Description:** A new stack frame is allocated on the general register stack, and the Previous Function State

register (PFS) is copied to GR  $r_1$ . The change of frame size is immediate. The write of GR  $r_1$  and subsequent instructions in the same instruction group use the new frame. This instruction cannot be

predicated.

The four parameters, i (size of inputs), l (size of locals), o (size of outputs), and r (size of rotating) specify the sizes of the regions of the stack frame.

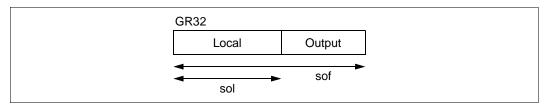

Figure 2-2. Stack Frame

The size of the frame (sof) is determined by i + l + o. Note that this instruction may grow or shrink the size of the current register stack frame. The size of the local region (sol) is given by i + l. There is no real distinction between inputs and locals. They are given as separate operands in the instruction only as a hint to the assembler about how the local registers are to be used.

The rotating registers must fit within the stack frame and be a multiple of 8 in number. If this instruction attempts to change the size of CFM.sor, and the register rename base registers (CFM.rrb.gr, CFM.rrb.fr, CFM.rrb.pr) are not all zero, then the instruction will cause a Reserved Register/Field fault.

Although the assembler does not allow illegal combinations of operands for alloc, illegal combinations can be encoded in the instruction. Attempting to allocate a stack frame larger than 96 registers, or with the rotating region larger than the stack frame, or with the size of locals larger than the stack frame, will cause an Illegal Operation fault. An alloc instruction must be the first instruction in an instruction group. Otherwise, the results are undefined.

If insufficient registers are available to allocate the desired frame alloc will stall the processor until enough dirty registers are written to the backing store. Such mandatory RSE stores may cause the data related faults listed below.

```

// tmp_sof, tmp_sol, tmp_sor are the fields encoded in the instruction

Operation:

tmp\_sof = i + l + o;

tmp\_sol = i + 1;

tmp\_sor = r u >> 3;

\verb|check_target_register_sof(r_1, tmp_sof)|;

if (tmp\_sof u> 96 \mid \mid r u> tmp\_sof \mid \mid tmp\_sol u> tmp\_sof)

illegal_operation_fault();

if (tmp_sor != CFM.sor &&

(CFM.rrb.gr != 0 || CFM.rrb.fr != 0 || CFM.rrb.pr != 0))

reserved_register_field_fault();

alat_frame_update(0, tmp_sof - CFM.sof);

rse_new_frame(CFM.sof, tmp_sof);// Make room for new registers; Mandatory

// RSE stores can raise faults listed below.

CFM.sof = tmp_sof;

CFM.sol = tmp_sol;

CFM.sor = tmp_sor;

```

#### **Interruptions:** Illegal Operation fault

Reserved Register/Field fault Unimplemented Data Address fault VHPT Data fault Data Nested TLB fault Data TLB fault

Alternate Data TLB fault Data Page Not Present fault

$GR[r_1] = AR[PFS];$  $GR[r_1].nat = 0;$

Data NaT Page Consumption fault

Data Key Miss fault

Data Key Permission fault

Data Access Rights fault

Data Dirty Bit fault

Data Access Bit fault

Data Debug fault

#### **Logical And**

Format: (qp) and  $r_1 = r_2, r_3$  register\_form A1 (qp) and  $r_1 = imm_8, r_3$  register\_form A3

**Description:** The two source operands are logically ANDed and the result placed in GR  $r_1$ . In the register\_form

the first operand is GR  $r_2$ ; in the imm8\_form the first operand is taken from the  $imm_8$  encoding

field.

Interruptions: Illegal Operation fault

#### **And Complement**

Format: (qp) and  $r_1 = r_2, r_3$  register\_form A1 (qp) and  $r_1 = imm_8, r_3$  imm8\_form A3

**Description:** The first source operand is logically ANDed with the 1's complement of the second source operand

and the result placed in GR  $r_1$ . In the register\_form the first operand is GR  $r_2$ ; in the imm8\_form

the first operand is taken from the  $imm_8$  encoding field.

```

\begin{array}{lll} \textbf{Operation:} & & \text{if } (\operatorname{PR}[qp]) \; \{ & & \\ & & & \text{check\_target\_register}(r_1); \\ \\ & & & & \text{tmp\_src} = (\operatorname{register\_form} \; ? \; \operatorname{GR}[r_2] \; : \; \operatorname{sign\_ext}(\mathit{imm}_g, \; 8)); \\ \\ & & & & \text{tmp\_nat} = (\operatorname{register\_form} \; ? \; \operatorname{GR}[r_2] \cdot \operatorname{nat} \; : \; 0); \\ \\ & & & & & \text{GR}[r_1] = \operatorname{tmp\_src} \; \& \; \sim \operatorname{GR}[r_3]; \\ \\ & & & & & \text{GR}[r_1] \cdot \operatorname{nat} = \operatorname{tmp\_nat} \; | \; | \; \operatorname{GR}[r_3] \cdot \operatorname{nat}; \\ \\ & & & & & \\ \\ \end{array}

```

Interruptions: Illegal Operation fault

#### **Branch**

| Fo | r | m | a | t |

|----|---|---|---|---|

| гυ | ш | ш | а | L |

| (qp) br.btype    | e.bwh.ph.dh target <sub>25</sub>  | ip_relative_form               | B                |

|------------------|-----------------------------------|--------------------------------|------------------|

| (qp) br.btype    | $e.bwh.ph.dh$ $b_1 = target_{25}$ | call_form, ip_relative_form    | <b>B</b> 3       |

| br. <i>btype</i> | .bwh.ph.dh target <sub>25</sub>   | counted_form, ip_relative_form | $\mathbf{B}^{2}$ |

| br. <i>ph.dh</i> | target <sub>25</sub>              | pseudo-op                      |                  |

| (qp) br.btype    | e.bwh.ph.dh b <sub>2</sub>        | indirect_form                  | $\mathbf{B}^2$   |

| (qp) br.btype    | $e.bwh.ph.dh$ $b_1 = b_2$         | call_form, indirect_form       | B5               |

| br. <i>ph.dh</i> | $b_2$                             | pseudo-op                      |                  |

#### **Description:**

A branch condition is evaluated, and either a branch is taken, or execution continues with the next sequential instruction. The execution of a branch logically follows the execution of all previous non-branch instructions in the same instruction group. On a taken branch, execution begins at slot 0.

Branches can be either IP-relative, or indirect. For IP-relative branches, the  $target_{25}$  operand, in assembly, specifies a label to branch to. This is encoded in the branch instruction as a signed immediate displacement  $(imm_{21})$  between the target bundle and the bundle containing this instruction  $(imm_{21} = target_{25} - IP >> 4)$ . For indirect branches, the target address is taken from BR  $b_2$ .

**Table 2-5. Branch Types**

| btype        | Function                     | Branch Condition                      | Target Address     |

|--------------|------------------------------|---------------------------------------|--------------------|

| cond or none | Conditional branch           | Qualifying predicate                  | IP-rel or Indirect |

| call         | Conditional procedure call   | Qualifying predicate                  | IP-rel or Indirect |

| ret          | Conditional procedure return | Qualifying predicate                  | Indirect           |

| ia           | Invoke IA-32 instruction set | Unconditional                         | Indirect           |

| cloop        | Counted loop branch          | Loop count                            | IP-rel             |

| ctop, cexit  | Mod-scheduled counted loop   | Loop count and epilog count           | IP-rel             |

| wtop, wexit  | Mod-scheduled while loop     | Qualifying predicate and epilog count | IP-rel             |

There are two pseudo-ops for unconditional branches. These are encoded like a conditional branch (btype = cond), with the qp field specifying PR 0, and with the bwh hint of sptk.

The branch type determines how the branch condition is calculated and whether the branch has other effects (such as writing a link register). For the basic branch types, the branch condition is simply the value of the specified predicate register. These basic branch types are:

- cond: If the qualifying predicate is 1, the branch is taken. Otherwise it is not taken.

- call: If the qualifying predicate is 1, the branch is taken and several other actions occur:

- The current values of the Current Frame Marker (CFM), the EC application register and the current privilege level are saved in the Previous Function State application register.

- The caller's stack frame is effectively saved and the callee is provided with a frame containing only the caller's output region.

- The rotation rename base registers in the CFM are reset to 0.

- A return link value is placed in BR  $b_1$ .

- return: If the qualifying predicate is 1, the branch is taken and the following occurs:

- CFM, EC, and the current privilege level are restored from PFS. (The privilege level is restored only if this does not increase privilege.)

- The caller's stack frame is restored.

- If the return lowers the privilege, and PSR.lp is 1, then a Lower-Privilege Transfer trap is taken

- ia: The branch is taken unconditionally, if it is not intercepted by the OS. The effect of the branch is to invoke the IA-32 instruction set (by setting PSR.is to 1) and begin processing IA-32 instructions at the virtual linear target address contained in BR  $b_2$ {31:0}. If the qualifying predicate is not PR 0, an Illegal Operation fault is raised. If instruction set transitions are disabled (PSR.di is 1), then a Disabled Instruction Set Transition fault is raised.

The IA-32 target effective address is calculated relative to the current code segment, i.e. EIP $\{31:0\} = BR \ b_2\{31:0\} - CSD$ .base. The IA-32 instruction set can be entered at any privilege level, provided PSR.di is 0. If PSR.dfh is 1, a Disabled FP Register fault is raised on the target IA-32 instruction. No register bank switch nor change in privilege level occurs during the instruction set transition.

Software must ensure the code segment descriptor (CSD) and selector (CS) are loaded before issuing the branch. If the target EIP value exceeds the code segment limit or has a code segment privilege violation, an IA-32\_Exception(GPFault) is raised on the target IA-32 instruction. For entry into 16-bit IA-32 code, if BR  $b_2$  is not within 64K-bytes of CSD.base a GPFault is raised on the target instruction. EFLAG.rf is unmodified until the successful completion of the first IA-32 instruction. PSR.da, PSR.id, PSR.ia, PSR.dd, and PSR.ed are cleared to zero after br.ia completes execution and before the first IA-32 instruction begins execution. EFLAG.rf is not cleared until the target IA-32 instruction successfully completes.

Software must issue a mf instruction before the branch if memory ordering is required between IA-32 processor consistent and IA-64 unordered memory references. The processor does not ensure IA-64-instruction-set-generated writes into the instruction stream are seen by subsequent IA-32 instruction fetches. br.ia does not perform an instruction serialization operation. The processor does ensure that prior writes (even in the same instruction group) to GRs and FRs are observed by the first IA-32 instruction. Writes to ARs within the same instruction group as br.ia are not allowed, since br.ia may implicitly reads all ARs. If an illegal RAW dependency is present between an AR write and br.ia, the first IA-32 instruction fetch and execution may or may not see the updated AR value.

IA-32 instruction set execution leaves the contents of the ALAT undefined. Software can not rely on ALAT values being preserved across an instruction set transition. All registers left in the current register stack frame are undefined across an instruction set transition. On entry to IA-32 code, existing entries in the ALAT are ignored. If the register stack contains any dirty registers, an Illegal Operation fault is raised on the br.ia instruction. The current register stack frame is forced to zero. To flush the register file of dirty registers, the flushrs instruction must be issued in an instruction group preceding the br.ia instruction. To enhance the performance of the instruction set transition, software can start the IA-64 register stack flush in parallel with starting the IA-32 instruction set by 1) ensuring flushrs is exactly one instruction group before the br.ia, and 2) br.ia is in the first B-slot. br.ia should always be executed in the first B-slot with a hint of "static-taken" (default), otherwise processor performance will be degraded.

If a br.ia causes any IA-64 traps (e.g. Single Step trap, Taken Branch trap, or Unimplemented Instruction Address trap), IIP will contain the original 64-bit target IP. (The value will not have been zero extended from 32 bits.)

Another branch type is provided for simple counted loops. This branch type uses the Loop Count application register (LC) to determine the branch condition, and does not use a qualifying predicate:

• **cloop:** If the LC register is not equal to zero, it is decremented and the branch is taken.

In addition to these simple branch types, there are four types which are used for accelerating modulo-scheduled loops (and refer to Volume 1). Two of these are for counted loops (which use the LC register), and two for while loops (which use the qualifying predicate). These loop types use register rotation to provide register renaming, and they use predication to turn off instructions that correspond to empty pipeline stages.

The Epilog Count application register (EC) is used to count epilog stages and, for some while loops, a portion of the prolog stages. In the epilog phase, EC is decremented each time around and, for most loops, when EC is one, the pipeline has been drained, and the loop is exited. For certain types of optimized, unrolled software-pipelined loops, the target of a br.cexit or br.wexit is set to the next sequential bundle. In this case, the pipeline may not be fully drained when EC is one, and continues to drain while EC is zero.

For these modulo-scheduled loop types, the calculation of whether the branch is taken or not depends on the kernel branch condition (LC for counted types, and the qualifying predicate for while types) and on the epilog condition (whether EC is greater than one or not).

These branch types are of two categories: top and exit. The top types (ctop and wtop) are used when the loop decision is located at the bottom of the loop body and therefore a taken branch will continue the loop while a fall through branch will exit the loop. The exit types (cexit and wexit) are used when the loop decision is located somewhere other than the bottom of the loop and therefore a fall though branch will continue the loop and a taken branch will exit the loop. The exit types are also used at intermediate points in an unrolled pipelined loop. (For more details, refer to Volume 1).

The modulo-scheduled loop types are:

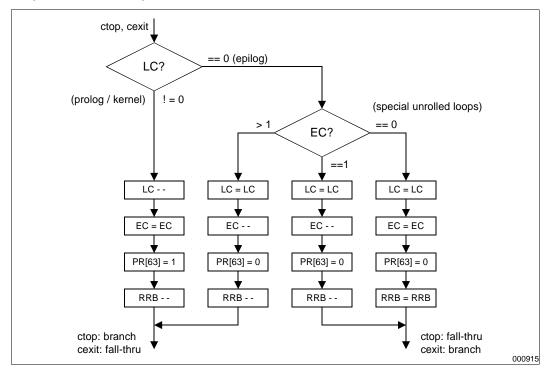

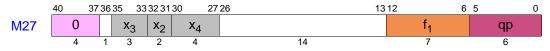

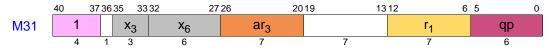

• ctop and cexit: These branch types behave identically, except in the determination of whether to branch or not. For br.ctop, the branch is taken if either LC is non-zero or EC is greater than one. For br.cexit, the opposite is true. It is not taken if either LC is non-zero or EC is greater than one and is taken otherwise.

These branch types also use LC and EC to control register rotation and predicate initialization. During the prolog and kernel phase, when LC is non-zero, LC counts down. When br.ctop or br.cexit is executed with LC equal to zero, the epilog phase is entered, and EC counts down. When br.ctop or br.cexit is executed with LC equal to zero and EC equal to one, a final decrement of EC and a final register rotation are done. If LC and EC are equal to zero, register rotation stops. These other effects are the same for the two branch types, and are described in Figure 2-3.

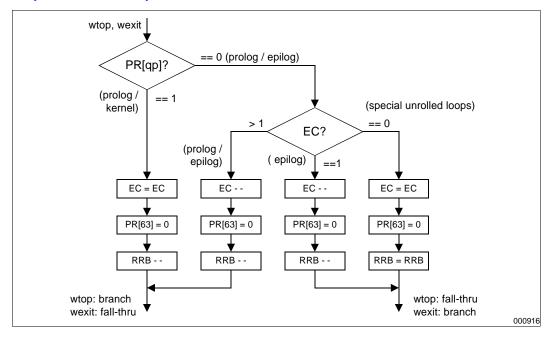

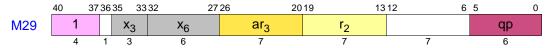

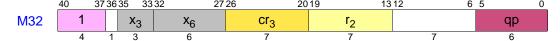

wtop and wexit: These branch types behave identically, except in the determination of whether to branch or not. For br.wtop, the branch is taken if either the qualifying predicate is one or EC is greater than one. For br.wexit, the opposite is true. It is not taken if either the qualifying predicate is one or EC is greater than one, and is taken otherwise.

These branch types also use the qualifying predicate and EC to control register rotation and predicate initialization. During the prolog phase, the qualifying predicate is either zero or one, depending upon the scheme used to program the loop. During the kernel phase, the qualifying predicate is one. During the epilog phase, the qualifying predicate is zero, and EC counts down. When br.wtop or br.wexit is executed with the qualifying predicate equal to zero and EC equal to one, a final decrement of EC and a final register rotation are done. If the qualifying

predicate and EC are zero, register rotation stops. These other effects are the same for the two branch types, and are described in Figure 2-4.

Figure 2-3. Operation of br.ctop and br.cexit

The loop-type branches (br.cloop, br.ctop, br.cexit, br.wtop, and br.wexit) are only allowed in instruction slot 2 within a bundle. Executing such an instruction in either slot 0 or 1 will cause an Illegal Operation fault, whether the branch would have been taken or not.

Read after Write (RAW) and Write after Read (WAR) dependency requirements are slightly different for branch instructions. Changes to BRs, PRs, and PFS by non-branch instructions are visible to a subsequent branch instruction in the same instruction group (i.e. a limited RAW is allowed for these resources). This allows for a low-latency compare-branch sequence, for example. The normal RAW requirements apply to the LC and EC application registers, and the RRBs.

Within an instruction group, a WAR dependency on PR 63 is not allowed if both the reading and writing instructions are branches. For example, a br.wtop or br.wexit may not use PR[63] as its qualifying predicate and PR[63] cannot be the qualifying predicate for any branch preceding a br.wtop or br.wexit in the same instruction group.

Figure 2-4. Operation of br.wtop and br.wexit

For dependency purposes, the loop-type branches effectively always write their associated resources, whether they are taken or not. The cloop type effectively always writes LC. When LC is 0, a cloop branch leaves it unchanged, but hardware may implement this as a re-write of LC with the same value. Similarly, br.ctop and br.cexit effectively always write LC, EC, the RRBs, and PR[63]. br.wtop and br.wexit effectively always write EC, the RRBs, and PR[63].

Values for various branch hint completers are shown in the following tables. Whether Prediction Strategy hints are shown in Table 2-6. Sequential Prefetch hints are shown in Table 2-7. Branch Cache Deallocation hints are shown in Table 2-8. See "Branch Prediction Hints" in Volume 1.

**Table 2-6. Branch Whether Hint**

| bwh Completer Branch Whether Hint |                   |

|-----------------------------------|-------------------|

| spnt                              | Static Not-Taken  |

| sptk                              | Static Taken      |

| dpnt                              | Dynamic Not-Taken |

| dptk                              | Dynamic Taken     |

**Table 2-7. Sequential Prefetch Hint**

| ph Completer | Sequential Prefetch Hint |

|--------------|--------------------------|

| few or none  | Few lines                |

| many         | Many lines               |

**Table 2-8. Branch Cache Deallocation Hint**

| dh Completer Branch Cache Deallocation Hint |                               |

|---------------------------------------------|-------------------------------|

| none                                        | Don't deallocate              |

| clr                                         | Deallocate branch information |

```

Operation:

if (ip_relative_form)

// determine branch target

tmp_{IP} = IP + sign_{ext}((imm_{21} << 4), 25);

else // indirect_form

tmp_{IP} = BR[b_2];

if (btype != 'ia')

// for IA-64 branches,

tmp_IP = tmp_IP & ~0xf;

// ignore bottom 4 bits of target

lower_priv_transition = 0;

switch (btype) {

case 'cond':

// simple conditional branch

tmp_taken = PR[qp];

break;

case 'call':

// call saves a return link

tmp_taken = PR[qp];

if (tmp_taken) {

BR[b_1] = IP + 16;

// ... and saves the stack frame

AR[PFS].pfm = CFM;

AR[PFS].pec = AR[EC];

AR[PFS].ppl = PSR.cpl;

alat_frame_update(CFM.sol, 0);

rse_preserve_frame(CFM.sol);

CFM.sof -= CFM.sol; // new frame size is size of outs

CFM.sol = 0;

CFM.sor = 0;

CFM.rrb.gr = 0;

CFM.rrb.fr = 0;

CFM.rrb.pr = 0;

break;

case 'ret':

// return restores stack frame

tmp_taken = PR[qp];

if (tmp_taken) {

// tmp_growth indicates the amount to move logical TOP *up*:

// tmp_growth = sizeof(previous out) - sizeof(current frame)

// a negative amount indicates a shrinking stack

tmp_growth = (AR[PFS].pfm.sof - AR[PFS].pfm.sol) - CFM.sof;

alat_frame_update(-AR[PFS].pfm.sol, 0);

rse_fatal = rse_restore_frame(AR[PFS].pfm.sol, tmp_growth,

CFM.sof);

if (rse_fatal) {

// See Section 6.4 in Volume 2.

CFM.sof = 0;

CFM.sol = 0;

CFM.sor = 0;

CFM.rrb.gr = 0;

CFM.rrb.fr = 0;

CFM.rrb.pr = 0;

} else // normal branch return

CFM = AR[PFS].pfm;

rse enable current frame load();

AR[EC] = AR[PFS].pec;

if (PSR.cpl u< AR[PFS].ppl) { // ... and restores privilege

PSR.cpl = AR[PFS].ppl;

lower_priv_transition = 1;

}

```

```

break;

case 'ia':

// switch to IA mode

tmp_taken = 1;

if (qp != 0)