# Intel® Itanium® Processor 9500 Series Reference Manual

Software Development and Optimization Guide

July 2012

Reference Number: 327132-001

**Notice:** This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® Itanium® Processor 9500 Series processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/go/virtualization

Available on select Intel® Core<sup>™</sup> processors. Requires an Intel® HT Technology-enabled system. Consult your PC manufacturer. Performance will vary depending on the specific hardware and software used. For more information including details on which processors support HT Technology, visit http://www.intel.com/info/hyperthreading.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel, Itanium, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010-2012, Intel Corporation. All Rights Reserved.

## Contents

| 1 | Intro | ntroduction |                                                              | 15  |

|---|-------|-------------|--------------------------------------------------------------|-----|

|   | 1.1   | Termin      | ology                                                        | 15  |

|   | 1.2   | Related     | Documentation                                                | 15  |

|   | 1.3   | Identify    | ying Intel® Itanium® Processors                              | 16  |

| 2 | The I | ntel Ita    | nium Processor 9500 series Core                              | 19  |

|   | 2.1   |             | PW                                                           |     |

|   | 2.2   |             | el Itanium Processor 9500 Series                             |     |

|   | 2.2   | 2.2.1       | Implementation Specific Behavior                             |     |

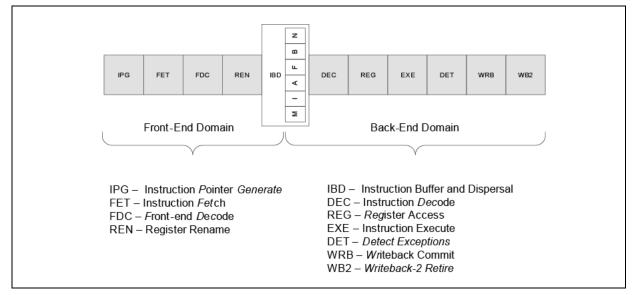

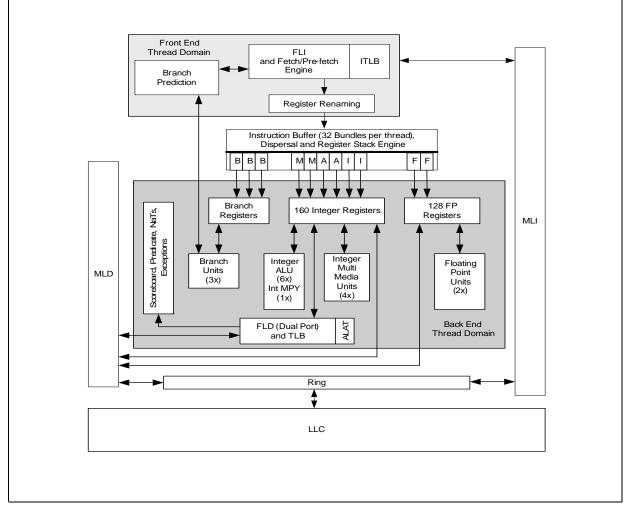

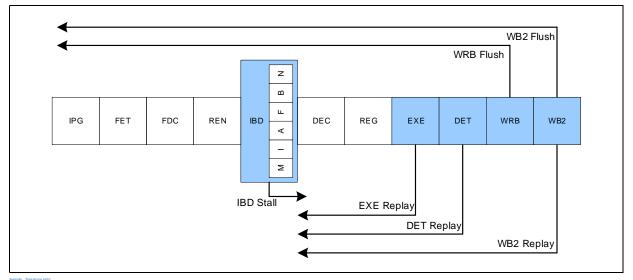

|   |       | 2.2.2       | Processor Core Pipeline                                      |     |

|   |       | 2.2.3       | New Instruction Support                                      |     |

|   |       | 2.2.4       | Advanced Load Address Table (ALAT)                           |     |

|   |       | 2.2.5       | Data Translation Lookaside Buffers (TLBs)                    |     |

|   |       | 2.2.6       | Architectural Ordering                                       |     |

|   |       | 2.2.7       | Execution Latencies                                          |     |

|   | 2.3   | Data A      | ccess Hints, Fetch, Dispersal and Execution                  |     |

|   |       | 2.3.1       | Data Access Hints                                            |     |

|   |       | 2.3.2       | Instruction Fetch                                            |     |

|   |       | 2.3.3       | Register Fetch                                               | 47  |

|   |       | 2.3.4       | Data Fetch                                                   |     |

|   |       | 2.3.5       | Instruction Execution                                        | 61  |

|   | 2.4   | Intel Ita   | anium Processor 9500 Series Multi-Threading                  | 71  |

|   |       | 2.4.1       | Frontend MT Introduction                                     | 71  |

|   |       | 2.4.2       | BE Thread Domain                                             | 72  |

|   | 2.5   | Intel®      | Virtualization Technology                                    | 83  |

|   |       | 2.5.1       | Intel® VT-i3 Support                                         |     |

|   | 2.6   | IA-32 E     | Execution                                                    | 84  |

|   | 2.7   | Brand I     | Information                                                  | 84  |

| 3 | Core  | Perform     | nance Monitoring                                             | 87  |

|   | 3.1   | Introdu     | ıction                                                       | 87  |

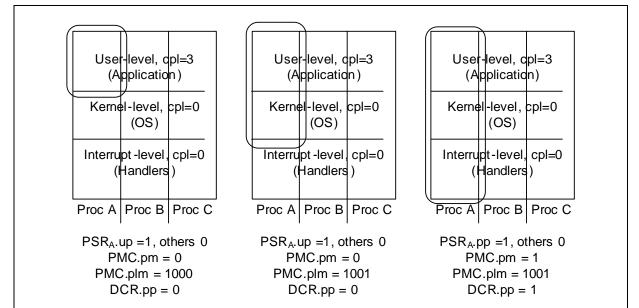

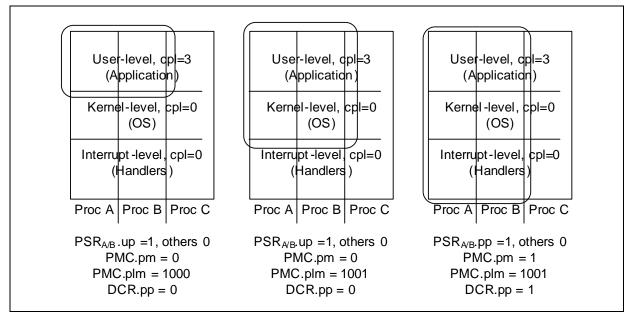

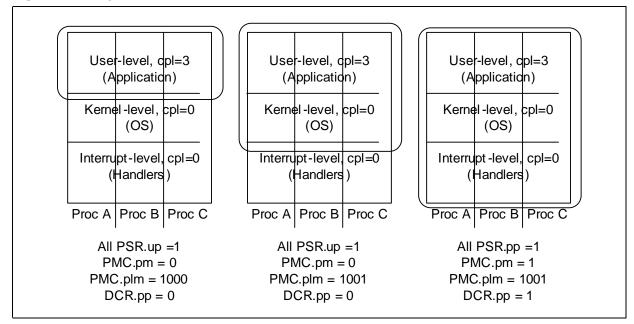

|   | 3.2   | Perform     | nance Monitor Programming Models                             |     |

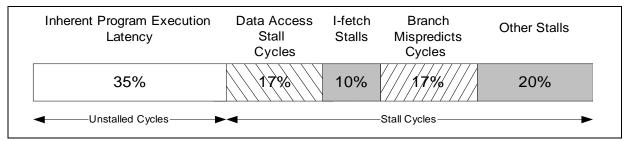

|   |       | 3.2.1       | Workload Characterization                                    |     |

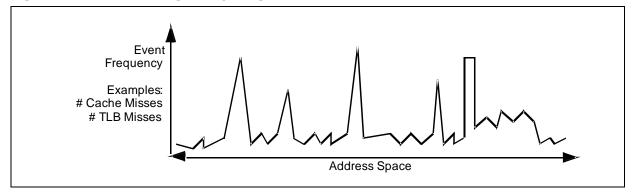

|   |       | 3.2.2       | Profiling                                                    |     |

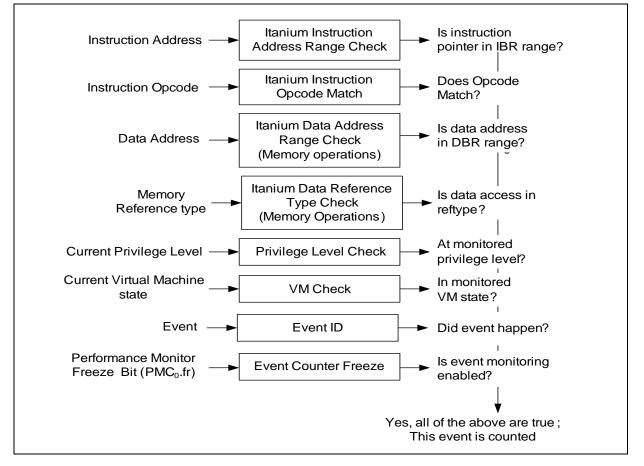

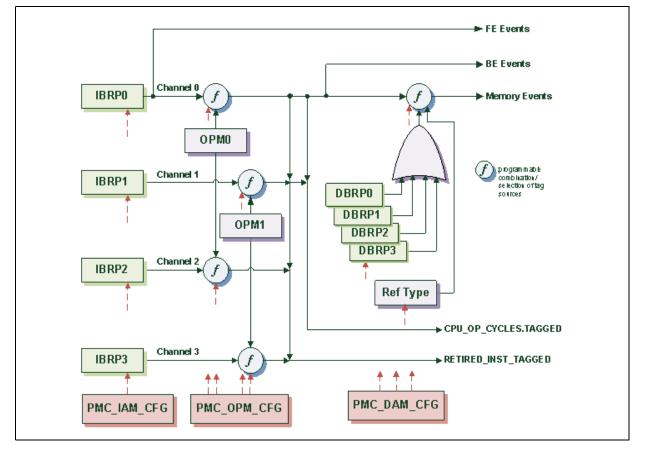

|   |       | 3.2.3       | Event Qualification                                          | 93  |

|   |       | 3.2.4       | References                                                   | 99  |

|   | 3.3   |             | nance Monitor State                                          |     |

|   |       | 3.3.1       | Performance Monitor Control and Accessibility 1              |     |

|   |       | 3.3.2       | Performance Counter Registers                                |     |

|   |       | 3.3.3       | Performance Monitor Event Counting Restrictions Overview     |     |

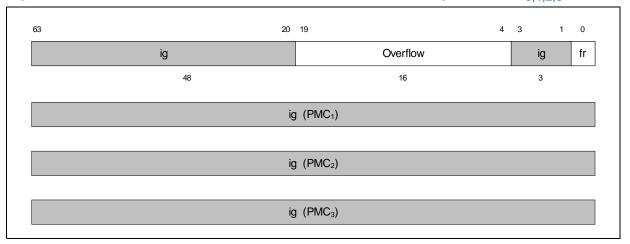

|   |       | 3.3.4       | Performance Monitor Overflow Status Registers (PMC0,1,2,3) 1 |     |

|   |       | 3.3.5       | Instruction Address Range Matching                           |     |

|   |       | 3.3.6       | Opcode Match Check                                           |     |

|   |       | 3.3.7       | Data Address Range Matching (PMC_DAM_CFG)                    |     |

|   |       | 3.3.8       | Data Reference Type Matching (PMC_DAM_CFG)                   |     |

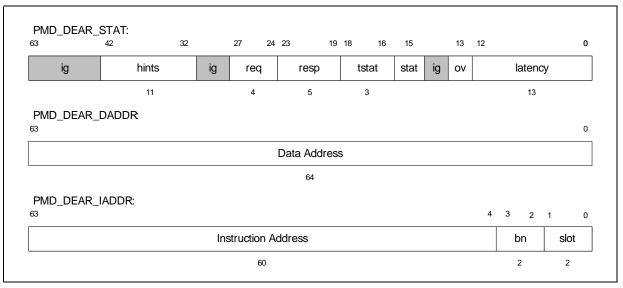

|   |       | 3.3.9       | Event Address Registers                                      |     |

|   |       |             | Instruction Cache EAR                                        |     |

|   |       |             | Data Cache EAR                                               |     |

|   |       |             | Execution Trace Buffer                                       |     |

|   |       |             | Thread-State Event Configuration                             |     |

|   |       |             | Interrupt Counting<br>PerfMon Interrupts                     |     |

| _ | -     |             |                                                              |     |

| 4 | Core  | Perform     | nance Monitor Events                                         | 133 |

| 4.1  | Introdu                                                                                                                                                                                               | uction1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 4.1.1                                                                                                                                                                                                 | Categorization of Events1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                                                                                 |

|      | 4.1.2                                                                                                                                                                                                 | Multi-Threading and Event Types1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                                                                                 |

|      | 4.1.3                                                                                                                                                                                                 | Performance Event Associativity1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34                                                                                                                                                 |

|      | 4.1.4                                                                                                                                                                                                 | Event Description Tables Field Definition1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                                                                                                                                                 |

|      | 4.1.5                                                                                                                                                                                                 | Performance Monitor Events Ordered by Event Code1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                                                                                 |

|      | 4.1.6                                                                                                                                                                                                 | Performance Monitor Events Ordered by Event Name1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                    |

| 4.2  | Perforr                                                                                                                                                                                               | nance Monitor Events by Area1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                                                                                                                                 |

|      | 4.2.1                                                                                                                                                                                                 | Basic Events1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                                                                                                                                 |

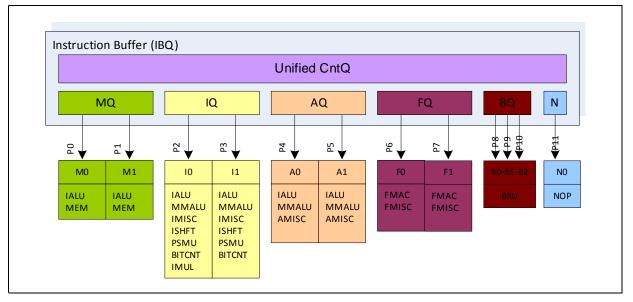

|      | 4.2.2                                                                                                                                                                                                 | Dispersal Events1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76                                                                                                                                                 |

|      | 4.2.3                                                                                                                                                                                                 | Execution Events1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                                                                 |

|      | 4.2.4                                                                                                                                                                                                 | Back-End Cycle Accounting1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 94                                                                                                                                                 |

|      | 4.2.5                                                                                                                                                                                                 | Front-End Cycle Accounting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 05                                                                                                                                                 |

|      | 4.2.6                                                                                                                                                                                                 | Branch Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 09                                                                                                                                                 |

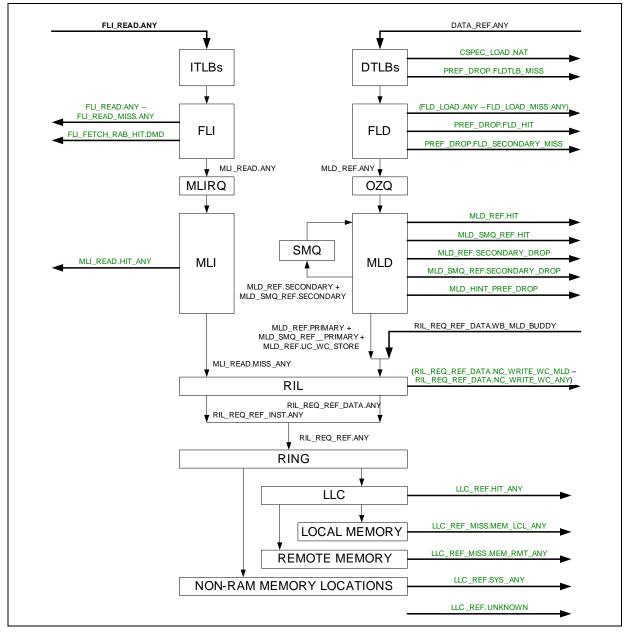

|      | 4.2.7                                                                                                                                                                                                 | Memory Hierarchy Events2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                 |

|      | 4.2.8                                                                                                                                                                                                 | FLI Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                                                                                                 |

|      | 4.2.9                                                                                                                                                                                                 | MLI Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                                                                                 |

|      | 4.2.10                                                                                                                                                                                                | FLITLB Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                                 |

|      | 4.2.11                                                                                                                                                                                                | MLITLB Events2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                                                 |

|      | 4.2.12                                                                                                                                                                                                | FLD Events2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                                                 |

|      |                                                                                                                                                                                                       | MLD Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

|      | 4.2.14                                                                                                                                                                                                | FLDTLB Events2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54                                                                                                                                                 |

|      |                                                                                                                                                                                                       | MLDTLB Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |

|      |                                                                                                                                                                                                       | DPF Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

|      |                                                                                                                                                                                                       | RIL Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

|      |                                                                                                                                                                                                       | RSE Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

|      |                                                                                                                                                                                                       | LLC Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

|      |                                                                                                                                                                                                       | System Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                    |

|      | 4.2.21                                                                                                                                                                                                | Multithreading Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95                                                                                                                                                 |

| Unco | ore Perf                                                                                                                                                                                              | ormance Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 07                                                                                                                                                 |

| 5.1  | Dreese                                                                                                                                                                                                | sor Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>7</u>                                                                                                                                           |

| D. I | Process                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 07                                                                                                                                                 |

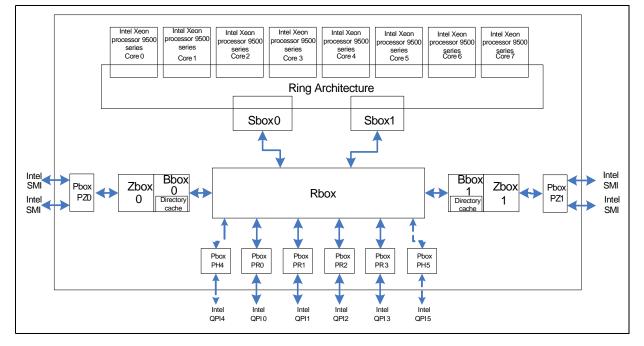

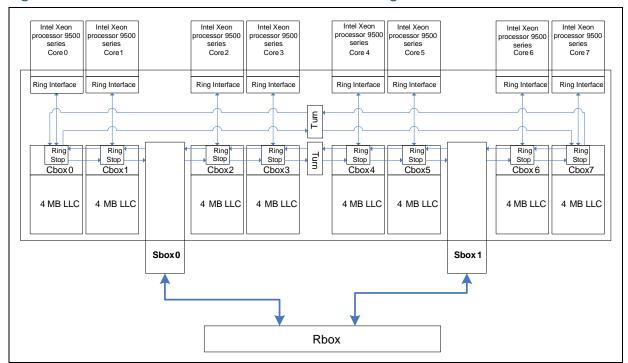

| э. I | 5.1.1                                                                                                                                                                                                 | Ring Interconnect Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                    |

| э. I |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 09                                                                                                                                                 |

| 0.1  | 5.1.1                                                                                                                                                                                                 | Ring Interconnect Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 09<br>10                                                                                                                                           |

| 3.1  | 5.1.1<br>5.1.2                                                                                                                                                                                        | Ring Interconnect Overview    3      Cache Control (Cbox) Overview    3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 09<br>10<br>11                                                                                                                                     |

| J. I | 5.1.1<br>5.1.2<br>5.1.3                                                                                                                                                                               | Ring Interconnect Overview    3      Cache Control (Cbox) Overview    3      Last-Level Cache (LLC) Overview    3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 09<br>10<br>11<br>12                                                                                                                               |

| 0.1  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                                                                      | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 09<br>10<br>11<br>12<br>12                                                                                                                         |

| 3.1  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                                                                                                                                                             | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 09<br>10<br>11<br>12<br>12<br>12<br>13                                                                                                             |

| 3.1  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6                                                                                                                                                    | Ring Interconnect Overview30Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13                                                                                                       |

|      | $5.1.1 \\ 5.1.2 \\ 5.1.3 \\ 5.1.4 \\ 5.1.5 \\ 5.1.6 \\ 5.1.7 \\ 5.1.8 \\ 5.1.9 $                                                                                                                      | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13                                                                                                 |

| 5.1  | $5.1.1 \\ 5.1.2 \\ 5.1.3 \\ 5.1.4 \\ 5.1.5 \\ 5.1.6 \\ 5.1.7 \\ 5.1.8 \\ 5.1.9 $                                                                                                                      | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13                                                                                                 |

|      | $5.1.1 \\ 5.1.2 \\ 5.1.3 \\ 5.1.4 \\ 5.1.5 \\ 5.1.6 \\ 5.1.7 \\ 5.1.8 \\ 5.1.9 $                                                                                                                      | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13                                                                                                 |

|      | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1                                                                                                      | Ring Interconnect Overview34Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 09<br>10<br>11<br>12<br>12<br>13<br>13<br>13<br>14                                                                                                 |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2                                                                                             | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 09<br>10<br>11<br>12<br>12<br>13<br>13<br>13<br>14                                                                                                 |

|      | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global                                                                                   | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Performance Monitoring Control3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13<br>14<br>17<br>19                                                                               |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global<br>5.3.1                                                                          | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Performance Monitoring Control3Global Enable/Disable3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13<br>13<br>14<br>17<br>19<br>20                                                                   |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global<br>5.3.1<br>5.3.2                                                                 | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Uncore PMU Summary Tables3Performance Monitoring Control3Setting Up a Global Monitoring Session3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 09<br>10<br>11<br>12<br>12<br>13<br>13<br>13<br>14<br>17<br>19<br>20<br>20                                                                         |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global<br>5.3.1<br>5.3.2<br>5.3.3                                      | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Uncore PMU Summary Tables3Performance Monitoring Control3Setting Up a Global Monitoring Session3Reading the Sample Interval3                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 09<br>10<br>11<br>12<br>12<br>13<br>13<br>13<br>14<br>17<br>19<br>20<br>21                                                                         |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4                             | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Uncore PMU Summary Tables3Setting Up a Global Monitoring Session3Reading the Sample Interval3Enabling a New Sample Interval from Frozen Counters3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 09<br>10<br>11<br>12<br>12<br>13<br>13<br>13<br>13<br>14<br>17<br>20<br>20<br>21<br>22                                                             |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.7<br>5.1.8<br>5.1.9<br>Uncore<br>5.2.1<br>5.2.2<br>Global<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5                    | Ring Interconnect Overview3Cache Control (Cbox) Overview3Last-Level Cache (LLC) Overview3System Bridge (Sbox) Overview3Global Coherence Engine (Bbox) Overview3Integrated Memory Controller (Zbox) Overview3Inter-processor Router (Rbox) Overview3Port Physical Interfaces (Pbox) Overview3System Utilities Controller (Ubox) Overview3PMU Programming Overview3On Accessing Uncore PMUs by Virtual Addresses3(Win/Linux*)3153Uncore PMU Summary Tables3Setting Up a Global Monitoring Session3Reading the Sample Interval3Enabling a New Sample Interval from Frozen Counters3Global Performance Monitors3                                                                                                                                                                                                                                                                                                                                                                                                                      | 09<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13<br>14<br>17<br>19<br>20<br>20<br>21<br>22<br>22                                                 |