# Intel® IA-64 Architecture Software Developer's Manual

**Specification Update**

**March 2001**

**Notice:** The Intel® Itanium processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Document Number: 248699-004

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://developer.intel.com/design/litcentr.

Copyright © 2001, Intel Corporation

\*Other brands and names are the property of their respective owners.

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Table of Changes     | 7  |

| Specification Changes        | 8  |

| Specification Clarifications | 15 |

| Documentation Changes        | 22 |

# Revision History

| Revision<br>Number | Description                                                                                                                                                             | Date          |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0                | Initial version of this document.                                                                                                                                       | April 2000    |

| 2.0                | Added changes to performance monitoring Section (Section 7.8, Volume 4)                                                                                                 | October 2000  |

|                    | Added a clarification to class pr-writers-int in Table A-5 of Volume 2                                                                                                  |               |

|                    | Added a clarification to Section 4.4.6.1 of Volume 2                                                                                                                    |               |

| 3.0                | Added a VHPT walk and forward progress change (Section 4.1.1.2, Volume 2)                                                                                               | December 2000 |

|                    | Revised Chapter 7 of Volume 4, Performance Monitoring Events (new Section 7.6.5, Frontside Bus; added bus monitors to Section 7.8, Event List; misc. changes and fixes) |               |

|                    | Added a faults in Id.c that hits ALAT clarification (Section 4.4.5.3.1, Volume 1)                                                                                       |               |

|                    | Added an IA-32 IBR/DBR match clarification (Section 7.1.1, Volume 2)                                                                                                    |               |

|                    | Added an IA-32 CPUID clarification (p. 5-71 of Volume 3)                                                                                                                |               |

|                    | Added ISR figure changes on pp. 8-5, 8-26, 8-33 and 8-36 of Volume 2)                                                                                                   |               |

| 4.0                | Added a change to PAL_CACHE_FLUSH return argument (Section 11.8.3, Volume 2)                                                                                            | March 2001    |

|                    | Added a change to PAL self-test Control and PAL_A procedure requirement change (Section 11.2, Volume 2)                                                                 |               |

|                    | Added clarifications to PAL_CACHE_FLUSH (Section 11, Volume 2)                                                                                                          |               |

|                    | Added a clarification to non-speculative reference (Section 4.4.6, Volume 2)                                                                                            |               |

|                    | Added clarifications to RID and Preferred Page Size usage (Section 4.1, Volume 2)                                                                                       |               |

|                    | Added clarifications to VHPT read atomicity (Section 4.1, Volume 2)                                                                                                     |               |

|                    | Added clarifications to IIP and WC flush (Section 4.4.5, Volume 2)                                                                                                      |               |

|                    | Revised IBR and DBR addressing (Section 6.2.4, Volume 4)                                                                                                                |               |

|                    | Revised figures for extract, deposit, and alloc instructions (Section 2.2,                                                                                              |               |

|                    | Volume 3)                                                                                                                                                               |               |

|                    | Revised RSE and PMC typographical errors (Section 6.4, Volume 2)                                                                                                        |               |

|                    | Revised DV table (Section A.4, Volume 2)                                                                                                                                |               |

# **Preface**

This document is an update to the specifications contained in the Affected Documents/Related Documents in the table below. This document is a compilation of specification changes, specification clarifications and document changes. It does not cover errata.

## **Affected Documents/Related Documents**

| Title                                                                                                  | Document # |

|--------------------------------------------------------------------------------------------------------|------------|

| Intel® IA-64 Architecture Software Developer's Manual, Volume 1: IA-64 Application Architecture        | 245317     |

| Intel® IA-64 Architecture Software Developer's Manual, Volume 2: IA-64 System Architecture             | 245318     |

| Intel® IA-64 Architecture Software Developer's Manual, Volume 3: Instruction Set Reference             | 245319     |

| Intel® IA-64 Architecture Software Developer's Manual, Volume 4: Itanium™ Processor Programmer's Guide | 245320     |

## **Nomenclature**

**Specification Changes** are modifications to the current published specifications for the Itanium<sup>TM</sup> processor. These changes will be incorporated in the next release of the specifications.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the *Intel*® *IA-64 Architecture Software Developer's Manual*.

# **Summary Table of Changes**

The following tables indicate the specification changes, specification clarifications, or documentation changes which apply to the *Intel*® *IA-64 Architecture Software Developer's Manual*.

# **Specification Changes**

| No. | Page | SPECIFICATION CHANGES                                                  |

|-----|------|------------------------------------------------------------------------|

| 1   | 8    | Volume 2: PAL_CACHE_FLUSH return argument addition                     |

| 2   | 8    | Volume 2: PAL self-test Control and PAL_A procedure requirement change |

# **Specification Clarifications**

| No. | Page | SPECIFICATION CLARIFICATIONS                              |

|-----|------|-----------------------------------------------------------|

| 1   | 15   | Volume 2: PAL_CACHE_FLUSH clarifications                  |

| 2   | 17   | Volume 2: Non-speculative reference clarification         |

| 3   | 17   | Volume 2: RID and Preferred Page Size usage clarification |

| 4   | 18   | Volume 2: VHPT read atomicity clarification               |

| 5   | 19   | Volume 2: IIP and WC flush clarifications                 |

# **Documentation Changes**

| No. | Page | DOCUMENTATION CHANGES                                                 |

|-----|------|-----------------------------------------------------------------------|

| 1   | 22   | Volume 4: IBR and DBR addressing typographical errors                 |

| 2   | 23   | Volume 3: Figure changes for extract, deposit, and alloc instructions |

| 3   | 24   | Volume 2: RSE and PMC typographical errors                            |

| 4   | 25   | Volume 2: DV table typographical error                                |

# **Specification Changes**

#### 1. Volume 2: PAL\_CACHE\_FLUSH return argument addition

On p. 11-42 and 11-45, addition of a new return argument of value 2:

a. Page 11-42, Status section. Add a new return status of value 2:

| Status Value | Description                                                                               |

|--------------|-------------------------------------------------------------------------------------------|

| 2            | Call completed without error, but a PMI was taken during the execution of this procedure. |

| 1            | Call has not completed flushing due to a pending external event                           |

| 0            | Call completed without error                                                              |

| -2           | Invalid argument                                                                          |

| -3           | Call completed with error                                                                 |

b. Page 11-45, Status bullet. Add the following new paragraph right under status bullet:

When the call returns a 2, it indicates that the call completed without any errors but that a PMI was taken during the execution of this call. This indicates to the caller that all cache lines that were present in the cache (when the most recent call to PAL\_CACHE\_FLUSH with a *progress\_indicator* of zero) are flushed but that code and data related to handling PMIs may be present in the cache.

#### 2. Volume 2: PAL self-test Control and PAL\_A procedure requirement change

On p. 11-9, Section 11.2.1, replace the following:

...PALE\_RESET then branches to SALE\_ENTRY to determine if a recovery condition exists, which would require an update of the firmware. If it does, SALE\_ENTRY performs the update and resets the system. If not, SAL returns to PALE\_RESET, which performs a full processor self-test and initialization. PAL may execute IA-32 instructions ...

#### WITH (new paragraph):

PALE\_RESET then branches to SALE\_ENTRY to determine if a recovery condition exists, which would require an update of the firmware. If it does, SALE\_ENTRY performs the update and resets the system. If no firmware recovery is needed, SAL returns to PALE\_RESET to perform the processor self-tests and initialization. SAL can control the length and coverage of the PAL processor self-test by examining and modifying the self-test control word passed to SAL at the firmware recovery hand-off state. Please see Section 11.2.3 for more information on the self-test control word.

The PAL processor self-tests are split into two phases. The first phase is written to test processor features that do not require external memory to be present to execute correctly. These tests are automatically run when SAL returns to PAL after the branch to SALE\_ENTRY for a firmware recovery check. This section is referred to as phase one of processor self-test and they are generally run early during the processor boot process. The second phase is written requiring that external memory is available to execute correctly. These tests are run when a call to the PAL procedure PAL\_TEST\_PROC is made with the correct parameters set up. These tests are referred to as phase two of processor self-test since they are usually run later in the processor boot process after external memory has been initialized on the platform.

PAL may execute IA-32 instructions ....

On p. 11-9, Section 11.2.2, PALE\_RESET Exit State. Modify GR34 bullet as follows:

#### FROM:

... needed for SALE\_ENTRY to perform firmware recovery will be available. These procedures are PAL\_PLATFORM\_ADDR, PAL\_PROC\_GET\_FEATURES (to view current settings), PAL\_PROC\_SET\_FEATURES (enable/disable cache), PAL\_CACHE\_INIT(level=all, sidesboth,restrict-no) and an implementation specific PAL procedure for PAL authentication.

#### TO:

... needed for SALE\_ENTRY to perform firmware recovery will be available. These procedures are PAL\_PLATFORM\_ADDR and an implementation specific PAL procedure for PAL authentication.

On p. 11-9, Section 11.2.2, PALE\_RESET Exit State. Add a GR37 bullet:

GR37 contains the self-test control word as defined in Section 11.2.3. This control word is

processor implementation specific and informs SAL if self-test control is implemented and the

number of controllable bits. If self-test control is implemented, PAL will read this value when

SAL returns to PAL after firmware recovery check. If the self-test control is not supported, this

register will be ignored when SAL returns to PAL after firmware recovery check.

On p. 11-10, Cache and TLB bullets. Change

#### FROM:

- Cache: The processor internal caches are enabled and invalidated. The caches themselves and

the paths from the caches to the processor core have been tested. The path from external

memory to the caches have not been tested.

- TLB: The TRs and TCs are initialized with all entries having been invalidated. The TLB is

disabled because PSR.it=PSR.dt=PSR.rt=0 and is not available for use until after the second

phase of processor self-test. (SEE PAL\_TEST\_PROCESSOR).

#### TO:

- Cache: The processor internal caches are enabled and invalidated. Unless directed otherwise

by the self-test control word, phase one of the processor self-test verifies the caches

themselves and the paths from the caches to the processor core. The path from external

memory to the caches cannot be tested until phase two of the processor self-test.

- TLB: The TRs and TCs are initialized with all entries having been invalidated. The TLB is disabled because PSR.it=PSR.dt=PSR.rt=0. The TLBs cannot be fully tested until phase two of the processor self-test.

On p. 11-11, description of the *state* field which is part of the Self-test State Parameter. Change FROM:

• state - a 2-bit field indicating the state of the processor after self-test.

#### TO:

• *state* - a 2-bit field indicating the state of the processor after self-test. If SAL directed PAL to skip some self tests by modifying the self-test control word, failures related to these self-tests will not be reflected in this state.

On p. 11-12, change the bullet describing FUNCTIONALLY RESTRICTED

#### FROM:

The paths between the processor controlled caches and the register files must work during the

tests in PAL\_RESET, and the entire path from memory through the caches to the register file

must work during the tests in PAL\_TEST\_PROCESSOR

#### TO:

• The paths between the processor controlled caches and the register files have been shown to work. The path between the processor caches and memory cannot be validated until phase two of the processor self-test invoked by the PAL\_TEST\_PROC procedure.

On p. 11-12, add a new Section 11.2.3 titled PAL Self-test Control Word:

The PAL self-test control word is a 48-bit value. This bit field is defined in Figure 11-9.

Add a Figure 11-9, showing 48 bits, bit 47 is named "cs" and bits 46-0 named "test\_control".

• test\_control - This is an ordered implementation specific control word that allows the user control over the length and run-time of the processor self-tests. This control word is ordered from the longest running tests up to the shortest running tests with bit 0 controlling the longest running test.

PAL may not implement all 47-bits of the test\_control word. PAL communicates if a bit provides control by placing a zero in that bit. If a bit provides no control, PAL will place a one in it.

PAL will have two sets of test control bits for the two phases of the processor self-test.

PAL provides information about implemented *test\_control* bits at the hand-off from PAL to SAL for the firmware recovery check. These *test\_control* bits provide control for phase one of processor self-test. It also provides this information via the PAL procedure call PAL\_TEST\_INFO for both the phase one and phase two processor tests depending on which information the caller is requesting.

PAL interprets these bits as input parameters on two occasions. The first time is when SAL passes control back to PAL after the firmware recovery check. The second time is when a call to PAL\_TEST\_PROC is made. When PAL interprets these bits it will only interpret implemented *test\_control* bits and will ignore the values located in the un-implemented *test\_control* bits.

PAL interprets the implemented bits such that if a bit contains a zero, this indicates to run the test. If a bit contains a one, this indicates to PAL to skip the test.

If the *cs* bit indicates that control is not available, the *test\_control* bits will be ignored or generate an illegal argument in procedure calls if the caller sets these bits.

• cs - Control Support: This bit defines if an implementation supports control of the PAL self-tests via the self-test control word. If this bit is 0, the implementation does not support control of the processor self-tests via the self-test control word. If this bit is 1, the implementation does support control of the processor self-tests via the self-test control word.

If control is not supported, GR37 will be ignored at the hand-off between SAL and PAL after the firmware recovery check and the PAL procedures related to the processor self-tests may return illegal arguments if a user tries to use the self-test control features.

On p. 11-31, Table 11-16, change the procedure name and description section.

#### FROM:

• PAL MEM FOR TEST

#### TO:

• PAL\_TEST\_INFO

and

#### FROM:

Return the amount of memory needed for late processor self-test

#### TO:

Returns alignment and size requirements needed for the memory buffer passed to the PAL\_TEST\_PROC procedure as well as information on self-test control words for the processor self tests.

On p. 11-91, PAL\_MEM\_FOR\_TEST procedure description:

a. Modify purpose statement to state the following:

Returns the alignment and size requirements needed for the memory buffer passed to the PAL\_TEST\_PROC procedure as well as information on self-test control words for the processor self-tests.

#### b. Add a new Argument:

| Argument   | Description                                                                                    |

|------------|------------------------------------------------------------------------------------------------|

| test_phase | Unsigned integer that specifies which phase of the processor self-test information is being    |

|            | requested on. A value of 0 indicates the phase two of the processor self-test and a value of 1 |

|            | indicates phase one of the processor self-test. All other values are reserved.                 |

#### c. Add a new Return:

| Return Value | Description                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------|

| st_control   | 48-bit wide bit-field indicating if control of the processor self-tests is supported and which bits |

|              | of the 'test_control' field are defined for use.                                                    |

#### d. Modify the description section to the following:

PAL\_TEST\_INFO returns the size and alignment requirements for the memory buffer that is passed to the PAL\_TEST\_PROC procedure and returns information on the implementation of the self-test control word based on the *test\_phase* input argument. Please see Section 11.2.3 for more information on the self-test control word.

When *test\_phase* is equal to zero, information is returned about phase two of the processor self-test. These are the tests that require external memory to execute properly. When *test\_phase* is equal to one, information is returned about phase one of the processor self-test. These are the tests that are normally run during PALE\_RESET and do not require external memory to properly execute. When information is requested about phase one of the processor self-test a memory buffer and alignment argument will be returned as well since these tests may need to save and restore processor state to this memory buffer if executed from the PAL\_TEST\_PROC procedure.

On p. 11-102, PAL\_TEST\_PROC procedure description. Change the input arguments as follows:

#### FROM:

Argument

| 3                            |                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| index                        | Index of PAL_TEST_PROC within the list of PAL procedures.                                                                                                                                                                                                                                                                                              |

| test_address                 | 64-bit physical address of main memory area to be used by processor self-test. The memory                                                                                                                                                                                                                                                              |

|                              | region passed must be cacheable, bit 63 must be zero.                                                                                                                                                                                                                                                                                                  |

| test_size                    | Number of bytes of main memory to be used by processor self-test.                                                                                                                                                                                                                                                                                      |

| attributes                   | A 16-bit mask of memory attributes to be tested.                                                                                                                                                                                                                                                                                                       |

| TO:                          |                                                                                                                                                                                                                                                                                                                                                        |

|                              |                                                                                                                                                                                                                                                                                                                                                        |

| Argument                     | Description                                                                                                                                                                                                                                                                                                                                            |

| Argument index               | Description Index of PAL_TEST_PROC within the list of PAL procedures.                                                                                                                                                                                                                                                                                  |

|                              | •                                                                                                                                                                                                                                                                                                                                                      |

| index                        | Index of PAL_TEST_PROC within the list of PAL procedures.                                                                                                                                                                                                                                                                                              |

| index                        | Index of PAL_TEST_PROC within the list of PAL procedures.  64-bit physical address of main memory area to be used by processor self-test. The memory                                                                                                                                                                                                   |

| index<br>test_address        | Index of PAL_TEST_PROC within the list of PAL procedures. 64-bit physical address of main memory area to be used by processor self-test. The memory region passed must be cacheable, bit 63 must be zero.                                                                                                                                              |

| index test_address test_info | Index of PAL_TEST_PROC within the list of PAL procedures. 64-bit physical address of main memory area to be used by processor self-test. The memory region passed must be cacheable, bit 63 must be zero. Input argument specifying the size of the memory buffer passed and the phase of the                                                          |

| index<br>test_address        | Index of PAL_TEST_PROC within the list of PAL procedures. 64-bit physical address of main memory area to be used by processor self-test. The memory region passed must be cacheable, bit 63 must be zero. Input argument specifying the size of the memory buffer passed and the phase of the processor self-test that should be run. See Figure 11-9. |

a. Change the description section to the following:

Description

The PAL\_TEST\_PROC procedure will perform a phase of the processor self-tests as directed by the *test info* and the *test control* input parameters.

test\_address points to a contiguous memory region to be used by PAL\_TEST\_PROC. This memory region must be aligned as specified by the alignment return value from PAL\_TEST\_INFO, otherwise this procedure will return with an invalid argument return value. The PAL\_TEST\_PROC routine requires that the memory has been initialized and that there are no known uncorrected errors in the allocated memory.

The *test\_info* input parameter specifies the size of the memory buffer passed to the procedure and which phase of the processor self-test is requested to be run. (either phase one or phase two)

Add a figure that shows upper 8 bits as test\_phase and lower 56 bits as buffer\_size.

- buffer\_size indicates the size in bytes of the memory buffer that is passed to this procedure. buffer\_size must be greater than or equal in size to the bytes\_needed return value of the PAL\_TEST\_INFO otherwise this procedure will return with an invalid argument return value.

- test\_phase defines which phase of the processor self-tests are requested to be run. A value of zero indicates to run phase two of the processor self-tests. Phase two of the processor self-tests are ones that require external memory to execute correctly. A value of one indicates to run phase one of the processor self-tests. Phase one of the processor self-tests are tests run during PALE\_RESET and do not depend on external memory to run correctly. When the caller requests to have phase one of the processor self-test run via this procedure call, a memory buffer may be needed to save and restore state as required by the PAL calling conventions. The procedure PAL\_TEST\_INFO informs the caller about the requirements of the memory buffer.

The *test\_params* input argument specifies which memory attributes are allowed to be used with the memory buffer passed to this procedure as well as the self-test control word. The self-test control word *test\_control* controls the run-time and coverage of the processor self-test phase specified in the *test\_phase* parameter.

Add a figure that shows upper 48 bits as test\_control, next 8-bits as reserved and lower 8-bits as attributes.

- attributes specifies the memory attributes that are allowed to be used with the memory buffer passed to this procedure. The attributes parameter is a vector where each bit represents one of the virtual memory attributes defined by the architecture The bit field position corresponds to the numeric memory attribute encoding defined in Section 9.4, "Memory Attributes". The caller is required to support the cacheable attribute for the memory buffer, otherwise an invalid argument will be returned.

- test\_control is the self-test control word corresponding to the test\_phase passed. This test\_control directs the coverage and run-time of the processor self-tests specified by the test\_phase input argument. Information about the self-test control word can be found on Section 11.2.3 and information on if this feature is implemented and the number of bits supported can be obtained by the PAL\_TEST\_INFO procedure call. If this feature is implemented by the processor, the caller can selectively skip parts of the processor self-test by setting test\_control bits to a one. If a bit has a zero, this test will be run. The values in the unimplemented bits are ignored. If PAL\_TEST\_INFO indicated that the self-test control word is not implemented, this procedure will return with an invalid argument status if the caller sets any of the test\_control bits.

PAL\_TEST\_PROC will classify the processor after the self-test in one of four states: CATASTROPHIC FAILURE, FUNCTIONALLY RESTRICTED, PERFORMANCE RESTRICTED, or HEALTHY. These processor self-test states are described in Table 11-14 on p. 11-11. If PAL\_TEST\_PROC returns in the FUNCTIONALLY RESTRICTED or PERFORMANCE RESTRICTED states the self-test\_status return value can provide additional information regarding the nature of the failure. In the case of a CATASTROPHIC FAILURE, the procedure does not return.

The procedure will only perform memory accesses to the buffer passed to it using the memory attributes indicated in the attributes bit-field. The caller must ensure that the memory region passed to the procedure is in a coherent state.

PAL\_TEST\_PROC may modify PSR bits or system registers as necessary to test the processor. These bits or registers must be restored upon exit from PAL\_TEST\_PROC with the exception of the translation caches, which are evicted as a result of testing. PAL\_TEST\_PROC is free to invalidate all cache contents. If the caller depends on the contents of the cache, they should be flushed before making this call. PAL\_TEST\_PROC requires that the RSE is set up properly to handle spills and fills to a valid memory location if the contents of the register stack are needed. PAL\_TEST\_PROC requires that the memory buffer passed to it is not shared with other processors running this procedure in the system at the same time. PAL\_TEST\_PROC will use this memory region in a non-coherent manner.

#### 3. Volume 2: VHPT walks and forward progress

On p. 4-5, Section 4.1.1.2, change the second bullet under "In order to ensure forward progress for IA-64 code, the following rules must be observed by the processor and software:"

TO:

The processor may occasionally invalidate the last TC entry inserted. The processor must guarantee visibility of the last inserted TC entry to all references while PSR.ic is zero. The processor must eventually guarantee visibility of the last inserted TC entry until an rfi sets PSR.ic to 1 and at least one instruction is executed with PSR.ic equal to 1, and completes without a fault or interrupt. The last inserted TC entry may be occasionally removed before this point, and software must be prepared to re-insert the TC entry on a subsequent fault. For example, eager or mandatory RSE activity, speculative VHPT walks, or other interruptions of the restart

instructions may displace the software-inserted TC entry, but when software later re-inserts the same TC entry, the processor must eventually complete the restart instruction to ensure forward progress, even if that restart instruction takes other faults which must be handled before it can complete. If PSR.ic is set to 1 by instructions other than rfi, the processor does not guarantee forward progress.

On p. 4-5, Section 4.1.1.2, insert these two bullets below the bullet cited above:

- If software inserts an entry into the TLB with an overlapping entry (same or larger size) in the VHPT, and if the VHPT walker is enabled, forward progress is not guaranteed. See VHPT Searching, Section 4.1.5.2 on p. 4-15.

- Software may only make references to memory with physical addresses or with virtual addresses which are mapped with TRs, or to addresses mapped by the just-inserted translation, between the insertion of a TC entry, and the execution of the instruction with PSR.ic equal to 1 which is dependent on that entry for forward progress. Software may also make repeated attempts to execute the same instruction with PSR.ic equal to 1. If software makes any other memory references than these, the processor does not guarantee forward progress.

On p. 4-14, at the end of Section 4.1.5, add this paragraph:

If software needs to control the entries inserted into the TLB more explicitly, or programs the VHPT with differing mappings for the same virtual address range, it may need to take additional action to ensure forward progress. See VHPT searching, Section 4.1.5.2 on p. 4-15.

On p. 4-15, at the end of Section 4.1.5.2, add this paragraph:

VHPT walks may be done speculatively by the processor's VHPT walker. Additionally, VHPT walks triggered by non-speculatively-executed instructions are not required to be done in program order. Therefore, if the walker is enabled and if the VHPT contains multiple entries that map the same virtual address range, software must set up these entries such that any of them can be used in the translation of any part of this virtual address range. Additionally, if software inserts a translation into the TLB which is needed for forward progress, and this translation has a smaller page size than the translation which would have been inserted on a VHPT walk for the same address, then software may need to disable the VHPT walker in order to ensure forward progress, since this inserted translation may be displaced by a VHPT walker before it can be used.

# 4. Revised Chapter 7 of Volume 4, Performance Monitoring Events (text included at end of this update)

Volume 4, Chapter 7, Performance Monitoring Events has been modified to include new content and reflect changes to enhance readability. The entire content of Chapter 7 are presented at the end of this update for convenience.

**Note:** The content in this specification update completely replaces Chapter 7 in Volume 4 of the *Intel*® *IA-64 Software Developer's Manual*.

# Specification Clarifications

#### 1. Volume 2: PAL\_CACHE\_FLUSH clarifications

On pp. 11-33 and 11-34, Table 11-19:

- Remove footnote reference (a.) from the psr.ic bit

- Remove footnote (a.) described below the table.

On pp. 11-42 to 11-45, PAL\_CACHE\_FLUSH procedure changes:

a. Page 11-42, return status of 1 description. Replace with the following:

Call has not completed flushing due to a pending interrupt.

b. Page 11-43, *int* bullet section. Remove all PMI references by replacing with the following:

*int* - 1 bit field indicating if the processor will periodically poll for external interrupts while flushing the specified *cache\_type(s)*.

If this bit is a 0, unmasked external interrupts will not be polled. The processor will ignore all pending unmasked external interrupts until all cache lines in the specified *cache\_type(s)* are flushed. Depending on the size of the processor's caches, bus bandwidth and implementation characteristics, flushing the caches can take a long period of time, possibly delaying interrupt response times and potentially causing I/O devices to fail.

If this bit is a 1, external interrupts will be polled periodically and will exit the procedure if one is seen. If an unmasked external interrupt becomes pending, this procedure will return and allow the caller to service the interrupt before all cache lines in the specified *cache\_type(s)* are flushed.

c. Page 11-44, third and fifth paragraphs. Remove a few sentences related to the psr.ic and psr.i settings:

#### Old text:

This procedure makes one flush pass through all caches specified by *cache\_type* and all sets and associativities within those caches. The specified *cache\_type(s)* are ensured to be flushed only of cache lines resident in the caches prior to PAL\_CACHE\_FLUSH initially being called with the *progress\_indicator* set to 0.

This procedure must be called with PSR.i and PSR.ic set to zero to ensure external interrupts are not taken before this procedure begins to flush the cache(s) or while this procedure is terminating. PSR.i and PSR.ic must be zero regardless of the value of the *int* field.

#### New text:

This procedure makes one flush pass through all caches specified by *cache\_type* and all sets and associativities within those caches. The specified *cache\_type(s)* are ensured to be flushed only of cache lines resident in the caches prior to PAL\_CACHE\_FLUSH initially being called with the *progress\_indicator* set to 0.

d. Page 11-44, bullets listing contents of caches after this procedure exits. Add new bullets and remove references to PMI:

#### Old text:

Due to the following conditions, software cannot assume that when this procedure completes the entire flush pass that the specified  $cache\_type(s)$  are empty of all clean and/or modified cache lines.

- After an interruption, the flush pass resumes at the interruption point (specified by progress\_indicator). Due to execution of the interrupt handlers during the flush pass, the specified caches may contain new and possibly modified cache lines in sections of the caches already flushed.

- Prior prefetches initiated before this procedure is called are disabled and flushed from the cache. However, if a speculative translation exists in either the ITLB or DTLB, speculative instruction or data prefetch operation could immediately reload a non-modified cache line after it was flushed. To ensure prefetches do not occur, software must remove all speculative translation before calling this routines. Alternatively, software can disable the TLBs by setting PSR.it, PSR.dt, and PSR.rt to 0.

- The specified caches may also contain PAL firmware code cache entries required to flush the cache.

#### New text:

Due to the following conditions, software cannot assume that when this procedure completes the entire flush pass that the specified  $cache\_type(s)$  are empty of all clean and/or modified cache lines.

- After an interruption, the flush pass resumes at the interruption point (specified by *progress\_indicator*). Due to execution of the interrupt handlers during the flush pass, the specified caches may contain new and possibly modified cache lines in sections of the caches already flushed. The caller specifies if this procedure should poll for interrupts via the *int* bit of the *operation* parameter.

- Prior prefetches initiated before this procedure is called are disabled and flushed from the cache as described above. However, if a speculative translation exists in either the ITLB or DTLB, speculative instruction or data prefetch operation could immediately reload a non-modified cache line after it was flushed. To ensure prefetches do not occur, software must remove all speculative translation before calling this routines. Alternatively, software can disable the TLBs by setting PSR.it, PSR.dt, and PSR.rt to 0.

- The specified caches may contain PAL firmware code cache entries required to flush the cache.

- The specified caches may contain PAL and SAL PMI code if this call was made with psr.ic = 1 and a PMI interrupt is seen during the execution of the call.

- The specified caches may contain SAL or OS machine check or INIT code if these handlers run in a cacheable mode and a machine check or INIT event is seen.

- e. Page 11-45, remove PMI reference from the following paragraph:

#### Old text:

To ensure forward progress, PAL\_CACHE\_FLUSH advances through the cache flush sequence at least by one cache line before sampling for pending external interrupts or PMI. The amount of flushing that occurs before interrupts are polled will vary across implementations.

New text:

To ensure forward progress, PAL\_CACHE\_FLUSH advances through the cache flush sequence at least by one cache line before sampling for pending external interrupts. The amount of flushing that occurs before interrupts are polled will vary across implementations.

f. Page 11-45, *Status* and *vector* bullet descriptions. Remove PMI references by replacing bullets with the following:

Status

When the call returns a 1, it indicates that the call did not have any errors but is returning due to a pending unmasked external interrupt. To continue flushing the caches, the caller must call PAL\_CACHE\_FLUSH again with the value returned in the *progress\_indicator* return value.

When the call returns a 0, it indicates that the call completed without any errors. All cache lines that were present in the cache (when the most recent call to PAL\_CACHE\_FLUSH with a *progress\_indicator* of zero) are flushed and possibly invalidated. All intermediate calls must have used the proper *progress\_indicator*, otherwise behavior is undefined.

*vector* - If the return status is 1 and this procedure exited due to a pending unmasked external interrupt, this field returns the interrupt vector number. The external interrupt will have been removed. The interrupt is considered to be "in-service" and software must service this interrupt for the specified vector and then issue EOI. If the return status is not 1, the values returned is undefined.

#### 2. Volume 2: Non-speculative reference clarification

On p. 4-30, Section 4.4.6, just after the bullet list, add this sentence:

References that meet these requirements are termed non-speculative references. An instruction fetch which meets these requirements, but which takes an Instruction Debug fault or an External interrupt is still a non-speculative reference.

#### 3. Volume 2: RID and Preferred Page Size usage clarification

On p. 4-11, Section 4.1.2, Table 4-5, add the following footnote to the "Description" column for "ps" field:

1. For more details on the usage of this field, please refer to Section 4.1.6 "VHPT Hashing".

On p. 4-19, at the end of Section 4.1.6.2, replace item (1.) with:

1. Software must use only one preferred page size for each unique region identifier at any given time; otherwise, processor operation is undefined.

On p. 4-19, at the end of Section 4.1.6.2, add the following item (4.):

4. To reuse a region identifier with a different preferred page size, software must first ensure that the VHPT contains no insertable translations for that rid, purge all translations for that rid from all processors that may have used it, and then update the region register with the new preferred page size.

#### 4. Volume 2: VHPT read atomicity clarification

On p. 4-17, Section 4.1.5.4, for this paragraph and bullet list:

Atomic updates of long-format VHPT entries may be ensured by software as follows:

- Before making multiple non-atomic updates to a VHPT entry in memory, software is required to set its ti bit to one.

- After making multiple non-atomic updates to a VHPT entry in memory, software may clear its ti bit to zero to re-enable tag matches."

#### Change the first sentence to this:

For multi-processor systems, atomic updates of long-format VHPT entries may be ensured by software as follows:

#### Add this paragraph after the bullet list:

The updates to the VHPT entry in memory must be constrained to be observable only after the store that sets the it bit to one is observable. This can be accomplished with a mf instruction, or by performing the updates to the VHPT entry with release stores. Similarly, the clearing of the ti bit must be constrained to be observable only after all of the updates to the VHPT entry are observable. This can be accomplished with a mf instruction, or by performing the clear of the ti bit with a release store.

#### On p. 4-19, Section 4.1.7, for this paragraph:

VHPT walker references to the VHPT are performed at privilege level 0, regardless of the state of PSR.cpl. VHPT byte ordering is determined by the state of DCR.be. When DCR.be=1, VHPT walker references are performed using big-endian memory formats; otherwise, VHPT walker references are little-endian. The VHPT walker references the VHPT entry as a sequence of at least 8-byte atomic accesses. A long-format VHPT reference is matched against the data breakpoint registers as a 32-byte reference.

#### Delete the sentence:

The VHPT walker references the VHPT entry as a sequence of at least 8-byte atomic accesses.

#### On p. 4-20, Section 4.1.7, for this paragraph and bullet list:

The processor's VHPT walker is required to read and insert VHPT entries from memory atomically as follows:

- If the walker does not read an entry from memory atomically, and an update to part of the entry

that is being installed is detected, the walker must abort the insert and deliver an Instruction/

Data TLB Miss.

- If the walker reads an entry from memory atomically, and an update to part of the entry that is being installed is detected, the walker must either abort the insert and deliver an Instruction/ Data TLB Miss, or ignore the update and install the complete old entry.

- If the purge address range of a TLB purge operation (ptc.l, ptc.e, local or remote ptc.g or ptc.ga, ptr.i,or ptr.d) overlaps the virtual address the walker is attempting to insert, then the walker must either abort the insert and deliver an Instruction/Data TLB Miss, or delay the purge operation until after the walker either completes the insertion or aborts the walk.

#### Replace with this:

The processor's VHPT walker is required to read and insert VHPT entries from memory atomically (an 8-byte atomic read-and-insert for short format, and a 32-byte atomic read-and-insert for long format).

On p. 4-32, Section 4.4.7, the first paragraph begins as follows:

As described in Section 4.4.7, read-after-write, write-after-write, and write-after-read dependencies to the same memory location (memory dependency) are performed in program order by the processor.

Add a footnote to this sentence that reads as follows:

Although VHPT walks are performed somewhat asynchronously with respect to program execution, each walker VHPT read appears as though it were performed atomically, at some single point in the program order.

#### 5. Volume 2: IIP and WC flush clarifications

On p. 4-29, Section 4.4.5, replace the 4th paragraph:

Any IA-64 release operation (regardless of whether it references a page with a coalescing memory attribute), or any IA-64 fence type instruction, forces write-coalesced data to become visible prior to the instruction itself becoming visible. (See Table 4-14 for a list of release and fence instruction.) Any IA-32 serializing instruction, or access to an uncached memory type, forces write-coalesced data to become visible prior to itself becoming visible.

#### WITH:

Any IA-64 release operation (regardless of whether it references a page with a coalescing memory attribute), or any IA-64 fence type instruction, forces write-coalesced data to be flushed and made visible prior to the instruction itself becoming visible (See Table 4-14 for a list of release and fence instruction.) Any IA-32 serializing instruction, or access to an uncached memory type, forces write-coalesced data to become flushed and made visible prior to itself becoming visible.

On p. 8-36, Section 8.3, parameters. Replace the following:

IIP, IPSR, IIPA, IFS - are defined; refer to p. 8-1 for a detailed description.

#### WITH:

6.

IIP, IPSR, IIPA, IFS - are defined; refer to p. 8-1 for a detailed description.

**Note:** Please see Section 3.3.5.3 on page 3-18 for a further clarification of the IIP value for an unimplemented instruction address trap.

On p. 4-19, Section 4.4.5.3.1, Item 2 in the middle of the page:

Volume 1: Faults in Id.c that hits ALAT clarification

1. If the implementation chooses to leave the target register unchanged and one or more exception conditions related to the data access or translation of the check load occurs, the implementation may choose to either raise the highest-priority of these faults or ignore them all and continue execution. The faults that can be ignored are those related to data access and translation (Data

Nested TLB fault, Alternate Data TLB fault, VHPT Data fault, Data TLB fault, Data Page Not Present fault, Data NaT Page Consumption Fault, Data Key Miss fault, Data Key Permission fault, Data Access Rights fault, Data Dirty bit fault, Data Access Bit fault, Data Debug fault, Unaligned Data Reference fault, Unsupported Data Reference fault.

#### 7. Volume 2: IA-32 IBR/DBR match clarification

On p. 7-3, Table 7-1, change the "addr" field description as follows:

FROM:

For IA-32 instruction set references, IBR{31:0} are used in the match. For IA-32 memory references, addr{63:32} must be zero to match.

TO:

For IA-32 instruction references, IBR.addr{31:0} are used in the match and IBR.addr{63:32} must be zero to match.

On p. 7-3, Table 7-1, change the "mask" field description

FROM:

For IA-32 memory references, mask{63:32} are ignored

TO:

For IA-32 instruction references, IBR.mask{55:32} are ignored

On p. 7-5, remove this sentence from the last bullet:

The upper 32-bits of DBR addr field must be zero to detect IA-32 data memory references.

#### 8. Volume 3: IA-32 CPUID clarification

```

On p. 5-71, change

FROM:

BREAK;

ESAC;

TO:

BREAK;

DEFAULT: (* EAX > highest value recognized by CPUID *)

EAX <- Reserved, undefined;

EBX <- Reserved, undefined;

ECX <- Reserved, undefined;

EDX <- Reserved, undefined;

EDX <- Reserved, undefined;

EDX <- Reserved, undefined;

```

#### 9. Volume 2: Table A-5 class pr-writers-int

In Table A-5 on p. A-22, for the class pr-writers-int, add pr-and-writers and pr-or-writers to the Events/Instructions column.

10. Volume 2: Section 4.4.6.1 PAL\_MC\_DRAIN procedure only causes cache line writeback transactions to be forced onto the bus, and does not guarantee that they reached main memory

Change the last paragraph of Section 4.4.6.1on p. 4-32 to:

To further guarantee that any cache lines containing addresses belonging to page [X] have been evicted from all caches in the coherence domain and *forced onto the bus*, software must perform a PAL\_MC\_DRAIN operation on all processors in the coherence domain (via the IPI mechanism) after executing the above sequence. Note that this operation does not ensure that the cache lines have been written back to memory.

(In the paragraph above, the words "written back to memory" have been changed to "forced onto the bus" and a new sentence was added at the end.)

# **Documentation Changes**

#### 1. Volume 4: IBR and DBR addressing typographical errors

On p. 6-19, Section 6.2.4, in the middle of the page there are several equations. Replace all  $IBR_{i}$  addr to  $IBR_{i}$  addr:

```

Old text:

IBRmatch_{i} = match(IP,IBR_{i}.addr,IBR_{i}.mask,IBR_{i}.mask,IBR_{i}.plm

IBRmatch_{i} = match(IP,IBR_{2*i}).addr,IBR_{2*i}.mask,IBR_{2*i}.plm

*Note - () are changed to [], to make the equations consistent with others.

Old text:

IBRmatch_{i} = (IBR_{[2*i]+1}.plm[PSR.cpl])

and (AND_{b=50..0}((IBR_i.addr\{b\} \text{ and } IBR_{[2*i]+1}.mask\{b\}) = (IP\{b\} \text{ and } IBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=55..51}((IBR_i .addr\{b\} and IBR_{[2*i]+1}.mask\{b\}) = (IP\{50\} and IBR_{[2*i]+1}.mask[b]) = (IP\{50\} and IBR_{[

IBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=60..56}(IBR_i.addr\{b\} = IP\{50\}))

and (AND_{b=63..61}(IBR_{i}.addr\{b\} = IP\{b\}))

New text:

IBRmatch_i = (IBR_{\lceil 2*i \rceil+1}.plm[PSR.cpl])

and (AND_{b=50..0}((IBR_{\lceil 2^*i \rceil}.addr\{b\} \text{ and } IBR_{\lceil 2^*i \rceil+1}.mask\{b\}) = (IP\{b\} \text{ and } IBR_{\lceil 2^*i \rceil+1}.mask\{b\}) = (IP\{b\})

IBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=55..51}((IBR_{[2*i]}.addr\{b\} \text{ and } IBR_{[2*i]+1}.mask\{b\}) = (IP\{50\} \text{ and } IBR_{[2*i]+1}.mask[b]) = (IP\{50\} \text{ and } IBR_{[2*i]+1}.mask[b

IBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=60..56}(IBR_{[2*i]}.addr\{b\} = IP\{50\}))

and (AND_{b=63..61}(IBR_{[2*i]}.addr\{b\} = IP\{b\}))

On p. 6-21, Section 6.2.6, at the bottom of the page there are several equations. Replace all

DBR_{i}.addr to DBR_{[2*i]}.addr:

Old text:

DBRRangeMatch<sub>i</sub> =

(AND_{b=50..0}((DBR_i.addr\{b\} \text{ and } DBR_{[2*i]+1}.mask\{b\}) = (addr\{b\} \text{ and } DBR_{[2*i]+1}.mask[b]) = (a

DBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=55,51}((DBR_i.addr\{b\} \text{ and } DBR_{[2*i]+1}.mask\{b\}) = (addr\{50\} \text{ and } DBR_{[2*i]+1}.mask[b]) = (addr\{50\} \text{ and } DBR_{[2*i]+1}.mask[b]

DBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=60..56}(DBR_i.addr\{b\} = addr\{50\}))

```

2.

```

and (AND_{b=63..61}(DBR_i.addr\{b\}) = addr\{b\}))

New text:

DBRRangeMatch<sub>i</sub>=

(AND_{b=50..0}((DBR_{[2*i]}.addr\{b\} \text{ and } DBR_{[2*i]+1}.mask\{b\}) = (addr\{b\} \text{ and } DBR_{[2*i]+1}.mask[b]) = (addr\{b\} \text{ and } DBR_{[2*i]+1}.mask[b]

DBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=55..51}((DBR_{[2*i]}.addr\{b\} \text{ and } DBR_{[2*i]+1}.mask\{b\}) = (addr\{50\} \text{ and } DBR_{[2*i]+1}.mask\{b\}) = (addr\{50\})

DBR_{[2*i]+1}.mask\{b\})))

and (AND_{b=60...56}(DBR_{[2*i]}.addr\{b\} = addr\{50\}))

and (AND_{b=63..61}(DBR_{[2*i]}.addr\{b\}) = addr\{b\}))

Volume 3: Figure changes for extract, deposit, and alloc instructions

On p. 2-40, the extract instruction, change the text just before Figure 2-6

FROM:

The operation of extr t = r, 7, 50 is illustrated...

TO:

The operation of extr r_1 = r_3, 7, 50 is illustrated...

On p. 2-40, change the labels of the register values in Figure 2-6

FROM:

GR r, to: GR r<sub>3</sub>

AND FROM:

GR t, to: GR r<sub>1</sub>

On p. 2-37, the deposit instruction, change the text just before Figure 2-5

FROM:

The operation of dep t = s, r, 36, 16 is illustrated...

TO:

The operation of dep r_1 = r_2, r_3, 36, 16 is illustrated...

On p. 2-37, change the labels of the register values in Figure 2-5

FROM:

GR r, to: GR r3

AND FROM:

GR s, to: GR r<sub>2</sub>

AND FROM:

GR t, to: GR r<sub>1</sub>

On p. 2-37, after Figure 2-5, add this new paragraph:

The operation of dep.z r_1 = r_2, 36, 16 is illustrated in Figure XXX

```

Copy Figure 2-5 and the ParaAnchor paragraph that contains it.

Paste the copy just below the new paragraph.

In the copy, remove the label and register for  $GR r_3$  and for the two lines from that register pointing to the result register.

Add a "0" in the left and right portions of the GR  $r_1$  register, to show that these bits get 0. (For an example of a "0" in the target register in a figure, see the addp instruction, p. 2-4.)

On p. 2-5, the alloc instruction, Figure 2-2, add a double-arrow line below the sol line.

The left end of this new line should be aligned with the left end of the sol line.

The new line should be about half as long as the sol line.

Below the new line, create the text "sor", centered under the new line.

#### 3. Volume 2: RSE and PMC typographical errors

...(PMC[4]..PMC[p])

```

On p. 6-6, Section 6.4, Table 6-2, change the table entry for the CFM row, br.call column:

```

```

FROM:

CFM.sof = CFM.sol

TO:

CFM.sof -= CFM.sol

On pp. 7-7 and 7-8, Section 7.2.1, change "PMD" to "PMC" in three places:

The title of Figure 7-5

FROM:

...(PMC[4]..PMD[p])

TO:

...(PMC[4]..PMC[p])

In Figure 7-5, the left-hand side of the figure is a cell containing:

...(PMC[4]..PMD[p])"

TO:

...(PMC[4]..PMC[p])

In Table 7-4, change the title

FROM:

...(PMC[4]..PMD[p])

TO:

```

#### 4. Volume 2: DV table typographical error

On p. A-22, Appendix A, Section A.4, Table A-5 (Instruction Classes), add instruction 'setf' into list for class fp-writers.

\_\_\_\_\_

#### 5. Volume 2: ISR figure and wording changes

On p. 8-5 of Volume 2, change the Unsupported Data Reference fault row in Table 8-2 so that the r column reads "r", and the w column reads "w".

On p. 8-26 of Volume 2, change the second ISR figure on the General Exception vector page to show sp as always 0.

On p. 8-33 of Volume 2, change the ISR figure on the Unsupported Data Reference vector page so that bit 34 reads "r", and bit 33 reads "w".

On p. 8-33 of Volume 2, add the following statement below the ISR figure on the Unsupported Data Reference vector page:

For ldfe and stfe instructions, the processor may optionally set both ISR.r and ISR.w to 1, although this is not recommended.

# 6. Volume 2: ISR figure change on the Lower-privilege Transfer Trap vector page (new p. 8-36 of Volume 2)

#### Name Lower-privilege Transfer Trap vector (0x5e00)

Cause Two trapping conditions transfer control to this vector:

- An attempt is made to execute an instruction at an unimplemented address, resulting in an Unimplemented Instruction Address trap. See "Unimplemented Address Bits" on p. 4-24.

- The PSR.lp bit is 1, and a branch lowers the privilege level.

IA-32 instructions can not raise this trap.

Interruptions on this vector:

Unimplemented Instruction Address trap Lower-privilege Transfer trap

Parameters

IIP, IPSR, IIPA, IFS – are defined; refer to p. 8-1 for a detailed description.

ISR – The ISR.ei bits are set to indicate which instruction caused the exception. The ISR.code contains a bit vector (see Table 8-3 on p. 8-5) for all traps which occurred in the just-executed instruction. The defined ISR bits are specified below.

If the trap is due to an Unimplemented Instruction Address trap:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15           | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    | (  | )  |    |    |    | 0  |    |    |    |    |    |    | 0  | fp trap code |    |    |    |    |    |    |    |    | 0  | 1  | ss | tb | lр | fp |    |

| 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 | 47           | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|    |    |    |    |    |    |    |    |    | (  | )  |    |    |    |    |    |              |    |    |    | 0  | е  | ėi | 0  | ni | ir | 0  | 0  | 0  | 0  | 0  | 0  |

If the trap is due to a Lower-Privilege Transfer trap:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    | (  | )  |    |    |    |    |    |    | (  | )  |    |    |    |    |    |    |    | 0  |    |    |    |    | 0  | 0  | 0  | ss | tb | 1  | 0  |

| 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|    |    |    |    |    |    |    |    |    | (  | )  |    |    |    |    |    |    |    |    |    | 0  | e  | i  | 0  | ni | ir | 0  | 0  | 0  | 0  | 0  | 0  |

Notes

The Unimplemented Instruction Address trap can be the result of an inline instruction fetch, a taken or not-taken branch or an rfi. The lower privilege transfer trap is only taken on a branch demotion, and not an rfi return.

#### 7. Volume 4: Figure 6-17 and Figure 6-19 bit typo

In Figure 6-17, Instruction Event Address Configuration Register (PMC[10]) and Figure 6-19, Data Event Address Configuration Register (PMC[11]) on p. 6-22 and p. 6-25 respectively, the second 'ignored' field (bits 8-15) from the right is showing 7 bits where it should be 8 bits.

#### 8. Volume 4: Chapter 6 the eight stall and flush reasons

On p. 6-19, replace the text before Section 6.1.2, Profiling with the following:

The Itanium processor cycle accounting monitors account for all major single and multi-cycle stall and flush conditions. Overlapping stall and flush conditions are prioritized in reverse pipeline order (i.e. delays that occur later in the pipe and that overlap with earlier stage delays are reported as being caused later in the pipeline). The eight stall and flush reasons are prioritized in the following order:

- 1. Back-end Flush Cycles: cycles lost due to branch mispredictions, ALAT flushes, serialization flushes, failed control speculation flushes, MMU-IEU bypasses and other exceptions.

- Data Access Cycles: cycles lost when instructions stall waiting for their source operands from the memory subsystem, and when memory flushes arise (L1D way mispredictions, DTC flushes).

- 3. Scoreboard Dependency Cycles: cycles lost when instructions stall waiting for their source operands from non-load instructions; this includes FP-related flushes.

- 4. RSE Active Cycles: stalls due to register stack spills to and fills from the backing store in memory.

- 5. Issue Limit Cycles: dispersal breaks due to stops, port over-subscription or asymmetries.

- 6. Instruction Access Cycles: instruction fetch stalls due to L1I or ITLB misses.

- 7. Taken Branch Cycles: bubbles incurred on correct taken branch predictions.

- 8. Unstalled Pipeline Cycles: cycles due to the inherent execution of the program.

Four of the eight categories (1, 2, 3, 6) are directly measurable as Itanium processor events. The other four categories (4, 5, 7, 8) are not measured directly. Instead, four combined categories are available as the Itanium processor events: pipeline flush cycles (1+7), memory cycles (2+4), dependency cycles (3+5), and unstalled back-end cycles (6+8). For details, refer to Section 7.4, "Cycle Accounting Events".

# **Performance Monitor Events**

7

This chapter describes the architectural and microarchitectural events on the Itanium processor whose occurrences are countable through the performance monitoring mechanisms described earlier in Chapter 6. The earlier sections of this chapter aim to provide a high-level view of the event list, grouping logically related events together. Computation (either directly by a counter in hardware, or indirectly as a "derived" event) of common performance metrics is also discussed. Each directly measurable event is then described in greater detail in the alphabetized list of all processor events in Section 7.8, "Performance Monitor Event List".

## 7.1 Categorization of Events

Performance related events are grouped into the following categories:

- Basic Events: clock cycles, retired instructions (Section 7.2)

- Instruction Execution: instruction decode, issue and execution, data and control speculation, and memory operations (Section 7.3)

- Cycle Accounting Events: stall and execution cycle breakdowns (Section 7.4)

- Branch Events: branch prediction (Section 7.5)

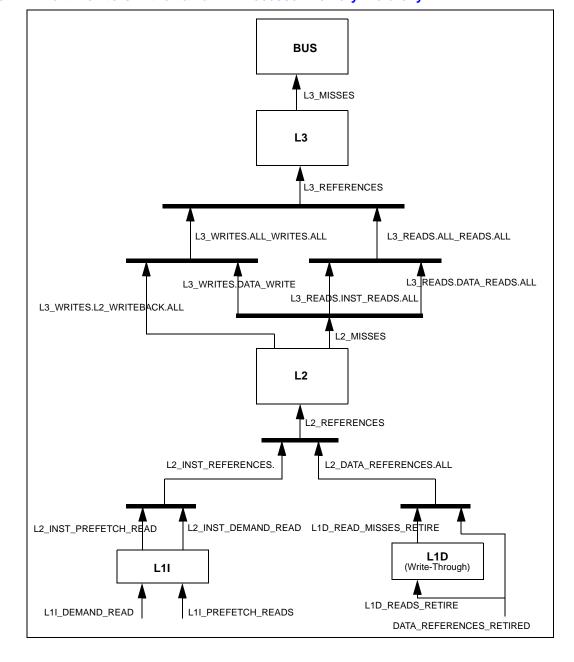

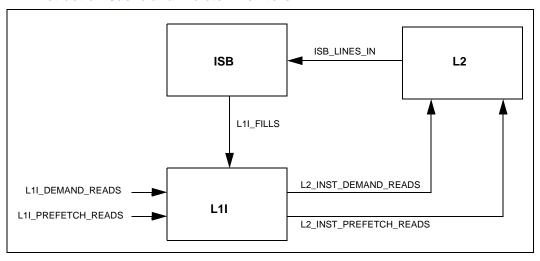

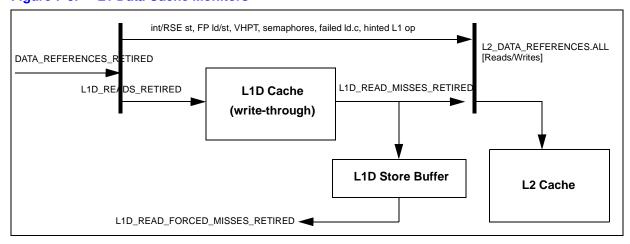

- Memory Hierarchy: instruction and data caches (Section 7.6)

- System Events: operating system monitors, instruction and data TLBs (Section 7.7)

Each section listed above includes a table of all events (both directly measured and derived) in that category. Directly measurable events often use the PMC.umask field (See Table 6-7 in Chapter 6) to measure a certain variant of the event in question. Symbolic event names for such events (e.g. ALAT\_REPLACEMENT.ALL) include a period to indicate use of the umask, specified by 4 bits in the detailed event description (x's are for don't-cares). Derived events are computable from directly measured events and include a ".d" suffix in their symbolic event names. Formulas to compute relevant derived events also appear in each section. Derived events are not, however, discussed in the systematic event listing in Section 7.8.

The tables in the subsequent sections define events by specifying three attributes: symbolic event name, a brief event title and a reference to the detailed event description page. Derived events are not listed in the detailed event description pages and hence lack the appropriate reference.

## 7.2 Basic Events

Table 7-1 summarizes four basic execution monitors. The CPU\_CYCLES event can be used to break out separate or combined IA-64 or IA-32 cycle counts (by constraining the PMC/PMD based on the currently executing instruction set). The IA-64 retired instruction count (IA64\_INST\_RETIRED) includes predicated true and false instructions, and nops, but excludes RSE operations.

Table 7-1. IA-64 and IA-32 Instruction Set Execution and Retirement Monitors

| Execution Monitors | Title                          | Page |

|--------------------|--------------------------------|------|

| CPU_CYCLES         | CPU Cycles                     | 7-67 |

| IA64_INST_RETIRED  | Retired IA-64 Instructions     | 7-71 |

| IA32_INST_RETIRED  | Retired IA-32 Instructions     | 7-71 |

| ISA_TRANSITIONS    | IA-64 to IA-32 ISA Transitions | 7-74 |

Table 7-2 defines IPC and average instructions/cycles per ISA transition metrics.

Table 7-2. IA-64 and IA-32 Instruction Set Execution and Retirement Performance Metrics

| Performance Metric                    | Performance Monitor Equation               |

|---------------------------------------|--------------------------------------------|

| IA-64 Instruction per Cycle           | IA64_INST_RETIRED / CPU_CYCLES[IA-64 only] |

| IA-32 Instruction per Cycle           | IA32_INST_RETIRED / CPU_CYCLES[IA-32 only] |

| Average IA-64 Instructions/Transition | IA64_INST_RETIRED/ (ISA_TRANSITIONS*2)     |

| Average IA-32 Instructions/Transition | IA32_INST_RETIRED/ (ISA_TRANSITIONS*2)     |

| Average IA-64 Cycles/Transition       | CPU_CYCLES[IA64]/ (ISA_TRANSITIONS*2)      |

| Average IA-32 Cycles/Transition       | CPU_CYCLES[IA32]/ (ISA_TRANSITIONS*2)      |

## 7.3 Instruction Execution

This section describes events related to instruction issue and retirement (Table 7-3, Table 7-4) multi-media and FP (Table 7-5), data and control speculation (Table 7-7), as well as memory monitors (Table 7-9).

**Table 7-3. Instruction Issue and Retirement Events**

| Decode, Issue, Retirement Monitors | Description                                | Page |

|------------------------------------|--------------------------------------------|------|

| INST_DISPERSED                     | Instructions Dispersed                     | 7-73 |

| EXPL_STOPS_DISPERSED               | Explicit Stops Dispersed                   | 7-70 |

| ALL_STOPS_DISPERSED                | Implicit and Explicit Stops Dispersed      | 7-45 |

| IA64_TAGGED_INST_RETIRED           | Retired Tagged IA-64 Instructions          | 7-72 |

| NOPS_RETIRED                       | Retired Nop Instructions                   | 7-85 |

| PREDICATE_SQUASHED_RETIRED         | Instructions Squashed Due to Predicate Off | 7-86 |

| RSE_REFERENCES_RETIRED             | RSE Accesses                               | 7-87 |

| RSE_LOADS_RETIRED                  | RSE Load Accesses                          | 7-86 |

Table 7-4. Instruction Issue and Retirement Events (Derived)

| Decode, Issue, Retirement<br>Monitors | Description        | Performance Monitor Equation                  |

|---------------------------------------|--------------------|-----------------------------------------------|

| RSE_STORES_RETIRED.d                  | RSE Store Accesses | RSE_REFERENCES_RETIRED -<br>RSE_LOADS_RETIRED |

Instruction cache lines are delivered to the execution core and are dispersed to the Itanium processor functional units. The number of dispersed instructions (INST\_DISPERSED) on every cycle depends on the stops in the instruction stream (EXPL\_STOPS\_DISPERSED) as well as functional unit availability. Resource limitations and branch bundles (regardless of prediction) force a break in the instruction dispersal. Therefore, they are known as implicit stops, and can be computed as ALL\_STOPS\_DISPERSED - EXPL\_STOPS\_DISPERSED.

Retired instruction counts (IA64\_TAGGED\_INST\_RETIRED, NOPS\_RETIRED) are based on tag information specified by the address range check and opcode match facilities. The tagged retired instruction counts include predicated off instructions. A separate event (PREDICATE\_SQUASHED\_RETIRED) is provided to count predicated off instructions. RSE\_REFERENCES\_RETIRED counts the number of retired RSE operations.

There are two ways to count the total number of retired IA-64 instructions. Either the untagged IA64\_INST\_RETIRED event can be used or the IA64\_TAGGED\_INST\_RETIRED event can be used by setting up the PMC<sub>8</sub> opcode match register to its don't care setting.

The FP monitors listed in Table 7-5 (FP\_SIR\_FLUSH, FP\_FLUSH\_TO\_ZERO) capture dynamic information about pipeline flushes and flush-to-zero occurrences due to floating-point operations. FP\_OPS\_RETIRED.d is a derived event that counts the number of retired FP operations.

#### **Table 7-5. Floating-point Execution Monitors**

| Floating-Point Monitors | Description               | Page |

|-------------------------|---------------------------|------|

| FP_FLUSH_TO_ZERO        | FP Result Flushed to Zero | 7-70 |

| FP_SIR_FLUSH            | FP SIR Flushes            | 7-71 |

#### **Table 7-6. Floating-point Execution Monitors (Derived)**

| Floating-Point Monitors | Description | Performance Monitor Equation |

|-------------------------|-------------|------------------------------|

| FP_OPS_RETIRED.d        | •           | (4 * FP_OPS_RETIRED_HI) +    |

|                         | Retired     | FP_OPS_RETIRED_LO            |

As Table 7-7 describes, monitors for control and data speculation capture dynamic run-time information: the number of failed chk.s instructions (INST\_FAILED\_CHKS\_RETIRED.ALL), the number of advanced load checks and check loads (ALAT\_INST\_CHKA\_LDC.ALL) and failed advanced load checks and check loads (ALAT\_INST\_FAILED\_CHKA\_LDC.ALL) as seen by the ALAT. The number of retired chk.s instructions is monitored by the IA64\_TAGGED\_INST\_RETIRED event with the appropriate opcode mask. Since the Itanium processor ALAT is updated by operations on mispredicted branch paths the number of advanced load checks and check loads needs an explicit event (ALAT\_INST\_CHKA\_LDC.ALL). Finally, the

ALAT REPLACEMENT.ALL event can be used to monitor ALAT overflows.

**Table 7-7. Control and Data Speculation Monitors**

| Control and Data Speculation<br>Monitors | Description                                 | Page |

|------------------------------------------|---------------------------------------------|------|

| INST_FAILED_CHKS_RETIRED.ALL             | Failed Speculative Check Loads              | 7-73 |

| ALAT_INST_CHKA_LDC.ALL                   | Advanced Load Checks and Check Loads        | 7-44 |

| ALAT_INST_FAILED_CHKA_LDC.ALL            | Failed Advanced Load Checks and Check Loads | 7-45 |

| ALAT_REPLACEMENT.ALL                     | ALAT Entries Replaced by Any Instruction    | 7-43 |

Using an instruction type unit mask the four control and data speculation events can be constrained to monitor integer, FP or all speculative instructions. With the Itanium processor speculation monitors, the performance metrics described in Table 7-8 can be computed.

Performance Monitor Events 7-29

Table 7-8. Control/Data Speculation Performance Metrics

| Performance Metric             | Performance Monitor Equation                                                                                                                                           |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Speculation Miss Ratio | INST_FAILED_CHKS_RETIRED.ALL / (IA64_TAGGED_INST_RETIRED[chk.s]-PREDICATE_SQUASHED_R ETIRED[chk.s])                                                                    |

| Data Speculation Miss Ratio    | ALAT_INST_FAILED_CHKA_LDC.ALL / ALAT_INST_CHKA_LDC.ALL                                                                                                                 |

| ALAT Capacity Miss Ratio       | ALAT_REPLACEMENT.ALL/ IA64_TAGGED_INST_RETIRED[Id.a,Id.sa,Id.c.nc, Idf.a, Idf.sa, Idf.c.nc]-PREDICATE_SQUASHED_RETIRED[Id.a, Id.sa, Id.c.nc, Idf.a, Idf.sa, Idf.c.nc]) |