# **UNIX System V Application Binary Interface**

September 2000

Document Number: 245370-002

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IA-64 processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's website at http://developer.intel.com/design/litcentr.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

# intel。 Contents

| 1 | Introd | luction    |                                                 | 1-1 |

|---|--------|------------|-------------------------------------------------|-----|

|   | 1.1    | The Inte   | el IA-64 Architecture and the System V ABI      | 1-1 |

|   | 1.2    | How to     | Use the System V ABI for Intel IA-64 Processors | 1-1 |

|   | 1.3    | Evolution  | on of the ABI Specification                     | 1-2 |

|   | 1.4    | Addition   | nal Documents                                   | 1-2 |

| 2 | Softw  | are Instal | lation                                          | 2-1 |

| 3 | Low-l  | evel Syste | em Information                                  | 3-1 |

|   | 3.1    |            | ction                                           |     |

|   | 3.2    | Machine    | e Interface                                     | 3-1 |

|   |        | 3.2.1      | Fundamental Types                               | 3-1 |

|   | 3.3    | Operati    | ng System Interface                             |     |

|   |        | 3.3.1      | Exception Interface                             |     |

|   |        | 3.3.2      | Signal Delivery                                 | 3-4 |

|   |        | 3.3.3      | Signal Handler Interface                        | 3-5 |

|   |        | 3.3.4      | Debugging Support                               | 3-6 |

|   |        | 3.3.5      | Process Startup                                 | 3-6 |

| 4 | Objec  | t Files    | ·                                               | 4-1 |

| • | 4.1    |            | ader                                            |     |

|   |        | 4.1.1      | Machine Information                             |     |

|   | 4.2    | Section    | S                                               |     |

|   |        | 4.2.1      | Section Types                                   |     |

|   |        | 4.2.2      | Section Attribute Flags                         |     |

|   |        | 4.2.3      | Special Sections                                |     |

|   |        | 4.2.4      | Architecture Extensions                         |     |

|   | 4.3    | Relocat    | ions                                            |     |

|   |        | 4.3.1      | Relocation Types                                |     |

| 5 | Progr  | am Loadi   | ng and Dynamic Linking                          | 5-1 |

|   | 5.1    |            | n Header                                        |     |

|   | 5.2    | Progran    | n Loading                                       | 5-1 |

|   |        | 5.2.1      | Linktime and Runtime Addresses                  |     |

|   |        | 5.2.2      | Initializations                                 | 5-4 |

|   | 5.3    | Dynami     | c Linking                                       | 5-4 |

|   |        | 5.3.1      | Dynamic Linker                                  | 5-4 |

|   |        | 5.3.2      | Dynamic Section                                 | 5-5 |

|   |        | 5.3.3      | Shared Object Dependencies                      | 5-5 |

|   |        | 5.3.4      | Global Offset Table                             | 5-6 |

|   |        | 5.3.5      | Function Addresses                              | 5-6 |

|   |        | 5.3.6      | Procedure Linkage Table                         | 5-7 |

|   |        | 5.3.7      | Initialization and Termination Functions        |     |

| 6 | Libraı | ries       |                                                 | 6-1 |

|   | 6.1    | Unwind     | Library Interface                               |     |

|   |        | 6.1.1      | Exception Handler Framework                     |     |

|   |        | 6.1.2      | •                                               |     |

# intط

|     |              | 6.1.3      | Throwing an Exception                                        | .6-5 |

|-----|--------------|------------|--------------------------------------------------------------|------|

|     |              | 6.1.4      | Exception Object Management                                  | .6-7 |

|     |              | 6.1.5      | Context Management                                           | .6-7 |

|     |              | 6.1.6      | Personality Routine                                          | .6-9 |

| 7   | Miscel       | laneous    |                                                              | 7-1  |

|     | 7.1          | Introduct  | tion                                                         | 7-1  |

|     | 7.2          | Develop    | ment Environment                                             | 7-1  |

|     |              | 7.2.1      | Pre-defined Preprocessor Symbols                             | .7-1 |

|     |              | 7.2.2      | Pre-defined Preprocessor Assertions                          | 7-1  |

|     |              | 7.2.3      | Compiler Pragmas                                             | .7-2 |

|     | 7.3          | ILP32 Al   | 3I                                                           | .7-3 |

|     |              | 7.3.1      | Objectives of the 32-bit Little-endian Runtime Architecture. | .7-3 |

|     |              | 7.3.2      | Changes from the 64-bit Software Conventions                 | .7-3 |

|     |              | 7.3.3      | Addressing and Protection                                    | .7-4 |

|     |              | 7.3.4      | Data Allocation                                              | .7-4 |

|     |              | 7.3.5      | Local Memory Stack Variables                                 | 7-4  |

|     |              | 7.3.6      | Parameter Passing                                            | .7-4 |

|     | 7.4          | Synchro    | nization Primitives                                          | .7-4 |

|     |              | 7.4.1      | Atomic Fetch-and-op Operations                               | .7-5 |

|     |              | 7.4.2      | Atomic Op-and-fetch Operations                               | .7-6 |

|     |              | 7.4.3      | Atomic Compare-and-swap Operation                            | .7-6 |

|     |              | 7.4.4      | Atomic Synchronize Operation                                 | .7-6 |

|     |              | 7.4.5      | Atomic Lock-test-and-set Operation                           | .7-7 |

|     |              | 7.4.6      | Atomic Lock_Release Operation                                | .7-7 |

|     |              |            |                                                              |      |

|     |              |            |                                                              |      |

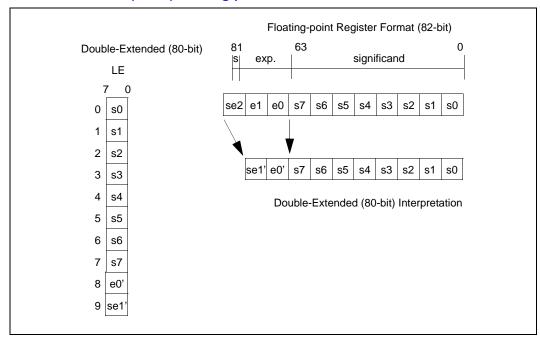

| 3-1 | Double       | -evtender  | d (80-bit) Floating-point Formats                            | 3-2  |

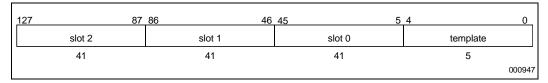

| 4-1 |              |            | e Layout                                                     |      |

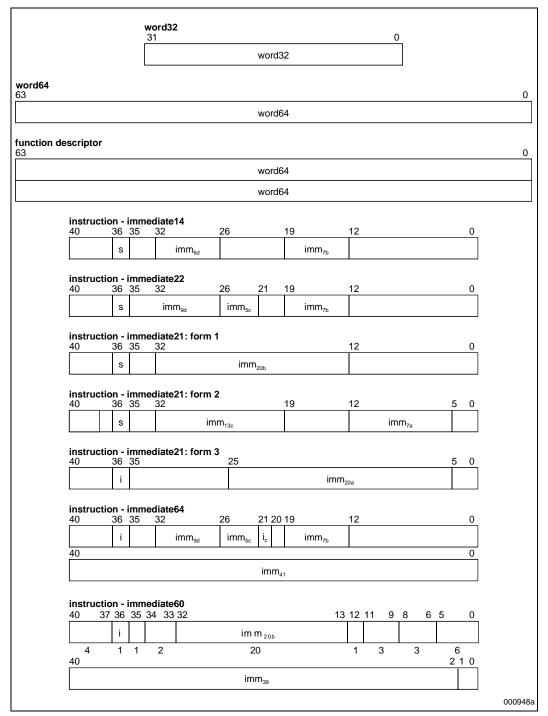

| 4-2 |              |            | ds                                                           |      |

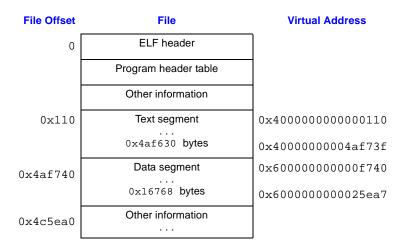

| 5-1 |              |            | able File                                                    |      |

| 5-2 |              |            | m Header Segments                                            |      |

| 5-3 |              | -          | s Image Segments                                             |      |

| 5-4 | Proced       | dure Linka | ge Table Sample Entries                                      | .5-8 |

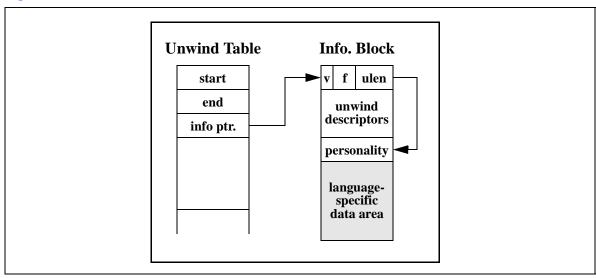

| C 1 | Unwind Table |            |                                                              |      |

**Figures**

# int<sub>e</sub>l<sub>®</sub>

# **Tables**

| 3-1 | Additional Fundamental Data Types                  | 3-1  |

|-----|----------------------------------------------------|------|

| 3-2 | Hardware Exceptions and Signals                    |      |

| 3-3 | Floating-point Exceptions                          |      |

| 3-4 | Standard Signal Delivery                           |      |

| 3-5 | Signal Delivery – Additional Details for IA-64     |      |

| 4-1 | Operating System Identification, e_ident[EI_OSABI] | 4-2  |

| 4-2 | IA-64 Processor-Specific Flags, e_flags            |      |

| 4-3 | Section Types, sh_type                             | 4-3  |

| 4-4 | Section Attribute Flags, sh_flags                  | 4-4  |

| 4-5 | Special Sections                                   | 4-5  |

| 4-6 | Relocation Offset Instruction Slot Encoding        | 4-7  |

| 4-7 | IA-64 Relocation Types                             | 4-11 |

| 5-1 | Program Header Types, p_type                       |      |

| 5-2 | Program Header Flags, p_flags                      | 5-1  |

| 5-3 | Example Runtime Address Calculation                | 5-4  |

| 5-4 | Dynamic Linker Location                            | 5-5  |

| 5-5 | Dynamic Section Tag, d_tag                         | 5-5  |

| 5-6 | Default Shared Object Location                     | 5-6  |

|     |                                                    |      |

# int<sub>e</sub>l<sub>®</sub>

Introduction 1

# 1.1 The Intel IA-64 Architecture and the System V ABI

The System V Application Binary Interface defines a system interface for compiled application programs. Its purpose is to establish a standard binary interface for application programs on systems that implement the interfaces defined in the X/Open Common Application Environment Specification, Issue 4.2 (also known as the "Single UNIX Specification") and the System V Interface Definition, Issue 4. This includes, but is not limited to, systems that have implemented UNIX System V, Release 4.

This document is the result of consensus among operating system vendors intending to provide UNIX and UNIX workalike operating systems on the IA-64 architecture. The vendors participating in this effort include Intel, Sun Microsystems, SCO, IBM, SGI, Cygnus Solutions, VA Linux Systems, HP, and Compaq. This specification builds upon the definitions of the *System V ABI* and supplies those aspects of the *System V ABI* which are indicated as being processor-specific. In combination with the *System V ABI* and the documents included by reference by this specification, constitutes a specification for compiler, linker and object model compatibility for implementations of UNIX and UNIX workalike operating systems on systems that utilize the processor architecture of Intel IA-64 microprocessors.

# 1.2 How to Use the System V ABI for Intel IA-64 Processors

The IA-64 architecture supports a 64 bit instruction set and also provides compatibility with the IA-32 instruction set. Binaries using the IA-64 instruction set may program to either a 32-bit model, in which the C data types int and long and all pointer types are 32-bit objects (*ILP32*); or to a 64-bit model, in which the C int type is 32-bits but the C long type and all pointer types are 64-bit objects (*LP64*). This specification describes information needed to construct, link and execute binaries using the LP64 programming model. In addition, the IA-64 architecture allows both big-endian (most-significant byte first) and little-endian (least-significant byte first) encoding. This specification may be used to instantiate a big-endian and/or a little-endian ABI.

This specification does not fully describe the ILP32 programming model. Since some vendors will support this model, some non-binding considerations will be covered in Chapter 7. The specification also does not describe the compatibility mode for IA-32 instruction set binaries. That mode is described by a separate ABI document.

This document is a supplement to the generic *System V ABI* and contains information referenced in the generic specification that may differ when System V is implemented on different processors. Therefore, the generic ABI is the prime reference document, and this supplement is provided to fill gaps in that specification.

As with the System V ABI, this specification references other available documents, especially the IA-64 Processor Programmer's Reference Manual, the Intel IA-64 Software Conventions and Runtime Architecture Guide and the 32-Bit Little-Endian IA-64 Software Conventions Addendum for IA-64 UNIX. All the information referenced by this supplement should be considered part of this specification unless otherwise noted, and just as binding as the requirements and data explicitly included here.

# 1.3 Evolution of the ABI Specification

This specification will evolve over time to address new technology and market requirements, and will be reissued periodically. Each new edition of the specification is likely to contain extensions and additions that will increase the potential capabilities of applications that are written to conform to the ABI.

# 1.4 Additional Documents

The following documents available at developer.intel.com web site (http://developer.intel.com/design/ia-64/devinfo.htm) are included by reference into this specification:

- The IA-The IA-64 Architecture Software Developer's Manual Vol. 1 rev 1.1: Application Architecture

- The IA-64 Architecture Software Developer's Manual Vol. 2 rev 1.1: System Architecture

- The IA-64 Architecture Software Developer's Manual Vol. 3 rev 1.1: Instruction Set Reference

- IA-64 Architecture Software Developer's Manual Vol. 4 rev 1.1: Itanium processor Programmer's Guide

- Intel® IA-64 Architecture Software Developer's Manual Specification Update

- IA-64 Software Conventions and Runtime Architecture Guide, Order Number 24538-001

- IA-64 Assembly Language Reference Guide, Order Number 248801-002.

1-2 Introduction

# Software Installation

2

For future use.

# int<sub>e</sub>l<sub>®</sub>

2-2 Software Installation

# Low-level System Information

# 3.1 Introduction

The *System V ABI* leaves processor-specific low-level system information to the *Processor Supplement* (this document). The majority of this required information is documented in the Intel *IA-64 Software Conventions and Runtime Architecture Guide* ("Conventions"), which is operating-system independent. Only information that is specific to implementing the ABI on the IA-64 architecture will be described here.

Object files (relocatable files, executable files and shared object files) that are supplied as part of an ABI-conforming application must use position-independent code as described in Chapter 12 of *Conventions*.

# 3.2 Machine Interface

# 3.2.1 Fundamental Types

The following additional C language scalar data types are required. long long is an integral type, while long double is a floating-point type.

**Table 3-1. Additional Fundamental Data Types**

| Data Model | C Type                          | Size | Align | Hardware Representation               |

|------------|---------------------------------|------|-------|---------------------------------------|

| ILP32      | long long<br>unsigned long long | 8    | 4     | Signed doubleword Unsigned doubleword |

| LP64       | long long<br>unsigned long long | 8    | 8     | Signed doubleword Unsigned doubleword |

| ILP32      | long double                     | 12   | 4     | IEEE Double-Extended floating point   |

| LP64       | long double                     | 16   | 16    | IEEE Double-Extended floating point   |

**NOTE:** long double in the LP64 model is allocated 16 bytes (128 bits) of storage but uses the 80-bit extended double format internally.

Figure 3-1. Double-extended (80-bit) Floating-point Formats

# 3.3 Operating System Interface

# 3.3.1 Exception Interface

As the IA-64 architecture manuals describe, the processor changes mode to handle *exceptions*. Some exceptions can be explicitly generated by a process. This section specifies those exception types with defined behavior. Table 3-2 shows the signal number (si\_signo) and the code (si\_code) values that will be delivered for each type of hardware exception that has an effect on program execution.

**Table 3-2. Hardware Exceptions and Signals**

| Type of Exception         | si_signo | si_code       | Notes |

|---------------------------|----------|---------------|-------|

| TLB faults                | SIGSEGV  | SEGV_MAPERR   | (1)   |

| Access faults             | SIGSEGV  | SEGV_ACCERR   |       |

| Privilege violations      | SIGILL   | ILL_PRVOPC    |       |

| Register NaT consumption  | SIGILL   | ILL_PRVREG    |       |

| NaT page consumption      | SIGSEGV  | ILL_REGNAT    |       |

| Speculative operation     | None     | SEGV_MAPERR   | (2)   |

| Unaligned data            | SIGBUS   | BUS_ADRALN    | (3)   |

| Floating-point exceptions | SIGFPE   | see Table 3-3 |       |

| Illegal instructions      | SIGILL   | ILL_ILLOPC    |       |

Table 3-2. Hardware Exceptions and Signals (Cont'd)

| Break 0 (unknown error)               | SIGILL    | ILL_ILLOPC   |     |

|---------------------------------------|-----------|--------------|-----|

| Break 1 (integer divide by zero)      | SIGFPE    | FPE_INTDIV   |     |

| Break 2 (integer overflow)            | SIGFPE    | FPE_INTOVF   |     |

| Break 3 (range check/bounds check)    | SIGFPE    | FPE_FLTSUB   |     |

| Break 4 (null pointer dereference)    | SIGSEGV   | SEGV_MAPERR  |     |

| Break 5 (misaligned data)             | SIGBUS    | BUS_ADRALN   |     |

| Break 6 (decimal overflow)            | SIGFPE    | FPE_DECOVF   |     |

| Break 7 (decimal divide by zero)      | SIGFPE    | FPE_DECDIV   |     |

| Break 8 (packed decimal error)        | SIGFPE    | FPE_DECERR   |     |

| Break 9 (invalid ASCII digit)         | SIGFPE    | FPE_INVASC   |     |

| Break 10 (invalid decimal digit)      | SIGFPE    | FPE_INVDEC   |     |

| Break 11 (paragraph stack overflow)   | SIGSEGV   | SEGV_PSTKOVF |     |

| Break 12-0x03ffff (reserved)          | undefined |              |     |

| Break 0x040000-0x07ffff (application) | SIGILL    | ILL_BREAK    |     |

| Break 0x080000-0x0fffff (debugger)    | SIGTRAP   | TRAP_BRKPT   | (4) |

| Break 0x100000-0x1fffff (reserved)    | undefined |              |     |

#### Notes:

- 1. TLB faults are first serviced by the system to determine if the attempted access was to a page to which the process has access.

- A signal is delivered to the application only if the attempted access is determined to be invalid.

2. Speculative operation faults are the result of a speculative check or floating-point check flags operation. The system services this fault, and emulates the instruction as a pc-relative branch when the fault is taken.

- 3. The system may emulate unaligned data references, possibly depending on flags set in the executable object file or on the executable's setting of the PSR.ac bit. If it does, no signal is delivered. Applications that rely on such behavior are not ABI con-

- 4. If the process is being controlled by a debugger, these faults generate debugger events, and do not cause a signal to be delivered to the process.

Table 3-3 details the possible reasons for a SIGFPE signal caused by a floating-point exception:

**Table 3-3. Floating-point Exceptions**

| Code       | Reason                           |

|------------|----------------------------------|

| FPE_FLTDIV | floating-point divide by zero    |

| FPE_FLTOVF | floating-point overflow          |

| FPE_FLTUND | floating-point underflow         |

| FPE_FLTRES | floating-point inexact result    |

| FPE_FLTINV | invalid floating-point operation |

| FPE_FLTSUB | subscript out of range           |

# 3.3.2 Signal Delivery

The *Single UNIX Specification* defines information that is made available in the siginfo\_t structure for specific signals. That information is reproduced, for informational purposes, in Table 3-4. Table 3-5 lists additional information delivered for specific signals on IA-64.

**Table 3-4. Standard Signal Delivery**

| Signal            | Member                                        | Value                                                                                    |

|-------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|

| SIGILL<br>SIGFPE  | void * si_addr                                | Address of faulting instruction                                                          |

| SIGSEGV<br>SIGBUS | void * si_addr                                | Address of faulting memory reference                                                     |

| SIGCHLD           | pid_t si_pid<br>int si_status<br>uid_t si_uid | Child process ID  Exit value or signal  Real user ID of the process that sent the signal |

| SIGPOLL           | long si_band                                  | Band event for POLL_IN, POLL_OUT or POLL_MSG                                             |

Table 3-5. Signal Delivery – Additional Details for IA-64

| Signal  | Member                       | Value                                                               |

|---------|------------------------------|---------------------------------------------------------------------|

| SIGTRAP | void * si_addr<br>int si_imm | Address of faulting instruction break instruction immediate operand |

| SIGILL  | int si_imm                   | break instruction immediate operand (forILL_BREAK)                  |

When a signal handler is installed, the application passes a function pointer to the system. As defined by *Conventions*, a function pointer points to a function descriptor, which contains the handler's entry point address and its global pointer register (gp) value. The implementation must be aware of the structure of the function descriptor in order to deliver a signal correctly.

When delivering a signal, the implementation must do the following:

- 1. Build the signal info and signal context records at the top of the user stack. If SA\_SIGINFO was not set when installing the signal handler, these records are not required.

- 2. Create a new 16-byte scratch area at the top of the user stack, for the handler's use.

- 3. Create a new register stack frame with three output argument registers, and place the signal handler's arguments in these registers.

- 4. Set the global pointer register (gp) to the handler's gp value.

- 5. Initialize the floating-point status register (ar.fpsr) to the standard value, as defined by the common runtime conventions.

- Transfer control to the signal handler, providing the appearance that the handler has been called, so that a return from the handler will reinstall the saved (and possibly modified) context.

### 3.3.3 Signal Handler Interface

According to the *Single UNIX Specification*, if the SA\_SIGINFO flag is used when a signal handler is installed, the handler will be called with three arguments, according to the following prototype:

```

void handler(int signo, siginfo_t *info, void *context);

```

In addition to the several members required by *Single UNIX Specification*, the siginfo\_t structure contains the following fields for IA-64:

| int si_imm Immediate operand for break instruction |

|----------------------------------------------------|

|----------------------------------------------------|

The Single UNIX Specification defines the si\_addr field as the address of the faulting instruction or the faulting memory reference. When it is an instruction address, the value is represented as a bundle address with the low-order two bits set to indicate the particular instruction within a bundle.

The Single UNIX Specification allows the application to cast the context argument to the type ucontext\_t, which contains the following fields (at least):

| stack_t uc_stack       | The stack used by this context.                         |

|------------------------|---------------------------------------------------------|

| mcontext_t uc_mcontext | A machine-specific representation of the saved context. |

The stack\_t structure contains the following fields (at least):

| void *ss_sp    | Stack base or pointer |

|----------------|-----------------------|

| size_t ss_size | Size of the stack     |

| int ss_flags   | Flags                 |

The stack described by this structure includes both the memory stack and the backing store.

The mcontext\_t structure is an opaque structure. Its size must be specified by the ABI, but its layout is implementation specific. Each implementation may provide an API for accessing and modifying the context.

**Note:** REVIEW NOTE: Specification of the size is left to an external standards body.

### 3.3.3.1 Signal Delivery – Implementation Notes

**Note:** This section is informational and does not form part of the specification.

The si\_imm field may be placed in the \_fault member of the siginfo\_t structure, since it is delivered only for SIGTRAP signals, when si addr is also delivered.

A signal handler's return pointer must be some value that causes the saved signal context to be reinstalled when the signal handler returns; thus, it can not be an address within the range of any of the application's loaded segments. Typically, it will be the address of a kernel entry point, mapped into a shared portion of the application's address space.

The signal context record placed on the stack marks a discontinuity in the stack. While the signal handler's frame itself is an ordinary stack frame, its caller appears to be a routine whose stack frame is the context record. The system's unwind routines will need a way of recognizing the

discontinuity. The common runtime conventions provide a special implementation-dependent unwind descriptor format (P10) for this purpose. A recommended, but not required, mechanism is for the system to provide a special unwind table for the signal handler return point, using this special unwind descriptor to indicate to the unwind library that it has reached a signal context record on the stack. This unwind table is made available to the unwind library through an implementation-specific mechanism.

Implementations will likely choose not to copy the stacked general registers into the signal context record, relying instead on accessing the backing store as needed. Thus, the API routines for reading and writing the context record will need to understand the layout of the backing store in order to access and modify the stacked general registers.

If the backing store overflows as a result of flushing the register stack in preparation for signal delivery, the system may need to provide space in the mcontext\_t record for saving the remainder of the register stack. Thus, there may be a discontinuity in the backing store, and API routines for accessing the general registers must take this into account.

The API set should include read and write routines for each element of user-visible state, plus read and write routines for the stacked general registers. The APIs should provide an abstraction layer to help the programmer deal with the complexities of NaT bits, the layout of the backing store, the frame marker, and the location of the instruction pointer within the current bundle.

### 3.3.4 Debugging Support

A program may use the break instruction subject to the restrictions documented in Chapter 2 of *Conventions*. A break instruction with an immediate operand with the high-order two bits set to 01 is reserved for debugger breakpoints. For purposes of implementing the *System V ABI*, a value of zero in the remaining bits (i.e. an operand of  $0 \times 80000$ ) is defined as the debugger breakpoint; all other values in this range are undefined.

# 3.3.5 Process Startup

This section describes the initial program state that the exec functions create when constructing a new process image. Programming language systems use this initial program state to establish a standard environment for their application programs. As an example, a C program begins executing at a function named main, conventionally declared in the following way.

```

extern int main(int argc, char *argv[]);

```

Briefly, argc is a non-negative argument count and argv is an array of argument strings, with argv[argc]=0;.

Although this section does not describe C program initialization, it gives the information necessary to implement the call to main or to the entry point for a program in any other language.

The implementation will call (or appear to call) the program entry point recorded in the e\_entry field of the ELF header, hereafter referred to as "main", according to standard calling conventions. The system is responsible for initializing the process state to satisfy the common runtime conventions (see *Conventions*). These initializations include, but are not limited to, the following:

1. The current frame marker must be configured for zero input and local registers, and at least four output registers.

- 2. The stack pointer register (sp) must be aligned to a 16-byte boundary. An initial stack frame must exist for the routine in the implementation responsible for calling main, with space for a 16-byte scratch area for use by main.

- 3. The RSE backing store pointer registers must be valid.

- 4. The return pointer register (rp) is a valid return address, such that if the program returns from the main routine, the implementation will cause the program to exit normally, using the main's return value as the exit status.

- 5. The unwind information for this "bottom-of-stack" routine in the implementation must provide a mechanism for recognizing the bottom of the stack during a stack unwind.

- 6. The global pointer register (gp) contains main's global pointer.

- 7. The floating-point status register (ar.fpsr) is initialized as described in *Conventions*.

The first two argument registers (r32-r33, named out0-out1 at entry to main) must contain argc and argv, respectively. The third and fourth argument registers (r34-r35, out2-out3) must be allocated as required by the common runtime conventions, but are not defined by this ABI.

# int<sub>e</sub>l<sub>®</sub>

# intel<sub>®</sub> Object Files

#### 4.1 **ELF Header**

#### 4.1.1 **Machine Information**

#### 4.1.1.1 **Programming Model**

As described in Section 1.1, "The Intel IA-64 Architecture and the System V ABI" on page 1-1, binaries using the IA-64 instruction set may program to either a 32-bit model, in which the C data types int and long and all pointer types are 32-bit objects (ILP32); or to a 64-bit model, in which the C int type is 32-bits but the C long type and all pointer types are 64-bit objects (LP64). This specification describes both binaries that use the ILP32 and the LP64 model. For LP64 binaries, the e flags member of the ELF header will include the value EF IA 64 ABI64 (see Table 4-2 below). For ILP32 binaries e\_flags will not include EF\_IA\_64\_ABI64. IA-64 files using the 32-bit programming model may not be combined with IA-64 files using the 64-bit programming model.

#### 4.1.1.2 File Class

For IA-64 ILP32 relocatable (i.e. of type ET REL) objects, the file class value in e ident[EI CLASS] must be ELFCLASS32. For LP64 relocatable objects, the file class value may be either ELFCLASS32 or ELFCLASS64, and a conforming linker must be able to process either or both classes. ET\_EXEC or ET\_DYN object file types must use ELFCLASS32 for ILP32 and ELFCLASS64 for LP64 programs.

Addresses appearing in ELFCLASS32 relocatable objects for LP64 programs are implicitly extended to 64 bits by zero-extending.

Note: Some constructs legal in ILP64 programs, e.g. absolute 64-bit addresses outside the 32-bit range, may require use of an ELFCLASS64 relocatable object file.

#### 4.1.1.3 **Data Encoding**

For the data encoding in e\_ident[EI\_DATA], IA-64 64-bit objects can use either ELFDATA2MSB or ELFDATA2LSB. That is, IA-64 64-bit ELF files may use either the big endian or little endian data encoding. IA-64 files using ELFDATA2MSB encoding may not be combined with IA-64 files using ELFDATA2LSB encoding.

#### 4.1.1.4 Operating System Identification

The e\_ident[EI\_OSABI] value identifies the operating system and ABI to which the object is targeted, as listed in Table 4-1.

Table 4-1. Operating System Identification, e\_ident[EI\_OSABI]

| Name              | Value | Meaning                    |

|-------------------|-------|----------------------------|

| ELFOSABI_NONE     | 0     | Reserved                   |

| ELFOSABI_HPUX     | 1     | HP-UX                      |

| ELFOSABI_NETBSD   | 2     | NetBSD                     |

| ELFOSABI_LINUX    | 3     | Linux                      |

| "Unspecified"     | 4     | [IA-32 GNU Mach/Hurd]      |

| "Unspecified"     | 5     | [86 Open common IA-32 ABI] |

| ELFOSABI_SOLARIS  | 6     | Solaris                    |

| ELFOSABI_MONTEREY | 7     | Monterey                   |

| ELFOSABI_IRIX     | 8     | IRIX                       |

| ELFOSABI_FREEBSD  | 9     | FreeBSD                    |

| ELFOSABI_TRU64    | 10    | Compaq TRU64 UNIX          |

| ELFOSABI_MODESTO  | 11    | Novell Modesto             |

| ELFOSABI_OPENBSD  | 12    | Open BSD                   |

#### 4.1.1.5 **Processor Identification**

Processor identification resides in the ELF header's e\_machine member and must have the value EM\_IA\_64.

#### 4.1.1.6 **Processor-specific Flags**

The ELF header e\_flags member holds bit flags associated with the file, as listed in Table 4-2.

Table 4-2. IA-64 Processor-Specific Flags, e\_flags

| Name                        | Value      |

|-----------------------------|------------|

| EF_IA_64_MASKOS             | 0x00ff000f |

| EF_IA_64_ABI64              | 0x00000010 |

| EF_IA_64_REDUCEDFP          | 0x00000020 |

| EF_IA_64_CONS_GP            | 0x00000040 |

| EF_IA_64_NOFUNCDESC_CONS_GP | 0x00000080 |

| EF_IA_64_ABSOLUTE           | 0x00000100 |

| EF_IA_64_ARCH               | 0xff000000 |

All bits in this mask are reserved for operating system specific values. EF\_IA\_64\_MASKOS

EF\_IA\_64\_ABI64 If this bit is set, the object uses the LP64 programming model, as described above. If the bit is clear, the object uses the ILP32

programming model.

Object Files 4-2

EF\_IA\_64\_REDUCEDFP

If this bit is set, the object has been compiled with a reduced floating-point model. The compiler uses only floating point registers £6-£11 for integer arithmetic. If the program does not perform explicit floating-point calculations, registers £6-£11 are the only floating-point registers that need to be saved by interrupt handlers. When combining relocatable objects, a linker should set the EF\_IA\_64\_REDUCEDFP flag in the resulting object only if all of the objects to be combined have the flag set.

EF\_IA\_64\_CONS\_GP

If this bit is set, the global pointer (gp) is treated as a program-wide constant. The gp is saved and restored only for indirect function calls. Objects with this bit set may not be combined with objects that do not have this bit set. This model is intended for use primarily in standalone programs, such as operating system kernels. Objects with this bit set are not ABI-conforming.

#### EF IA 64 NOFUNCDESC CONS GP

If this bit is set, the global pointer (gp) is treated as a program-wide constant. The gp is never saved or restored across function calls. In this model, a function's address is not treated as the address of a two-word function descriptor. Rather, it is the actual address of the function definition itself. This model is intended for use primarily in standalone programs, such as operating system kernels. Objects with this bit set are not ABI-conforming.

EF IA 64 ABSOLUTE

If this bit is set, the program loader is instructed to load the executable at the addresses specified in the program headers. Objects with this bit set are not ABI-conforming.

EF\_IA\_64\_ARCH

The integer value formed by these eight bits identifies the architecture version. This field is reserved for use when the IA-64 architecture is extended with backward-compatible features. It records the minimum level of the architecture required by the object code. The only currently defined value is one.

## 4.2 Sections

# 4.2.1 Section Types

The IA-64 architecture defines two processor-specific section types and a reserved range to be used in the sh\_type member of the ELF section header in addition to the standard section types.

Table 4-3. Section Types, sh\_type

| Name                    | Value      |

|-------------------------|------------|

| SHT_IA_64_EXT           | 0x7000000  |

| SHT_IA_64_UNWIND        | 0x7000001  |

| SHT_IA_64_LOPSREG       | 0x78000000 |

| SHT_IA_64_HIPSREG       | 0x7fffffff |

| SHT_IA_64_PRIORITY_INIT | 0x79000000 |

Object Files 4-3

SHT\_IA\_64\_EXT The section contains product specific extension bits. These consist of at

least one 64-bit word of attribute flags that identify specific non-architectural extensions that are required by the object code. See

Section 4.2.4, "Architecture Extensions" on page 4-6.

SHT\_IA\_64\_UNWIND The section contains unwind function table entries for stack unwinding.

See Conventions for details.

SHT\_IA\_64\_LOPSREG to SHT\_IA\_64\_HIPSREG

Sections in this range are reserved for implementation-specific section types. A portion of this range is allocated for use by implementations which have assigned Operating System Identification values (see Section 4.1.1.4, "Operating System Identification" on page 4-1). If the high-order 8 bits of sh\_type contain  $0\times78$  then the next 8 bits contain the EI\_OSABI value. For example, if the EI\_OSABI value for an implementation is  $0\times03$ , the reserved range for that implementation is  $0\times78030000$  to  $0\times7803ffff$ .

SHT\_IA\_64\_PRIORITY\_INIT The section contains priority initialization records, each of which is a pair consisting of an Elfxx\_Word priority and an Elfxx\_Addr function address.

An implementation is not required to support this section type, beyond the gABI requirements for the handling of unrecognized section types (i.e. linking them into a contiguous section in the object file created by the static linker).

### 4.2.2 Section Attribute Flags

A section header sh\_flags member holds 1-bit flags that describe the attributes of the section. The IA-64 architecture defines two processor-specific values in addition to the standard values.

Table 4-4. Section Attribute Flags, sh\_flags

| Name              | Value      |

|-------------------|------------|

| SHF_IA_64_SHORT   | 0x10000000 |

| SHF_IA_64_NORECOV | 0x2000000  |

SHF\_IA\_64\_SHORT The section contains objects that will be referenced using an offset from

the global pointer (gp), so the section must be placed near gp.

SHF\_IA\_64\_NORECOV The section contains code that uses speculative instructions without recovery code. ABI-conforming implementations are not required to execute binaries that do not have recovery code associated with them.

4-4 Object Files

# 4.2.3 Special Sections

The following special sections are defined for use on the IA-64 architecture.

**Table 4-5. Special Sections**

| Name               | Туре             | Attributes                          |

|--------------------|------------------|-------------------------------------|

| .IA_64.archext     | SHT_IA_64_EXT    | None                                |

| .IA_64.pltoff      | SHT_PROGBITS     | SHF_ALLOC+SHF_WRITE+SHF_IA_64_SHORT |

| .IA_64.unwind      | SHT_IA_64_UNWIND | SHF_ALLOC+SHF_LINK_ORDER            |

| .IA_64.unwind_info | SHT_PROGBITS     | SHF_ALLOC                           |

| .got               | SHT_PROGBITS     | SHF_ALLOC+SHF_WRITE+SHF_IA_64_SHORT |

| .plt               | SHT_PROGBITS     | SHF_ALLOC+SHF_EXECINSTR             |

| .sbss              | SHT_NOBITS       | SHF_ALLOC+SHF_WRITE+SHF_IA_64_SHORT |

| .sdata             | SHT_PROGBITS     | SHF_ALLOC+SHF_WRITE+SHF_IA_64_SHORT |

| .sdata1            | SHT_PROGBITS     | SHF_ALLOC+SHF_WRITE+SHF_IA_64_SHORT |

.IA\_64.archext This section holds product-specific extension bits (see

SHT\_IA\_64\_EXT in Section 4.2.1, "Section Types" on page 4-3 for details). The link editor will perform a logical "or" of the extension bits of each object it combines when creating an executable so that it creates only a single .IA\_64.archext section in the executable.

.IA\_64.pltoff This section holds local function descriptor entries. See "Coding

Examples" in *Conventions* and Section 5.3.6, "Procedure Linkage

Table" on page 5-7 for more information.

.IA 64.unwind This section holds the unwind function table. The contents are described

in Conventions.

.IA 64.unwind info

This section holds stack unwind and exception handling information.

The contents specific to unwind information are described in *Conventions*. The exception handling information is programming

language specific and is unspecified.

.got This section holds the global offset table. See "Coding Examples" in

Conventions and Section 5.3.4, "Global Offset Table" on page 5-6 for

more information.

.plt This section holds the procedure linkage table. See Section 5.3.6,

"Procedure Linkage Table" on page 5-7 for more information.

.sbss This section holds uninitialized data that contribute to the program's

memory image. Data objects contained in this section are recommended to be eight bytes or less in size. The system initializes the data with zeroes when the program begins to run. The section occupies no file space, as indicated by the section type SHT\_NOBITS. The .sbss section is placed so it may be accessed using short direct addressing (22-

bit offset from gp). See "Protection Areas" in Conventions.

Object Files 4-5

.sdata and .sdata1

These sections hold initialized data that contribute to the program's memory image. Data objects contained in these sections are recommended to be eight bytes or less in size. The .sdata and .sdata1 sections are placed so they may be accessed using short direct addressing (22-bit offset from gp). See "Protection Areas" in *Conventions*.

### 4.2.4 Architecture Extensions

The .IA\_64.archext section allows a compiler to record dependencies on certain features and capabilities of a specific processor, that are extensions to the IA-64 architecture. Currently, there are no such extensions defined, and this section is not expected to be used by the compilers. Nevertheless, linkers and loaders should provide the proper implementation of this section in preparation for future architectural extensions.

The contents of the .IA\_64.archext section, if present, is interpreted as a series of individual bits grouped into 64-bit doublewords. The first doubleword of the group is defined to correspond bitwise to the bits in CPUID Register 4 (General Features/Capability Bits). Additional doublewords in the section have no defined meaning, unless and until the IA-64 architecture is extended with additional CPUID Registers defining additional capability bits.

All .IA\_64.archext sections must be of section type SHT\_IA\_64\_EXT, and should have no flags set in the sh\_flags field. Each section must be a multiple of 8 bytes in length, with 8 byte alignment. The linker must combine such sections by a bitwise OR operation on each corresponding doubleword of each section (i.e., the first doubleword of one section OR'ed with the first doubleword of the other section, and so on). If some sections are shorter than others, the shorter ones are padded with zeroes at the end, so that the combined output section is equal in length to the largest input section.

If a .IA\_64.archext section exists in the output file, the linker must create a program header table entry of type PT\_IA\_64\_ARCHEXT to communicate this information to the loader. This program header table entry must precede all entries of type PT\_LOAD. If the .IA\_64.archext section exists, but its contents are all zeroes, the linker may omit the section and program header table entry, but it is not required to.

When an executable or shared library is loaded, and a PT\_IA\_64\_ARCHEXT entry is present in the program header table, the loader should compare the contents of the first doubleword of the section with CPUID Register 4. If any bits are set in the section that are not also set in CPUID Register 4, the implementation must refuse to load the file. If, in the future, additional CPUID registers are defined to identify further capability bits, the loader should check additional doublewords of this section with those registers as well. If the section contains excess doublewords that do not correspond to defined CPUID registers, the loader should check that all excess bits are zero.

The linker should be prepared to deal with .IA\_64.archext sections of arbitrary length, but it is permissible to truncate the sections to a reasonable length. It is recommended that all tools should be prepared to deal with at least four doublewords in this section.

4-6 Object Files

# 4.3 Relocations

# 4.3.1 Relocation Types

A relocation entry's  $r_{offset}$  value designates the offset or virtual address of the affected storage unit. For data relocations, this is the first byte of the word or doubleword being relocated. For instructions, it is the address of the bundle containing the instruction being relocated. The least significant two bits of the offset identify the instruction slot to which the relocation applies, as described below. Each instruction bundle is 16 bytes long and 16 byte aligned; each instruction slot is 41 bits long. Whether a given relocation type applies to an instruction or data field is noted in the *Field* column of the table of relocations, below.

Figure 4-1. Instruction Bundle Layout

**Table 4-6. Relocation Offset Instruction Slot Encoding**

| Encoding (last two bits) | Instruction slot |

|--------------------------|------------------|

| 00                       | Slot 0           |

| 01                       | Slot 1           |

| 10                       | Slot 2           |

| 11                       | Invalid          |

Relocation entries describe how to alter the following instruction and data fields (bit numbers appear to the upper left of the field they label; all fields are numbered from bit 0).

Object Files 4-7

Figure 4-2. Relocatable Fields

word32

A 32-bit field occupying four bytes with arbitrary alignment. The byte order for these values is specified by the relocation type.

word64

A 64-bit field occupying eight bytes with arbitrary alignment. The byte order for these values is specified by the relocation type.

4-8 Object Files

function descriptor

Two contiguous 64-bit words occupying 16 bytes with 8-byte alignment. The byte order for the function descriptor is specified by the relocation type. Function descriptor entries are created by the linker and/or the dynamic linker and are used in resolving function addresses. The first 64-bit word contains the function address. The second 64-bit word contains the value of the global pointer (qp) for the object containing the definition of the function. Function descriptor entries are referenced by relocations contained in shared objects and executable objects only and are intended to be processed at run-time.

instruction - immediate14 A signed 14-bit immediate value. imm<sub>7b</sub> contains bits 0 through 6 (loworder bits). imm<sub>6d</sub> contains bits 7 through 12. s contains the high-order bit (sign bit).

instruction - immediate22 A signed 22-bit immediate value. imm<sub>7b</sub> contains bits 0 through 6 (loworder bits). imm<sub>9d</sub> contains bits 7 through 15. imm<sub>5c</sub> contains bits 16 through 20. s contains the high-order bit (sign bit).

instruction - immediate21 - form 1

A signed 21-bit immediate value. This value is formed by taking a 25-bit displacement and shifting it right by four bits. For the resulting value, imm<sub>20b</sub> contains bits 0 through 19 (low-order bits). s contains the highorder bit (sign bit).

instruction - immediate21 - form 2

A signed 21-bit immediate value. This value is formed by taking a 25-bit displacement and shifting it right by four bits. For the resulting value, imm<sub>7a</sub> contains bits 0 through 6 (low-order bits). imm<sub>13c</sub> contains bits 7 through 19. s contains the high-order bit (sign bit).

instruction - immediate21 - form 3

A signed 21-bit immediate value. This value is formed by taking a 25-bit displacement and shifting it right by four bits. For the resulting value, imm<sub>20a</sub> contains bits 0 through 19 (low order bits). i contains the highorder bit (sign bit).

instruction - immediate64 A 64-bit immediate value. The value is contained within two 41-bit instruction slots (slots 1 and 2 of a bundle). imm<sub>7b</sub> contains bits 0 through 6 (low order bits). imm<sub>9d</sub> contains bits 7 through 15. imm<sub>5c</sub> contains bits 16 through 20.  $i_c$  contains bit 21.  $imm_{41}$  contains bits 22 through 62 and takes the entire width of slot 1 (the second instruction slot). i contains bit 63.

instruction - immediate 60 A 60-bit immediate value which is left shifted 4 bits to form 64-bit value for long branch or call. The value is contained within two 41-bit instruction slots (slots 1 and 2 of a bundle). imm<sub>20b</sub> contains bits 0 through 19 (low order bits). imm<sub>39</sub> contains bits 20 through 58. i contains bit 59.

The calculations below assume one of two contexts. First, the relocations may be contained within a relocatable file; the actions are transforming the relocatable file into an executable or a shared object file. Conceptually, the link editor merges one or more relocatable files to form the output. It first decides how to locate and combine the input files, then updates the symbol values, and finally performs the relocation. Because many IA-64 instructions have small immediate fields, the longer form of relocation entry containing an explicit addend (Elf32\_Rela or Elf64\_Rela) is always used for relocatable objects on IA-64. Second, the relocations may be contained within an executable file or shared object; the actions complete the job of relocation by fixing addresses for position-independent code. Relocations contained within executable files or shared objects may

Object Files 4-9

use either the shorter form (Elf32\_Rel or Elf64\_Rel) or the longer form (Elf32\_Rela or Elf64\_Rela). These relocations always apply to word or doubleword data objects. The relocation dealt with at run-time would be aligned.

Descriptions below use the following notation.

A The Addend used to compute the value of the relocatable field.

BD The Base address Difference, a constant that must be applied to a virtual

address. This constant represents the difference between the run-time virtual address and the link-time virtual address of a particular segment. The segment is implied by the value of the link-time virtual address. See

Section 5.2, "Program Loading" on page 5-1 for details.

P The "Place" (section offset or address) of the storage unit being relocated

(computed using r\_offset). If the relocation applies to an instruction,

this is the address of the bundle containing the instruction.

S The value of the Symbol whose index resides in the relocation entry.

@gprel(expr) Computes a gp-relative displacement - the difference between expr and

the value of the global pointer (gp) for the current module.

@ltoff(expr) Requests the creation of a global offset table (GOT) entry that will hold

the full value of *expr* and computes the gp-relative displacement to that GOT entry. See Section 5.3.4, "Global Offset Table" on page 5-6 for

more information.

@pltoff(symbol) Requests the creation of a local function descriptor entry for the given

symbol and computes the gp-relative displacement to that function descriptor entry. See Section 5.3.6, "Procedure Linkage Table" on

page 5-7 for more information.

@ segrel(expr) Computes a segment-relative displacement - the difference between expr

and the address of the beginning of the segment containing the relocatable object. This relocation type is designed for data structures that reside in read-only segments, but need to contain pointers. The relocatable object and effective address must be contained within the same segment. Applications using these pointers must be aware that they are segment-relative and must adjust their values at run-time, using the load address of the containing segment. No output relocations will be

generated for @segrel relocations.

@secrel(expr) Computes a section-relative displacement - the difference between expr

and the address of the beginning of the (output) section that contains *expr*. This relocation type is designed for references from one non-allocatable section to another. Applications using these values must be aware that they are section-relative and must adjust their values at runtime, using the adjusted address of the target section. No output

relocations will be generated for @secrel relocations.

@fptr(symbol) Evaluates to the address of the "official" function descriptor for the given

symbol. See Conventions for more information.

The MSB and LSB suffixes on the following relocation types indicate whether the target field is stored most significant byte first (big-endian) or least significant byte first (little-endian), respectively.

4-10 Object Files

**Table 4-7. IA-64 Relocation Types**

| Name                    | Value | Field                            | Calculation          |

|-------------------------|-------|----------------------------------|----------------------|

| R_IA_64_NONE            | 0     | None                             | None                 |

| R_IA_64_IMM14           | 0x21  | instruction - immediate14        | S + A                |

| R_IA_64_IMM22           | 0x22  | instruction - immediate22        | S + A                |

| R_IA_64_IMM64           | 0x23  | instruction - immediate64        | S + A                |

| R_IA_64_DIR32MSB        | 0x24  | word32 MSB                       | S + A                |

| R_IA_64_DIR32LSB        | 0x25  | word32 LSB                       | S + A                |

| R_IA_64_DIR64MSB        | 0x26  | word64 MSB                       | S + A                |

| R_IA_64_DIR64LSB        | 0x27  | word64 LSB                       | S + A                |

| R_IA_64_GPREL22         | 0x2a  | instruction - immediate22        | @gprel(S + A)        |

| R_IA_64_GPREL64I        | 0x2b  | instruction - immediate64        | @gprel(S + A)        |

| R_IA_64_GPREL64MSB      | 0x2e  | word64 MSB                       | @gprel(S + A)        |

| R_IA_64_GPREL64LSB      | 0x2f  | word64 LSB                       | @gprel(S + A)        |

| R_IA_64_LTOFF22         | 0x32  | instruction - immediate22        | @Itoff(S + A)        |

| R_IA_64_LTOFF64I        | 0x33  | instruction - immediate64        | @Itoff(S + A)        |

| R_IA_64_PLTOFF22        | 0x3a  | instruction - immediate22        | @pltoff(S + A)       |

| R_IA_64_PLTOFF64I       | 0x3b  | instruction - immediate64        | @pltoff(S + A)       |

| R_IA_64_PLTOFF64MSB     | 0x3e  | word64 MSB                       | @pltoff(S + A)       |

| R_IA_64_PLTOFF64LSB     | 0x3f  | word64 LSB                       | @pltoff(S + A)       |

| R_IA_64_FPTR64I         | 0x43  | instruction - immediate64        | @fptr(S + A)         |

| R_IA_64_FPTR32MSB       | 0x44  | word32 MSB                       | @fptr(S + A)         |

| R_IA_64_FPTR32LSB       | 0x45  | word32 LSB                       | @fptr(S + A)         |

| R_IA_64_FPTR64MSB       | 0x46  | word64 MSB                       | @fptr(S + A)         |

| R_IA_64_FPTR64LSB       | 0x47  | word64 LSB                       | @fptr(S + A)         |

| R_IA_64_PCREL60B        | 0x48  | instruction - immediate60        | S + A – P            |

| R_IA_64_PCREL21B        | 0x49  | instruction - immediate21 form 1 | S + A – P            |

| R_IA_64_PCREL21M        | 0x4a  | instruction - immediate21 form 2 | S + A - P            |

| R_IA_64_PCREL21F        | 0x4b  | instruction - immediate21 form 3 | S + A - P            |

| R_IA_64_PCREL32MSB      | 0x4c  | word32 MSB                       | S + A - P            |

| R_IA_64_PCREL32LSB      | 0x4d  | word32 LSB                       | S + A – P            |

| R_IA_64_PCREL64MSB      | 0x4e  | word64 MSB                       | S + A – P            |

| R_IA_64_PCREL64LSB      | 0x4f  | word64 LSB                       | S + A - P            |

| R_IA_64_LTOFF_FPTR22    | 0x52  | instruction - immediate22        | @ltoff(@fptr(S + A)) |

| R_IA_64_LTOFF_FPTR64I   | 0x53  | instruction - immediate64        | @ltoff(@fptr(S + A)) |

| R_IA_64_LTOFF_FPTR32MSB | 0x54  | word32 MSB                       | @ltoff(@ftpr(S + A)) |

| R_IA_64_LTOFF_FPTR32LSB | 0x55  | word32 LSB                       | @ltoff(@fptr(S + A)) |

| R_IA_64_LTOFF_FPTR64MSB | 0x56  | word64 MSB                       | @ltoff(@fptr(S + A)) |

| R_IA_64_LTOFF_FPTR64LSB | 0x57  | word64 LSB                       | @ltoff(@fptr(S + A)) |

| R_IA_64_SEGREL32MSB     | 0x5c  | word32 MSB                       | @segrel(S + A)       |

Object Files 4-11

Table 4-7. IA-64 Relocation Types (Cont'd)

| Name                           | Value | Field                            | Calculation       |

|--------------------------------|-------|----------------------------------|-------------------|

| R_IA_64_SEGREL32LSB            | 0x5d  | word32 LSB                       | @segrel(S + A)    |

| R_IA_64_SEGREL64MSB            | 0x5e  | word64 MSB                       | @segrel(S + A)    |

| R_IA_64_SEGREL64LSB            | 0x5f  | word64 LSB                       | @segrel(S + A)    |

| R_IA_64_SECREL32MSB            | 0x64  | word32 MSB                       | @secrel(S + A)    |

| R_IA_64_SECREL32LSB            | 0x65  | word32 LSB                       | @secrel(S + A)    |

| R_IA_64_SECREL64MSB            | 0x66  | word64 MSB                       | @secrel(S + A)    |

| R_IA_64_SECREL64LSB            | 0x67  | word64 LSB                       | @secrel(S + A)    |

| R_IA_64_REL32MSB               | 0x6c  | word32 MSB                       | BD + A            |

| R_IA_64_REL32LSB               | 0x6d  | word32 LSB                       | BD + A            |

| R_IA_64_REL64MSB               | 0x6e  | word64 MSB                       | BD + A            |

| R_IA_64_REL64LSB               | 0x6f  | word64 LSB                       | BD + A            |

| R_IA_64_LTV32MSB               | 0x74  | word32 MSB                       | S + A (see below) |

| R_IA_64_LTV32LSB               | 0x75  | word32 LSB                       | S + A (see below) |

| R_IA_64_LTV64MSB               | 0x76  | word64 MSB                       | S + A (see below) |

| R_IA_64_LTV64LSB               | 0x77  | word64 LSB                       | S + A (see below) |

| R_IA_64_PCREL21BI <sup>a</sup> | 0x79  | instruction - immediate21 form 1 | S+A-P             |

| R_IA_64_PCREL22                | 0x7A  | instruction - immediate22        | S + A - P         |

| R_IA_64_PCREL64I               | 0x7B  | instruction - imm64              | S + A - P         |

| R_IA_64_IPLTMSB                | 0x80  | function descriptor MSB          | see below         |

| R_IA_64_IPLTLSB                | 0x81  | function descriptor LSB          | see below         |

| R_IA_64_SUB                    | 0x85  | Instruction - imm64              | A – S             |

| R_IA_64_LTOFF22X               | 0x86  | instruction - immediate22        | see below         |

| R_IA_64_LDXMOV                 | 0x87  | instruction - immediate22        | see below         |

a. The PCREL21BI relocation works just like PCREL21B, but it marks a call for which gp has not been saved, thus requiring that the target reside within the same load module as the call. It is needed it for the cases where we choose to bind a symbol locally, optimizing the call sequence, but where we don't want to, or can't, mark the symbol "protected" or "hidden."

**Note:** Relocation information not used at run-time may be unaligned. It is expected that linkers will have to deal with them. Relocations dealt at run-time will always be aligned.

**Note:** Values above 0xe0 are available for use in implementation-defined ways. All other values are reserved for future use.

4-12 Object Files

The relocation type values have been chosen so that the expression type can be easily extracted by masking off the lower three or four bits, and the data/instruction format can be determined in most cases by looking only at the low-order four bits.

R\_IA\_64\_LTV32MSB, R\_IA\_64\_LTV32LSB, R\_IA\_64\_LTV32MSB and R\_IA\_64\_LTV32LSB These relocations appear only in relocatable objects. They behave identically to the R\_IA\_64\_DIR\* family of relocations, with one exception: while it is expected that the addresses created will need further relocation at run-time, the linker should not create a corresponding relocation in the output executable or shared object file. The run-time consumer of the information provided is expected to relocate these values.

#### R\_IA\_64\_IPLTMSB and R\_IA\_64\_IPLTLSB

These relocations are used only by the dynamic linker. Object files may contain these relocations. Static linkers should pass these along for the dynamic linker. When used with the shorter form of relocation entry (Elf32\_Rel or Elf64\_Rel), they instruct the dynamic linker to initialize the corresponding function descriptor entry with the address of the referenced function and the value of the global pointer (gp) for the object containing the function's definition. When used with the longer form of relocation entry containing an explicit addend (Elf32\_Rela or Elf64\_Rela), the addend is additionally added to the address of the referenced function. See Section 5.3.6, "Procedure Linkage Table" on page 5-7 for more information.

#### R IA 64 LTOFF22X and R IA 64 LDXMOV

These relocations are used to support link-time rewriting of the indirect addressing code sequences. The R\_IA\_64\_LTOFF22X relocation is used on the addl instruction that computes the address of a linkage table entry in place of the normal R\_IA\_64\_LTOFF22 relocation. It has exactly the same semantics as R IA 64 LTOFF22 unless the linker determined that the symbol could be addressed directly, in which case the linker transforms this into an R\_IA\_64\_GPREL22 relocation. An ABI-conforming implementation must recognize this relocation, but may choose to treat it as a synonym for R\_IA\_64\_LTOFF22. The R\_IA\_64\_LDXMOV relocation is used on an 1d8 instruction, where no relocation would ordinarily be seen. The 1d8 instruction normally extracts the address of the referenced object from the linkage table by dereferencing the address computed by the addl. Its symbol and addend fields must match exactly those of a corresponding R\_IA\_LTOFF22X relocation. If the linker determines that the symbol can be addressed directly, it rewrites the 1d8 as a mov. This can be done by masking out all but the qp, r1, and r3 fields of the instruction, then or ing in the bit pattern 0x8000000000. If an ABI-conforming implementation is choosing to treat R\_IA\_64\_LTOFF22X as a synonym for R\_IA\_64\_LTOFF22, this relocation is ignored.

Object Files 4-13

# int<sub>el®</sub>

4-14 Object Files

# Program Loading and Dynamic Linking5

# 5.1 Program Header

The IA-64 architecture defines two processor-specific values to be used in the p\_type member of the program header.

Table 5-1. Program Header Types, p\_type

| Name             | Value     |

|------------------|-----------|

| PT_IA_64_ARCHEXT | 0x7000000 |

| PT_IA_64_UNWIND  | 0x7000001 |

PT\_IA\_64\_ARCHEXT The segment contains a section of type SHT\_IA\_64\_EXT as described

in Section 4.2, "Sections" on page 4-3. If this entry is present, it must

precede all entries of type PT\_LOAD.

PT\_IA\_64\_UNWIND The segment contains the stack unwind tables. See *Conventions* and

Section 4.2, "Sections" on page 4-3 for details.

The IA-64 architecture defines one processor-specific value to be used in the p\_flags member of the program header.

Table 5-2. Program Header Flags, p flags

| Name             | Value      |

|------------------|------------|

| PF_IA_64_NORECOV | 0x80000000 |

PF IA 64 NORECOV

If this bit is set, the segment contains code that uses speculative instructions without recovery code. Executbles with this flag bit set are not ABI conforming.

# 5.2 Program Loading

As the system creates or augments a process image, it logically copies a file's segment to a virtual memory segment. When—and if—the system physically reads the file depends on the program's execution behavior, system load, and so on. A process does not require a physical page unless it references the logical page during execution, and processes commonly leave many pages unreferenced. Therefore delaying physical reads frequently obviates them, improving system performance. To obtain this efficiency in practice, executable and shared object files must have segment images whose file offsets and virtual addresses are congruent, modulo the page size.

The preferred page size for virtual memory management purposes for an IA-64 64-bit segment is contained in the p\_align field of the program header entry describing that segment. The p\_align field must contain 4 KB (0x1000) or a page size as defined in Section 7 of the *IA-64 Processor Programmer's Reference Manual*. Virtual addresses and file offsets for IA-64 64-bit segments are congruent modulo either the value contained in the p\_align field or 4KB (0x1000), whichever is larger.

The following examples show a 64k alignment; virtual addresses and file offsets for segments are congruent modulo 64k (0x10000).

Figure 5-1. Example Executable File

Figure 5-2. Example Program Header Segments

| Member   | Text               | Data               |

|----------|--------------------|--------------------|

| p_type   | PT_LOAD            | PT_LOAD            |

| p_offset | 0x110              | 0x4af740           |

| p_vaddr  | 0x4000000000000110 | 0x600000000000f740 |

| p_paddr  | unspecified        | unspecified        |

| p_filesz | 0x4af630           | 0x16768            |

| p_memsz  | 0x4af630           | 0x46b90            |

| p_flags  | PF_R+PF_X          | PF_R+PF_W+PF_X     |

| p_align  | 0x10000            | 0x10000            |

Although the example's file offsets and virtual addresses are congruent modulo 64KB for both text and data, up to four file pages hold impure text or data (depending on page size and file system block size).

- The first text page contains the ELF header, the program header table, and other information.

- The last text page holds a copy of the beginning of data.

- The first data page has a copy of the end of text.

- The last data page may contain file information not relevant to the running process.

Logically, the system enforces the memory permissions as if each segment were complete and separate; segment addresses are adjusted to ensure each logical page in the address space has a single set of permissions. In the example above, the region of the file holding the end of text and the beginning of data will be mapped twice: at one virtual address for text and at a different virtual address for data.

The end of the data segment requires special handling for uninitialized data, which the system defines to begin with zero values. Thus if a file's last data page includes information not in the logical memory page, the extraneous data must be set to zero, not the unknown contents of the executable file. "Impurities" in the other three pages are not logically part of the process image; whether the system expunges them is unspecified. The memory image for this program follows, assuming 64KB (0x10000) pages.

Figure 5-3. Example Process Image Segments

| Address             | Contents                                 | Segment |

|---------------------|------------------------------------------|---------|

| 0x40000000000000000 | <i>Header padding</i> 0x110 bytes        |         |

| 0x4000000000000110  | Text segment 0x4af630 bytes              | Text    |

| 0x40000000004af740  | <i>Data padding</i><br>0x8c0 bytes       |         |

|                     |                                          |         |

| 0x60000000000000000 | <i>Text padding</i><br>0xf740 bytes      |         |

| 0x600000000000f740  | Data segment 0x16768 bytes               | Data    |

| 0x6000000000025ea8  | Uninitialized data<br>0x30428 zero bytes |         |

| 0x60000000000562d0  | Page padding<br>0x9d30 zero bytes        |         |

On the IA-64 architecture, both executable and shared object segments contain position-independent code. This lets a segment's virtual address change from one process to another, without invalidating execution behavior. Furthermore, there is no assumption that the individual segments for a given executable or shared object are fixed relatively in relation to one another. For example, the system might load all read-only segments for a process in one range of memory addresses and all read-write segments in a different range of addresses. Therefore, while the addresses shown in the example in Figures 5-3, 5-4 and 5-5 show the data segment for an executable immediately following the text segment, there is no requirement that it does so. The addresses assigned for each segment by the link editor, however, must not overlap.

Because dynamically linked IA-64 64-bit executable files are position-independent, the exec routines may choose to load such files at different addresses than those specified in the file's program header. The dynamic linker must be prepared to deal with this possibility.

### 5.2.1 Linktime and Runtime Addresses

Virtual addresses assigned by the linker when creating an executable or shared object file are known as link-time virtual addresses. Since position-independent executables and shared objects may be loaded at different addresses than those assigned by the linker, runtime virtual addresses differ from linktime virtual address by a constant value. Since there is no fixed address relationship at runtime among segments created at linktime, the constant value must be calculated based on the

segment containing the address in question. The constant is the difference between the address at which the containing segment was loaded and the address assigned for that segment by the linker. The following table illustrates the calculation for an example text object.

**Table 5-3. Example Runtime Address Calculation**

| Value or Calculation                        | Result             |

|---------------------------------------------|--------------------|

| Address as determined by link editor        | 0x40000000000532f0 |

| Segment address contained in program header | 0x4000000000000110 |

| Base address of segment in file             | 0x4000000000000000 |

| Base address of segment in process          | 0x4c80000000000000 |

| Runtime minus link-time base address        | 0x0c80000000000000 |

| Address of object in process                | 0x4c800000000532f0 |

### 5.2.2 Initializations

As the implementation constructs the new process, it is responsible for a number of initialization actions. Some of these have been described in Section 3.3.5, "Process Startup" on page 3-6. In addition to those steps, the implementation must:

- 1. Ensure the process environment has been properly initialized.

- 2. The global variable \_environ must be initialized to point to the environment, before the initialization routines are executed. The execution of the initialization routines may result in the modification of environ.

- 3. Pre-initializations routines in the executable, described in "Dynamic Linking" in Chapter 5 of the *System V ABI*, must be called, according to standard calling conventions.

- 4. Initialization routines, described in ""Dynamic Linking" in Chapter 5 of the *System V* ABI and in the following section, in the executable and in all loaded shared objects must be called, according to standard calling conventions. The only order specified is that, for every library dependency "A depends on B", the initialization routines for B must be called before those for A.

# 5.3 Dynamic Linking

# **5.3.1** Dynamic Linker

When building an executable file that uses dynamic linking, the link editor adds a program header element of type PT\_INTERP to an executable file, telling the system to invoke the dynamic linker as the program interpreter. The location of the dynamic linker, to be recorded on the PT\_INTERP string, varies depending on the code model, architecture and byte order.

**Table 5-4. Dynamic Linker Location**

| Architecture | Code Model | Byte Order    | Dynamic Linker Name      |

|--------------|------------|---------------|--------------------------|

| IA-64        | ILP32      | Little-Endian | /usr/lib/ia64132/ld.so.1 |

| IA-64        | ILP32      | Big-Endian    | /usr/lib/ia64b32/ld.so.1 |

| IA-64        | LP64       | Little-Endian | /usr/lib/ia64164/ld.so.1 |

| IA-64        | LP64       | Big-Endian    | /usr/lib/ia64b64/ld.so.1 |

## 5.3.2 Dynamic Section

All dynamic section entries containing addresses (entries that use the d\_ptr member) contain link-time virtual addresses, as described above. The dynamic linker must relocate these addresses based on the difference between the link-time and runtime addresses of the segments referenced by the d\_ptr member.

Dynamic section entries give information to the dynamic linker. Some of this information is processor-specific, including the interpretation of some entries in the dynamic structure.

DT PLTGOT

On the IA-64 architecture, this entry's d\_ptr member gives the address contained in the global pointer (gp) for the object.

The IA-64 architecture defines one processor-specific dynamic section tag value.

Table 5-5. Dynamic Section Tag, d\_tag

| Name                 | Value     |

|----------------------|-----------|

| DT_IA_64_PLT_RESERVE | 0x7000000 |

DT\_IA\_64\_PLT\_RESERVE

This element's d\_ptr member contains the address of the first of three 8-byte words in the short data segment reserved for use by the dynamic linker. The three words are contiguous, with the second and third words growing toward higher addresses.

# **5.3.3** Shared Object Dependencies