# Intel<sup>®</sup> Itanium<sup>®</sup> 2 Processor Reference Manual

For Software Development and Optimization

**June 2002**

Document Number: 251110-001

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium<sup>®</sup> and Itanium 2 processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-4725, or by visiting Intel's web site at http://www.intel.com.

Intel, Itanium, Pentium, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2002, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

# int<sub>el®</sub>

# Contents

| 1 | About                           | t this Manual                                                                                                                                                                        | 1              |

|---|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Overview Contents Terminology Related Documentation Revision History                                                                                                                 | 2              |

| 2 | Itaniu                          | ım <sup>®</sup> 2 Processor Enhancements                                                                                                                                             | 5              |

|   | 2.1<br>2.2<br>2.3<br>2.4        | Implemented Instructions Functional Units and Issue Rules Operation Latencies Data Operations 2.4.1 Data Speculation and the ALAT 2.4.2 Data Alignment                               | 5<br>6         |

|   | 2.5<br>2.6<br>2.7               | 2.4.3 Control Speculation  Memory Hierarchy  Branch Prediction  Instruction Prefetching                                                                                              | 8<br>10        |

| 3 | Funct                           | tional Units and Issue Rules                                                                                                                                                         | 11             |

|   | 3.1<br>3.2<br>3.3               | Execution Model  Number and Types of Functional Units  Instruction Slot to Functional Unit Mapping  3.3.1 Execution Width  3.3.2 Dispersal Rules  3.3.3 Split Issue and Bundle Types | 11<br>12<br>14 |

| 4 | Laten                           | ncies and Bypasses                                                                                                                                                                   | 19             |

|   | 4.1<br>4.2                      | Control and Data Speculation Penalties  Branch Related Latencies and Penalties                                                                                                       |                |

| 5 | Data                            | Operations                                                                                                                                                                           | 21             |

|   | 5.1                             | Data Speculation and the ALAT                                                                                                                                                        | 21             |

|   | 5.2<br>5.3<br>5.4               | Speculative and Predicated Loads/Stores  Floating-Point Loads  Data Cache Prefetching and Load Hints  5.4.1 Ifetch Implementation                                                    | 22<br>23<br>24 |

|   | 5.5<br>5.6                      | 5.4.2 Load Temporal Locality Completers  Data Alignment  Write Coalescing  5.6.1 WC Buffer Eviction Conditions                                                                       | 26             |

|   | 5.7                             | 5.6.2 WC Buffer Flushing Behavior                                                                                                                                                    |                |

# int<sub>el®</sub>

| 6 | Memo                                      | ory Subsy                   | rstem                                      | 29 |  |  |  |  |

|---|-------------------------------------------|-----------------------------|--------------------------------------------|----|--|--|--|--|

|   | 6.1                                       | Transla                     | ation Lookaside Buffers                    | 30 |  |  |  |  |

|   |                                           | 6.1.1                       | Instruction TLBs                           | 30 |  |  |  |  |

|   |                                           | 6.1.2                       | Data TLBs                                  | 30 |  |  |  |  |

|   | 6.2                                       | Hardw                       | are Page Walker                            | 31 |  |  |  |  |

|   | 6.3                                       | Cache                       | Summary                                    | 32 |  |  |  |  |

|   | 6.4                                       |                             | evel Instruction Cache                     |    |  |  |  |  |

|   | 6.5                                       | Instruc                     | tion Stream Buffer                         | 33 |  |  |  |  |

|   | 6.6                                       | First-L                     | evel Data Cache                            | 33 |  |  |  |  |

|   |                                           | 6.6.1                       | L1D Loads                                  | 34 |  |  |  |  |

|   |                                           | 6.6.2                       | L1D Stores                                 | 34 |  |  |  |  |

|   |                                           | 6.6.3                       | Load and Store Considerations              | 34 |  |  |  |  |

|   |                                           | 6.6.4                       | L1D Misses                                 |    |  |  |  |  |

|   | 6.7                                       | Secon                       | d-Level Unified Cache                      |    |  |  |  |  |

|   |                                           | 6.7.1                       | L1D Requests to L2                         |    |  |  |  |  |

|   |                                           | 6.7.2                       | L2 OzQ                                     |    |  |  |  |  |

|   |                                           | 6.7.3                       | L2 Cancels                                 |    |  |  |  |  |

|   |                                           | 6.7.4                       | L2 Recirculate                             |    |  |  |  |  |

|   |                                           | 6.7.5                       | Ordering                                   |    |  |  |  |  |

|   |                                           | 6.7.6                       | L2 Instruction Prefetch FIFO               |    |  |  |  |  |

|   |                                           | 6.7.7                       | System Bus/L3 Interactions                 |    |  |  |  |  |

|   | 6.8                                       |                             | Level Unified Cache                        |    |  |  |  |  |

|   | 6.9                                       | Systen                      | n Bus                                      | 43 |  |  |  |  |

| 7 | Branch Instructions and Branch Prediction |                             |                                            |    |  |  |  |  |

|   | 7 1                                       | 7.1 Branch Prediction Hints |                                            |    |  |  |  |  |

|   | 7.2                                       |                             | t Branches                                 |    |  |  |  |  |

|   | 7.3                                       |                             | t Loop Prediction                          |    |  |  |  |  |

| 8 | Inotru                                    |                             | fetching                                   |    |  |  |  |  |

| 0 |                                           |                             |                                            |    |  |  |  |  |

|   | 8.1                                       |                             | ning Prefetching                           |    |  |  |  |  |

|   | 8.2                                       |                             | refetching                                 |    |  |  |  |  |

|   | 8.3                                       |                             | ch Flush Hints                             |    |  |  |  |  |

|   | 8.4                                       | The br                      | I Instruction                              | 51 |  |  |  |  |

| 9 | Optim                                     | izing for                   | the Itanium <sup>®</sup> 2 Processor       | 53 |  |  |  |  |

|   | 9.1                                       | Hints fo                    | or Scheduling                              | 53 |  |  |  |  |

|   | 9.2                                       |                             | al Use of Ifetch                           |    |  |  |  |  |

|   | 9.3                                       |                             | treaming                                   |    |  |  |  |  |

|   |                                           | 9.3.1                       | Floating-Point Data Streams                | 54 |  |  |  |  |

|   |                                           | 9.3.2                       | Integer Data Streams                       | 55 |  |  |  |  |

|   |                                           | 9.3.3                       | Store Data Streams                         | 55 |  |  |  |  |

|   | 9.4                                       | Contro                      | I and Data Speculation                     | 56 |  |  |  |  |

|   | 9.5 Known L2 Miss Bundle Placement        |                             |                                            |    |  |  |  |  |

|   | 9.6                                       |                             | Known L2 Cancel and Recirculate Conditions |    |  |  |  |  |

|   | 9.7                                       |                             | tion Bundling                              |    |  |  |  |  |

|   | 9.8                                       |                             | nes                                        |    |  |  |  |  |

|   |                                           | 9.8.1                       | Single Cycle Branches                      |    |  |  |  |  |

|   |                                           | 9.8.2                       | Perfect Loop Prediction                    |    |  |  |  |  |

|   |                                           | 9.8.3                       | Branch Targets                             | 57 |  |  |  |  |

# intel<sub>®</sub>

| 10  | Perforr | mance Monitoring                                                  | 59    |

|-----|---------|-------------------------------------------------------------------|-------|

|     | 10.1    | Introduction                                                      | 59    |

|     | 10.2    | Performance Monitor Programming Models                            | 59    |

|     |         | 10.2.1 Workload Characterization                                  | 60    |

|     |         | 10.2.2 Profiling                                                  | 63    |

|     |         | 10.2.3 Event Qualification                                        | 65    |

|     |         | 10.2.4 References                                                 |       |

|     | 10.3    | Performance Monitor State                                         |       |

|     |         | 10.3.1 Performance Monitor Control and Accessibility              |       |

|     |         | 10.3.2 Performance Counter Registers                              |       |

|     |         | 10.3.3 Performance Monitor Overflow Status Registers (PMC0,1,2,3) |       |

|     |         | 10.3.4 Opcode Match Check (PMC8,9,15)                             |       |

|     |         | 10.3.5 Instruction Address Range Matching                         |       |

|     |         | 10.3.6 Data Address Range Matching (PMC13)                        |       |

|     |         | 10.3.7 Event Address Registers (PMC10,11/PMD0,1,2,3,17)           |       |

|     |         | 10.3.8 Data EAR (PMC11, PMD2,3,17)                                |       |

|     |         | 10.3.9 Branch Trace Buffer                                        |       |

|     |         | 10.3.10 Interrupts                                                |       |

|     |         | 10.3.11 Processor Reset, PAL Calls, and Low Power State           |       |

| 11  | Perforr | mance Monitor Events                                              | 95    |

|     | 11.1    | Introduction                                                      | 95    |

|     | 11.2    | Categorization of Events                                          | 95    |

|     | 11.3    | Basic Events                                                      |       |

|     | 11.4    | Instruction Dispersal Events                                      | 97    |

|     | 11.5    | Instruction Execution Events                                      | 97    |

|     | 11.6    | Stall Events                                                      | 98    |

|     | 11.7    | Branch Events                                                     |       |

|     | 11.8    | Memory Hierarchy                                                  |       |

|     |         | 11.8.1 L1 Instruction Cache and Prefetch Events                   |       |

|     |         | 11.8.2 L1 Data Cache Events                                       |       |

|     |         | 11.8.3 L2 Unified Cache Events                                    |       |

|     |         | 11.8.4 L3 Cache Events                                            |       |

|     | 11.9    | System Events                                                     |       |

|     | 11.10   | TLB Events                                                        |       |

|     | 11.11   | System Bus Events                                                 |       |

|     | 11.12   | RSE Events                                                        | 115   |

|     | 11.13   | Performance Monitors Ordered by Event Code                        |       |

|     | 11.14   | Performance Monitor Event List                                    | 122   |

| 12  | Model-  | Specific and Optional Features                                    | 175   |

|     | 12.1    | Memory Attributes                                                 | 175   |

|     | 12.2    | Purge Behavior of ptc.e                                           |       |

|     | 12.3    | CPUID Return Values                                               | 175   |

|     |         | 12.3.1 Itanium® Instruction CPUID Return Values                   | 175   |

|     |         | 12.3.2 IA-32 CPUID Return Values                                  | 176   |

| Α   | Itanium | n <sup>®</sup> 2 Processor Pipeline                               | 177   |

| / 1 |         | ·                                                                 |       |

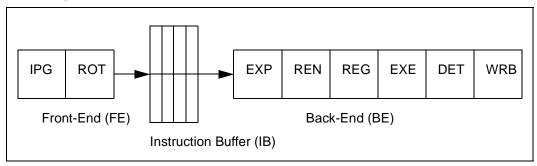

|     | A.1     | Core Pipeline                                                     |       |

|     | A.2     | Pipeline Stages                                                   |       |

|     |         | A.2.1 IPG STAGE                                                   |       |

|     |         | N.Z.Z NOTOTAGE                                                    | 1 / 0 |

# intel<sub>®</sub>

|       | A.2.5 REG Stage                                                                 | 178 |

|-------|---------------------------------------------------------------------------------|-----|

|       | A.2.6 EXE Stage                                                                 | 178 |

|       | A.2.7 DET Stage                                                                 | 178 |

|       | A.2.8 WRB Stage                                                                 | 179 |

| A.3   | Instruction Buffer (IB)                                                         | 179 |

| A.4   | Micro-Pipelines                                                                 | 179 |

|       | A.4.1 FPU Micro-Pipeline                                                        | 179 |

|       | A.4.2 L1D Micro-Pipeline                                                        | 179 |

|       | A.4.3 L2 Micro-Pipeline                                                         | 179 |

|       |                                                                                 |     |

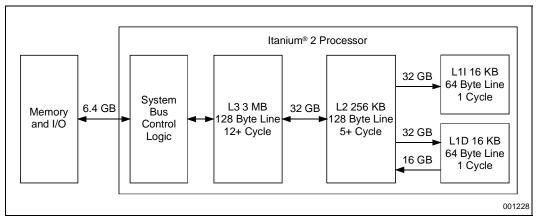

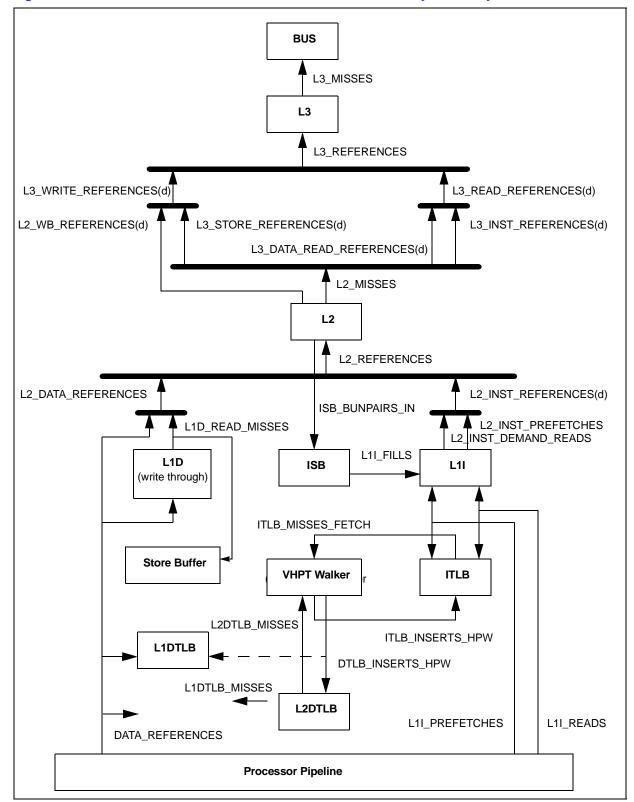

| 6-1   | Three Level Cache Hierarchy of the Itanium® 2 Processor                         | 29  |

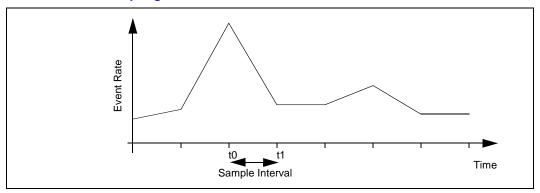

| 10-1  | Time-Based Sampling                                                             |     |

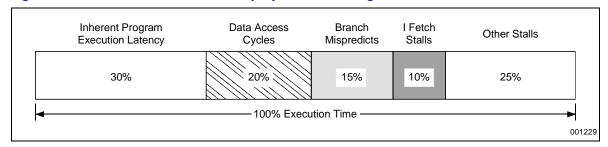

| 10-2  | Itanium® Processor Family Cycle Accounting                                      | 62  |

| 10-3  | Event Histogram by Program Counter                                              |     |

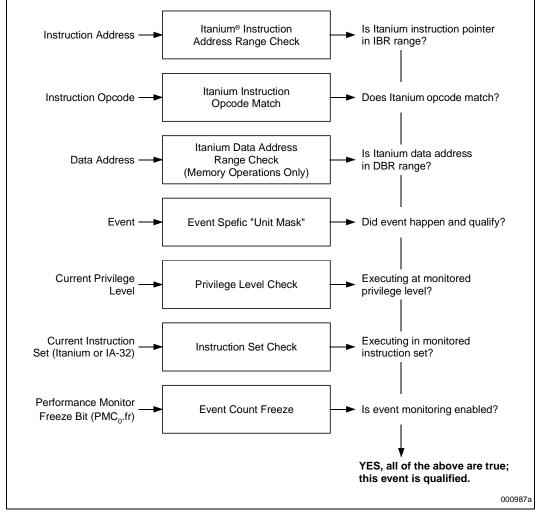

| 10-4  | Itanium® 2 Processor Event Qualification                                        | 66  |

| 10-5  | Instruction Tagging Mechanism in the Itanium® 2 Processor                       | 67  |

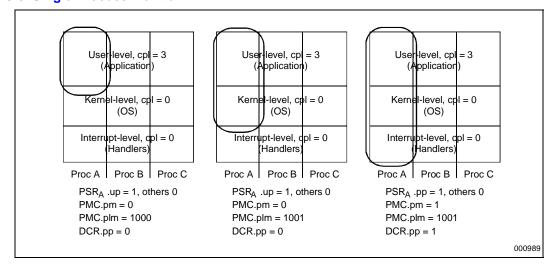

| 10-6  | Single Process Monitor                                                          |     |

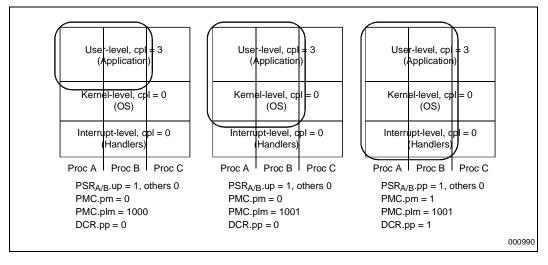

| 10-7  | Multiple Process Monitor                                                        |     |

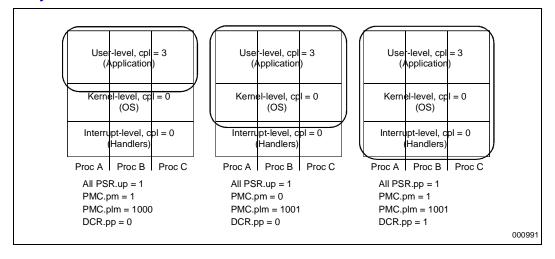

| 10-8  | System Wide Monitor                                                             |     |

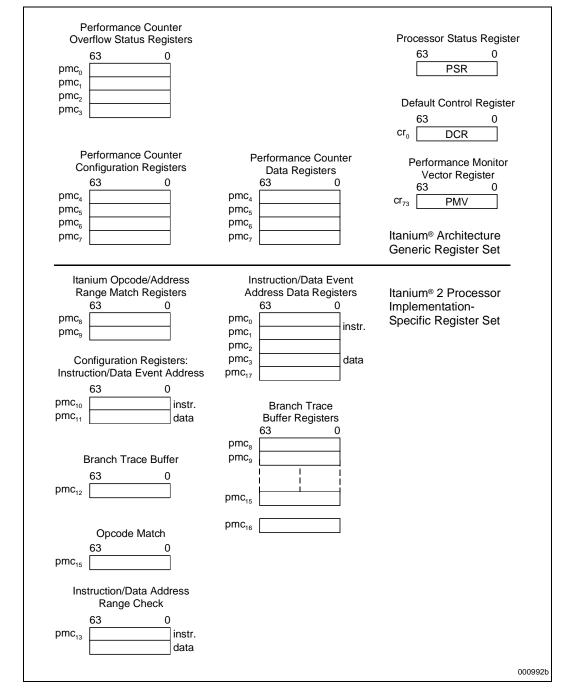

| 10-9  | Itanium® 2 Processor Performance Monitor Register Mode                          |     |

| 10-10 | Processor Status Register (PSR) Fields for Performance Monitoring               |     |

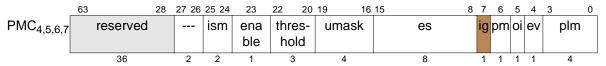

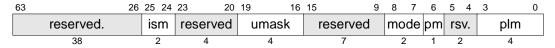

| 10-11 | Itanium® 2 Processor Generic PMC Registers (PMC4,5,6,7)                         |     |

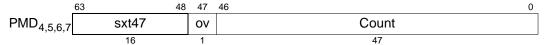

| 10-12 | Itanium® 2 Processor Generic PMD Registers (PMD4,5,6,7)                         | 75  |

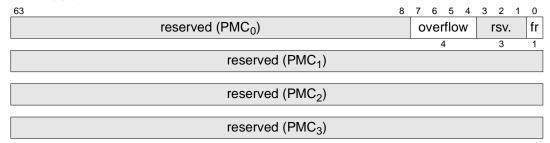

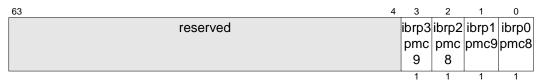

| 10-13 | Itanium® 2 Processor Performance Monitor Overflow Status Registers (PMC0,1,2,3) | 75  |

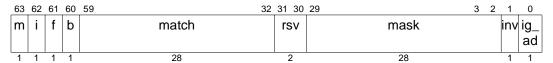

| 10-14 | Opcode Match Registers (PMC8,9)                                                 | 76  |

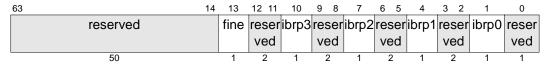

| 10-15 | Opcode Match Configuration Register (PMC15)                                     | 77  |

| 10-16 | Instruction Address Range Configuration Register (PMC14)                        | 79  |

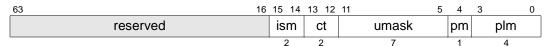

| 10-17 | Memory Pipeline Event Constraints Configuration Register (PMC13)                | 81  |

| 10-18 | Instruction Event Address Configuration Register (PMC10)                        |     |

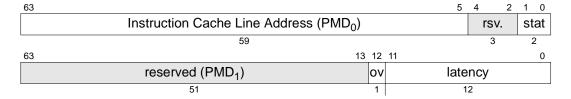

| 10-19 | Instruction Event Address Register Format (PMD0,1)                              | 83  |

| 10-20 | Data Event Address Configuration Register (PMC11)                               | 85  |

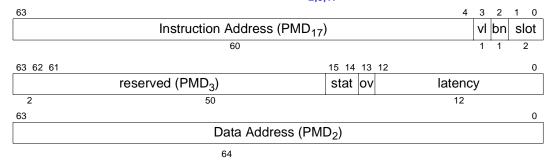

| 10-21 | Data Event Address Register Format (PMD2,3,17)                                  | 86  |

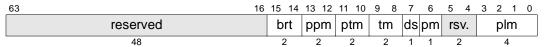

| 10-22 | Branch Trace Buffer Configuration Register (PMC12)                              |     |

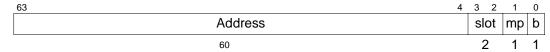

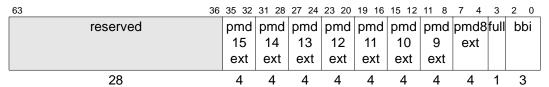

| 10-23 | Branch Trace Buffer Register Format (PMD8-15, where PMC <sub>12</sub> .ds == 0) | 91  |

| 10-24 | Branch Trace Buffer Register Format (PMD8-15, where PMC <sub>12</sub> .ds == 1) |     |

| 10-25 | Branch Trace Buffer Index Register Format (PMD16)                               | 92  |

| 11-1  | Event Monitors in the Itanium® 2 Processor Memory Hierarchy                     |     |

| A-1   | Core Pipeline of the Itanium® 2 Processor                                       | 177 |

|       |                                                                                 |     |

**Figures**

# int<sub>el®</sub>

# **Tables**

| 2-1   | Itanium® 2/ Itanium Processors Operation Latencies                               | 1  |

|-------|----------------------------------------------------------------------------------|----|

| 2-2   | L1I Cache Differences                                                            | 8  |

| 2-3   | L1D Cache Differences                                                            | 8  |

| 2-4   | L2 Unified Cache Differences                                                     | 9  |

| 2-5   | L3 Cache Differences                                                             | 9  |

| 2-6   | Instruction TLB Differences                                                      | 9  |

| 2-7   | Data TLB Differences                                                             | 9  |

| 2-8   | Branch Prediction Latencies (in cycles)                                          | 10 |

| 3-1   | A-type Instruction Port Mapping                                                  | 13 |

| 3-2   | I-type Instruction Port Mapping                                                  | 13 |

| 3-3   | M-type Instruction Port Mapping                                                  | 13 |

| 3-4   | Dual Issue Bundle Types                                                          | 16 |

| 4-1   | Speculative Load Recovery Latencies                                              | 19 |

| 4-2   | Branch Prediction Latencies                                                      | 19 |

| 4-3   | Execution with Bypass Latency Summary                                            | 20 |

| 5-1   | ALAT Entry Comparison Sizes                                                      | 2  |

| 5-2   | Control Speculation Penalties                                                    | 23 |

| 5-3   | Processor Cache Hints                                                            |    |

| 5-4   | Itanium® 2 Processor WCB Eviction Conditions                                     |    |

| 6-1   | Itanium® 2 Processor Virtual Memory Support                                      | 29 |

| 6-2   | Major Features of Instruction and Data TLBs                                      | 30 |

| 6-3   | Best Case HPW Penalties                                                          |    |

| 6-4   | Cache Summary                                                                    |    |

| 6-5   | Store to Load Forwarding Penalties                                               |    |

| 6-6   | L2 Issue Priorities                                                              |    |

| 6-7   | System Bus/L3 Requests and Final L2 State                                        |    |

| 7-1   | Branch Prediction Latencies                                                      |    |

| 8-1   | Summary of Streaming Prefetch Actions                                            |    |

| 8-2   | Prefetch Mechanisms                                                              | 50 |

| 10-1  | Average Latency per Request and Requests per Cycle Calculation Example61         |    |

| 10-2  | Itanium® 2 Processor EARs and Branch Trace Buffer                                |    |

| 10-3  | Itanium® 2 Processor Event Qualification Modes                                   |    |

| 10-4  | Itanium® 2 Processor Performance Monitor Register Set                            |    |

| 10-5  | Performance Monitor PMC Register Control Fields (PMC4,5,6,7,10,11,12)            |    |

| 10-6  | Itanium® 2 Processor Generic PMC Register Fields (PMC4,5,6,7)                    |    |

| 10-7  | Itanium® 2 Processor Generic PMD Register Fields                                 | 75 |

| 10-8  | Itanium® 2 Processor Performance Monitor Overflow Register Fields (PMC0,1,2,3)76 |    |

| 10-9  | Opcode Match Register Fields (PMC8,9)                                            |    |

| 10-10 | Opcode Match Configuration Register Fields (PMC15)                               |    |

| 10-11 | Itanium® 2 Processor Instruction Address Range Check by Instruction Set          |    |

| 10-12 | Instruction Address Range Configuration Register Fields (PMC14)                  |    |

| 10-13 | Memory Pipeline Event Constraints Fields (PMC13)                                 |    |

| 10-14 | Instruction Event Address Configuration Register Fields (PMC10)                  |    |

| 10-15 | Instruction EAR (PMC10) umask Field in Cache Mode (PMC10.ct='1x)                 |    |

| 10-16 | Instruction EAR (PMD0,1) in Cache Mode (PMC10.ct='1x)                            |    |

| 10-17 | Instruction EAR (PMC10) umask Field in TLB Mode (PMC10.ct=00)                    |    |

| 10-18 | Instruction EAR (PMD0,1) in TLB Mode (PMC10.ct='00)                              | 85 |

# intel®

| 10-19 | Data Event Address Configuration Register Fields (PMC11)              |    |

|-------|-----------------------------------------------------------------------|----|

| 10-20 | Data EAR (PMC11) Umask Fields in Data Cache Mode (PMC11.mode=00)      |    |

| 10-21 | PMD2,3,17 Fields in Data Cache Load Miss Mode (PMC11.mode=00)         |    |

| 10-22 | Data EAR (PMC11) Umask Field in TLB Mode (PMC10.ct=01)                |    |

| 10-23 | PMD2,3,17 Fields in TLB Miss Mode (PMC11.mode='01)                    |    |

| 10-24 | PMD2,3,17 Fields in ALAT Miss Mode (PMC11.mode='1x)                   |    |

| 10-25 | Branch Trace Buffer Configuration Register Fields (PMC12)             |    |

| 10-26 | Branch Trace Buffer Register Fields (PMD8-15)                         |    |

| 10-27 | Branch Trace Buffer Index Register Fields (PMD16)                     | 92 |

| 10-28 | Information Returned by PAL_PERF_MON_INFO for the Itanium® 2Processor |    |

| 11-1  | Performance Monitors for Basic Events                                 |    |

| 11-2  | Derived Monitors for Basic Events                                     |    |

| 11-3  | Performance Monitors for Instruction Dispersal Events                 |    |

| 11-4  | Performance Monitors for Instruction Execution Events                 |    |

| 11-5  | Derived Monitors for Instruction Execution Events                     |    |

| 11-6  | Performance Monitors for Stall Events                                 | 99 |

| 11-7  | Performance Monitors for Branch Events1                               |    |

| 11-8  | Performance Monitors for L1 Instruction Cache and Prefetch Events1    |    |

| 11-9  | Derived Monitors for L1 Instruction Cache and Prefetch Events1        | 03 |

| 11-10 | Performance Monitors for L1 Data Cache Events1                        |    |

| 11-11 | Performance Monitors for L1D Cache Set 01                             | 04 |

| 11-12 | Performance Monitors for L1D Cache Set 11                             | 04 |

| 11-13 | Performance Monitors for L1D Cache Set 21                             |    |

| 11-14 | Performance Monitors for L1D Cache Set 31                             | 04 |

| 11-15 | Performance Monitors for L1D Cache Set 41                             | 05 |

| 11-16 | Performance Monitors for L2 Unified Cache Events1                     | 05 |

| 11-17 | Derived Monitors for L2 Unified Cache Events1                         | 06 |

| 11-18 | Performance Monitors for L2 Cache Set 0                               | 07 |

| 11-19 | Performance Monitors for L2 Cache Set 11                              | 07 |

| 11-20 | Performance Monitors for L2 Cache Set 2                               | 07 |

| 11-21 | Performance Monitors for L2 Cache Set 31                              | 80 |

| 11-22 | Performance Monitors for L2 Cache Set 4                               | 80 |

| 11-23 | Performance Monitors for L2 Cache Set 51                              | 80 |

| 11-24 | Performance Monitors for L3 Unified Cache Events1                     | 09 |

| 11-25 | Derived Monitors for L3 Unified Cache Events1                         | 09 |

| 11-26 | Performance Monitors for System Events                                | 10 |

| 11-27 | Derived Monitors for System Events                                    | 10 |

| 11-28 | Performance Monitors for TLB Events1                                  | 10 |

| 11-29 | Derived Monitors for TLB Events1                                      | 11 |

| 11-30 | Performance Monitors for System Bus Events1                           | 12 |

| 11-31 | Derived Monitors for System Bus Events1                               |    |

| 11-32 | Conventions for System Bus Transactions                               | 15 |

| 11-33 | Bus Events by Snoop Response1                                         | 15 |

| 11-34 | Performance Monitors for RSE Events                                   | 15 |

| 11-35 | Derived Monitors for RSE Events1                                      | 16 |

| 11-36 | All Performance Monitors Ordered by Code1                             | 16 |

| 11-37 | Unit Masks for ALAT_CAPACITY_MISS1                                    |    |

| 11-38 | Unit Masks for BACK_END_BUBBLE1                                       |    |

| 11-39 | Unit Masks for BE_BR_MISPREDICT_DETAIL1                               |    |

| 11-40 | Unit Masks for BE_EXE_BUBBLE1                                         |    |

| 11-41 | Unit Masks for BE FLUSH BUBBLE                                        |    |

# intel<sub>®</sub>

| 11-42 | Unit Masks for BE_L1D_FPU_BUBBLE          | 124 |

|-------|-------------------------------------------|-----|

| 11-43 | Unit Masks for BE_LOST_BW_DUE_TO_FE       | 125 |

| 11-44 | Unit Masks for BE_RSE_BUBBLE              | 126 |

| 11-45 | Unit Masks for BR_MISPRED_DETAIL          | 127 |

| 11-46 | Unit Masks for BR_MISPREDICT_DETAIL2      | 128 |

| 11-47 | Unit Masks for BR_PATH_PRED               | 129 |

| 11-48 | Unit Masks for BR_PATH_PRED2              | 130 |

| 11-49 | Unit Masks for BUS_ALL                    | 131 |

| 11-50 | Unit Masks for BUS_BACKSNP_REQ            | 131 |

| 11-51 | Unit Masks for BUS_IO                     | 133 |

| 11-52 | Unit Masks for BUS_LOCK                   | 133 |

| 11-53 | Unit Masks for BUS_MEMORY                 | 134 |

| 11-54 | Unit Masks for BUS_MEM_READ               | 134 |

| 11-55 | Unit Masks for BUS_RD_DATA                | 136 |

| 11-56 | Unit Masks for BUS_RD_IO                  | 137 |

| 11-57 | Unit Masks for BUS_RD_PRTL                |     |

| 11-58 | Unit Masks for BUS_SNOOPS                 | 138 |

| 11-59 | Unit Masks for BUS_SNOOPS_HITM            |     |

| 11-60 | Unit Masks for BUS_SNOOP_STALL_CYCLES     |     |

| 11-61 | Unit Masks for BUS_WR_WB                  | 140 |

| 11-62 | Unit Masks for ENCBR_MISPRED_DETAIL       | 142 |

| 11-63 | Unit Masks for EXTERN_DP_PINS_0_TO_3      |     |

| 11-64 | Unit Masks for EXTERN_DP_PINS_4_TO_5      |     |

| 11-65 | Unit Masks for FE_BUBBLE                  | 144 |

| 11-66 | Unit Masks for FE_LOST_BW                 | 145 |

| 11-67 | Unit Masks for IA64_INST_RETIRED          | 147 |

| 11-68 | Unit Masks for IA64_TAGGED_INST_RETIRED   |     |

| 11-69 | Unit Masks for IDEAL_BE_LOST_BW_DUE_TO_FE | 148 |

| 11-70 | Unit Masks for INST_CHKA_LDC_ALAT         | 149 |

| 11-71 | Unit Masks for INST_FAILED_CHKA_LDC_ALAT  |     |

| 11-72 | Unit Masks for INST_FAILED_CHKS_RETIRED   |     |

| 11-73 | Unit Masks for ITLB_MISSES_FETCH          |     |

| 11-74 | Unit Masks for L1D_READ_MISSES            |     |

| 11-75 | Unit Masks for L1I_PREFETCH_STALL         |     |

| 11-76 | Unit Masks for L2_BAD_LINES_SELECTED      |     |

| 11-77 | Unit Masks for L2_BYPASS                  |     |

| 11-78 | Unit Masks for L2_DATA_REFERENCES         |     |

| 11-79 | Unit Masks for L2_FILLB_FULL              |     |

| 11-80 | Unit Masks for L2_FORCE_RECIRC            | 158 |

| 11-81 | Unit Masks for L2_GOT_RECIRC_IFETCH       | 158 |

| 11-82 | Unit Masks for L2_IFET_CANCELS            | 159 |

| 11-83 | Unit Masks for L2_ISSUED_RECIRC_IFETCH    |     |

| 11-84 | Unit Masks for L2_L3ACCESS_CANCEL         |     |

| 11-85 | Unit Masks for L2_OPS_ISSUED              |     |

| 11-86 | Unit Masks for L2_OZDB_FULL               |     |

| 11-87 | Unit Masks for L2_OZQ_CANCELS0            |     |

| 11-88 | Unit Masks for L2_OZQ_CANCELS1            |     |

| 11-89 | Unit Masks for L2_OZQ_CANCELS2            |     |

| 11-90 | Unit Masks for L2_OZQ_FULL                | 165 |

| 11-91 | Unit Masks for L2_STORE_HIT_SHARED        |     |

| 11-92 | Unit Masks for L2 VICTIMB_FULL            | 166 |

# intel<sub>®</sub>

| 11-93 | Unit Masks for L3_READS               | 167 |

|-------|---------------------------------------|-----|

| 11-94 | Unit Masks for L3_WRITES              | 168 |

| 11-95 | Unit Masks for MEM_READ_CURRENT       | 169 |

| 11-96 | Unit Masks for RSE_REFERENCES_RETIRED | 171 |

| 11-97 | Unit Masks for SYLL_NOT_DISPERSED     | 172 |

| 11-98 | Unit Masks for SYLL_OVERCOUNT         | 173 |

| 12-1  | Itanium® 2 CPUID Return Values        | 175 |

| 12-2  | Encoding of Cache Return Values       | 176 |

| A-1   | FPU Pipeline                          | 179 |

| A-2   | L1D Micro-Pipeline                    | 179 |

| A-3   | L2 Micro-Pipeline                     | 179 |

# intel® About this Manual

### 1.1 **Overview**

The Itanium<sup>®</sup> 2 processor is the second implementation of the Intel<sup>®</sup> Itanium<sup>®</sup> processor family. This document describes how the Itanium 2 processor implements features of the Itanium architecture, as well as specific features of the Itanium 2 processor that are relevant to performance tuning, compilation, and assembler programming. Unless otherwise stated, all of the restrictions, rules, sizes, and capacities described in this document apply specifically to the Itanium 2 processor and may not apply to other implementations of the Itanium processor family.

General understanding of processor components and explicit familiarity with Itanium instructions are assumed. This document is not intended to be used as an architectural reference for the Itanium architecture. For more information on the Itanium architecture, consult the Intel® Itanium<sup>TM</sup> Architecture Software Developer's Manual.

### 1.2 Contents

Chapter 2, "Itanium® 2 Processor Enhancements" compares the Itanium processor and the Itanium 2 processor, highlighting some of the considerations that should be taken when optimizing for the Itanium 2 processor.

Chapter 3, "Functional Units and Issue Rules" describes the number and type of available functional units, instruction issue rules, and heuristics for efficient instruction scheduling based upon machine resources and issue rules.

Chapter 4, "Latencies and Bypasses" describes latencies and bypasses for execution of the different instruction types on the Itanium 2 processor.

Chapter 5, "Data Operations" describes considerations for data operations such as speculative or predicated loads or stores, floating-point loads, and prefetches. Data alignment considerations are also discussed.

Chapter 6, "Memory Subsystem" provides an overview of the memory subsystem hierarchy on the Itanium 2 processor.

Chapter 7, "Branch Instructions and Branch Prediction" describes how hints for branch prediction and instruction prefetch are implemented on the Itanium 2 processor.

Chapter 8, "Instruction Prefetching" describes how prefetching is implemented on the Itanium 2 processor.

Chapter 9, "Optimizing for the Itanium® 2 Processor" is a summary that draws conclusions from important points noted in earlier chapters.

Chapter 10, "Performance Monitoring" discusses performance monitoring registers and implementations specific to the Itanium 2 processor.

Chapter 11, "Performance Monitor Events" summarizes the Itanium 2 processor events and describes how to compute commonly used performance metrics.

Chapter 12, "Model-Specific and Optional Features" discusses Itanium 2 processor model-specific behavior, such as executing CPUID instructions.

# 1.3 Terminology

The following definitions are for terms that will be used throughout this document:

**dispersal** The process of mapping instructions within bundles to functional units.

**bundle rotation** The process of bringing new bundles into the two-bundle issue window.

**split issue** Instruction execution when an instruction does not issue at the same time

as the instruction immediately before it.

advanced load address table (ALAT)

The ALAT holds the state necessary for advanced load and check

operations.

translation lookaside buffer (TLB)

The TLB holds virtual to physical mappings.

virtual hash page table (VHPT)

The VHPT is an extension of the TLB hierarchy, which resides in the virtual memory space, is designed to enhance virtual address translation

performance.

hardware page walker (HPW)

The HPW is the third level of address translation. It is an engine that performs page look-ups from the VHPT and seeks opportunities to insert

translations into the processor TLBs.

register stack engine (RSE)

The RSE moves registers between the register stack and the backing

store in memory.

event address registers (EARs)

The EARs record the instruction and data addresses of data cache misses.

## 1.4 Related Documentation

The reader of this document should also be familiar with the material and concepts presented in the following documents:

- Intel<sup>®</sup> Itanium<sup>™</sup> Architecture Software Developer's Manual, Volume 1: Application Architecture

- Intel<sup>®</sup> Itanium<sup>TM</sup> Architecture Software Developer's Manual, Volume 2: System Architecture

- Intel<sup>®</sup> Itanium<sup>™</sup> Architecture Software Developer's Manual, Volume 3: Instruction Set Reference

# 1.5 Revision History

| Revision<br>Number | Description                     | Date      |

|--------------------|---------------------------------|-----------|

| -001               | Public release of the document. | June 2002 |

About this Manual

# Itanium® 2 Processor Enhancements 2

This chapter outlines the major differences between the Itanium 2 processor and the Itanium processor. This is not an exhaustive list, so a reference to more details accompanies each topic.

# 2.1 Implemented Instructions

The Itanium 2 processor implements the 64-bit long branch instruction (brl) instruction directly in hardware. This instruction was not implemented in the Itanium processor. It allows programmers to direct a branch to an address that uses all 64 address bits. Details on the brl instruction can be found in *Volume 3: Instruction Set Reference* of the *Intel*<sup>®</sup> *Itanium*<sup>TM</sup> *Architecture Software Developer's Manual*. There are some branch prediction performance implications associated with the brl instruction which are noted in Chapter 7, "Branch Instructions and Branch Prediction."

# 2.2 Functional Units and Issue Rules

In general, the Itanium 2 processor has more functional units than the Itanium processor.

- In particular, the Itanium 2 processor has 6 arithmetic logic units (ALUs) to perform arithmetic operations, compares, most multimedia instructions, etc. The Itanium processor can only issue four of these types of instructions per cycle.

- The Itanium 2 processor has four memory ports allowing two integer loads and two integer stores per cycle. The Itanium processor has two memory ports.

- The Itanium 2 processor can issue one SIMD floating-point (FP) instruction per cycle. The Itanium processor can issue two SIMD FP instructions per cycle.

- Under certain conditions, the Itanium 2 processor can issue I-type instructions to memory

functional units, thus increasing the number of template pair types which can be issued in one

cycle. For the Itanium processor, I-type instructions will only be issued to integer functional

units.

- The Itanium 2 processor scoreboards multi-cycle operations such as first-level instruction cache (L1D) misses, multimedia, and floating-point operations.

- This means that when an integer operation uses the result of a multimedia operation and the integer operation is not scheduled to cover the latency, the dependent instruction group will wait until the multimedia data is available.

A predicated off operation, with a use of a scoreboarded operand, will stall the issue group for one cycle if the predicate was generated in the previous cycle. A predicated off instruction with predicates generated two or more cycles earlier will not incur pipeline stalls even when operands are scoreboarded.

# 2.3 Operation Latencies

On the Itanium 2 processor, most latencies are the same or shorter than on the Itanium processor with a few exceptions, i.e. memory latencies are shorter, floating-point latencies are shorter. A few more bypasses exist which remove some asymmetries. Table 2-1, "Itanium® 2/ Itanium Processors

Operation Latencies" shows latencies for both the Itanium 2 processor and the Itanium processor. The areas of difference are indicated by non-shaded boxes. The two different latency numbers are separated by a forward-slash or '/'. When reading from left to right, the first latency number corresponds to the Itanium 2 processor and the second number corresponds to the Itanium processor.

# 2.4 Data Operations

# 2.4.1 Data Speculation and the ALAT

The Itanium 2 processor advanced load address table (ALAT) is fully associative while the Itanium processor ALAT is two-way associative.

On the Itanium processor, a ld.c which misses the ALAT causes a 10-cycle pipeline flush. On the Itanium 2 processor, the penalty is 8 cycles.

On the Itanium processor, if a chk.a or chk.s fails, an OS handler will be invoked through a trap handler to steer execution to the recovery code at the location specified in the target field of the chk.a/chk.s instruction. On the Itanium 2 processor, hardware will usually perform the resteer without operating system intervention. This reduces the resteer cost from approximately 200 cycles to 18 cycles. If any of the following conditions are not met, the Itanium 2 processor will trap to the OS to service the chk.a/chk.s:

```

psr.ic = 1

psr.it = 1

psr.ss = 0

psr.tb = 0

```

If a chk. a follows a store within the same cycle, the chk. a will always fail on the Itanium processor. On the Itanium 2 processor, a 12-bit address compare against ALAT entries will occur. See Section 5.1, "Data Speculation and the ALAT" for more details.

# 2.4.2 Data Alignment

The Itanium processor can support misaligned integer accesses within 16-byte blocks; however, the Itanium 2 processor supports misaligned integer accesses within 8-byte blocks. Section 5.5, "Data Alignment" has greater detail on misaligned access support for the Itanium 2 processor.

Table 2-1. Itanium® 2/ Itanium Processors Operation Latencies

|          |                                                                                                                                                                                                | Consumer       |                 |     |                       |                 |               |      |       |      |      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----|-----------------------|-----------------|---------------|------|-------|------|------|

|          |                                                                                                                                                                                                | Qual.<br>Pred. | Branch<br>Pred. | ALU | Load<br>Store<br>Addr | Multi-<br>media | Store<br>Data | Fmac | Fmisc | getf | setf |

|          | Adder: add, cmp, tbit, addp4, shladd, shladdp4, sum, logical ops, 64-bit immed. moves, movl, post-inc ops (includes post-inc stores, loads, lfetches)                                          | n/a            | n/a             | 1   | 1/(1-2) <sup>1</sup>  | 3               | 1             | n/a  | n/a   | n/a  | 1    |

|          | Multimedia                                                                                                                                                                                     | n/a            | n/a             | 3   | 3                     | 2               | 3             | n/a  | n/a   | n/a  | 3    |

|          | getf                                                                                                                                                                                           | n/a            | n/a             | 5/9 | 6/9                   | 6/9             | 5/9           | n/a  | n/a   | n/a  | 6/9  |

|          | setf                                                                                                                                                                                           | n/a            | n/a             | n/a | n/a                   | n/a             | 6/2           | 6/2  | 6/2   | 6/2  | n/a  |

|          | Fmac: fma, fms,<br>fnma, fpma, fpms,<br>fpnma, fadd, fnmpy,<br>fsub, fpmpy, fpnmpy,<br>fmpy, fnorm, xma,<br>frcpa, fprcpa, frsqrta,<br>fpsqrta, fcvt, fpcvt                                    | n/a            | n/a             | n/a | n/a                   | n/a             | 4/5           | 4/5  | 4/5   | 4/5  | n/a  |

| Producer | Fmisc: fselect, fcmp, fclass, fmin, fmax, famin, famax, fpmin, fpmax, fpamin, fpcmp, fmerge, fmix, fsxt, fpack, fswap, fand, fandcm, for, fxor, fpmerge, fneg, fnegabs, fpabs, fpneg, fpnegabs | n/a            | n/a             | n/a | n/a                   | n/a             | 4/5           | 4/5  | 4/5   | 4/5  | n/a  |

|          | INT side predicate write: cmp, tbit, tnat                                                                                                                                                      | 1              | 0               | n/a | n/a                   | n/a             | n/a           | n/a  | n/a   | n/a  | n/a  |

|          | FP side predicate write: fcmp                                                                                                                                                                  | 2              | 1/1             | n/a | n/a                   | n/a             | n/a           | n/a  | n/a   | n/a  | n/a  |

|          | FP side predicate<br>write: frcpa, fprcpa,<br>frsqrta, fpsqrta                                                                                                                                 | 2              | 2               | n/a | n/a                   | n/a             | n/a           | n/a  | n/a   | n/a  | n/a  |

|          | Int Load <sup>2</sup>                                                                                                                                                                          | n/a            | n/a             | N   | N+1                   | N+1             | N             | N    | N     | N    | N    |

|          | FP Load <sup>3</sup>                                                                                                                                                                           | n/a            | n/a             | M+1 | M+2                   | M+2             | M+1           | M+1  | M+1   | M+1  | M+1  |

|          | IEU2: move_from_br, alloc                                                                                                                                                                      | n/a            | n/a             | 2   | 2                     | 3               | 2             | n/a  | n/a   | n/a  | 2    |

|          | Move to/from cr,ar <sup>4</sup>                                                                                                                                                                | n/a            | n/a             | С   | С                     | С               | С             | n/a  | n/a   | n/a  | С    |

|          | Move to pr                                                                                                                                                                                     | 1              | 0               | 2   | 2                     | 3               | 2             | n/a  | n/a   | n/a  | n/a  |

|          | Move indirect <sup>5</sup>                                                                                                                                                                     | n/a            | n/a             | D   | D                     | D               | D             | n/a  | n/a   | n/a  | D    |

On the Itanium® processor, the address computation instruction must be in an M-slot type to avoid an extra cycle of latency.

N depends upon which level of cache is hit. For the Itanium processor, N=2 for L1D, N=6 for L2, N=21 for L3. For the Itanium 2 processor, N=1 for L1D, N=5 for L2, N=(12-15) for L3. These are minimum latencies.

M depends upon which level of cache is hit. For the Itanium processor, M=8 for L2 and M=24 for L3. For the Itanium 2 processor, M=5 for L2 and M=(12-15) for L3. These are minimum latencies. The "+1" entries indicate one cycle is needed for format conversion.

Best-case values of C range from 2 to 35 cycles depending upon registers accessed. EC and LC accesses are 2 cycles. FPSR and CR accesses

are 10-12 cycles.

5. Best-case values of D range from 6 to 35 cycles depending upon indirect registers accessed; Iregs pkr and rr accesses are faster at 6 cycles.

# 2.4.3 Control Speculation

The Itanium 2 processor implements features intended to increase the performance of applications by decreasing the cost for incorrect control speculation. There are two parts of the solution for the Itanium 2 processor:

- The first part allows speculative load operations (This includes lfetch without the .fault completer.) to abort and set a NaT bit at the time of a data translation lookaside buffer (TLB) miss. In contrast, the Itanium processor would wait for the hardware page walker (HPW) operation to complete the walk before setting the NaT bit.

- The second part allows for a chk.s instruction (also for a chk.a instruction) to branch directly to the fix-up code without involving the OS. The Itanium processor faults on a chk.s or chk.a instruction and requests that the OS branch to the fix-up code.

Thus, deferrals on the Itanium 2 processor occur quickly and the branch to fix-up code occurs quickly.

The deferral at data TLB miss is turned off inside interrupt handlers (when PSR.is=1), which allows ld.s and lfetch instructions to complete a TLB walk and possibly return data. Clearing the dcr.dm bit will also prevent speculative operations from deferring at data TLB miss. Fast deferral requires the dcr.dm bit to be set. Refer to Section 5.2, "Speculative and Predicated Loads/Stores" for more information.

# 2.5 Memory Hierarchy

Both the Itanium microarchitecture and the Itanium 2 microarchitecture incorporate a three-level cache structure. In general, line sizes of the Itanium 2 processor are twice as large as those of the Itanium processor. Also, latencies of the Itanium 2 processor are shorter that those of the Itanium processor. The third-level cache (L3) of the Itanium 2 processor is smaller than that of the Itanium processor, but is on-chip and runs at a higher core frequency, which results in a much shorter latency. The Itanium 2 processor has a two-level TLB design for both instruction and data, while the Itanium processor has a single-level instruction TLB. The Itanium 2 processor's TLBs processor are larger. The following tables list some of the differences in caches and TLBs. Details can be found in Chapter 6, "Memory Subsystem."

Table 2-2. L1I Cache Differences

|               | Itanium <sup>®</sup> 2 Processor | Itanium Processor |

|---------------|----------------------------------|-------------------|

| Size          | 16 KB                            | 16 KB             |

| Line Size     | 64 bytes                         | 32 bytes          |

| Associativity | 4-way                            | 4-way             |

| Latency       | 1 cycle                          | 1 cycle           |

### Table 2-3. L1D Cache Differences

|               | Itanium <sup>®</sup> 2 Processor | Itanium Processor |

|---------------|----------------------------------|-------------------|

| Size          | 16 KB                            | 16 KB             |

| Line Size     | 64 bytes                         | 32 bytes          |

| Associativity | 4-way                            | 4-way             |

# Table 2-3. L1D Cache Differences (Cont'd)

|                | Itanium <sup>®</sup> 2 Processor    | Itanium Processor                   |  |

|----------------|-------------------------------------|-------------------------------------|--|

| Latency        | 1 cycle                             | 2 cycles                            |  |

| Write policies | Write through,<br>No write allocate | Write through,<br>No write allocate |  |

### **Table 2-4. L2 Unified Cache Differences**

|                        | Itanium <sup>®</sup> 2 Processor | Itanium Processor             |  |

|------------------------|----------------------------------|-------------------------------|--|

| Size                   | 256 KB                           | 96 KB                         |  |

| Line Size              | 128 bytes 64 bytes               |                               |  |

| Associativity          | 8-way                            | 6-way                         |  |

| Integer Latency        | Minimum of 5 cycles              | Minimum of 6 cycles           |  |

| Floating-point Latency | Minimum of 6 cycles              | Minimum of 9 cycles           |  |

| Write policies         | Write back,<br>Write allocate    | Write back,<br>Write allocate |  |

### **Table 2-5. L3 Cache Differences**

|                        | Itanium <sup>®</sup> 2 Processor | Itanium Processor      |

|------------------------|----------------------------------|------------------------|

| Size                   | 3 MB or 1.5 MB, on chip          | 4 MB or 2 MB, off chip |

| Line Size              | 128 bytes                        | 64 bytes               |

| Associativity          | 12-way                           | 4-way                  |

| Integer Latency        | Minimum of 12 cycles             | Minimum of 21 cycles   |

| Floating-point Latency | Minimum of 13 cycles             | Minimum of 24 cycles   |

| Bandwidth              | 32 bytes/cycle                   | 16 bytes/cycle         |

### **Table 2-6. Instruction TLB Differences**

|               | Itanium <sup>®</sup> 2 Processor | Itanium Processor |  |

|---------------|----------------------------------|-------------------|--|

| Hierarchy     | 2 levels: L1 ITLB, L2 ITLB       | 1 level: ITLB     |  |

| Size          | 32-entry, 128-entry              | 64-entry          |  |

| Associativity | Full, Full                       | Full              |  |

### **Table 2-7. Data TLB Differences**

|                                      | Itanium <sup>®</sup> 2 Processor | Itanium Processor          |

|--------------------------------------|----------------------------------|----------------------------|

| Hierarchy                            | 2 levels: L1 DTLB, L2 DTLB       | 2 levels: L1 DTLB, L2 DTLB |

| Size                                 | 32-entry, 128-entry              | 32-entry, 96-entry         |

| Associativity                        | Full, Full                       | Direct, Full               |

| Penalty for missing first level DTLB | 2 cycles                         | 10 cycles                  |

# 2.6 Branch Prediction

The major differences in the Itanium 2 processor and the Itanium processor branch prediction support are:

- Latencies

- brp instructions are ignored for branch prediction, i.e. the brp. imp is not required to achieve zero-bubble branches.

- Indirect branch targets are predicted from the source branch register rather than from a hardware table.

- Possible reduced prediction of BBB bundles due to prediction encoding.

- More robust method for prediction structure repair after a mispredicted return.

- Hardware implementation of the brl (64-bit relative branch) instruction.

- Setting ar.ec = 1 is not required for perfect loop prediction.

Full details can be found in Section 7, "Branch Instructions and Branch Prediction."

**Table 2-8. Branch Prediction Latencies (in cycles)**

|                                              | Itanium <sup>®</sup> 2 Processor | Itanium <sup>®</sup> Processor |

|----------------------------------------------|----------------------------------|--------------------------------|

| Correctly predicted taken IP-relative branch | 0                                | 1                              |

| Correctly predicted taken indirect branch    | 2                                | 0                              |

| Correctly predicted taken return branch      | 1                                | 1                              |

| Last branch in perfect loop prediction       | 0                                | 2                              |

| Misprediction latency                        | 6+                               | 9                              |

# 2.7 Instruction Prefetching

The Itanium 2 processor has an improved implementation of streaming and hint prefetching. See Chapter 8, "Instruction Prefetching" for more details.

# Functional Units and Issue Rules

3

This chapter describes the number and type of available functional units, instruction issue rules, and heuristics for efficient instruction scheduling based upon machine resources and issue rules.

## 3.1 Execution Model

The Itanium 2 processor issues and executes instructions in assembly order, so programmer understanding of stall conditions is essential for generating high performance assembly code.

In general, when an instruction does not issue at the same time as the instruction immediately before it, instruction execution is said to have *split issue*. When a split issue condition occurs, all instructions after the split point stall one or more clocks, even if there are sufficient resources for some of them to execute. Common causes of split issue in the Itanium 2 processor are:

- An explicit stop is encountered.

- There are insufficient machine resources of the type required to execute an instruction.

- Instructions have not been placed in accordance with issue rules on the Itanium 2 processor.

The Itanium 2 processor issues instructions in the order defined by the static schedule. Care should be taken by the code generator to avoid register dependencies within an issue group. The Itanium 2 processor does not insert implicit stop bits to break WAW hazards; thus, a WAW hazard between loads and stores will result in an 8-cycle penalty if the predicates are true. Other WAW hazards, such as those due to ALU operations, will result in non-deterministic results and also consider predicates.

Once instructions are issued as a group, they will proceed as a group through the pipeline. If one instruction in the issue group has a stall condition, the whole group will stall. This stall will also stall all instructions behind it (younger) in the pipeline.

# 3.2 Number and Types of Functional Units

Although parallel instruction groups may extend over an arbitrary number of bundles and contain an arbitrary number of each instruction type, the Itanium 2 processor has finite execution resources. If a parallel instruction group contains more instructions than there are available execution units, the first instruction for which an appropriate unit cannot be found will cause a split issue and break the parallel instruction group.

The front end of the Itanium 2 processor pipeline can fetch up to two bundles per cycle and the back end of the pipeline can issue as many as two bundles per cycle. Given that there are 3 instructions per bundle, the Itanium 2 processor can be considered a six instruction issue machine. For more on details on the pipeline, see Appendix A, "Itanium® 2 Processor Pipeline."

The Itanium 2 processor has a large number of functional units of various types. This allows many combinations of instructions to be issued per cycle. Since only six instruction may issue per cycle, only a portion of the Itanium 2 processor's functional units described below will be used each cycle.

There are six general-purpose ALU units (ALU0, 1, 2, 3, 4, 5), two integer units (I0, 1), and one shift unit (ISHIFT, used for general purpose shifts and other special instructions). A maximum of six of these types of instructions can be issued per cycle.

The Data Cache Unit (DCU) contains four memory ports. Two ports are generally used for load operations; two are generally used for store operations. A maximum of four of these types of instructions can be issued per cycle. The two store ports can support a special subset of the floating-point load instructions.

There are six multimedia functional units (PALU0, 1, 2, 3, 4, 5), two parallel shift units (PSMU0, 1), one parallel multiply unit (PMUL), and one population count unit (POPCNT). These handle multimedia, parallel multiply, and the popent instruction types. At most, one pmul or popent instruction may be issued per cycle. However, the Itanium 2 processor may issue up to six PALU instructions per cycle.

There are four floating-point functional units: two FMAC units to execute floating-point multiply-adds and two FMISC units to perform other floating-point operations, such as fcmp, fmerge, etc. A maximum of two floating-point operations can be executed per cycle.

There are three branch units enabling three branches to be executed per cycle.

All of the computational functional units are fully pipelined, so each functional unit can accept one new instruction per clock cycle in the absence of other types of stalls. System instructions and access to system registers may be an exception.

# 3.3 Instruction Slot to Functional Unit Mapping

Each fetched instruction is assigned to a functional unit through an issue port. The numerous functional units share a smaller number of issue ports. There are 11 issue ports: eight for non-branch instructions and three for branch instructions. They are labeled M0, M1, M2, M3, I0, I1, F0, F1, B0, B1, and B2. The process of mapping instructions within bundles to functional units is called *dispersal*.

An instruction's type and position within the issue group define to which issue port the instruction is assigned. An instruction is mapped to a subset of the issue ports based upon the instruction type (i.e. ALU, Memory, Integer, etc.). Then, based on the position of the instruction within the instruction group presented for dispersal, the instruction is mapped to a particular issue port within that subset.

Table 3-1, "A-type Instruction Port Mapping," Table 3-2, "I-type Instruction Port Mapping," and Table 3-3, "M-type Instruction Port Mapping" show the mappings of instruction types to ports and functional units. Section 3.3.2 describes the selection of the particular port based upon instruction position.

Note: Shading in the following tables indicates the instruction type can be issued on the port(s).

A-type instructions can be issued on all M and I ports (M0-M3 and I0 and I1). I-type instructions can only issue to I0 or I1. The I ports are asymmetric so some I-type instructions can only issue on port I0. M ports have many asymmetries: some M-type instructions can issue on all ports; some can only issue on M0 and M1; some can only issue on M2 and M3; some can only issue on M0; some can only issue on M2.

**Table 3-1. A-type Instruction Port Mapping**

| Instruction<br>Type | Description      | Examples        | Ports         |  |  |

|---------------------|------------------|-----------------|---------------|--|--|

| A1-A5               | ALU              | add, shladd     | M0-M3, I0, I1 |  |  |

| A4, A5              | Add Immediate    | addp4, addl     | M0-M3, I0, I1 |  |  |

| A6,A7,A8            | Compare          | cmp, cmp4       | M0-M3, I0, I1 |  |  |

| A9                  | MM ALU           | pcmp[1   2   4] | M0-M3, I0, I1 |  |  |

| A10                 | MM Shift and Add | pshladd2        | M0-M3, I0, I1 |  |  |

**Table 3-2. I-type Instruction Port Mapping**

| Instruction | Description               | Examples                                             | I Port |    |  |

|-------------|---------------------------|------------------------------------------------------|--------|----|--|

| Туре        | Type                      |                                                      | 10     | I1 |  |

| I1          | MM Multiply/Shift         | pmpy2.[l   r],<br>pmpyshr2{.u}                       |        |    |  |

| 12          | MM Mix/Pack               | mix[1   2   4].[l   r<br>pmin, pmax                  |        |    |  |

| 13, 14      | MM Mux                    | mux1, mux2                                           |        |    |  |

| 15          | Variable Right Shift      | shr{.u] =ar,ar<br>pshr[2   4] =ar,ar                 |        |    |  |

| 16          | MM Right Shift Fixed      | pshr[2   4] =ar,c                                    |        |    |  |

| 17          | Variable Left Shift       | shl{.u] =ar,ar<br>pshl[2   4] =ar,ar                 |        |    |  |

| 18          | MM Left Shift Fixed       | pshl[2   4] =ar,c                                    |        |    |  |

| 19          | MM Popcount               | popcnt                                               |        |    |  |

| I10         | Shift Right Pair          | shrp                                                 |        |    |  |

| I11-I17     | Extr, Dep<br>Test Nat     | extr{.u}, dep{.z}<br>tnat                            |        |    |  |

| I19         | Break, Nop                | break.i, nop.i                                       |        |    |  |

| 120         | Integer Speculation Check | chk.s.i                                              |        |    |  |

| 121-28      | Move to/from BR/PR/IP/AR  | mov =[br   pr   ip   ar]<br>mov [br   pr   ip   ar]= |        |    |  |

| 129         | Sxt/Zxt/Czx               | sxt, zxt, czx                                        |        |    |  |

**Table 3-3. M-type Instruction Port Mapping**

| Instruction | Description                  | Evennles                      | Memory Port |    |    |    |  |

|-------------|------------------------------|-------------------------------|-------------|----|----|----|--|

| Type        | Description                  | n Examples                    |             | M1 | M2 | M3 |  |

| M1, 2, 3    | Integer Load                 | ldsz, ld8.fill                |             |    |    |    |  |

| M4, 5       | Integer Store                | stsz, st8.spill               |             |    |    |    |  |

| M6, 7, 8    | Floating-point Load          | ldffsz, ldffsz.s, ldf.fill    |             |    |    |    |  |

|             | Floating-point Advanced Load | ldffsz.a, ldffsz.c.[clr   nc] |             |    |    |    |  |

| M9, 10      | Floating-point Store         | stffsz, stf.spill             |             |    |    |    |  |

**Table 3-3. M-type Instruction Port Mapping (Cont'd)**

| Instruction | Decemention                    | Evenules                                            | Memory Port |    |    |    |  |

|-------------|--------------------------------|-----------------------------------------------------|-------------|----|----|----|--|

| Туре        | Description                    | Examples                                            | MO          | M1 | M2 | М3 |  |

| M11, 12     | Floating-point Load Pair       | ldfpfsz                                             |             |    |    |    |  |

| M13, 14, 15 | Line Prefetch                  | lfetch                                              |             |    |    |    |  |

| M16         | Compare and Exchange           | cmpxchgsz.[acq   rel]                               |             |    |    |    |  |

| M17         | Fetch and Add                  | fetchaddsz.[acq   rel]                              |             |    |    |    |  |

| M18         | Set Floating-point Reg         | setf.[s   d   exp   sig}                            |             |    |    |    |  |

| M19         | Get Floating-point Reg         | getf.[s   d   exp   sig}                            |             |    |    |    |  |

| M20, 21     | Speculation Check              | chk.s{.m}                                           |             |    |    |    |  |

| M22, 23     | Advanced Load Check            | chk.a[clr   nc]                                     |             |    |    |    |  |

| M24         | Invalidate ALAT                | invala                                              |             |    |    |    |  |

|             | Mem Fence, Sync, Serialize     | fwb, mf{.a}, srlz.[d   i],<br>sync.li               |             |    |    |    |  |

| M25         | RSE Control                    | flushrs, loadrs                                     |             |    |    |    |  |

| M26, 27     | Invalidate ALAT                | invala.e                                            |             |    |    |    |  |

| M28         | Flush Cache, Purge TC Entry    | fc, ptc.e                                           |             |    |    |    |  |

| M29, 30, 31 | Move to/from App Reg           | mov{.m} <i>ar</i> =<br>mov{.m} = <i>ar</i>          |             |    |    |    |  |

| M32, 33     | Move to/from Control Reg       | mov <i>cr</i> =, mov = <i>cr</i>                    |             |    |    |    |  |

| M34         | Allocate Register Stack Frame  | alloc                                               |             |    |    |    |  |

| M35, 36     | Move to/from Proc. Status Reg  | mov psr.[l   um]<br>mov =psr.[l   m]                |             |    |    |    |  |

| M37         | Break, Nop.m                   | break.m, nop.m                                      |             |    |    |    |  |

| M38, 39, 40 | Probe Access                   | probe.[r   w].{fault}                               |             |    |    |    |  |

| M41         | Insert Translation Cache       | itc.[d   i]                                         |             |    |    |    |  |

| M42, 43     | Move Indirect Reg<br>Insert TR | mov <i>ireg</i> =, move = <i>ireg</i> , itr.[d   i] |             |    |    |    |  |

| M44         | Set/Reset User/System Mask     | sum, rum, ssm, rsm                                  |             |    |    |    |  |

| M45         | Purge Translation Cache/Reg    | ptc.[d   i   g   ga]                                |             |    |    |    |  |

| M46         | Virtual Address Translation    | tak, thash, tpa, ttag                               |             |    |    |    |  |

# 3.3.1 Execution Width

When dispersing instructions to functional units, the Itanium 2 processor views, at most, two bundles at a time with no special alignment requirements. This text refers to these bundles as the *first* and *second* bundles. A *bundle rotation* causes new bundles to be brought into the two-bundle window of instructions being considered for issue. Bundle rotations occur when all the instructions within a bundle are issued. Either one or two bundles can be rotated depending on how many instructions were issued.

# 3.3.2 Dispersal Rules

The Itanium 2 processor hardware makes no attempt to reorder instructions to avoid stalls. Thus, the code generator must be careful about the number, type, and order of instructions within a parallel instruction group to avoid unnecessary stalls. The use of predicates has no effect on dispersal – all instructions are dispersed in the same fashion whether predicated true, predicated false, or unpredicated. Similarly, nop instructions are dispersed to functional units as if they were normal instructions. The dispersal rules for execution units vary according to slot type; i.e. I, M, F, B, or L. The rules for the different slot types are described below.

### Dispersal rules for F slot instructions:

- An F slot instruction in the first bundle maps to F0.

- An F slot instruction in the second bundle maps to F1.

- A SIMD FP instruction essentially maps to both F0 and F1. See Section 3.3.3 for more information on SIMD FP issue rules.

### Dispersal rules for B slot instructions:

- Each B slot instruction in an MBB or BBB bundle maps to the corresponding B unit. That is, a B slot instruction in the first position of the template is mapped to B0; in the second position, it is mapped to B1; and in the third position, it is mapped to B2.

- The B instruction in an MIB/MFB/MMB bundle maps to B0 if it is a brp or nop. b and it is the first bundle, otherwise it maps to B2.

- For purposes of dispersal, break.b is treated like a branch.

### Dispersal rules for L slot instructions:

• An MLX bundle uses ports equivalent to an MFI bundle. If the MLX bundle is the first bundle, the L slot instruction maps to F0. Otherwise, it maps to F1. However, there is no conflict when the MLX template is issued with an MMF or MIF bundle and the F op is a SIMD FP instruction.

### Dispersal rules for I slot instructions:

- The instruction in the first I slot of the two-bundle issue group will issue to I0. The second I slot instruction will issue to I1.

- If the second I slot instruction can only map to an I0 port, see Table 3-2, an implicit stop will be inserted and the second I slot instruction will be issued in the next cycle. Thus, an I0-only instruction should be placed in the first I slot of a bundle pair. Only one I0-only instruction can be issued per cycle.

- An instruction in an I slot will not necessarily be issued to an I port. If the first two I slot instructions have been issued to the I ports, and an additional I slot instruction in the issue group contains A-type instructions as listed in Table 3-1, and M ports are available; these instructions will be mapped to available M ports. This allows the potential dual issue of the MII-MII bundle pair. This is new to the Itanium 2 processor and is not true on the Itanium processor.

- For the MLI template, the I slot instruction is always assigned to port I0 if it is in the first bundle or it is assigned to port I1 if it is in the second bundle. Thus, the bundle pair MII-MLI can never dual issue.

Dispersal rules for M slot instructions: