### Pentium<sup>®</sup> Processor Family Developer's Manual

### Volume 2: 82496/82497/82498 Cache Controller and 82491/82492/82493 Cache SRAM

NOTE: The Pentium® Processor Family Developer's Manual consists of three books: Pentium® Processor Order Number 241428; the 82496/82497/82498 Cache Controller and 82491/82492/82493 Cache SRAM, Order Number 241429; and the Architecture and Programming Manual, Order Number 241430. Please refer to all three volumes when evaluating your design needs.

1995

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The Pentium® processor may contain design defects or errors known as errata. Current characterized errata are available on request.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION 1996

### 82496 CACHE CONTROLLER AND 82491 CACHE SRAM FOR USE WITH THE PENTIUM PROCESSOR (510\60, 567\66)

- High Performance Second Level Cache

- Zero Wait States at 66 MHz

- Two-Way Set Associative

- Writeback with MESI Protocol

- Concurrent CPU Bus and Memory Bus Operation

- Boundary Scan

- Pentium<sup>™</sup> Processor (510\60, 567\66)

- Chip Set Version of Pentium™ Processor (510\60, 567\66)

- Superscalar Architecture

- Enhanced Floating Point

- On-Chip 8K Code and 8K Data Caches

- See Pentium<sup>™</sup> Processor Family Data Book for More Information

- Highly Flexible

- 256K to 512K with Parity

- 32-, 64-, or 128-Bit Wide Memory Bus

- Synchronous, Asynchronous and Strobed Memory Bus Operation

- Selectable Bus Widths, Line Sizes, Transfers and Burst Orders

- Full Multiprocessing Support

- Concurrent CPU, Memory Bus and Snoop Operations

- Complete MESI Protocol

- Internal/External Parity Generation/Checking

- Supports Read For Ownership, Write-Allocation and Cache-to-Cache Transfers

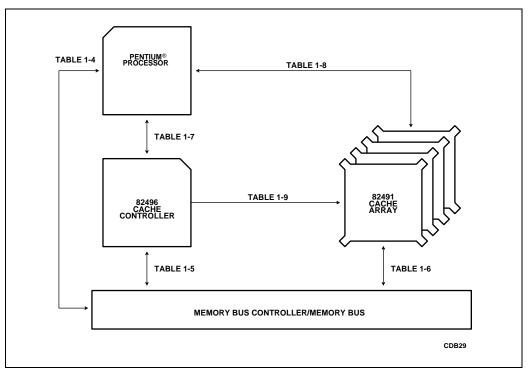

The 82496 Cache Controller and multiple 82491 Cache SRAMs combine with the Pentium processor (510\60, 567\66) to form a CPU Cache chip set designed for high performance servers and function-rich desktops. The high-speed interconnect between the CPU and cache components has been optimized to provide zero-wait state operation. This CPU Cache chip set is fully compatible with existing software, and has new data integrity features for mission critical applications.

The 82496 cache controller implements the MESI write-back protocol for full multiprocessing support. Dual ported buffers and registers allow

the 82496 to concurrently handle CPU bus, memory bus, and internal cache operation for maximum performance.

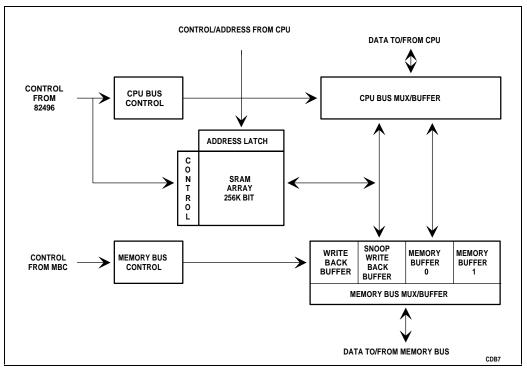

The 82491 is a customized highperformance SRAM that supports 32-, 64-, and 128-bit wide memory bus widths, 16-, 32-, and 64-byte line sizes, and optional sectoring. The data path between the CPU bus and memory bus is separated by the 82491, allowing the CPU bus to handshake synchronously, asynchronously, or with a strobed protocol, and allowing concurrent CPU bus and memory bus operations.

### 82497 CACHE CONTROLLER and 82492 CACHE SRAM FOR USE WITH THE PENTIUM<sup>®</sup> PROCESSOR (735\90, 815\100, 1000\120, 1110\133)

- High Performance Second Level Cache Zong weit states at CC Mbr.

- Zero wait states at 66 Mhz

- Two-way set associative

- Writeback with MESI protocol

- Concurrent CPU bus and memory bus operation

- Boundary scan

- Pentium<sup>®</sup> Processor (735\90, 815\100, 1000\120, 1110\133) cache chip set

- Chip set version of Pentium<sup>®</sup>

Processor (735\90, 815\100, 1000\120, 1110\133)

- Superscalar architecture

- Enhanced floating point

- On-chip 8K code and 8K data caches

- See Pentium<sup>™</sup> Processor Family Data Book for more information

- Highly Flexible

- 256K to 512K with parity

- 32-, 64-, or 128-bit wide memory bus

- Synchronous, asynchronous, and strobed memory bus operation

- Selectable bus widths, line sizes, transfers and burst orders

- Full Multiprocessing Support

- Concurrent CPU, memory bus and snoop operations

- Complete MESI protocol

- Internal/external parity

- generation/checking — Supports read for ownership,writeallocation and cache-to-cache transfers

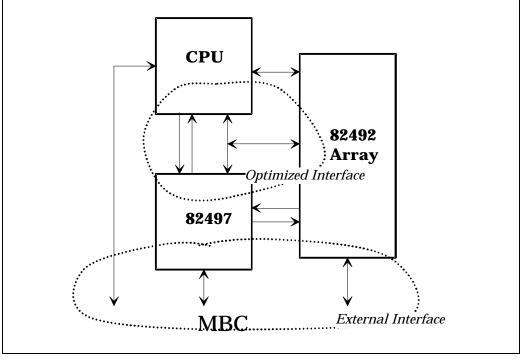

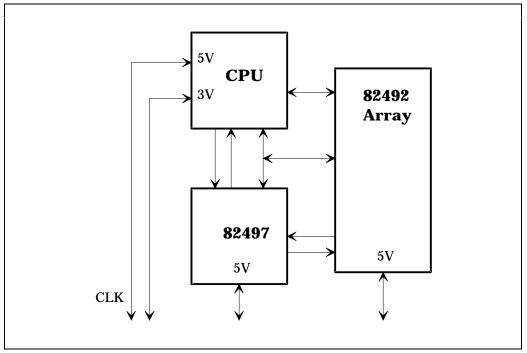

The 82497 Cache Controller with multiple 82492 Cache SRAMs combine with the Pentium<sup>®</sup> processor (735\90, 815\100, 1000\120, 1110\133) to form a CPU cache chip set designed for high performance servers and function-rich desktops. The high-speed interconnect between the CPU and cache components has been optimized to provide zero-wait state operation. This CPU cache chip set is fully compatible with existing software, and has data integrity features for mission critical applications.

The 82497 Cache Controller implements the MESI write-back protocol for full multiprocessing support. Dual ported buffers and registers allow the 82497 to concurrently handle CPU bus, memory bus, and internal cache operation for maximum performance.

The 82492 is a customized high SRAM performance that supports 32-, 64-, and 128-bit wide memory bus widths, 16-, 32-, and 64-byte line sizes, and optional sectoring. The data path between the CPU bus and the memory bus is separated by the 82492, allowing the CPU bus to handshake synchronously, asynchronously, or with a strobed protocol, and allowing concurrent CPU bus and memory bus operations.

### 82498 CACHE CONTROLLER and 82493 CACHE SRAM FOR USE WITH THE PENTIUM® PROCESSOR (735\90, 815\100, 1000\120, 1110\133)

- High Performance Second Level Cache

- Zero wait states at 60 and 66Mhz

- Two-way set associative

- Writeback with MESI protocol

- Concurrent CPU bus and memory bus operations

- Boundary scan

- Enhanced lock functionality

- Pentium Processor (735\90, 815\100, 1000\120, 1110\133) cache chip set

- Superscalar architecture

- Enhanced floating point

- On-chip 8K code and 8K data caches

- See Pentium® Processor Family Data Book for more information

- Highly Flexible

- 1Mbyte or 2Mbyte with parity

- 32-, 64-, and 128-bit wide memory bus

- Synchronous, asynchronous, and strobed memory bus operation

- Selectable bus widths, line sizes, transfers and burst orders

- Full Multiprocessing Support

- Concurrent CPU, memory bus and snoop operations

- Complete MESI protocol

- Internal/external parity generation/checking

- Supports read for ownership,writeallocation and cache-to-cache transfers

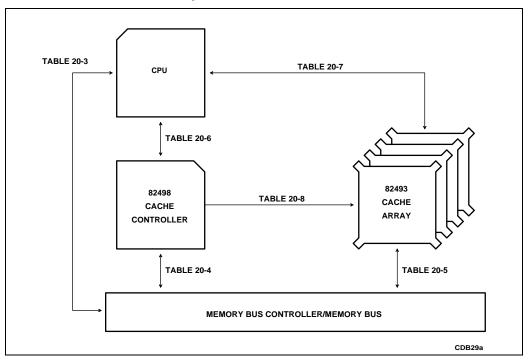

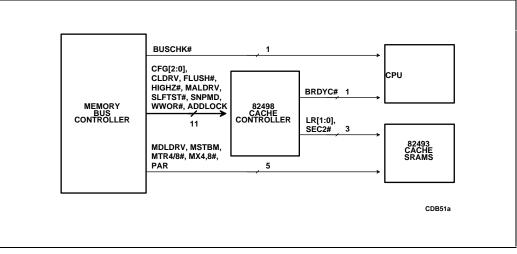

The 82498 Cache Controller and multiple 82493 Cache SRAMs combine with the Pentium<sup>®</sup> processor (735\90, 815\100, 1000\120, 1110\133) to form a CPU cache chip set designed for high performance servers and function-rich desktops. The 82498 Cache Controller and 82493 Cache SRAM are an enhanced version of the 82497/82492 cache solution. Additional performance is realized through higher density 1Mbyte and 2Mbyte support and improved lock functionality. The high-speed interconnect between the CPU and cache components has been optimized to provide zero-wait state operation. This CPU cache chip set is fully compatible with existing software, and has new data integrity features for mission critical applications.

The 82498 Cache Controller implements the MESI write-back protocol for full multiprocessing support. Dual ported buffers and registers allow the 82498 to concurrently handle CPU bus. memory bus, and internal cache operation for maximum performance.

The 82493 is a customized high performance SRAM that supports 32-, 64-, and 128-bit wide memory bus widths, 16-, 32-, and 64-byte line sizes, and optional sectoring. The data path between the CPU bus and the memory bus is separated by the 82493 Cache SRAM, allowing the CPU bus to handshake synchronously, asynchronously, or with a strobed protocol, and allowing concurrent CPU bus and memory bus operations.

### TABLE OF CONTENTS

### PART I — 82496 Cache Controller and 82491 Cache SRAM

#### CHAPTER 1 PINOUTS

intel

#### Page

| 1.1.   | PINOUT DIAGRAMS                        |      |

|--------|----------------------------------------|------|

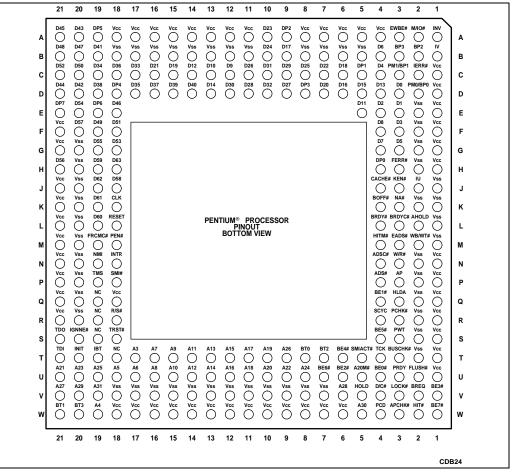

|        | Pentium <sup>®</sup> Processor Pinouts |      |

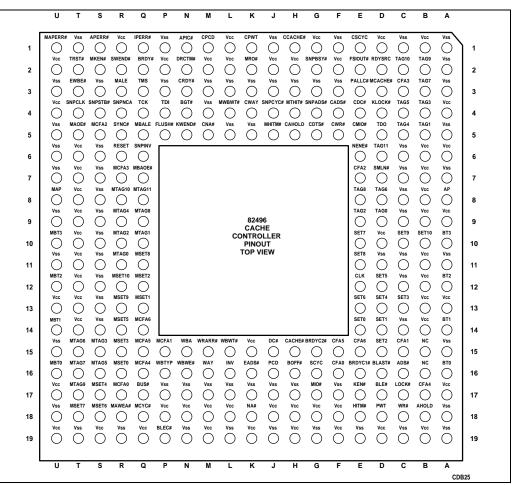

| 1.1.2. | 82496 Cache Controller Pinouts         | 1-3  |

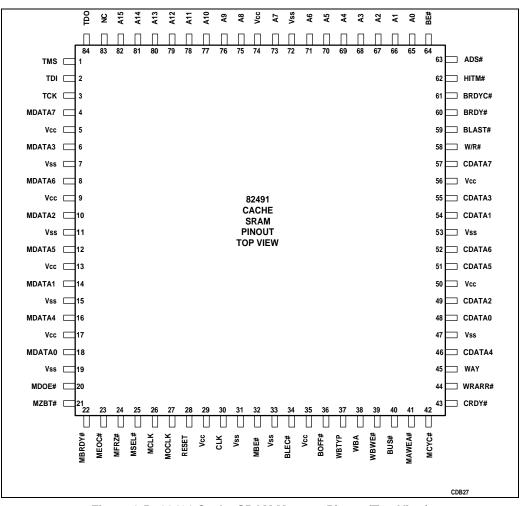

| 1.1.3. | 82491 Cache SRAM Memory Pinouts        |      |

| 1.2.   | PIN CROSS REFERENCE TABLES             | 1-7  |

| 1.2.1. | Pentium <sup>®</sup> Processor         | 1-7  |

| 1.2.2. | 82496 Cache Controller                 | 1-9  |

|        | 82491 Cache SRAM                       |      |

| 1.3.   | BRIEF PIN DESCRIPTIONS                 | 1-12 |

#### **CHAPTER 2**

#### CACHE ARCHITECTURE OVERVIEW

| 2.1. MAIN FEATURES                                   |                 |

|------------------------------------------------------|-----------------|

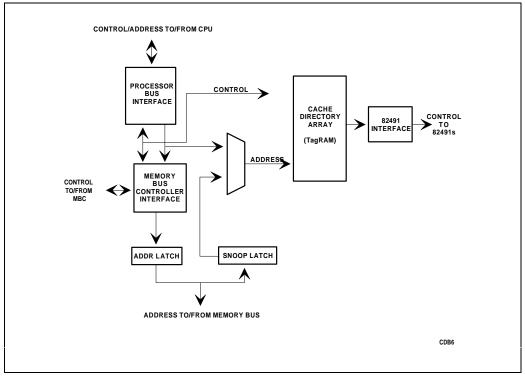

| 2.2. CPU/CACHE CORE DESCRIPTION                      |                 |

| 2.2.1. 82496 Cache Controller                        |                 |

| 2.2.2. 82491 Cache SRAMs                             |                 |

| 2.2.3. Memory Bus Controller                         |                 |

| 2.3. CONFIGURATION                                   |                 |

| 2.3.1. Physical Cache                                |                 |

| 2.3.2. Snoop Modes                                   |                 |

| 2.3.2.1. SYNCHRONOUS SNOOP MODE                      |                 |

| 2.3.2.2. CLOCKED (ASYNCHRONOUS) SNOOP MODE .         |                 |

| 2.3.2.3. STROBED SNOOP MODE                          |                 |

| 2.3.3. Memory Bus Modes                              |                 |

| 2.3.3.1. CLOCKED MEMORY BUS MODE                     |                 |

| 2.3.3.2. STROBED MEMORY BUS MODE                     |                 |

| 2.4. PENTIUM® PROCESSOR BUS INTERFACE                |                 |

| 2.5. 82496 Cache Controller/82491 Cache SRAM OPTIMIZ | ED INTERFACE2-8 |

| 2.6. MEMORY BUS INTERFACE                            |                 |

| 2.6.1. Snooping Logic                                |                 |

| 2.6.2. Cycle Control Logic                           |                 |

| 2.7. TEST                                            |                 |

| CHAP    | PTER 3                                                                          |      |

|---------|---------------------------------------------------------------------------------|------|

| COMF    | PONENT OPERATION                                                                | Page |

| 3.1.    | WRITETHROUGH CACHE DESIGNS                                                      | 3-1  |

| 3.2.    | WRITEBACK CACHE DESIGNS                                                         | 3-1  |

| 3.3.    | 82496 CACHE CONTROLLER CACHE CONSISTENCY PROTOCOL                               | 3-2  |

| 3.4.    | MESI CACHE CONSISTENCY PROTOCOL MODEL                                           | 3-2  |

| 3.5.    | BASIC MESI STATE TRANSITIONS                                                    |      |

| 3.5.1.  | MESI State Changes Resulting from CPU Bus Operations                            | 3-5  |

| 3.5.1.1 | READ HIT                                                                        | 3-5  |

| 3.5.1.2 | 2. READ MISS                                                                    | 3-6  |

| 3.5.1.3 | B. WRITE HIT                                                                    | 3-6  |

| 3.5.1.4 |                                                                                 |      |

| 3.5.1.5 |                                                                                 |      |

| 3.5.2.  | MESI State Changes Resulting from Memory Bus Masters                            |      |

| 3.5.2.1 |                                                                                 |      |

| 3.5.2.2 |                                                                                 | 3-8  |

| 3.6.    | MESI STATE CHANGES FOLLOWING CYCLES WITH SPECIAL ATTRIBUTES.                    |      |

| 3.6.1.  | Cacheability Attributes: PCD, MKEN#                                             | 3-8  |

| 3.6.2.  | Writethrough Protocol: PWT, MWB/WT#                                             |      |

| 3.6.3.  | Read Only Accesses: MRO#                                                        | 3-9  |

| 3.6.4.  | Locked Accesses: LOCK#                                                          | 3-10 |

| 3.6.5.  | Direct-To-Modified Attribute: DRCTM#                                            |      |

| 3.7.    | STATE TRANSITIONS                                                               |      |

| 3.7.1.  | CPU Bus Signals                                                                 |      |

| 3.7.2.  | Memory Bus Signals                                                              | 3-11 |

| 3.7.3.  | Tag State and Cycles Resulting from State Transitions                           |      |

| 3.7.3.1 |                                                                                 |      |

| 3.7.3.2 |                                                                                 |      |

| 3.7.4.  | MESI State Tables (82496 Cache Controller State Changes)                        | 3-14 |

| 3.8.    | PRIMARY TO SECONDARY CACHE COHERENCY                                            |      |

| 3.8.1.  | Inclusion                                                                       | 3-17 |

| 3.8.2.  | Inquire and Back-Invalidation Cycles                                            | 3-18 |

| 3.8.3.  | Write Once Policy                                                               | 3-19 |

| 3.8.4.  | MESI State Tables (Pentium <sup>®</sup> Processor Cache Chip Set State Changes) | 3-19 |

| CHAP    | PTER 4                                                                          |      |

| CACH    | E INITIALIZATION AND CONFIGURATION                                              |      |

| 4.1.    | CONFIGURATION SIGNAL SAMPLING DURING RESET                                      | 4-2  |

| 4.1.1.  | Initialization Required for Chip Set Mode                                       |      |

| 4.2.    | PHYSICAL CACHE                                                                  | 4-4  |

| ┯.∠.    |                                       | ······································ |

|---------|---------------------------------------|----------------------------------------|

| 4.2.1.  | Memory Bus Width                      |                                        |

| 4.2.2.  | Line Ratio                            |                                        |

| 4.2.3.  | TagRAM Size                           |                                        |

| 4.2.4.  | TagRAM Structure                      |                                        |

| 4.2.5.  | Lines per Sector (L/S)                |                                        |

| 4.2.6.  | Cache Size                            |                                        |

| 4.2.7.  | Configurable Address Connections      |                                        |

| 4.2.8.  | 82491 Cache SRAM Bus Configuration    |                                        |

| 4.2.9.  | 82491 Cache SRAM Parity Configuration |                                        |

| 4.2.10. |                                       |                                        |

| 4.2.11. | Bus Driver Buffer Selection           |                                        |

| 4.3.    | CACHE MODES                           |                                        |

| 4.3.1.  | Memory Bus Modes                      |                                        |

|         |                                       |                                        |

intal

| 4.3.1.1. | CLOCKED MODE                     |  |

|----------|----------------------------------|--|

|          | STROBED MODE                     |  |

| 4.3.1.3. | CONFIGURATION OF MEMORY BUS MODE |  |

| 4.3.2.   | Snoop Modes                      |  |

| 4.3.2.1. | CONFIGURATION OF SNOOP MODE      |  |

| 4.3.3.   | Strong/Weak Write Ordering       |  |

|          | DESCRIPTION                      |  |

| 4.3.3.2. | CONFIGURATION                    |  |

|          |                                  |  |

### CHAPTER 5

#### HARDWARE INTERFACE 5.1. 5.1.1. 5.1.1.1. 5.1.1.1.1. 5.1.1.1.2. 5.1.1.1.3. Non-Cacheable Read Miss......5-8 Write Hit [E], [M]......5-8 5.1.1.1.4. 5.1.1.1.5. 5.1.1.1.6. 5.1.1.1.7. Replacement......5-9 5.1.1.1.8. 5.1.1.1.9. 5.1.1.1.10. Read For Ownership......5-10 5.1.1.1.11. 5.1.1.1.12. 5.1.1.1.13. 5.1.1.1.14. FLUSH and SYNC Cycles ......5-11 5.1.2. 5.1.2.1. Synchronous Snooping Mode......5-13 5.1.2.1.1. 5.1.2.1.2. Asynchronous Snooping Mode......5-13 5.1.2.1.3. 5.1.2.2. 5.1.2.3. 5.1.2.4. 5.1.2.5. Snooping during Split Locked Cycles ...... 5-22 5.1.2.5.1. 5.1.2.6. 5.1.3. 5.1.3.1. 5.1.3.2. 5.1.4. CPU DATA BUS TRANSFER CONTROL 5.1.4.1. Memory Bus Mode Selection ...... 5-26 5.1.5. 5.1.6. 5.1.6.1. 5.1.6.2. 5.1.6.3. 5.1.6.4. 5.1.6.5. 5.1.7.

#### CONTENTS

| 5.1.8.    | Warm Reset                                                                                                              | 5-32   |

|-----------|-------------------------------------------------------------------------------------------------------------------------|--------|

| 5.1.9.    | Handling of Large Caches/Larger Line Sizes                                                                              | 5-32   |

| 5.1.10.   | 82496 Cache Controller Guaranteed Signal Relationships                                                                  | 5-33   |

| 5.1.11.   | 82496 Cache Controller Cycle Progress Requirements                                                                      | 5-34   |

| 5.1.12.   | 82496 Cache Controller Input Signal Recognition Requirements                                                            |        |

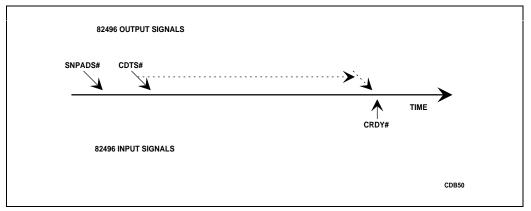

| 5.1.12.   | 82496 Cache Controller and 82491 Cache SRAM CRDY# Requirements                                                          |        |

| 5.1.13.   | 82496 Cache Controller Cycle Attribute Sampling Requirements                                                            |        |

| 5.1.14.   | Pentium <sup>®</sup> Processor, 82496 Cache Controller and 82491 Cache                                                  | . 5-55 |

| 5.1.15.   | SRAM BRDY# Requirements                                                                                                 | E 2E   |

| E 1 1 C   | 82496 Cache Controller Cycle Progress Signal Sampling Requirements                                                      | 5 26   |

| 5.1.16.   |                                                                                                                         |        |

| 5.1.17.   | 82491 Cache SRAM Data Control Signal Requirements                                                                       | 5-37   |

| 5.1.18.   | Semaphore (Strong Write Ordering) Consistency<br>ETAILED PENTIUM <sup>®</sup> PROCESSOR CACHE CHIP SET PIN DESCRIPTIONS | . 5-37 |

|           | ETAILED PENTIUM® PROCESSOR CACHE CHIP SET PIN DESCRIPTIONS                                                              | . 5-39 |

| 5.2.1.    | Signal/Category Cross-Reference                                                                                         | 5-39   |

| 5.2.1.1.  | CONFIGURÁTION SIGNALS                                                                                                   |        |

| 5.2.1.2.  | SNOOPING SIGNALS                                                                                                        | . 5-39 |

| 5.2.1.3.  | CYCLE ATTRIBUTE/PROGRESS SIGNALS                                                                                        |        |

| 5.2.1.4.  | CYCLE CONTROL SIGNALS                                                                                                   |        |

| 5.2.1.5.  | MEMORY ADDRESS BUS AND ADDRESS CONTROL SIGNALS                                                                          |        |

| 5.2.1.6.  | MEMORY DATA BUS AND DATA CONTROL SIGNALS                                                                                | . 5-40 |

| 5.2.1.7.  | CACHE SYNCHRONIZATION SIGNALS                                                                                           | . 5-40 |

| 5.2.1.8.  | CPU SIGNALS                                                                                                             | . 5-40 |

| 5.2.1.9.  | TEST SIGNALS                                                                                                            | . 5-40 |

| 5.2.1.10. | PENTIUM® PROCESSOR BUS OPTIMIZED INTERFACE SIGNALS                                                                      | . 5-40 |

| 5.2.1.11. | 82496 CACHE CONTROLLER/82491 CACHE SRAM                                                                                 |        |

|           | OPTIMIZED INTERFACE SIGNALS.                                                                                            | . 5-40 |

| 5.2.2.    | Pentium® Processor Cache Chip Set Detailed Pin Descriptions                                                             | . 5-41 |

| 5.2.2.1.  | A[31:3]/A[15:0]                                                                                                         |        |

| 5.2.2.2.  | A20M#                                                                                                                   |        |

| 5.2.2.3.  | ADS#                                                                                                                    | 5-43   |

| 5.2.2.4.  | ADSC#                                                                                                                   | 5-44   |

| 5.2.2.5.  | AHOLD                                                                                                                   | 5-45   |

| 5.2.2.6.  | AP                                                                                                                      | 5-46   |

| 5.2.2.7.  | APCHK#                                                                                                                  | 5-47   |

| 5.2.2.8.  | APERR#                                                                                                                  |        |

| 5.2.2.9.  | APIC#                                                                                                                   |        |

| 5.2.2.10. | BE#,BE[7:0]#                                                                                                            |        |

| 5.2.2.11. | BGT#                                                                                                                    |        |

| 5.2.2.12. | BLAST#                                                                                                                  |        |

| 5.2.2.13. | BLE#                                                                                                                    |        |

| 5.2.2.14. | BLEC#                                                                                                                   |        |

| 5.2.2.15. | BOFF#                                                                                                                   |        |

| 5.2.2.16. | BP[3:2], PM/BP[1:0]                                                                                                     |        |

| 5.2.2.17. | BRDY#                                                                                                                   |        |

| 5.2.2.18. | BRDYC#                                                                                                                  |        |

| 5.2.2.19. | BRDYC1#                                                                                                                 |        |

| 5.2.2.19. | BRDYC2#                                                                                                                 |        |

| 5.2.2.20. | BREQ                                                                                                                    |        |

| 5.2.2.21. | BT[3:0]                                                                                                                 |        |

| 5.2.2.23  | B1[5:0]<br>BUS#                                                                                                         | 5-66   |

| 5.2.2.23. | BUSCHK#                                                                                                                 |        |

| 0.2.2.24. |                                                                                                                         | 0-07   |

| 5.2.2.25. | CACHE#                       | . 5-68 |

|-----------|------------------------------|--------|

| 5.2.2.26. | CADS#                        | 5-69   |

| 5.2.2.27. | CAHOLD                       | .5-71  |

| 5.2.2.28. | CCACHE#                      | 5-72   |

| 5.2.2.29. | CD/C#                        |        |

| 5.2.2.30. | CDATA[7:0]                   |        |

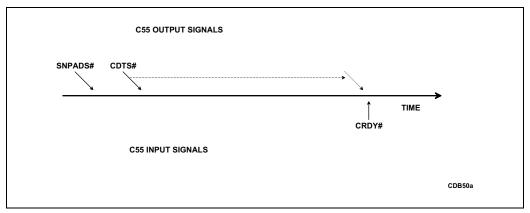

| 5.2.2.31. | CDTS#                        |        |

| 5.2.2.32. | CFA[6:0],SET[10:0],TAG[11:0] |        |

| 5.2.2.33. | CFG[2:0]                     |        |

| 5.2.2.34. | CLDRV                        |        |

| 5.2.2.35. | CLK                          |        |

| 5.2.2.36. | CM/IO#                       |        |

| 5.2.2.37. | CNA#                         |        |

| 5.2.2.38. | CPCD                         |        |

| 5.2.2.39. | CPWT                         |        |

| 5.2.2.40. | CRDY#                        |        |

| 5.2.2.41. | CSCYC                        |        |

| 5.2.2.42. | CW/R#                        |        |

| 5.2.2.43. | CWAY                         |        |

| 5.2.2.43. | D/C#                         |        |

| 5.2.2.44. | D/C#<br>D[63:0]              |        |

| 5.2.2.45. | D[63.0]<br>DP[7:0]           |        |

| 5.2.2.40. | DF[7.0]<br>DRCTM#            |        |

| •         |                              |        |

| 5.2.2.48. |                              |        |

| 5.2.2.49. | EWBE#                        |        |

| 5.2.2.50. | FERR#                        |        |

| 5.2.2.51. | FLUSH#                       |        |

| 5.2.2.52. | FRCMC#                       |        |

| 5.2.2.53. | FSIOUT#                      |        |

| 5.2.2.54. | HIGHZ#                       |        |

| 5.2.2.55. | HIT#                         |        |

| 5.2.2.56. | HITM#                        |        |

| 5.2.2.57. | HLDA                         |        |

| 5.2.2.58. | HOLD                         |        |

| 5.2.2.59. | IBT                          |        |

| 5.2.2.60. | IERR#                        |        |

| 5.2.2.61. | IGNNE#                       |        |

| 5.2.2.62. | INIT                         |        |

| 5.2.2.63. | INTR                         |        |

| 5.2.2.64. | INV                          |        |

| 5.2.2.65. | IPERR#                       | 5-114  |

| 5.2.2.66. | IU                           | 5-115  |

| 5.2.2.67. | IV                           | 5-116  |

| 5.2.2.68. | KEN#                         | 5-117  |

| 5.2.2.69. | KLOCK#                       | 5-119  |

| 5.2.2.70. | KWEND#                       | 5-121  |

| 5.2.2.71. | LOCK#                        |        |

| 5.2.2.72. | LR[1:0]                      | 5-124  |

| 5.2.2.73. | M/IO#                        |        |

| 5.2.2.74. | MALDRV                       |        |

| 5.2.2.75. | MALE                         | 5-127  |

| 5.2.2.76. | MAOE#                        |        |

|           |                              |        |

#### CONTENTS

| 5.2.2.77.  | MAP                               | 5-1 | 30 |

|------------|-----------------------------------|-----|----|

| 5.2.2.78.  | MAPERR#                           | 5-1 | 32 |

| 5.2.2.79.  | MAWEA#                            |     |    |

| 5.2.2.80.  | MBALE                             |     |    |

| 5.2.2.81.  | MBAOE#                            | -   |    |

| 5.2.2.82.  | MBE#                              |     |    |

| 5.2.2.83.  | MBRDY#                            | -   |    |

| 5.2.2.84.  | MBT[3:0]                          |     |    |

| 5.2.2.85.  | MCACHE#                           |     |    |

| 5.2.2.86.  | MCFA[6:0], MSET[10:0], MTAG[11:0] | 5-1 | 46 |

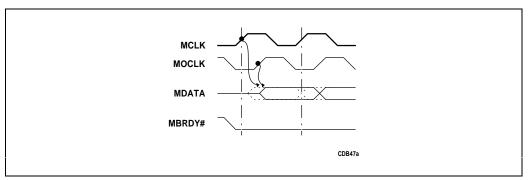

| 5.2.2.87.  | MCLK.                             | 5-1 | 48 |

| 5.2.2.88.  | MCYC#                             | 5-1 | 49 |

| 5.2.2.89.  | MDATA[7:0]                        |     |    |

| 5.2.2.90.  | MDLDRV                            |     |    |

| 5.2.2.91.  | MDOE#                             |     |    |

| 5.2.2.92.  | MEOC#                             |     |    |

| 5.2.2.93.  | ME00#                             | -   | -  |

| 5.2.2.94.  | MHTX2#<br>MHITM#                  | -   |    |

| 5.2.2.94.  | MISTB                             |     |    |

| 5.2.2.95.  | MKEN#                             | -   |    |

| 5.2.2.90.  | MOCLK                             | -   |    |

| 5.2.2.97.  | MOCLK                             |     |    |

| 5.2.2.90.  | MRO#                              | -   |    |

| 5.2.2.99.  | MRO#<br>MSEL#                     |     |    |

| 5.2.2.100. | MSEL#                             | -   |    |

| 5.2.2.101. | MISTIBM<br>MTHIT#                 | -   |    |

|            |                                   | -   |    |

| 5.2.2.103. | MTR4/8#                           |     |    |

| 5.2.2.104. | MWB/WT#                           |     |    |

| 5.2.2.105. | MX4/8#                            | -   |    |

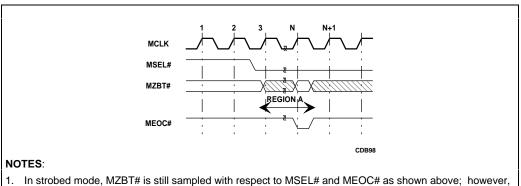

| 5.2.2.106. | MZBT#                             |     |    |

| 5.2.2.107. | NA#                               | -   | -  |

| 5.2.2.108. | NENE#                             |     |    |

| 5.2.2.109. | NMI                               |     |    |

| 5.2.2.110. | PALLC#                            | -   | -  |

| 5.2.2.111. | PAR#                              |     |    |

| 5.2.2.112. | PCD                               |     |    |

| 5.2.2.113. | PCHK#                             |     |    |

| 5.2.2.114. | PEN#                              | -   |    |

| 5.2.2.115. | PRDY                              |     |    |

| 5.2.2.116. | PWT                               | -   |    |

| 5.2.2.117. | R/S#                              | -   |    |

| 5.2.2.118. | RDYSRC                            |     |    |

| 5.2.2.119. | RESET                             | -   |    |

| 5.2.2.120. | SCYC                              |     |    |

| 5.2.2.121. | SEC2#                             |     |    |

| 5.2.2.122. | SLFTST#                           | -   | -  |

| 5.2.2.123. | SMI#                              | -   |    |

| 5.2.2.124. | SMIACT#                           |     |    |

| 5.2.2.125. | SMLN#                             |     |    |

| 5.2.2.126. | SNPADS#                           | -   |    |

| 5.2.2.127. | SNPBSY#                           |     |    |

| 5.2.2.128. | SNPCLK                            | 5-1 | 99 |

| 5.2.2.129. | SNPCYC# |       |

|------------|---------|-------|

| 5.2.2.130. | SNPINV  |       |

| 5.2.2.131. | SNPMD   |       |

| 5.2.2.132. | SNPNCA  |       |

| 5.2.2.133. | SNPSTB# |       |

| 5.2.2.134. | SWEND#  |       |

| 5.2.2.135. | SYNC#   |       |

| 5.2.2.136. | TCK     |       |

| 5.2.2.137. | TDI     | 5-212 |

| 5.2.2.138. | TDO     | 5-213 |

| 5.2.2.139. | TMS     | 5-214 |

| 5.2.2.140. | TRST#   | 5-215 |

| 5.2.2.141. | W/R#    | 5-216 |

| 5.2.2.142. | WAY     | 5-217 |

| 5.2.2.143. | WB/WT#  | 5-218 |

| 5.2.2.144. | WBA     | 5-219 |

| 5.2.2.145. | WBTYP   |       |

| 5.2.2.146. | WBWE#   | 5-221 |

| 5.2.2.147. | WRARR#  |       |

| 5.2.2.148. | WWOR#   | 5-223 |

|            |         |       |

#### CHAPTER 6

#### MEMORY BUS FUNCTIONAL DESCRIPTION

| 6.1.1.       Read Hit Cycles       6         6.1.2.       Read Miss Cycles       6         6.1.2.1.       WITH CLEAN REPLACEMENT       6 | 6-4<br>6-4 |

|------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                                                                                                                                          | 6-4        |

|                                                                                                                                          |            |

|                                                                                                                                          |            |

| 6.1.2.2. WITH REPLACEMENT OF MODIFIED LINE                                                                                               | ò-7        |

| 6.1.3. Non-Cacheable Read Miss Cycles                                                                                                    | 5-9        |

| 6.2. WRITE CYCLES                                                                                                                        |            |

| 6.2.1. Write Hit to [E] or [M] State Cycles                                                                                              | 10         |

| 6.2.2. Write Miss with No Allocation or Write Hit to [S] State Cycles                                                                    |            |

| 6.2.3. Write Miss with Allocation Cycles                                                                                                 |            |

| 6.3. LOCKED READ-MODIFY-WRITE CYCLES                                                                                                     | 16         |

| 6.4. SNOOP HIT TO [M] STATE — SYNCHRONOUS SNOOP MODE                                                                                     | 18         |

| 6.5. I/O CYCLES                                                                                                                          | 21         |

#### CHAPTER 7

#### **ELECTRICAL SPECIFICATIONS**

| 7.1.     | POWER AND GROUND                  | 7-1  |

|----------|-----------------------------------|------|

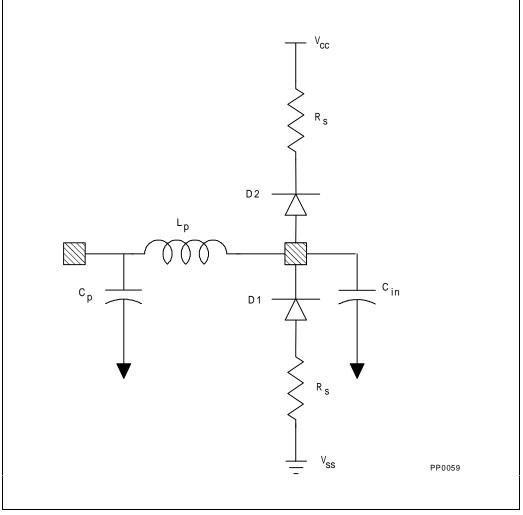

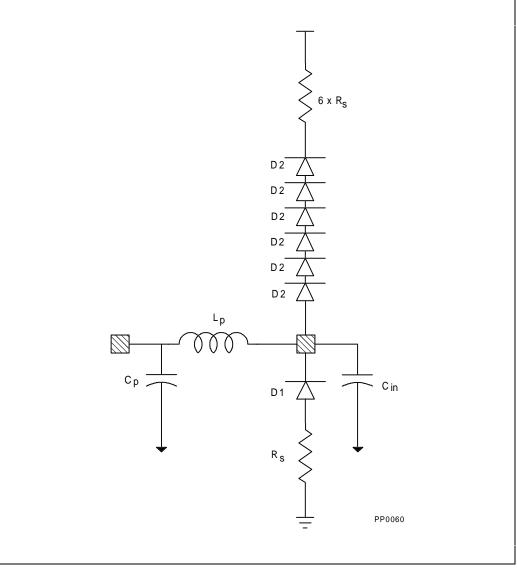

| 7.2.     | DECOUPLING RECOMMENDATIONS        | 7-1  |

| 7.3.     | CONNECTION SPECIFICATIONS         | 7-1  |

| 7.4.     | MAXIMUM RATINGS                   | 7-1  |

| 7.5.     | DC SPECIFICATIONS                 |      |

|          | AC SPECIFICATIONS                 |      |

| 7.6.1.   | Optimized Interface               | 7-4  |

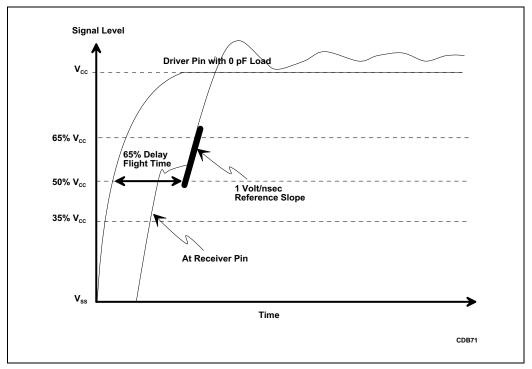

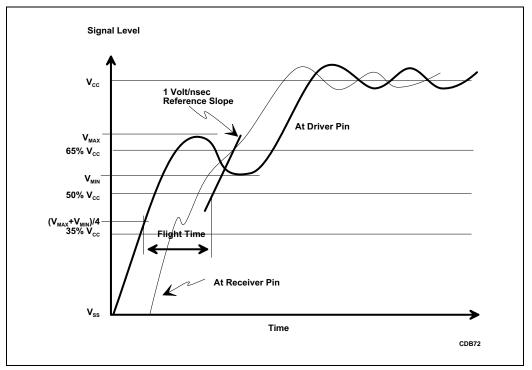

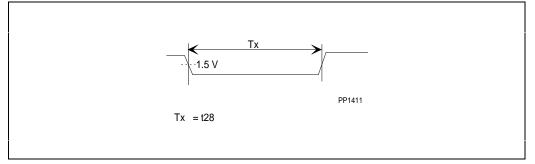

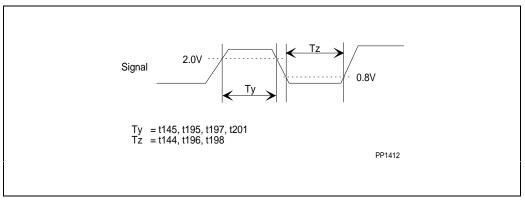

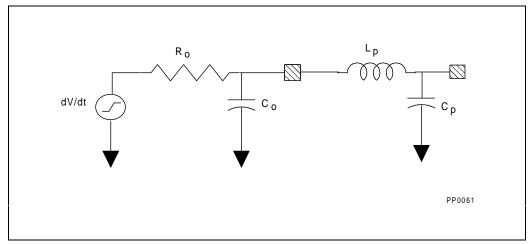

| 7.6.1.1. | FLIGHT TIME SPECIFICATION         | 7-5  |

| 7.6.1.1. | .1. 66-MHz 256-Kbyte Flight Times | 7-9  |

| 7.6.1.1. | .2. 60-MHz 256-Kbyte Flight Times | 7-12 |

| 7.6.1.1. | .3. 60-MHz 512-Kbyte Flight Times | 7-15 |

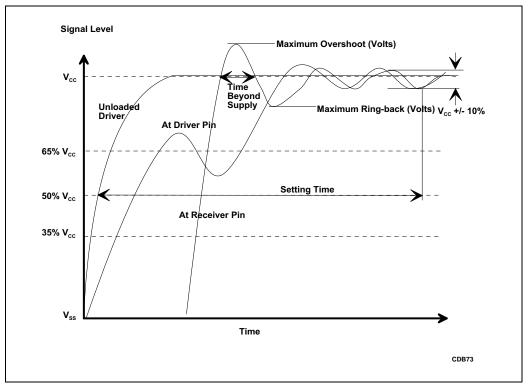

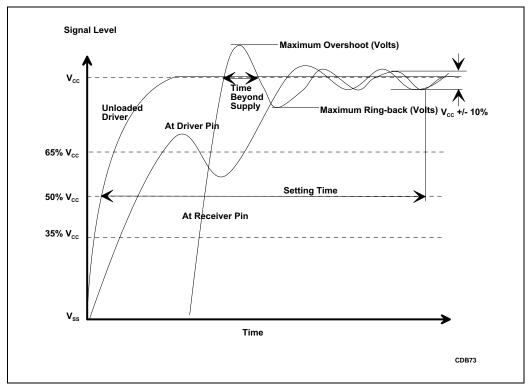

| 7.6.1.2. | . SIGNAL QUALITY                  | 7-18 |

|          |                                   |      |

| 7.6.2.   | External Interface              | 7-21 |

|----------|---------------------------------|------|

| 7.6.2.1. | 66-MHz AC SPECIFICATIONS        | 7-22 |

| 7.6.2.2. | 60-MHz AC SPECIFICATIONS        | 7-33 |

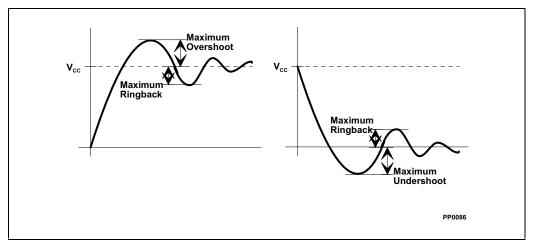

| 7.7.     | OVERSHOOT/UNDERSHOOT GUIDELINES | 7-51 |

#### **CHAPTER 8**

#### I/O BUFFER MODELS

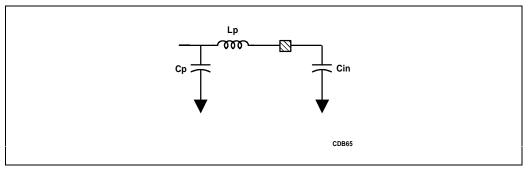

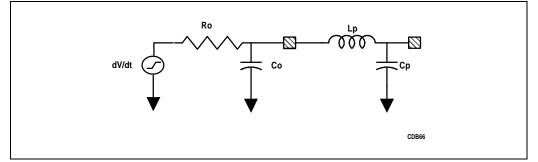

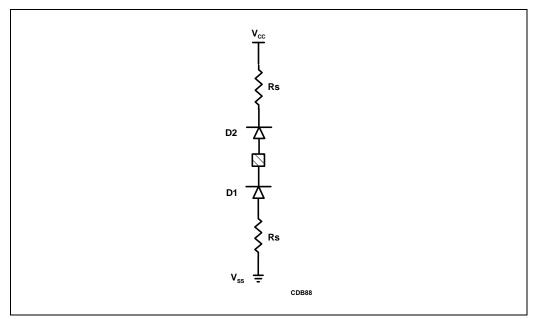

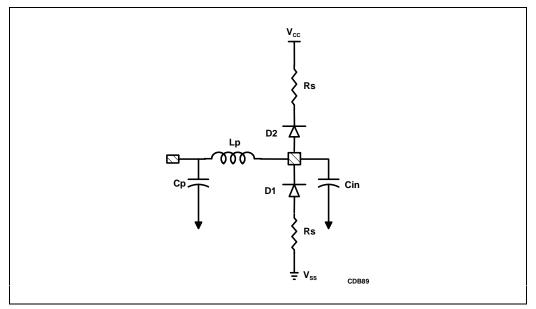

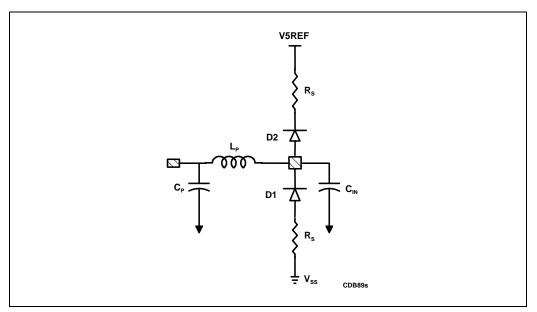

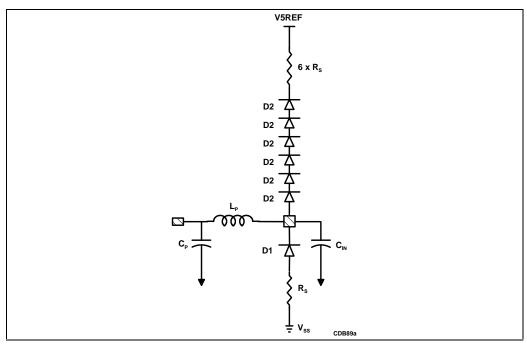

| 8.1. | OPTIMIZED INTERFACE BUFFERS | 8-2 |

|------|-----------------------------|-----|

| 8.2. | EXTERNAL INTERFACE BUFFERS  | 8-5 |

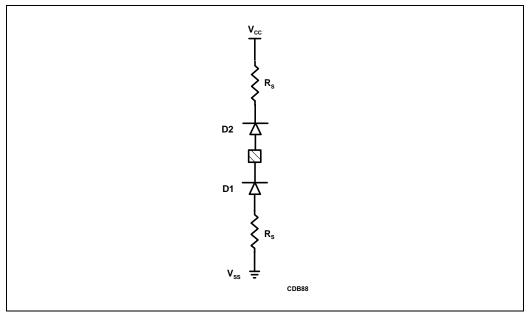

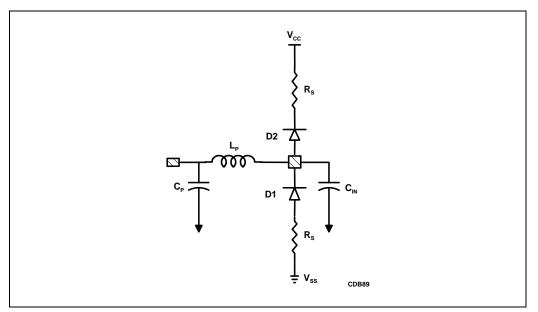

| 8.3. | INPUT DIODE MODELS          | 8-6 |

#### **CHAPTER 9**

#### **MECHANICAL SPECIFICATIONS**

#### CHAPTER 10 THERMAL SPECIFICATIONS

#### CHAPTER 11

#### TESTABILITY

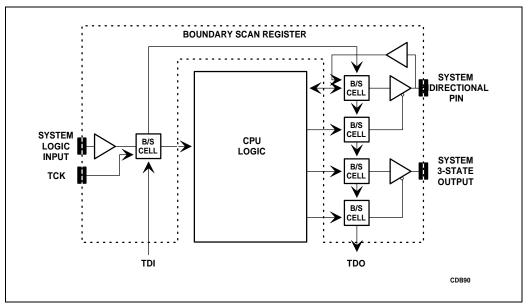

| 11.1.       BUILT-IN SELT TEST (BIST)       11-1         11.2.       BOUNDARY SCAN       11-2         11.2.1.       Boundary Scan Architecture       11-3         11.2.2.       Test Data Registers       11-3         11.2.2.       Test Data Registers       11-3         11.2.2.       BOUNDARY SCAN REGISTER       11-4         11.2.2.3.       DEVICE IDENTIFICATION REGISTER       11-4         11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       NSTRUCTION SET         NSTRUCTION SET       11-6       11-2       11-7         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.       TEST-LOGIC-RESET STATE       11-9         11.2.4.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10         11.2.5.       DENTIUM® PROCESSOR BOUNDARY SCAN REGISTER CELL       11-10 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.2.1.       Boundary Scan Architecture       11-3         11.2.2.       Test Data Registers       11-3         11.2.2.1.       BYPASS REGISTER       11-4         11.2.2.2.       BOUNDARY SCAN REGISTER       11-4         11.2.2.3.       DEVICE IDENTIFICATION REGISTER       11-5         11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                            |

| 11.2.2.       Test Data Registers       11-3         11.2.2.1.       BYPASS REGISTER       11-4         11.2.2.2.       BOUNDARY SCAN REGISTER       11-4         11.2.2.3.       DEVICE IDENTIFICATION REGISTER       11-5         11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                |

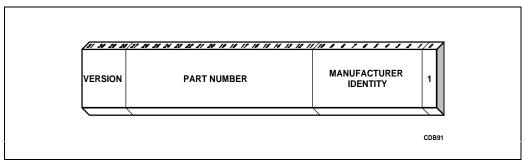

| 11.2.2.2.       BOUNDARY SCAN REGISTER       11-4         11.2.2.3.       DEVICE IDENTIFICATION REGISTER       11-5         11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.2.2.       BOUNDARY SCAN REGISTER       11-4         11.2.2.3.       DEVICE IDENTIFICATION REGISTER       11-5         11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.2.4.       RUNBIST REGISTER       11-6         11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11.2.3.       Instruction Register       11-6         11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I       11-6         NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I<br>NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.2.3.1.       PENTIUM® PROCESSOR CACHE CHIP SET BOUNDARY SCAN I<br>NSTRUCTION SET       11-6         11.2.4.       Test Access Port (TAP) Controller       11-8         11.2.4.1.       TEST-LOGIC-RESET STATE       11-9         11.2.4.2.       CAPTURE-IR STATE       11-10         11.2.5.       Boundary Scan Register Cell       11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

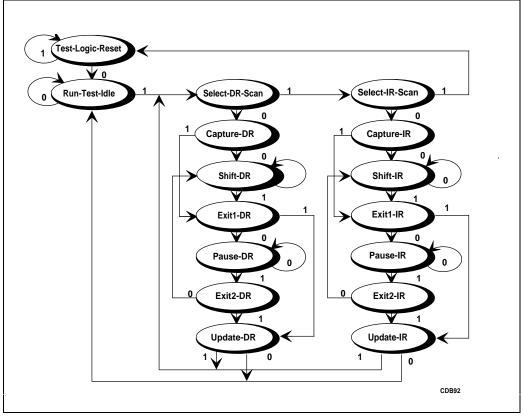

| 11.2.4.         Test Access Port (TAP) Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11.2.4.1.         TEST-LOGIC-RESET STATE         11-9           11.2.4.2.         CAPTURE-IR STATE         11-10           11.2.5.         Boundary Scan Register Cell         11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.4.1.         TEST-LOGIC-RESET STATE         11-9           11.2.4.2.         CAPTURE-IR STATE         11-10           11.2.5.         Boundary Scan Register Cell         11-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.5. Boundary Scan Register Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11.2.3.1. FENTIONS PROCESSOR DOUNDART SCAN REGISTER GELL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11.2.5.2. 82496 CACHE CONTROLLER BOUNDARY SCAN REGISTER CELL 11-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11.2.5.3. 82491 CACHE SRAM BOUNDARY SCAN REGISTER CELL 11-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.2.6. Boundary Scan Description Language (BSDL) 11-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14.0.7 Devenden: Cean Cinnel Descriptions 14.40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11.2.7. Boundary Scan Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### PART II — 82497 Cache Controller and 82492 Cache SRAM

#### **CHAPTER 12** PINOUTS Page 12.1. 12.2. **CHAPTER 13 PRODUCT OVERVIEW AND OPERATION** 13.1.1. 13.1.2. 13.1.3. 13.2. 13.2.1. 13.2.2. **CHAPTER 14** ELECTRICAL SPECIFICATIONS 14.1. 14.2. 14.3. 14.3.1. 14.3.1.1. 14.3.1.1.1. 14.3.1.1.2. 14.3.1.2. 14.3.1.2.1. 14.3.1.2.2. 14.3.2. EXTERNAL INTERFACE AC TIMINGS......14-19 14.3.2.1. EXTERNAL INTERFACE SIGNAL QUALITY ......14-36 14.3.2.2.

### CHAPTER 15

14.3.2.2.1.

14.3.2.2.2.

| I/O  | BUFFER MODELS                            |      |

|------|------------------------------------------|------|

| 15.1 | 1. OPTIMIZED INTERFACE BUFFER PARAMETERS | 15-1 |

| 15.2 | 2. EXTERNAL INTERFACE BUFFER PARAMETERS  | 15-7 |

### CHAPTER 16

#### MECHANICAL SPECIFICATIONS

#### CHAPTER 17 TESTABILITY

#### CHAPTER 18 THERMAL SPECIFICATIONS

#### APPENDIX A SUPPLEMENTAL INFORMATION

### PART III — 82497 Cache Controller and 82492 Cache SRAM

#### **CHAPTER 19** PRODUCT OVERVIEW AND OPERATION Page Main Features......19-1 19.1.1. 19.2. DIFFERENCES BETWEEN THE 82498/82493 AND 82497/82492 CACHE 19.2.1. Pins & Connections ...... 19-3 19.2.2. 19.2.3. 19.2.4. 19.2.5.

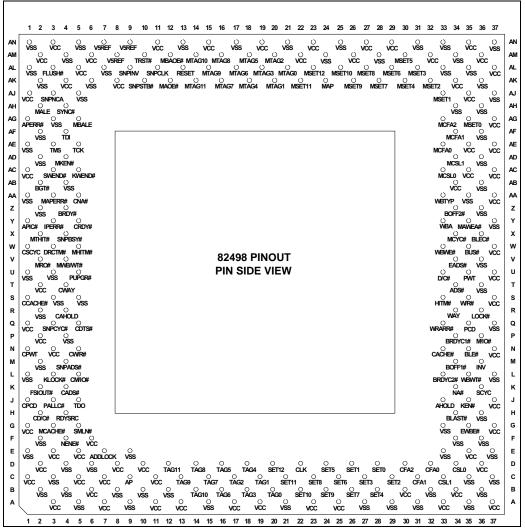

#### CHAPTER 20 PINOUTS

|            | OUT DIAGRAMS                                 |  |

|------------|----------------------------------------------|--|

|            | 2498 Cache Controller Pinouts                |  |

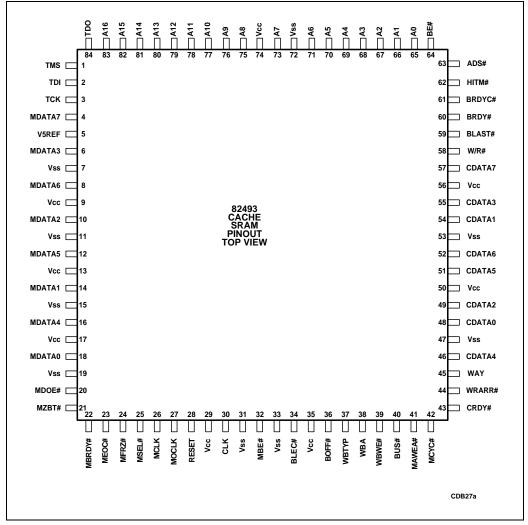

| 20.1.2. 82 | 2493 Cache SRAM Pinouts                      |  |

| 20.2. PIN  | CROSS REFERENCE TABLES                       |  |

| 20.2.1. 82 | 2498 Cache Controller                        |  |

|            | 2493 Cache SRAM                              |  |

| 20.2.3. B  | rief Pin Description Cross Reference         |  |

| 20.2.4. Pi | in Additions & Modifications                 |  |

| 20.2.4.1.  | ADDLOCK                                      |  |

| 20.2.4.2.  | BOFF#, BOFF1#, BOFF2#                        |  |

| 20.2.4.3.  | BT[3:0]/MBT[3:0]                             |  |

| 20.2.4.4.  | CFA[2:0],SET[12:0],TAG[11:0], CSL[1:0]       |  |

| 20.2.4.5.  | KLOCK#                                       |  |

| 20.2.4.6.  | MCFA[2:0], MCSL[1:0], MSET[12:0], MTAG[11:0] |  |

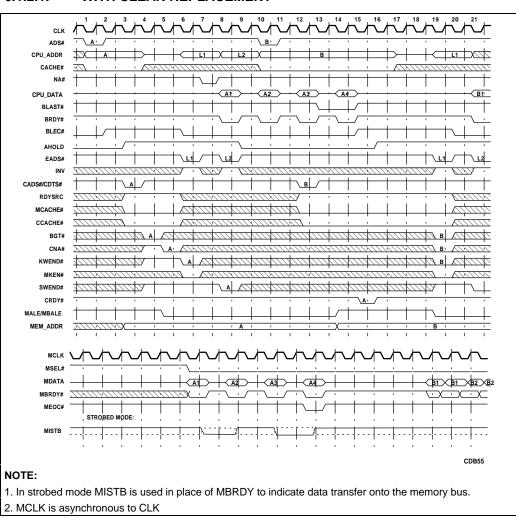

| 20.2.4.7.  | MISTB                                        |  |

| 20.2.4.8.  | MOSTB                                        |  |

| 20.2.4.9.  | PUPGR#                                       |  |

| 20.2.4.10. | SNPBSY#                                      |  |

| 20.2.4.11. | SNPCYC#                                      |  |

|            |                                              |  |

### CHAPTER 21

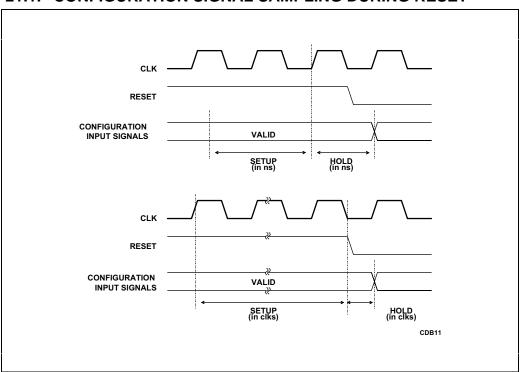

| 21.1. CONFIGURATION SIGNAL SAMPLING DURING RESET  | 21-2   |

|---------------------------------------------------|--------|

| 21.1.1. Initialization Required for Chip Set Mode | 21-3   |

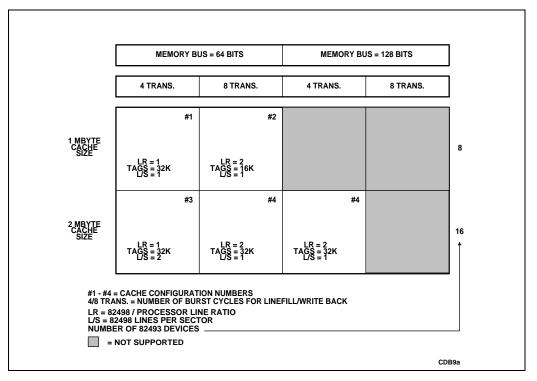

| 21.2. PHYSICAL CACHE                              | 21-4   |

| 21.2.1. Memory Bus Width                          | . 21-5 |

| 21.2.2. Line Ratio                                |        |

| 21.2.3.  | TagRAM Size                                    |  |

|----------|------------------------------------------------|--|

| 21.2.4.  | TagRAM Structure                               |  |

| 21.2.5.  | Lines per Sector (L/S)                         |  |

| 21.2.6.  | Cache Size                                     |  |

| 21.2.7.  | Configurable Address Connections               |  |

| 21.2.8.  | 82493 Cache SRAM Bus Configuration             |  |

| 21.2.9.  | 82493 Cache SRAM Parity Configuration          |  |

| 21.2.10. | CPU to 82493 Cache SRAM Address Configurations |  |

| 21.2.11. | Bus Driver Buffer Selection                    |  |

| 21.3. C  | ACHE MODES                                     |  |

| 21.3.1.  | MEMORY BUS MODES                               |  |

| 21.3.2.  | Clocked Mode                                   |  |

| 21.3.3.  | Strobed Mode                                   |  |

| 21.3.4.  | Configuration of Memory Bus Mode               |  |

| 21.3.5.  | Snoop Modes                                    |  |

| 21.3.6.  | Configuration of Snoop Mode                    |  |

| 21.3.7.  | Lock Configuration                             |  |

|          |                                                |  |

#### CHAPTER 22 FUNCTIONALITY

| 22.1. S   | TATE TRANSITIONS                                     | 22-1 |

|-----------|------------------------------------------------------|------|

| 22.1.1.   | CPU Bus Signals                                      |      |

| 22.1.2.   | Memory Bus Signals                                   |      |

| 22.1.3.   | Tag States & Cycles Resulting from State Transitions |      |

| 22.1.3.1. | TAG STATE                                            |      |

| 22.1.3.2. | CYCLES RESULTING FROM STATE TRANSITIONS              |      |

| 22.1.4.   | MESI State Tables (82498 State Changes)              |      |

| 22.1.5.   | MESI State Tables (CPU & 82498 Changes)              |      |

| 22.2. LO  | DCKED CYCLES                                         |      |

|           | LOCKed Cycle Categories                              |      |

| 22.2.1.1. | NON-SPLIT LOCKED CYCLES                              |      |

| 22.2.1.2. | SPLIT LOCKED CYCLES                                  |      |

| 22.2.2.   | LOCKed Cycle Examples                                |      |

| 22.2.2.1. | NON-SPLIT LOCKED SEQUENCE - HIT TO E/M STATE         |      |

| 22.2.2.2. | NON-SPLIT LOCKED READ HIT TO S - WRITE THROUGH       |      |

| 22.2.2.3. | NON-SPLIT LOCKED READ MISS WITH CLEAN REPLACEMENT    |      |

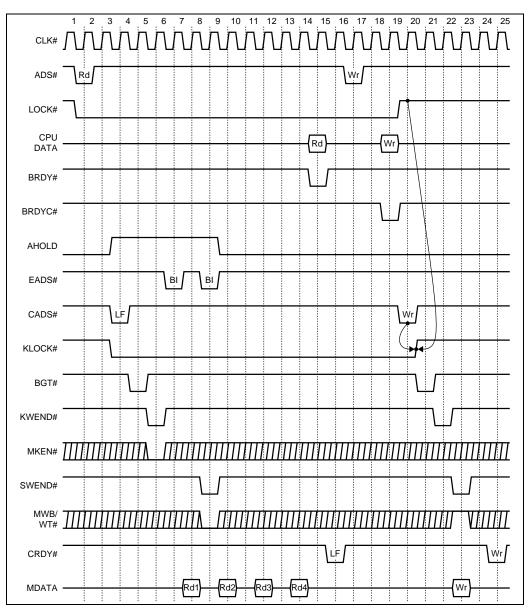

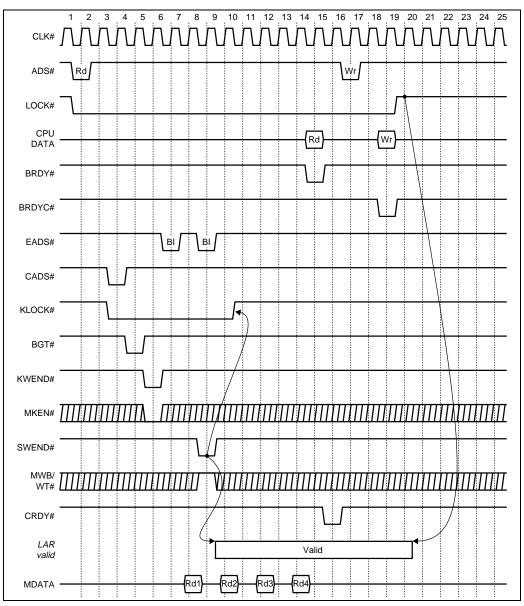

| 22.2.2.4. | NON-SPLIT LOCKED READ MISS - LINE FILL TO E/M        |      |

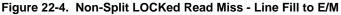

| 22.2.2.5. | NON-SPLIT LOCKED READ MISS WITH REPLACEMENT          |      |

|           | OF MODIFIED LINE                                     |      |

| 22.3. SI  | NOOPING                                              |      |

| 22.3.1.   | Snoop Operation                                      |      |

| 22.3.2.   | Snoop Blocking                                       |      |

| 22.3.3.   | When Snooping is Not Allowed                         |      |

| 22.3.4.   | Snooping During LOCKed Cycles                        |      |

| 22.3.4.1. | SNOOPING DURING SPLIT LOCKED CYCLES                  |      |

| 22.3.5.   | Snoop Write Back Cycles                              |      |

| 22.3.6.   | Snoop Hit to [M] State                               |      |

| 22.3.7.   | Snoop Hit to LAR (Synchronous Snoop Mode)            |      |

#### **CHAPTER 23**

| ELECTRICAL SPECIFICATIONS             | PAGE |

|---------------------------------------|------|

| 23.1. POWER AND GROUND                |      |

| 23.2. DECOUPLING RECOMMENDATIONS      |      |

| 23.3. CONNECTION SPECIFICATIONS       |      |

| 23.4. MAXIMUM RATINGS                 |      |

| 23.5. DC SPECIFICATIONS               |      |

| 23.6. AC SPECIFICATIONS               |      |

| 23.6.1. Optimized Interface           |      |

| 23.6.2. Flight Time Specification     |      |

| 23.6.2.1. FLIGHT TIMES                |      |

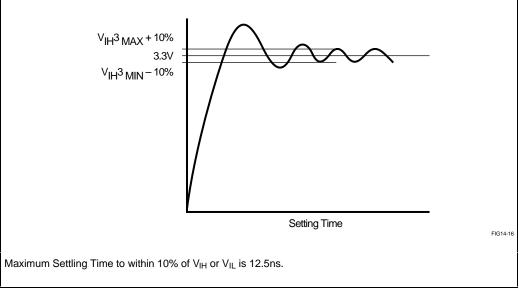

| 23.6.3. Signal Quality Specifications |      |

| 23.6.4. Ringback                      |      |

| 23.6.5. Settling Time                 |      |

| 23.6.6. External Interface            |      |

| 23.7. AC SPECIFICATIONS               |      |

### CHAPTER 24

| NO DU |                             |   |

|-------|-----------------------------|---|

| 24.1. | OPTIMIZED INTERFACE BUFFERS | 2 |

| 24.2. | EXTERNAL INTERFACE BUFFERS  | 5 |

| 24.3. | INPUT DIODE MODELS          | 8 |

| -     |                             | - |

### CHAPTER 25

#### **MECHANICAL SPECIFICATIONS**

#### CHAPTER 26 THERMAL SPECIFICATIONS

### CHAPTER 27

| IESI  |                                                    |   |

|-------|----------------------------------------------------|---|

| 27.1. | 82498 CACHE CONTROLLER BOUNDARY SCAN REGISTER CELL | 1 |

| 27.2. | 82493 CACHE SRAM BOUNDARY SCAN REGISTER CELL       | 2 |

| 27.3. | 82498 CACHE CONTROLLER TESTING                     | 3 |

| 27.4. | TEST-LOGIC-RESET STATE                             | 3 |

### Figures

| Figure | Title                                                                                          | Page    |

|--------|------------------------------------------------------------------------------------------------|---------|

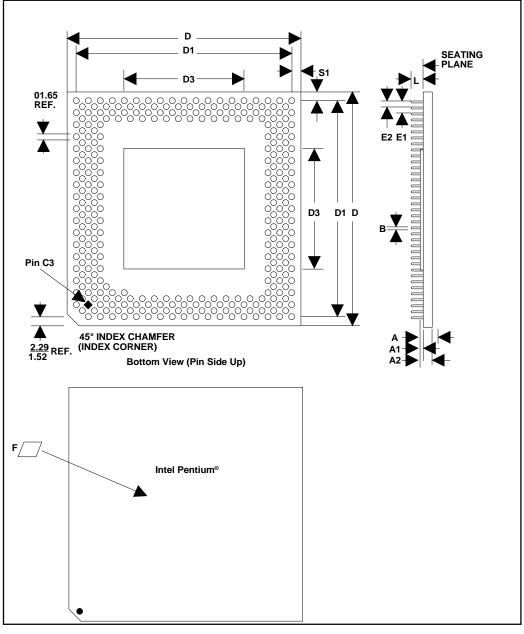

| 1-1.   | Pentium <sup>®</sup> Processor Pinout (Top View)                                               | 1-1     |

| 1-2.   | Pentium® Processor Pinout (Bottom View)                                                        | 1-2     |

| 1-3.   | 82496 Cache Controller Pinout (Top View)                                                       | 1-3     |

| 1-4.   | 82496 Cache Controller Pinout (Bottom View)                                                    | 1-4     |

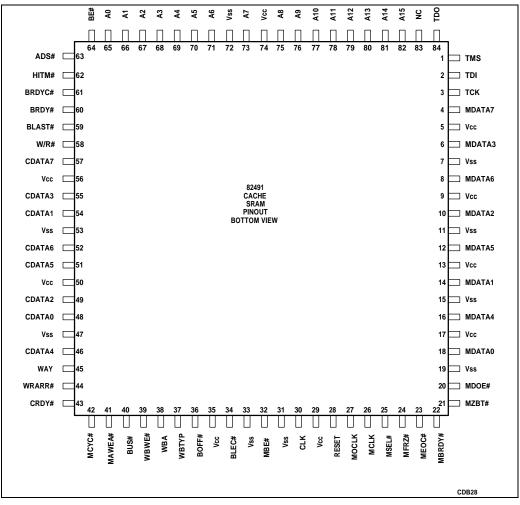

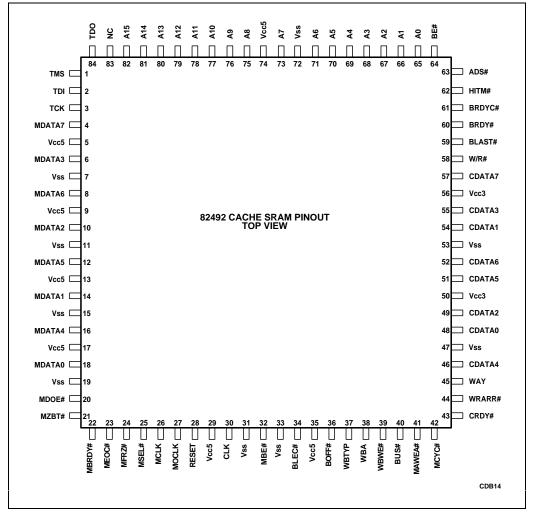

| 1-5.   | 82491 Cache SRAM Memory Pinout (Top View)                                                      | 1-5     |

| 1-6.   | 82491 Cache SRAM Pinout (Bottom View)                                                          | 1-6     |

| 1-7.   | Brief Pin Description Table Cross Reference                                                    | 1-14    |

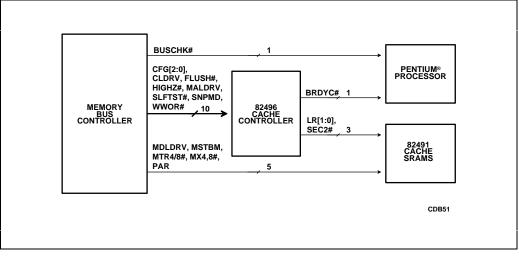

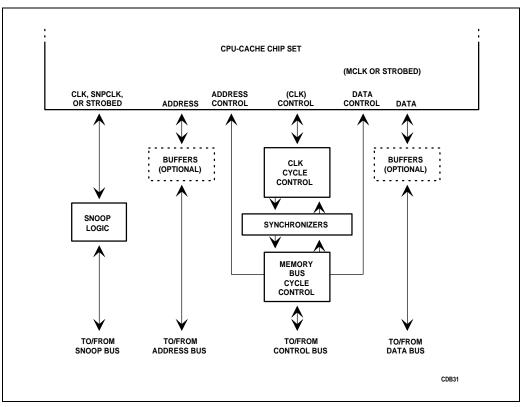

| 2-1.   | 82496 Cache Controller Block Diagram                                                           | 2-3     |

| 2-2.   | 82491 Cache SRAM Block Diagram                                                                 |         |

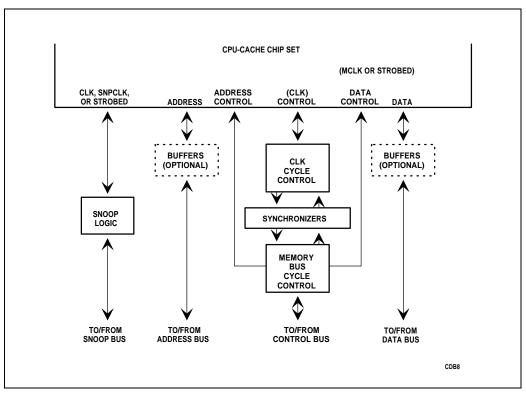

| 2-3.   | MBC Block Diagram                                                                              |         |

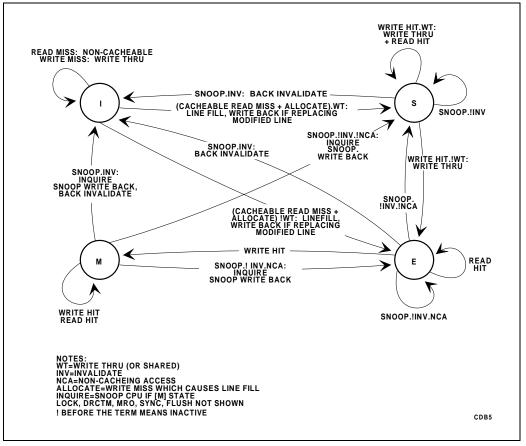

| 3-1.   | State Changes                                                                                  |         |

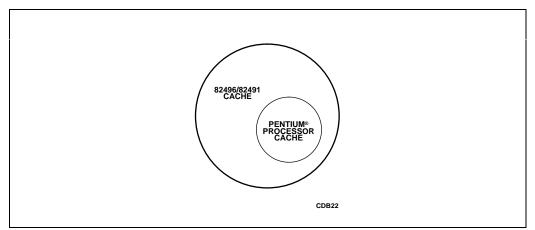

| 3-2.   | Pentium® Processor Cache Chip Set Cache Inclusion                                              | 3-17    |

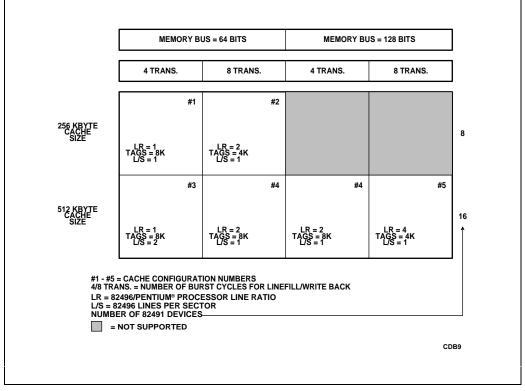

| 4-1.   | 82491 Cache Controller/82491 Cache SRAM Configurations with the Pentium <sup>®</sup> Processor | 4-1     |

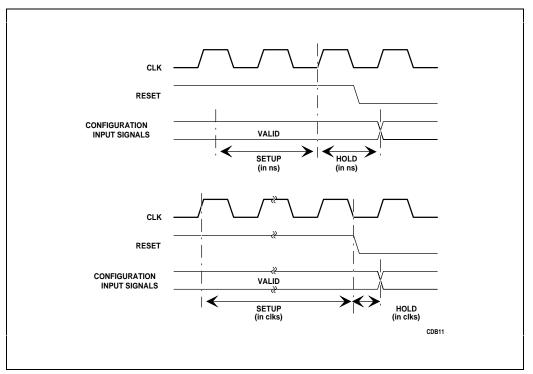

| 4-2.   | Configuration Input Sampling                                                                   | 4-2     |

| 4-3.   | CPU-Cache Chip Set Configuration Inputs                                                        | 4-3     |

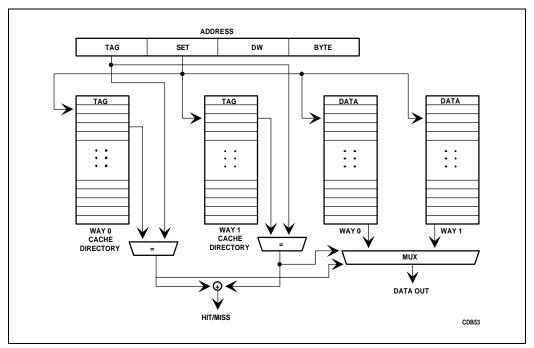

| 4-4.   | Two-Way Set Associative TagRAM Structure                                                       | 4-6     |

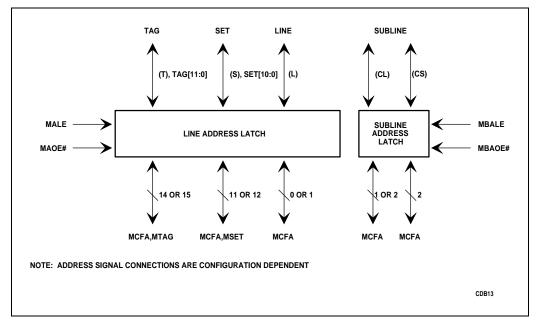

| 4-5.   | Address Latching                                                                               | 4-8     |

| 5-1.   | MBC Block Diagram                                                                              |         |

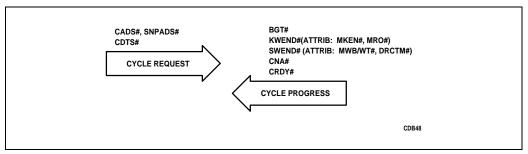

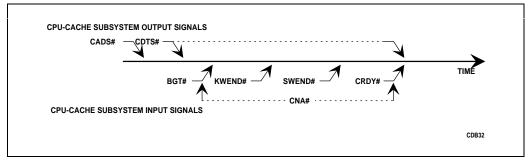

| 5-2.   | Memory Bus Cycle Progress and Attribute Signals                                                | 5-3     |

| 5-3.   | Cycle Progress Signals and Responses                                                           | 5-3     |

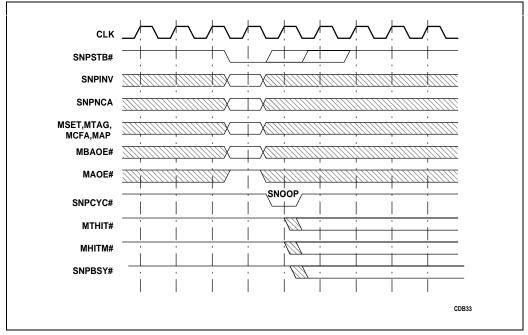

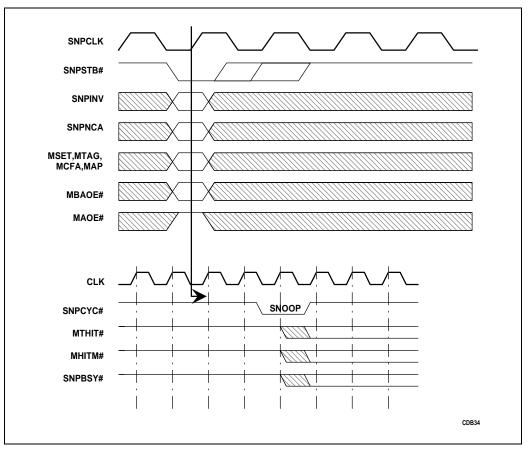

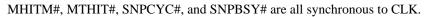

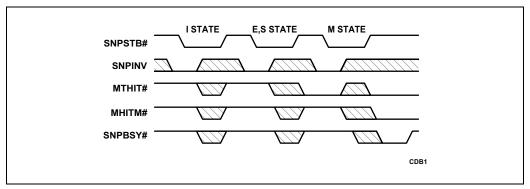

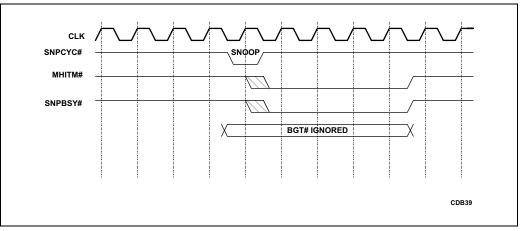

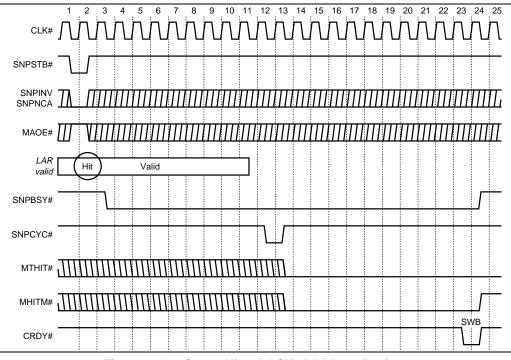

| 5-4.   | Synchronous Snoop Mode                                                                         |         |

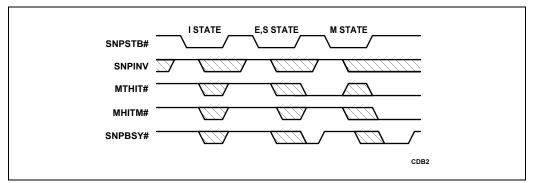

| 5-5.   | Clocked Snoop Mode                                                                             |         |

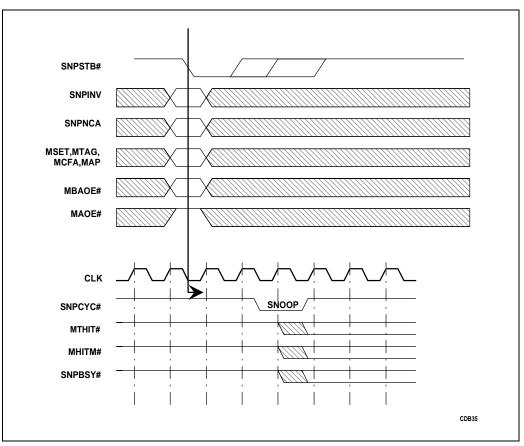

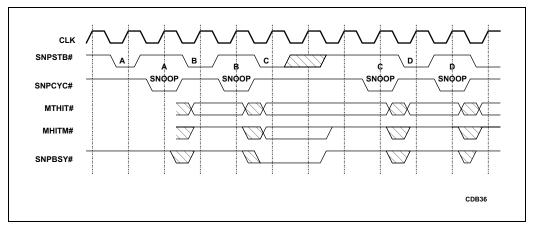

| 5-6.   | Strobed Snoop Mode                                                                             | 5-15    |

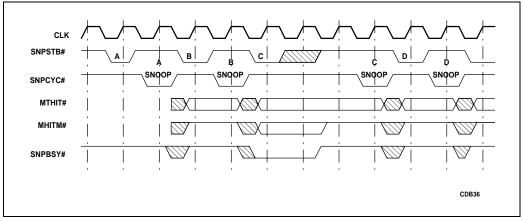

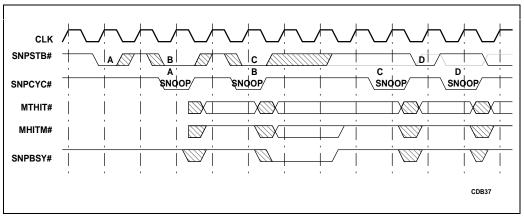

| 5-7.   | 82496 Cache Controller Snooping Operations                                                     |         |

| 5-8.   | Fastest Synchronous Snooping                                                                   | 5-17    |

| 5-9.   | Fastest Asynchronous Snooping                                                                  | 5-17    |

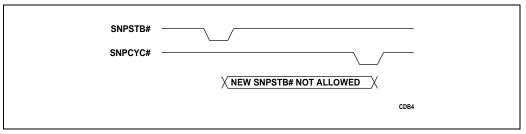

| 5-10.  | Snoops without Invalidation                                                                    | 5-18    |

| 5-11.  | Snoops with Invalidation                                                                       | 5-18    |

| 5-12.  | Snoop Response During Cycles                                                                   | 5-19    |

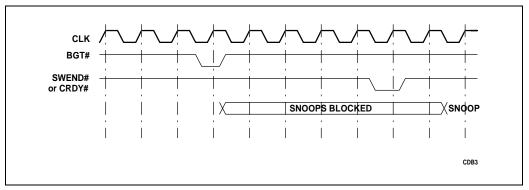

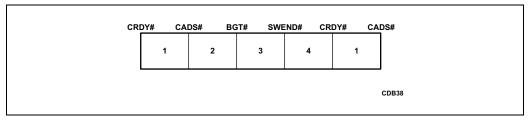

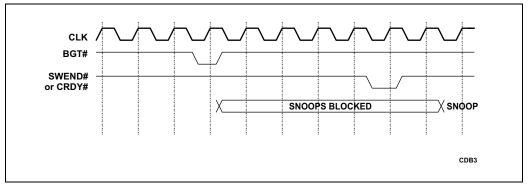

| 5-13.  | Snoop Response Blocking Using BGT#                                                             | 5-20    |

| 5-14.  | Snoop Executing before BGT# is Asserted                                                        | 5-20    |

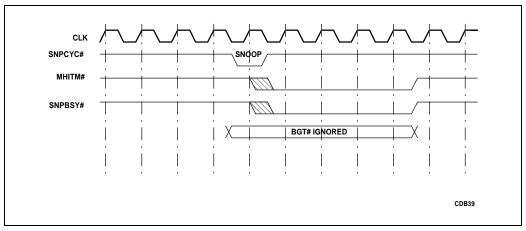

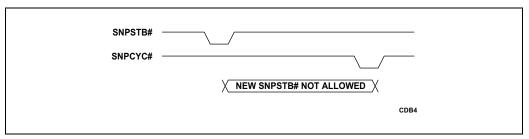

| 5-15.  | New SNPSTB# Not Allowed                                                                        | 5-21    |

| 5-16.  | Cycle Progress for Snoop Writeback Cycles                                                      | 5-23    |

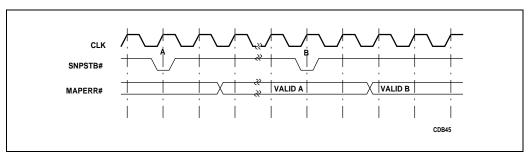

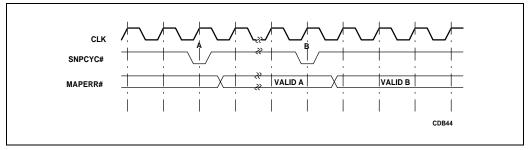

| 5-17.  | MAPERR# Timing for Synchronous Snoop Mode                                                      | 5-25    |

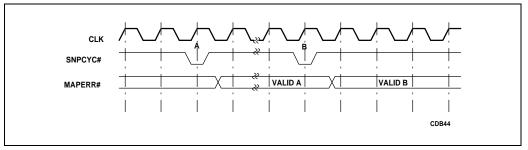

| 5-18.  | MAPERR# Timing for Asynchronous Snoop Modes                                                    | 5-25    |

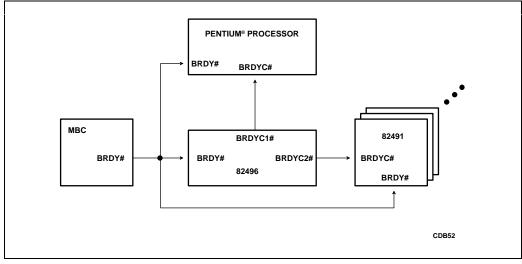

| 5-19.  | BRDY#/BRDYC#/BRDYC1#/BRDYC2# Interconnection                                                   | 5-26    |

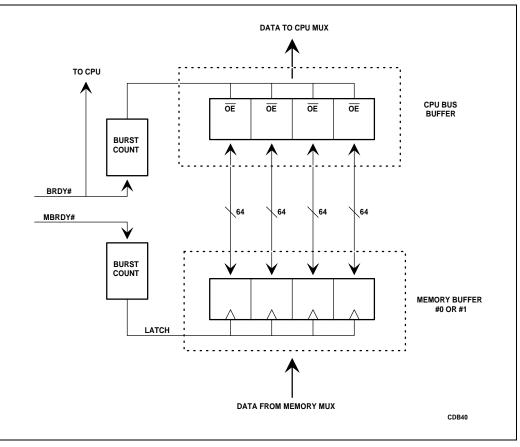

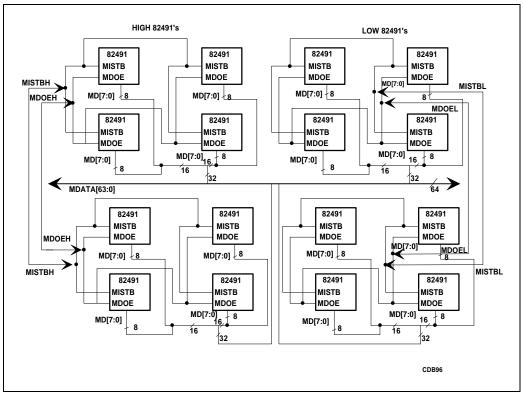

| 5-20.  | 82491 Cache SRAM Read Data Path                                                                |         |

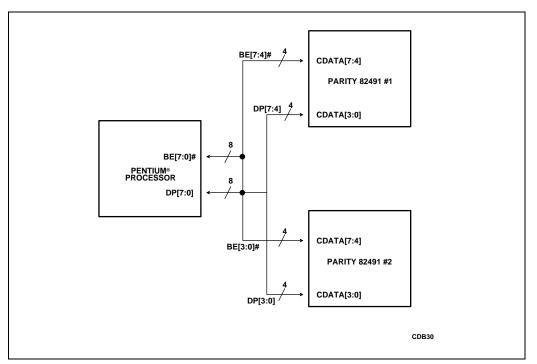

| 5-21.  | Pentium® Processor/82491 Cache SRAM Data Parity Connections                                    |         |

| 5-22.  | 512K Cache, 64-Bit Bus                                                                         | 5-33    |

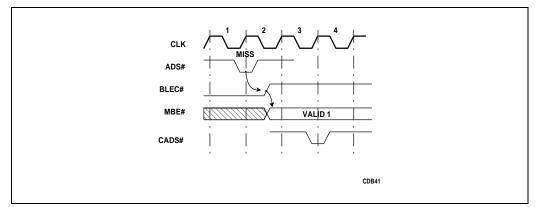

| 5-23.  | BLEC# Deassertion Due to ADS# Assertion                                                        |         |

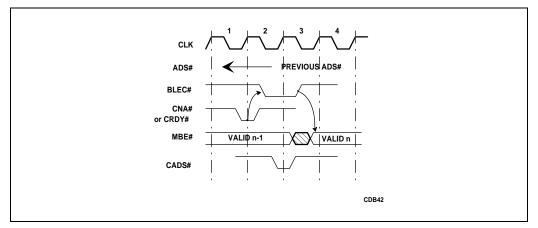

| 5-24.  | BLEC# Assertion Due to CNA# or CRDY# Assertion                                                 |         |

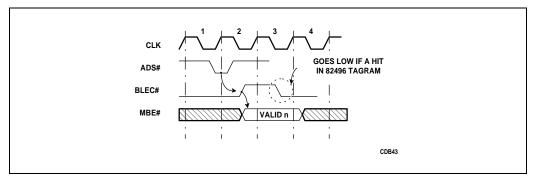

| 5-25.  | BLEC# Assertion Due to Hit in 82496 Cache Controller TagRAM                                    | 5-56    |

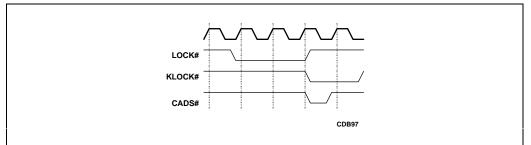

| 5-26.  | KLOCK# to LOCK# Relationship                                                                   | . 5-119 |

| 5-27.  | MAPERR# Timing                                                                                 |         |

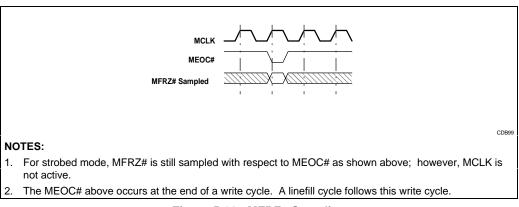

| 5-28.  | MFRZ# Sampling                                                                                 |         |

| 5-29.  | Increasing Hold Time of Output Burst Data                                                      |         |

| 5-30.  | MZBT# Sampling                                                                                 | 5-1/4   |

| Figure         | Title                                                                       | Page  |

|----------------|-----------------------------------------------------------------------------|-------|

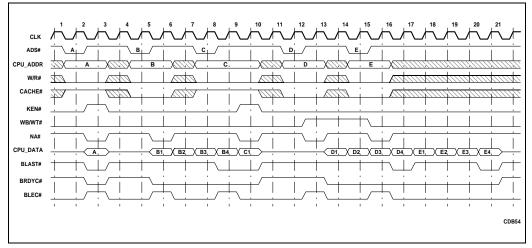

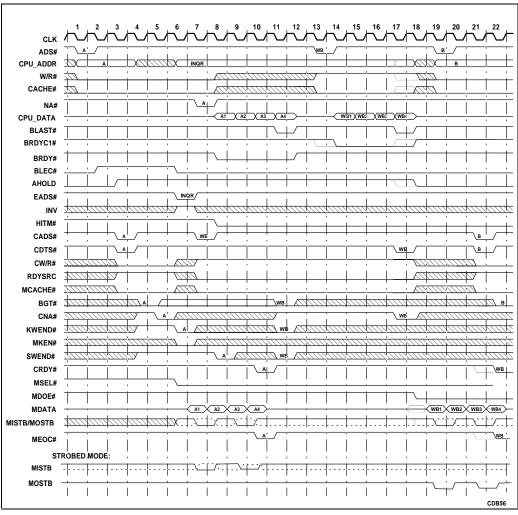

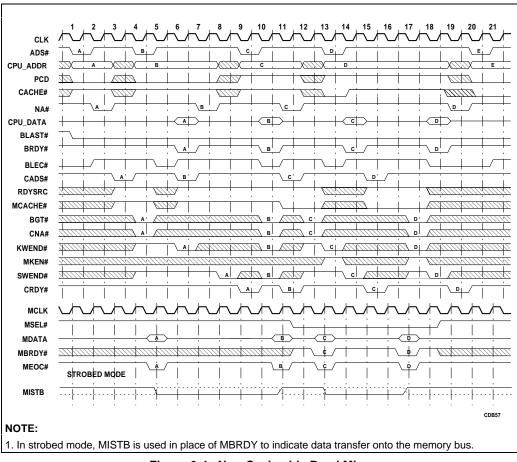

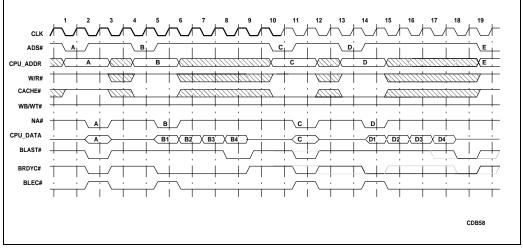

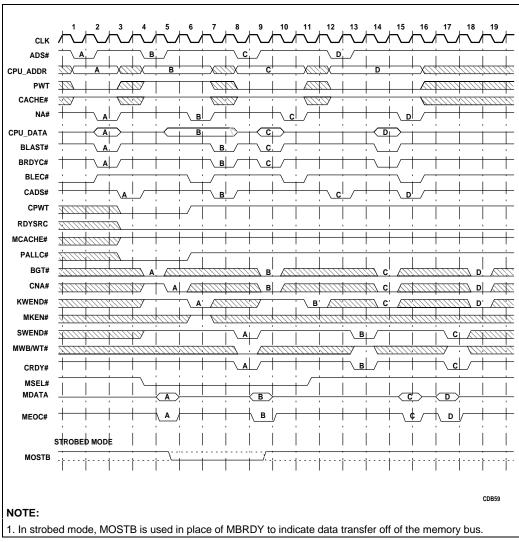

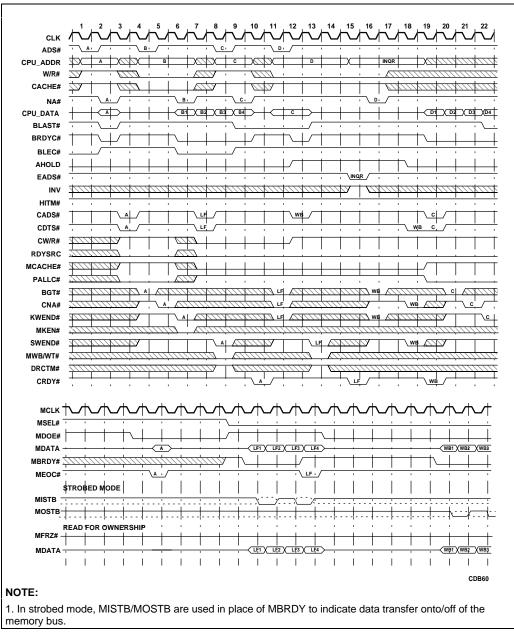

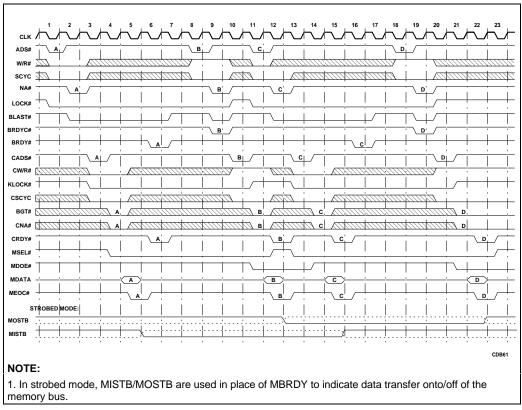

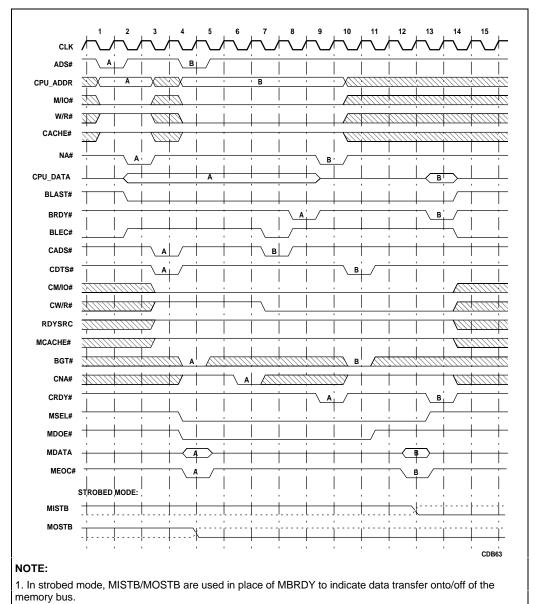

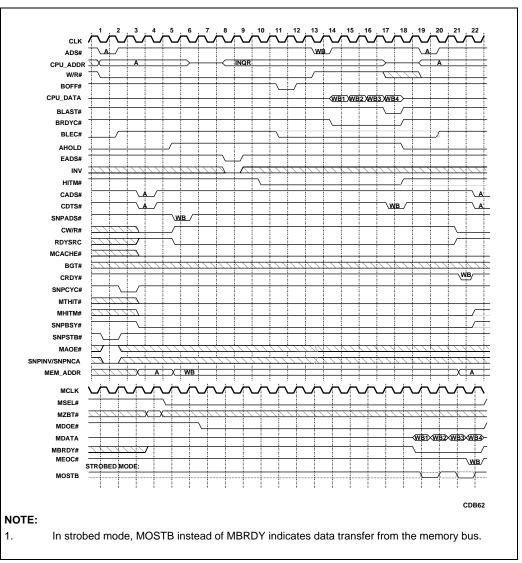

| 6-1.           | Pipelined Read Hits                                                         |       |

| 6-2.           | Read Miss with Clean Replacement                                            |       |

| 6-3.           | Read Miss with Replacement of Modified Line                                 | 6-7   |

| 6-4.           | Non-Cacheable Read Miss                                                     | 6-9   |

| 6-5.           | Write Hits to [E] or [M] State Cycles                                       |       |

| 6-6.           | Write Miss with No Allocation or Write Hit to [S] State Cycles              |       |

| 6-7.           | Write Miss with Allocation to Modified Line                                 |       |

| 6-8.           | Locked Read Modify Write Cycles                                             |       |

| 6-9.           | Snoop Hit to [M] State — Synchronous Snoop Mode                             |       |

| 6-10.          | I/O Cycles                                                                  | 6-21  |

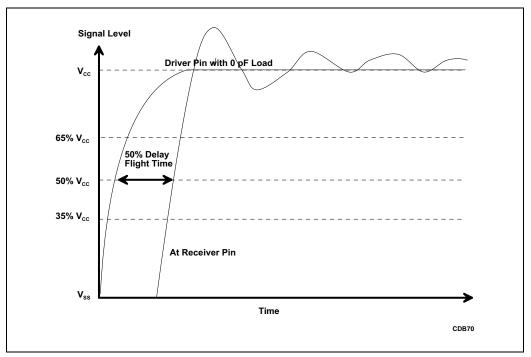

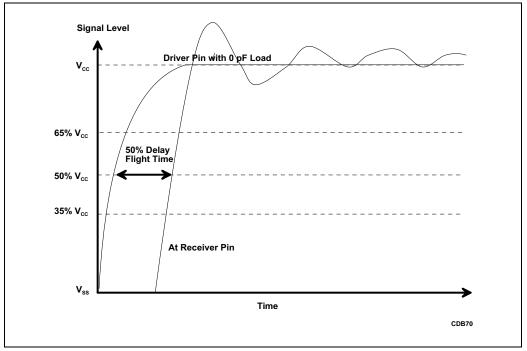

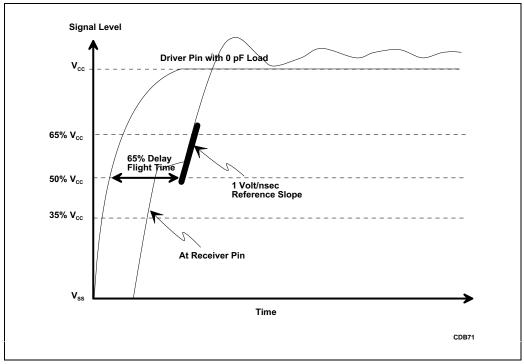

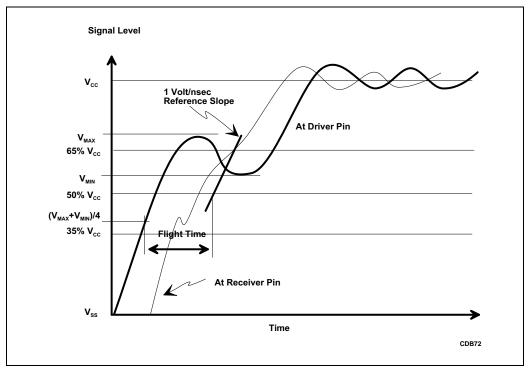

| 7-1.           | Determination of Flight Time                                                |       |

| 7-2.           | Derating the Flight Time                                                    |       |

| 7-3.           | In-System Measurement of Flight Time                                        | 7-8   |

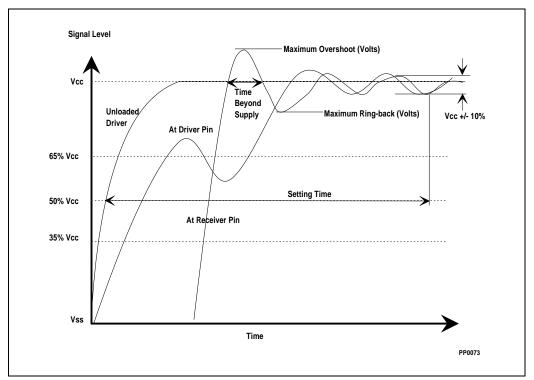

| 7-4.           | Driver and Receiver Signal Waveforms Showing Signal Quality Parameters      |       |

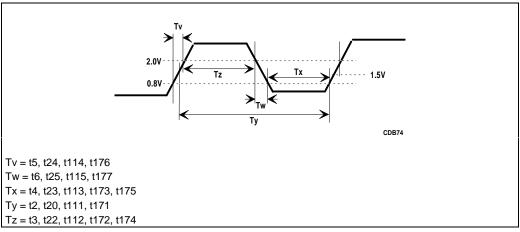

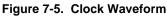

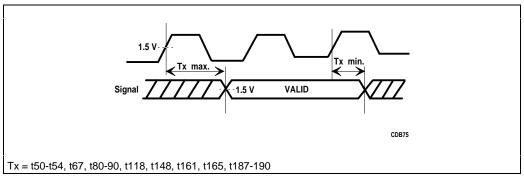

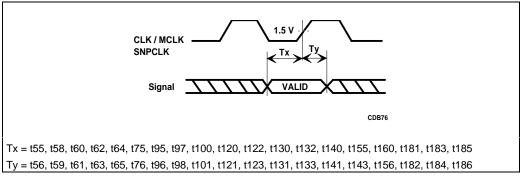

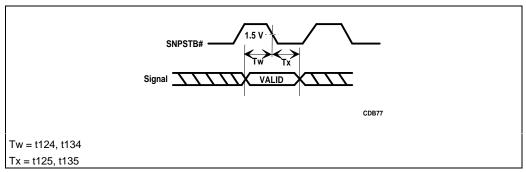

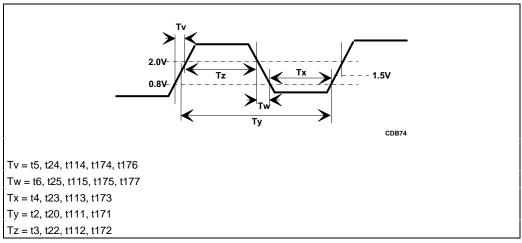

| 7-5.           | Clock Waveform                                                              |       |

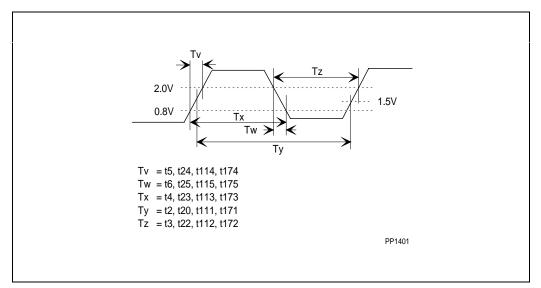

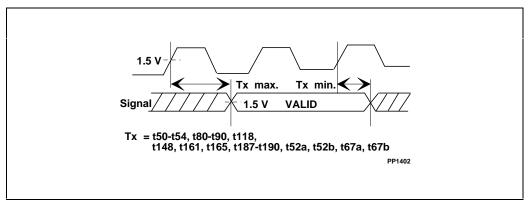

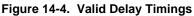

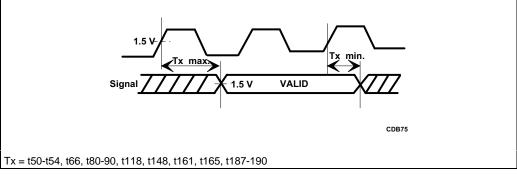

| 7-6.           | Valid Delay Timings                                                         |       |

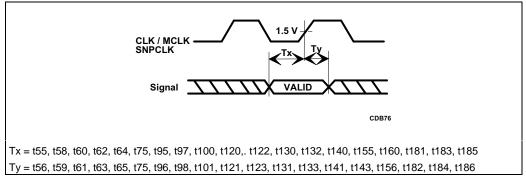

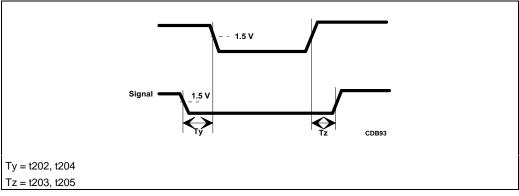

| 7-7.           | Setup and Hold Timings                                                      | 7-44  |

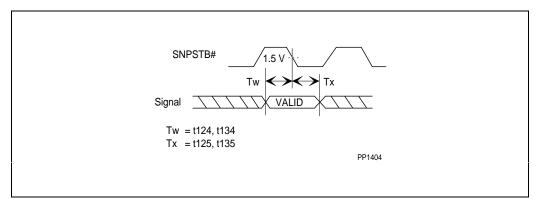

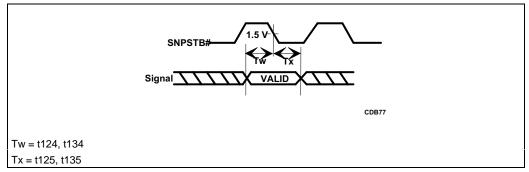

| 7-8.           | Setup and Hold Timings in Strobed Snooping Mode                             | 7-45  |

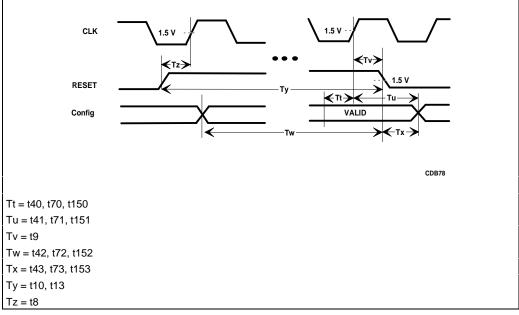

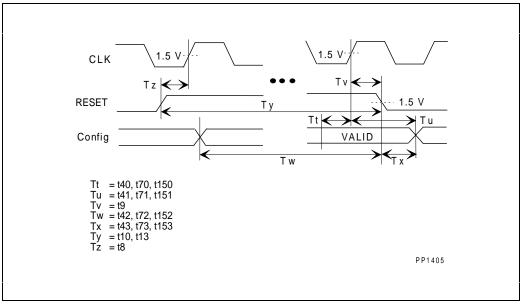

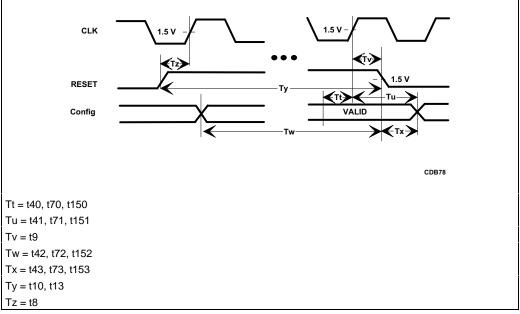

| 7-9.           | Reset and Configuration Timings                                             | 7-45  |

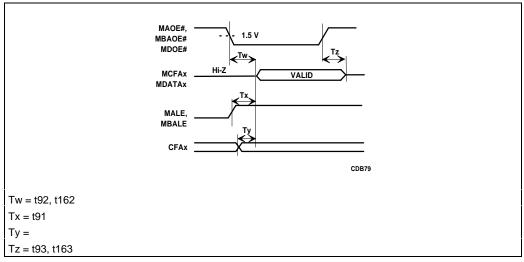

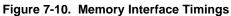

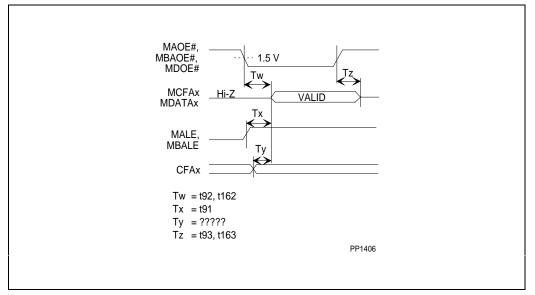

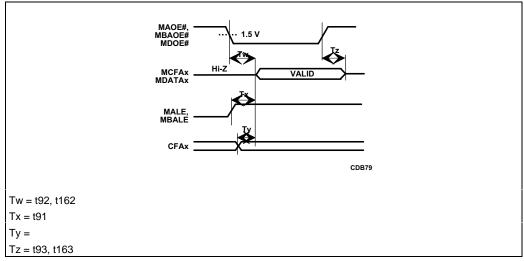

| 7-10.          | Memory Interface Timings                                                    |       |

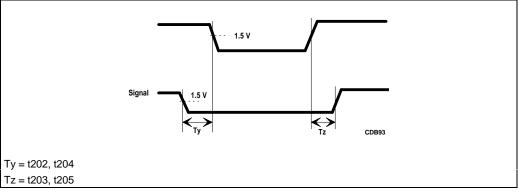

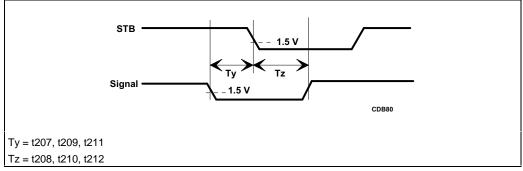

| 7-11.          | Setup and Hold Timings to Strobes                                           |       |

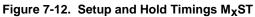

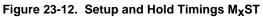

| 7-12.          | Setup and Hold Timings MxST                                                 |       |

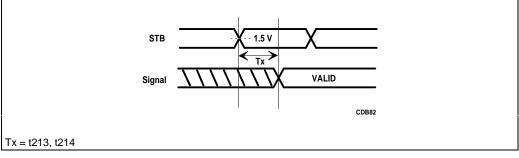

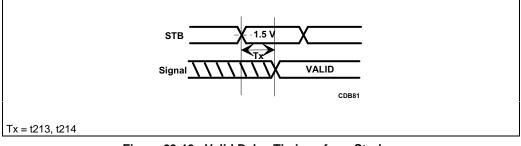

| 7-13.          | Valid Delay Timings from Strobes                                            |       |

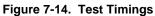

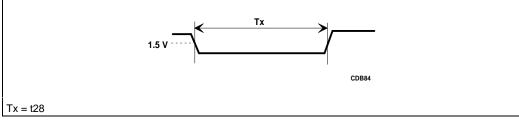

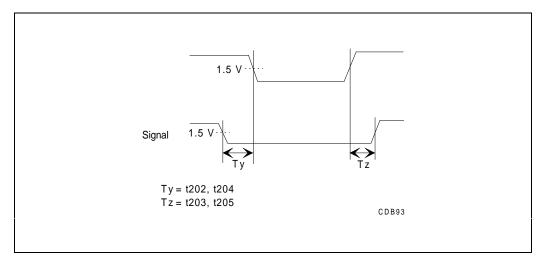

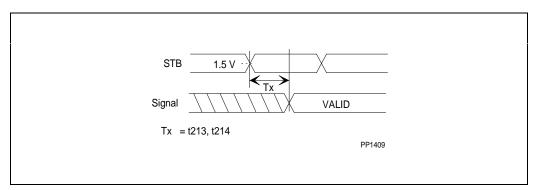

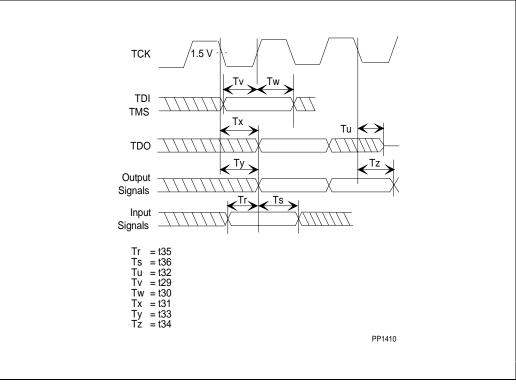

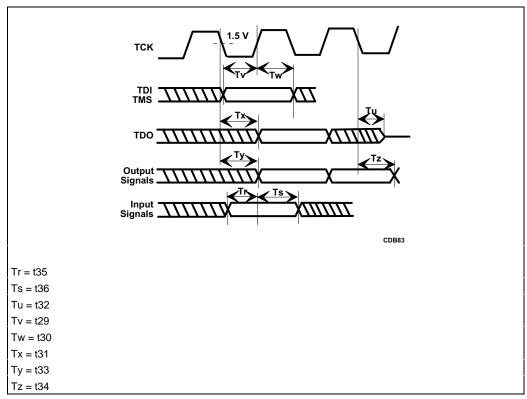

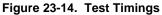

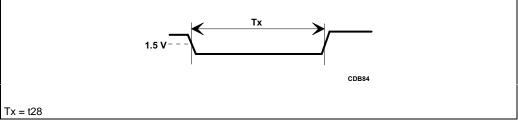

| 7-14.          | Test Timings                                                                |       |

| 7-15.          | Test Reset Timings                                                          |       |

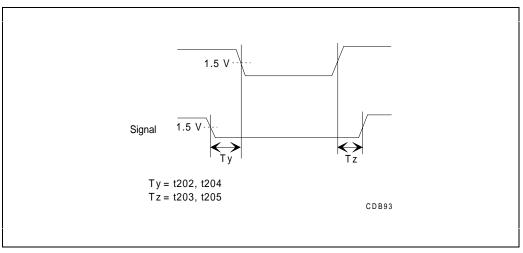

| 7-16.          | Active/Inactive Timings                                                     | 7-49  |

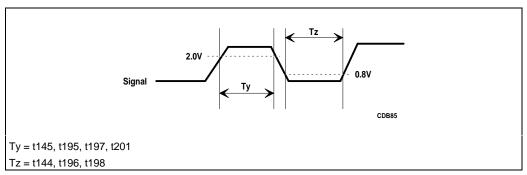

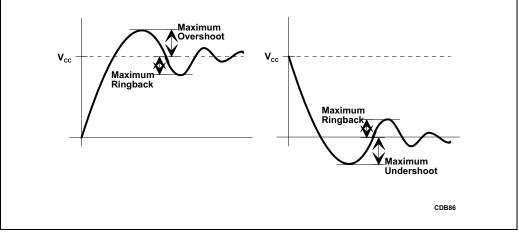

| 7-17.          | Overshoot/Undershoot and Ringback Guidelines                                |       |

| 8-1.           | First Order Input Buffer                                                    |       |

| 8-2.           | First Order Output Buffer                                                   |       |

| 8-3.           | Input Diode Model                                                           | 8-7   |

| 8-4.           | Complete Input Model Including Diode                                        | 8-8   |

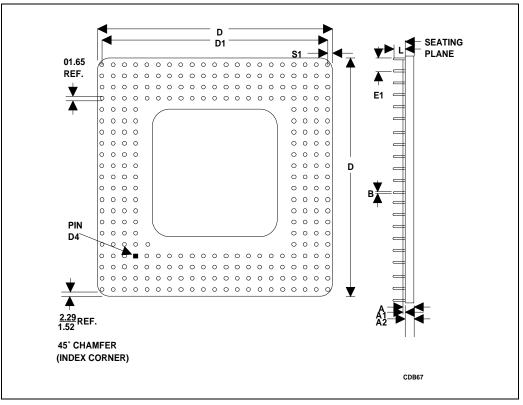

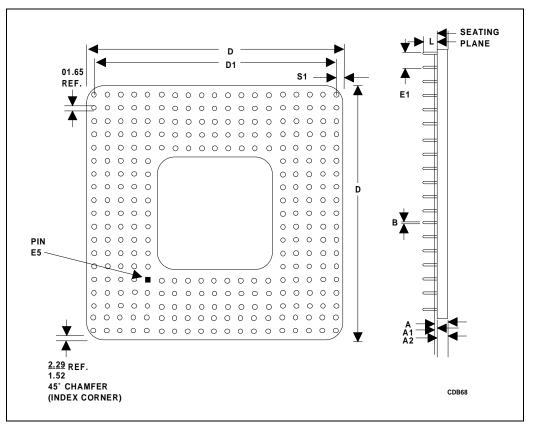

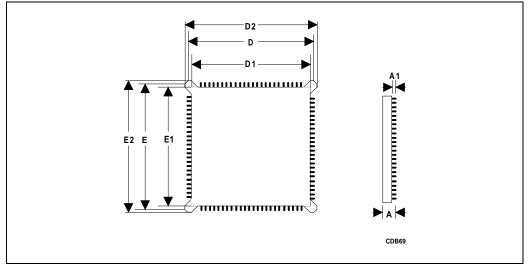

| 9-1.           | Pentium <sup>®</sup> Processor Mechanical Specifications                    |       |

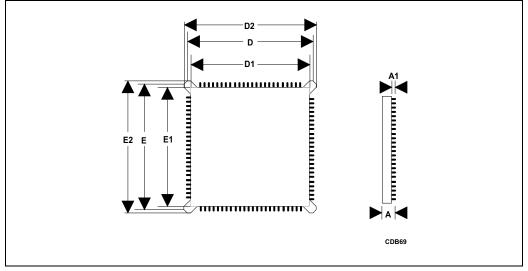

| 9-2.           | 82496 Cache Controller Mechanical Specifications                            |       |

| 9-3.           | 82491 Cache SRAM Mechanical Specifications                                  |       |

| 10-1.<br>11-1. | Technique for Measuring T <sub>CASE</sub>                                   | 10-1  |

| 11-1.<br>11-2. | Boundary Scan Register Structure of a Component                             |       |

| 11-2.          | Device ID Register                                                          |       |

| 12-1.          | TAP Controller State Diagram<br>82497 Cache Controller Pinout Top Side View | 12.2  |

| 12-1.          | 82497 Cache Controller Pinout Pin Side View                                 | 12-2  |

| 12-2.          | 82497 Cache Memory Pinout Top Side View                                     |       |

| 12-3.          | Chip Set Interface                                                          |       |

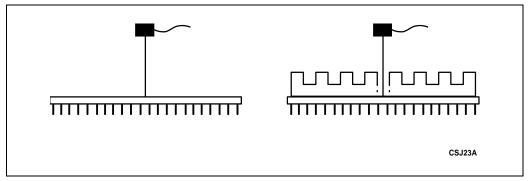

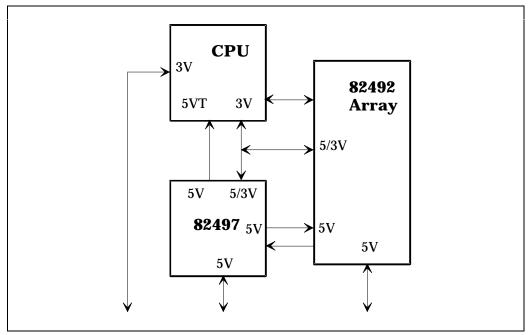

| 13-2.          | Interface Buffer Types                                                      |       |

| 14-1.          | Driver and Receiver Signal Waveforms Showing Signal Quality Parameters      |       |