# IA-32 Intel<sup>®</sup> Architecture Software Developer's Manual

**Documentation Changes**

November 2003

**Notice:** The IA-32 Intel<sup>®</sup> Architecture may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IA-32 Intel® Architecture may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Celeron, Intel SpeedStep, Intel Xeon and the Intel logo, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002-2003, Intel Corporation

# int<sub>el®</sub> Contents

| Revision History         | 4 |

|--------------------------|---|

| Preface                  | 5 |

| Summary Table of Changes | 6 |

| Documentation Changes    | 8 |

### **Revision History**

| Version | Description                                                                                                                                                                                    | Date           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001    | Initial Release                                                                                                                                                                                | November 2002  |

| -002    | Added 1-10 Documentation Changes.<br>Removed old Documentation Changes items that already have been<br>incorporated in the published Software Developer's manual                               | December 2002  |

| -003    | Added 9 -17 Documentation Changes<br>Removed Documenation Change #6 - References to bits Gen and Len<br>Deleted<br>Removed Documenation Change #4 - VIF Information Added to CLI<br>Discussion | February 2003  |

| -004    | Removed Documentation changes 1-17<br>Added Documentation changes 1-24                                                                                                                         | June 2003      |

| -005    | Removed Documentation Changes 1-24<br>Added Documentation Changes 1-15                                                                                                                         | September 2003 |

| -006    | Added Documentation Changes 16- 34                                                                                                                                                             | November 2003  |

I

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of documentation changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

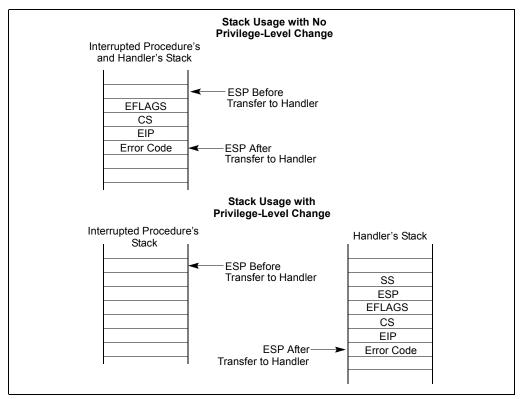

### **Affected Documents/Related Documents**

| Document Title                                                                             | Document<br>Number |

|--------------------------------------------------------------------------------------------|--------------------|

| IA-32 Intel® Architecture Software Developer's Manual: Volume 1, Basic Architecture        | 245470-011         |

| IA-32 Intel® Architecture Software Developer's Manual: Volume 2, Instruction Set Reference | 245471-011         |

| IA-32 Intel® Architecture Software Developer's Manual: Volume 3, System Programming Guide  | 245472-011         |

### **Nomenclature**

Documentation Changes include errors or omissions from the current published specifications. These changes will be incorporated in the next release of the Software Development Maunal.

int

### **Summary Table of Changes**

The following table indicates documentation changes which apply to the IA-32 Intel Architecture. This table uses the following notations:

### **Codes Used in Summary Table**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### **Summary Table of Documentation Changes**

| Number | DOCUMENTATION CHANGES                                                                                    |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.     | IA32_THERM_CONTROL has Been Changed to IA32_CLOCK_MODULATION                                             |  |  |  |  |

| 2.     | INTER-PRIVILEGE" was not Spelled Corretly in Pseudocode Entry                                            |  |  |  |  |

| 3.     | Confusing Text Artifact Removed                                                                          |  |  |  |  |

| 4.     | IA32_MISC_CTL has Been Removed From the List of Architectural MSRs                                       |  |  |  |  |

| 5.     | Typo Corrected in Figure 8-24                                                                            |  |  |  |  |

| 6.     | Typo Corrected in Figure 8-23                                                                            |  |  |  |  |

| 7.     | Corrupted Text Corrected                                                                                 |  |  |  |  |

| 8.     | Corrected an Error in PACKSSDW Illustration                                                              |  |  |  |  |

| 9.     | SSM Corrected to SMM                                                                                     |  |  |  |  |

| 10.    | Exiting From SMM Text Updated                                                                            |  |  |  |  |

| 11.    | L1 Data Cache Context Mode Description has Been Udpated                                                  |  |  |  |  |

| 12.    | #DE Should be #DB in Description of EFLAGS.RF                                                            |  |  |  |  |

| 13.    | There Have Been Revisions to the Table That States Priority Among Simultaneous Exceptions and Interrupts |  |  |  |  |

| 14.    | Corrections to Page-Directory-Pointer-Table Entry Desciption                                             |  |  |  |  |

| 15.    | Behavior Notes on the Accessed (A) Flag and Dirty (D) Flag                                               |  |  |  |  |

| 16.    | Interrupt 11 Discussion Concerning EXT Flag Functioning Has Been Updated                                 |  |  |  |  |

| 17.    | Improved Information on Interpreting Machine-Check Error Codes                                           |  |  |  |  |

| 18.    | More information on the Functioning of Debug BPs after POP SS/MOV SS Has Been Provided                   |  |  |  |  |

| 19.    | More Information on the LBR Stack Has Been Provided                                                      |  |  |  |  |

| 20.    | Limited Availability of Two MSRs Has Been Documented                                                     |  |  |  |  |

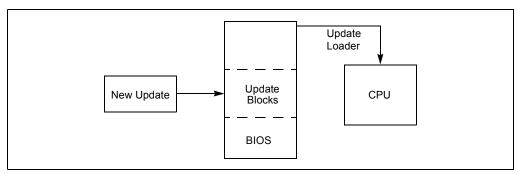

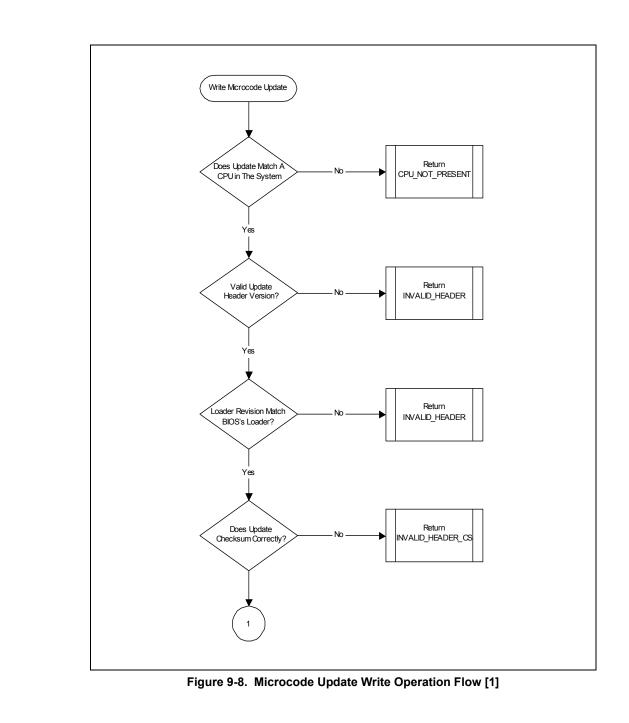

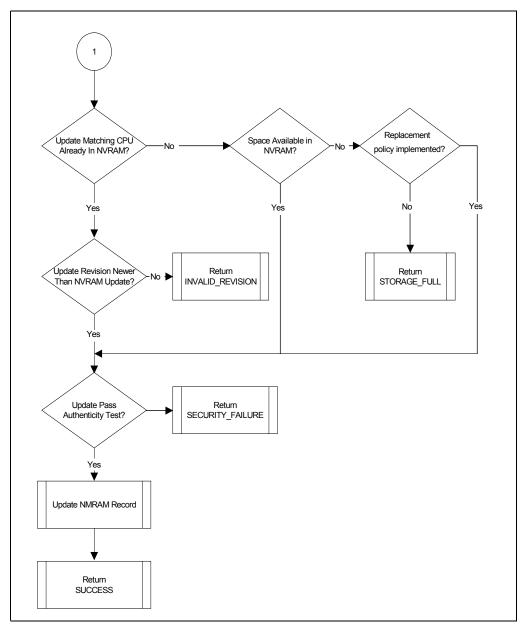

| 21.    | The Section On Microcode Update Facilities Has Been Refreshed                                            |  |  |  |  |

| 22.    | A Mechanism for Determining Sync/Async SMIs Has Been Documented                                          |  |  |  |  |

I

### Summary Table of Documentation Changes

| Number | DOCUMENTATION CHANGES                                                       |

|--------|-----------------------------------------------------------------------------|

| 23.    | Omitted Debug Data Has Been Restored                                        |

| 24.    | CLTS Exception Information Improved                                         |

| 25.    | The MOVSS Description Have Been Updated                                     |

| 26.    | An Instruction Listing (PULLHUW) Has Been Deleted                           |

| 27.    | Some Data Entry Errors in Table B-20 Have Been Corrected                    |

| 28.    | Figure 8-22 Has Been Corrected                                              |

| 29.    | The Description of Minimum Thermal Monitor Activation Time Has Been Updated |

| 30.    | Corrected Description of Exception- or Interrupt-Handler Procedures         |

| 31.    | CMPSD and CMPSS Exception Information Updated                               |

| 32.    | PUNPCKHB*/PUNPCKLB* Exception Information Improved                          |

| 33.    | MOVHPD, MOVLPD, UNPCKHPS, UNPCKLPS Exception Information Improved.          |

| 34.    | PEXTRW - PINSRW Exception Information Improved                              |

### **Documentation Changes**

IA32\_THERM\_CONTROL has been Changed to IA32\_CLOCK\_MODULATION

The name of the MSR IA32\_THERM\_CONTROL has been changed to IA32\_CLOCK\_MODULATION. This was done to avoid confusion about the MSR's function.

The following corrected table segment is from Appendix B, Table B-3, the *IA-32 Intel Architecture Software Developer's Manual, Volume 3*. See the reproduced text below

| Register Address |     |                           |                                                                                                                                                                                                                                                                                                             |

|------------------|-----|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex              | Dec | Register Name             | Bit Description                                                                                                                                                                                                                                                                                             |

| 19AH             | 410 | IA32_CLOCK_MODULATI<br>ON | Clock Modulation. (R/W) Enables and disables on-<br>demand clock modulation and allows the selection of<br>the on-demand clock modulation duty cycle. (See<br>Section 13.15.3., Software Controlled Clock<br>Modulation.<br>NOTE: IA32_CLOCK_MODULATION MSR was<br>originally named IA32_THERM_CONTROL MSR. |

2.

1.

#### INTER-PRIVILEGE" Was Not Spelled Correctly in Pseudocode Entry

The term inter-privilege was incorrectly spelled in pseudocode provided as part of the "INT n/INTO/ INT 3—Call to Interrupt Procedure" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 2.*

The corrected text segment is reproduced below.

-----

...INTER-PRIVILEGE-LEVEL-INTERRUPT

(\* PE=1, interrupt or trap gate, non-conforming code segment, DPL<CPL \*)

(\* Check segment selector and descriptor for stack of new privilege level in current TSS \*)

IF current TSS is 32-bit TSS

THEN

$TSS stackAddress \leftarrow (new \ code \ segment \ DPL * 8) + 4....$

### 3. Confusing text Artifact Removed

There were some materials in the OPCODE table that should have been deleted. This error has been corrected. The corrected table segment (reproduced below) is in Appendix A, Table A-3, *IA-32 Intel Architecture Software Developer's Manual, Volume 2*. See address 0x0f0b

|   | 8    | 9      | А | В   | С | D | E | F |

|---|------|--------|---|-----|---|---|---|---|

| 0 | INVD | WBINVD |   | UD2 |   |   |   |   |

#### 4.

1

1

#### IA32\_MISC\_CTL Has Been Removed from the List of Architectural MSRs

The MSR IA32\_MISC\_CTL has been removed from the list of architectural MSRs . Note that this MSR is still listed in other locations.

The impacted segment (reproduced below) is from Appendix B, Table B-5, *IA-32 Intel Architecture Software Developer's Manual, Volume 3.* The change bars show where the table row was deleted.

| 79H  | 121 | IA32_BIOS_UPDT_TRIG | BIOS_UPDT_TRIG      | P6 Family Processors |

|------|-----|---------------------|---------------------|----------------------|

| 8BH  | 139 | IA32_BIOS_SIGN_ID   | BIOS_SIGN/BBL_CR_D3 | P6 Family Processors |

| FEH  | 254 | IA32_MTRRCAP        | MTRRcap             | P6 Family Processors |

| 174H | 372 | IA32_SYSENTER_CS    | SYSENTER_CS_MSR     | P6 Family Processors |

| 175H | 373 | IA32_SYSENTER_ESP   | SYSENTER_ESP_MSR    | P6 Family Processors |

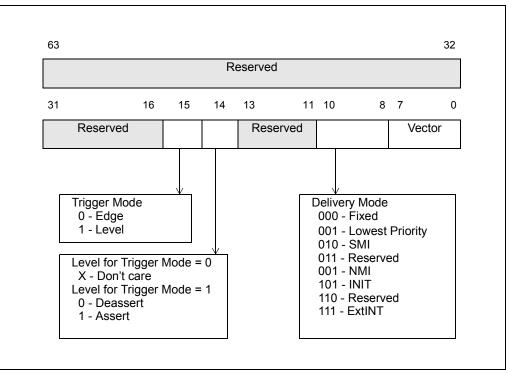

### 5. Typographical Error Corrected in Figure 8-24

ExINT should be ExtINT in Figure 8-24, located in the "Message Data Register Format" section, Chapter 8, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*. The corrected figure is reproduced below.

Figure 8-24. Layout of the MSI Message Data Register

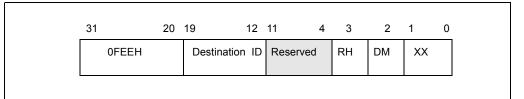

### 6. Typographical Error Corrected in Figure 8-23

0FEEH was incorrectly represented as 0FEEEH in Figure 8-23, located the "Message Address Register Format" section, Chapter 8, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*.

The corrected figure is reproduced below.

Figure 8-23. Layout of the MSI Message Address Register

7.

### Corrupted Text Corrected

There was some corrupted text in the "State of the Logical Processors" section, Chapter 7, *IA-32 Intel Architecture Software Developer's Manual, Volume 3.*

The correction is shown in the segment below. See the changebar.

-----

#### 7.6.1.1 State of the Logical Processors

The following features are considered part of the architectural state of a logical processor with HT Technology. The features can be subdivided into three groups:

- Duplicated for each logical processor

- Shared by logical processors in a physical processor

- Shared or duplicated, depending on the implementation

The following features are duplicated for each logical processor:

• General purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, ESP, and EBP)

.....

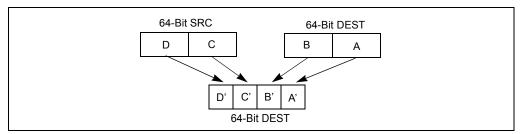

### 8. Corrected an Error in PACKSSDW Illustration

Operation of the PACKSSDW instruction was incorrectly illustrated in Figure 3-6, the "PACKSSWB/PACKSSDW—Pack with Signed Saturation" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 2.*

The corrected figure is reproduced below.

Figure 3.6. Operation of the PACKSSDW Instruction Using 64-bit Operands

#### 9. SSM Corrected to SMM

In several places, SSM was still being used as an acronym for 'system management mode.' The correct usage is SMM. Corrections were made in the "Modes of Operation" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 1*. The updated paragraph is reproduced below.

.....

**System management mode (SMM).** This mode provides a transparent mechanism for implementing platform-specific functions such as power management and system security. The processor enters SMM when the external SMM interrupt pin (SMI#) is activated or an SMI is received from the advanced programmable interrupt controller (APIC). In SMM, the processor switches to a separate address space while saving the basic context of the currently running program or task. SMM-specific code may then be executed transparently. Upon returning from SMM, the processor is placed back into its state prior to the system management interrupt. SMM was introduced with the Intel386 SL and Intel486 SL processors and became a standard IA-32 feature with the Pentium processor family.

This change was also made in the "RSM—Resume from

This change was also made in the "RSM—Resume from System Management Mode" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 2*. The corrected segments are reproduced below.

.....

Returns program control from system management mode (SMM) to the application program or operatingsystem procedure that was interrupted when the processor received an SMM interrupt. The processor's state is restored from the dump created upon entering SMM. If the processor detects invalid state information during state restoration, it enters the shutdown state....

ReturnFromSMM; ProcessorState ← Restore(SMMDump);

### 10. Exiting from SMM Text Updated

A paragraph in the "Exiting from SMM" section, Chapter 13, *IA-32 Intel Architecture Software Developer's Manual, Volume 3* has been updated. The information previously provided was not complete. The corrected text segment is reproduced below. See the change bar for location.

In the shutdown state, Intel processors stop executing instructions until a RESET#, INIT# or NMI# is asserted. Processors do recognize the FLUSH# signal in the shutdown state. While Pentium family processors recognize the SMI# signal in shutdown state, P6 family and Intel486 processors do not. Intel does not support using SMI# to recover from shutdown states for any processor family; the response of processors in this circumstance is not well defined. On Pentium 4 and later processors, shutdown will inhibit INTR and A20M but will not change any of the other inhibits. On these processors, NMIs will be inhibited if no action is taken in the SMM handler to uninhibit them (see Section 13.7.).

If the processor is in the HALT state when the SMI is received, the processor handles the return from SMM slightly differently (see Section 13.10., "Auto HALT Restart"). Also, the SMBASE address can be changed on a return from SMM (see Section 13.11., "SMBASE Relocation").

<sup>• (</sup>For the Pentium and Intel486 processors only.) If the address stored in the SMBASE register when an RSM instruction is executed is not aligned on a 32-KByte boundary. This restriction does not apply to the P6 family processors.

11.

### L1 Data Cache Context Mode Description Has Been Udpated

In Appendix B, Table B-1, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; the "L1 Data Cache Context Mode (RW)" table cell has been updated. Information about adaptive mode was clarified.

**Register Address Register Name** Shared/, Fields and Flags Unique **Bit Description** Hex Dec 24 L1 Data Cache Context Mode (R/W). When set to 1, this bit places the L1 Data Cache into shared mode. When set to 0 (the default), this bit places the L1 Data Cache into adaptive mode. When the L1 Data Cache is running in adaptive mode and the CR3s are identical, data in L1 is shared across logical processors. Otherwise, data in L1 is not shared and cache use is competitive. NOTE: If the Context ID feature flag, ECX[10], is not set to 1 after executing CPUID with EAX = 1; the ability to switch modes is not supported and the BIOS must not alter the contents of IA32 MISC ENABLE[24].

The updated table segment is reproduced below.

### 12. #DE Should Be #DB in Description of EFLAGS.RF

In the "System Flags and Fields in the EFLAGS Register" section, Chapter 2, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; there was a sentence that began "When set, this flag temporarily disables debug exceptions (#DE)". Debug exceptions are noted as #DB, not #DE. This error has been corrected.

The corrected entry is reproduced below.

-----

RF **Resume (bit 16).** Controls the processor's response to instruction-breakpoint conditions. When set, this flag temporarily disables debug exceptions (#DB) from being generated for instruction breakpoints; although, other exception conditions can cause an exception to be generated. When clear, instruction breakpoints will generate debug exceptions.

The primary function of the RF flag is to allow the restarting of an instruction following a debug exception that was caused by an instruction breakpoint condition. Here, debugger software must set this flag in the EFLAGS image on the stack just prior to returning to the interrupted program with the IRETD instruction, to prevent the instruction breakpoint from causing another debug exception. The processor then automatically clears this flag after the instruction returned to has been successfully executed, enabling instruction breakpoint faults again.

See Section 15.3.1.1., *Instruction-Breakpoint Exception Condition*, for more information on the use of this flag.

### 13. There Have Been Revisions to the Table That States Priority among Simultaneous Exceptions and Interrupts

We have made a number of updates to Table 5-2, located in the "Priority Among Simultaneous Exceptions and Interrupts" section, Chapter 5, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*.

The updated cells are reproduced below.

| Priority   | Descriptions (continued)                                                                                                                                                                                                                                                |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5          | External Interrupts<br>- NMI Interrupts<br>- Maskable Hardware Interrupts                                                                                                                                                                                               |  |  |  |  |

| 6          | Code Breakpoint Fault                                                                                                                                                                                                                                                   |  |  |  |  |

| 7          | Faults from Fetching Next Instruction<br>- Code-Segment Limit Violation<br>- Code Page Fault                                                                                                                                                                            |  |  |  |  |

| 8          | Faults from Decoding the Next Instruction<br>- Instruction length > 15 bytes<br>- Invalid Opcode<br>- Coprocessor Not Available                                                                                                                                         |  |  |  |  |

| 9 (Lowest) | Faults on Executing an Instruction<br>- Overflow<br>- Bound error<br>- Invalid TSS<br>- Segment Not Present<br>- Stack fault<br>- General Protection<br>- Data Page Fault<br>- Alignment Check<br>- x87 FPU Floating-point exception<br>- SIMD floating-point exception |  |  |  |  |

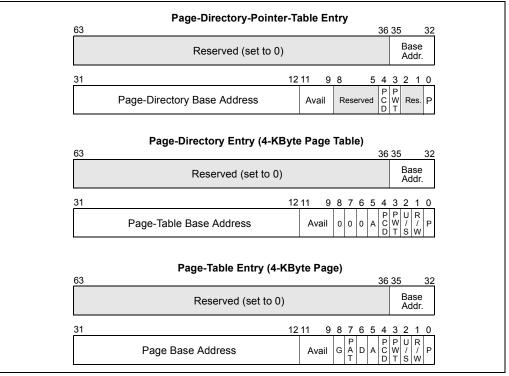

14.

### Corrections to Page-Directory-Pointer-Table Entry Desciption

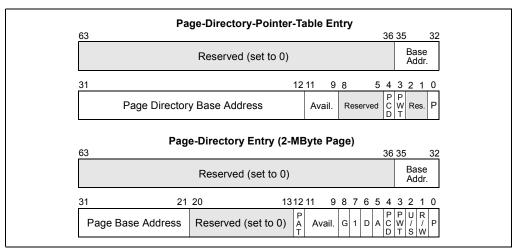

In Figure 3-20 and 3-21, located in the "Page-Directory and Page-Table Entries With Extended Addressing Enabled" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; Bit 0 of both representations of the Page-Directory-Pointer-Table Entry now indicate P (showing the the location of the 'present flag' bit).

The corrected tables are reproduced below.

Figure 3-20. Format of Page-Directory-Pointer-Table, Page-Directory, and Page-Table Entries for 4-KByte Pages with PAE Enabled

In addition, the paragraph discussing the present flag has been updated. this text is also located in the "Page-Directory and Page-Table Entries With Extended Addressing Enabled" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 3.*

The applicable text segment is reproduced below. Note the change bar.

The present flag (bit 0) in the page-directory-pointer-table entries can be set to 0 or 1. If the present flag is clear, the remaining bits in the page-directory-pointer-table entry are available to the operating system. If the present flag is set, the fields of the page-directory-pointer-table entry are defined in Figures for 4KB pages and Figures for 2MB pages.

The page size (PS) flag (bit 7) in a page-directory entry determines if the entry points to a page table or a 2-MByte page. When this flag is clear, the entry points to a page table; when the flag is set, the entry points to a 2-MByte page. This flag allows 4-KByte and 2-MByte pages to be mixed within one set of paging tables.

For all table entries (except for page-directory entries that point to 2-MByte pages), the bits in the page base address are interpreted as the 24 most-significant bits of a 36-bit physical address, which forces page tables and pages to be aligned on 4-KByte boundaries. When a page-directory entry points to a 2-MByte page, the base address is interpreted as the 15 most-significant bits of a 36-bit physical address, which forces pages to be aligned on 2-MByte boundaries.

#### 15.

### Behavior Notes on the Accessed (A) Flag and Dirty (D) Flag

Notes have been added to two sub-paragraphs of the "Page-Directory and Page-Table Entries" section, Chapter 3, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*. The notes clarify a limitation on the processor's Self-Modifying Code detection logic in the Accessed (A) flag and Dirty (D) flag context.

The applicable sections are reproduced below. See the change bars.

-----

#### Accessed (A) flag, bit 5

Indicates whether a page or page table has been accessed (read from or written to) when set. Memory management software typically clears this flag when a page or page table is initially loaded into physical memory. The processor then sets this flag the first time a page or page table is accessed.

This flag is a "sticky" flag, meaning that once set, the processor does not implicitly clear it. Only software can clear this flag. The accessed and dirty flags are provided for use by memory management software to manage the transfer of pages and page tables into and out of physical memory.

**NOTE:** The accesses used by the processor to set this bit may or may not be exposed to the processor's Self-Modifying Code detection logic. If the processor is executing code from the same memory area that is being used for page table structures, the setting of the bit may or may not result in an immediate change to the executing code stream.

#### Dirty (D) flag, bit 6

Indicates whether a page has been written to when set. (This flag is not used in page-directory entries that point to page tables.) Memory management software typically clears this flag when a page is initially loaded into physical memory. The processor then sets this flag the first time a page is accessed for a write operation.

This flag is "sticky," meaning that once set, the processor does not implicitly clear it. Only software can clear this flag. The dirty and accessed flags are provided for use by memory management software to manage the transfer of pages and page tables into and out of physical memory.

**NOTE:** The accesses used by the processor to set this bit may or may not be exposed to the processor's Self-Modifying Code detection logic. If the processor is executing code from the same memory area that is being used for page table structures, the setting of the bit may or may not result in an immediate change to the executing code stream.

### 16. Interrupt 11 Discussion Concerning EXT Flag Functioning Has Been Updated

The Volume 3, Chapter 5, Interrupt 11: Error Code section has been updated. This section now provides a more complete description of the EXT flag. The impacted text is reproduced below.

-----

#### Exception Error Code

An error code containing the segment selector index for the segment descriptor that caused the violation is pushed onto the stack of the exception handler. If the EXT flag is set, it indicates that the exception resulted from either:

- an external event (NMI or INTR) that caused an interrupt, which subsequently referenced a not-present segment.

- a benign exception that subsequently referenced a not-present segment. A contributory exception or page fault that subsequently referenced a not-present segment would cause a double fault (#DF) to be generated instead of #NP.

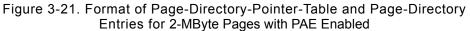

### 17. Improved Information on Interpreting Machine-Check Error Codes

In Volume 3, Appendix E has been re-written to incorporate new IA32\_MCi\_STATUS data. Encoding of the model-specific and other information fields is different for the 06H and 0FH processor families. Changes are documented in the following sections.

\_\_\_\_\_

### E.1. DECODING FAMILY 06H SPECIFIC MACHINE ERROR CODES

Machine error code reporting by processor family 06H is based on values read from IA32\_MC*i*\_STATUS (Figure E-1).

Figure E-1. IA32\_MCi\_STATUS Encoding for Family 06H

Table E-1 shows how to interpret internal watchdog timer timeout machine-check errors reported in IA32\_MC*i*\_STATUS for processor family 06H.

|                                 | Bit No. | Bit Function     | Bit Description                                                                                                   |  |

|---------------------------------|---------|------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Architectural MCA<br>error code | 0-15    | 0000010000000000 | Internal watchdog timer timeout. Note that a watch-dog timer time-out only occurs if the BINIT driver is enabled. |  |

| Model-specific error codes      | 16-31   | Reserved         | Reserved                                                                                                          |  |

| Other information               | 32-56   | Reserved         | Reserved                                                                                                          |  |

#### Table E-1. Family 06H Encoding of Internal Watchdog Timer Errors Reported in IA32\_MCi\_STATUS

Table E-2 shows how to interpret errors that occur on the external bus.

| Туре                     | Bit No. | Bit Function                                     | Bit Description                                                                                                                                                                         |

|--------------------------|---------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCA error                | 0-1     | Reserved                                         | Reserved.                                                                                                                                                                               |

| codes                    | 2-3     | For external bus errors:<br>special cycle or I/O | <ul> <li>For external bus errors:</li> <li>Bit 2 is set to 1 if the access was a special cycle.</li> <li>Bit 3 is set to 1 if the access was a special cycle OR a I/O cycle.</li> </ul> |

|                          |         | For internal timeout:<br>Reserved                | For internal timeout:<br>Reserved                                                                                                                                                       |

|                          | 4-7     | For external bus errors:<br>Read/Write           | For external bus errors, 00WR:<br>W = 1 for writes<br>R = 1 for reads                                                                                                                   |

|                          |         | For internal timeout:<br>Reserved                | For internal timeout:<br>Reserved                                                                                                                                                       |

|                          | 8-9     | Reserved                                         | Reserved                                                                                                                                                                                |

|                          | 10-11   | 10                                               | External bus errors                                                                                                                                                                     |

|                          |         | 01                                               | Internal watchdog timer timeout                                                                                                                                                         |

|                          | 12-15   | Reserved                                         | Reserved                                                                                                                                                                                |

| Model specific<br>errors | 16-18   | Reserved                                         | Reserved                                                                                                                                                                                |

#### Table E-2. Family 06H Encoding 32\_MCi\_STATUS for External Bus Errors

| Туре                     | Bit No. | Bit Function           | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|---------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model specific<br>errors | 19-24   | Bus queue request type | 000000 for BQ_DCU_READ_TYPE error<br>000010 for BQ_IFU_DEMAND_TYPE error<br>000011 for BQ_IFU_DEMAND_NC_TYPE error<br>000100 for BQ_DCU_RFO_TYPE error<br>000101 for BQ_DCU_RFO_LOCK_TYPE error<br>000100 for BQ_DCU_ITOM_TYPE error<br>001000 for BQ_DCU_WB_TYPE error<br>001010 for BQ_DCU_WCEVICT_TYPE error<br>001011 for BQ_DCU_WCLINE_TYPE error<br>001010 for BQ_DCU_BTM_TYPE error                                                         |

|                          |         |                        | 001101 for BQ_DCU_INTACK_TYPE error<br>001110 for BQ_DCU_INVALL2_TYPE error<br>001111 for BQ_DCU_FLUSHL2_TYPE error<br>010000 for BQ_DCU_PART_RD_TYPE error<br>010010 for BQ_DCU_PART_WR_TYPE error<br>010100 for BQ_DCU_SPEC_CYC_TYPE error<br>011000 for BQ_DCU_IO_RD_TYPE error<br>011001 for BQ_DCU_IO_WR_TYPE error<br>011100 for BQ_DCU_LOCK_RD_TYPE error<br>011110 for BQ_DCU_SPLOCK_RD_TYPE error                                         |

|                          |         |                        | 011101 for BQ_DCU_LOCK_WR_TYPE error<br>000010 for BQ_IFU_DEMAND_TYPE error<br>000011 for BQ_IFU_DEMAND_NC_TYPE error<br>000100 for BQ_DCU_RFO_TYPE error<br>000101 for BQ_DCU_RFO_LOCK_TYPE error<br>000110 for BQ_DCU_ITOM_TYPE error<br>001000 for BQ_DCU_WB_TYPE error<br>001010 for BQ_DCU_WCEVICT_TYPE error<br>001011 for BQ_DCU_WCLINE_TYPE error<br>001100 for BQ_DCU_BTM_TYPE error                                                      |

|                          |         |                        | 001101 for BQ_DCU_INTACK_TYPE error<br>001110 for BQ_DCU_INVALL2_TYPE error<br>001111 for BQ_DCU_FLUSHL2_TYPE error<br>010000 for BQ_DCU_PART_RD_TYPE error<br>010010 for BQ_DCU_PART_WR_TYPE error<br>010100 for BQ_DCU_SPEC_CYC_TYPE error<br>011000 for BQ_DCU_IO_RD_TYPE error<br>011001 for BQ_DCU_IO_WR_TYPE error<br>011100 for BQ_DCU_LOCK_RD_TYPE error<br>011110 for BQ_DCU_SPLOCK_RD_TYPE error<br>011101 for BQ_DCU_LOCK_WR_TYPE error |

| Model specific<br>errors | 27-25   | Bus queue error type   | 000 for BQ_ERR_HARD_TYPE error<br>001 for BQ_ERR_DOUBLE_TYPE error<br>010 for BQ_ERR_AERR2_TYPE error<br>100 for BQ_ERR_SINGLE_TYPE error<br>101 for BQ_ERR_AERR1_TYPE error                                                                                                                                                                                                                                                                       |

| Table E-2. Far | nily 06H | Encoding 32_ | MCi_STA | TUS for External | Bus Errors | (Continued) |

|----------------|----------|--------------|---------|------------------|------------|-------------|

|                |          |              |         |                  |            |             |

| Туре           | Bit No. | Bit Function             | Bit Description                                                                                                                                                                                                                                                                                                                        |

|----------------|---------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model specific | 28      | FRC error                | 1 if FRC error active                                                                                                                                                                                                                                                                                                                  |

| errors         | 29      | BERR                     | 1 if BERR is driven                                                                                                                                                                                                                                                                                                                    |

|                | 30      | Internal BINIT           | 1 if BINIT driven for this processor                                                                                                                                                                                                                                                                                                   |

|                | 31      | Reserved                 | Reserved                                                                                                                                                                                                                                                                                                                               |

| Other          | 32-34   | Reserved                 | Reserved                                                                                                                                                                                                                                                                                                                               |

| information    | 35      | External BINIT           | 1 if BINIT is received from external bus.                                                                                                                                                                                                                                                                                              |

|                | 36      | RESPONSE PARITY<br>ERROR | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has received a parity error on the RS[2:0]# pins for a response transaction. The RS signals are checked by the RSP# external pin.                                                                                                                                   |

|                | 37      | BUS BINIT                | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has received a hard error response on a split transaction (one access that has needed to be split across the 64-bit external bus interface into two accesses).                                                                                                      |

|                | 38      | TIMEOUT BINIT            | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has experienced a ROB time-out, which indicates that no micro-instruction has been retired for a predetermined period of time.                                                                                                                                      |

|                |         |                          | A ROB time-out occurs when the 15-bit ROB time-out counter carries a 1 out of its high order bit. The timer is cleared when a micro-instruction retires, an exception is detected by the core processor, RESET is asserted, or when a ROB BINIT occurs.                                                                                |

|                |         |                          | The ROB time-out counter is prescaled by the 8-<br>bit PIC timer which is a divide by 128 of the bus<br>clock (the bus clock is 1:2, 1:3, 1:4 of the core<br>clock). When a carry out of the 8-bit PIC timer<br>occurs, the ROB counter counts up by one.<br>While this bit is asserted, it cannot be overwritten<br>by another error. |

|                | 39-41   | Reserved                 | Reserved                                                                                                                                                                                                                                                                                                                               |

|                | 42      | HARD ERROR               | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has initiated a bus transactions which has received a hard error response. While this bit is asserted, it cannot be overwritten.                                                                                                                                    |

|                | 43      | IERR                     | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has experienced a failure that causes the IERR pin to be asserted. While this bit is asserted, it cannot be overwritten.                                                                                                                                            |

Table E-2. Family 06H Encoding 32\_MCi\_STATUS for External Bus Errors (Continued)

| Туре                 | Bit No. | Bit Function | Bit Description                                                                                                                                                                                                                                                                                          |

|----------------------|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Other<br>information | 44      | AERR         | This bit is asserted in IA32_MC <i>i</i> _STATUS if this component has initiated 2 failing bus transactions which have failed due to Address Parity Errors (AERR asserted). While this bit is asserted, it cannot be overwritten.                                                                        |

|                      | 45      | UECC         | The Uncorrectable ECC error bit is asserted in IA32_MCi_STATUS for uncorrected ECC errors. While this bit is asserted, the ECC syndrome field will not be overwritten.                                                                                                                                   |

|                      | 46      | CECC         | The correctable ECC error bit is asserted in IA32_MCi_STATUS for corrected ECC errors.                                                                                                                                                                                                                   |

|                      | 47-54   | ECC syndrome | The ECC syndrome field in IA32_MC <i>i</i> _STATUS contains the 8-bit ECC syndrome only if the error was a correctable/uncorrectable ECC error and there wasn't a previous valid ECC error syndrome logged in IA32_MC <i>i</i> _STATUS.                                                                  |

|                      |         |              | A previous valid ECC error in<br>IA32_MCi_STATUS is indicated by<br>IA32_MCi_STATUS.bit45 (uncorrectable error<br>occurred) being asserted. After processing an<br>ECC error, machine-check handling software<br>should clear IA32_MCi_STATUS.bit45 so that<br>future ECC error syndromes can be logged. |

|                      | 55-56   | Reserved     | Reserved.                                                                                                                                                                                                                                                                                                |

| Table E-2. Family 06H | I Encoding 32_MC <i>i</i> _ST | ATUS for External Bus Errors | (Continued) |

|-----------------------|-------------------------------|------------------------------|-------------|

|                       |                               |                              |             |

### E.2. DECODING FAMILY 0FH SPECIFIC MACHINE ERROR CODES

Machine error code reporting by processor family 0FH is also based on values read from IA32\_MCi\_STATUS (Figure E-2).

| 56                                                            | CA Error Codes<br>27-26 | 10      | 0 |

|---------------------------------------------------------------|-------------------------|---------|---|

|                                                               |                         |         |   |

| Thread timeout ind<br>Internal watchdog                       |                         |         |   |

| External Bus Err                                              |                         |         |   |

| 56                                                            | 32 - 31                 | 16 - 15 | C |

| Other information<br>Model specific err<br>Architectural corr |                         |         |   |

| Memory Hierarcl                                               | hy Error Codes          |         |   |

| 56                                                            | 32 - 31                 | 16 - 15 | C |

|                                                               |                         |         |   |

|                                                               |                         |         |   |

| Other information                                             |                         |         |   |

| Model specific err                                            |                         |         |   |

Figure E-2. IA32\_MCi\_STATUS Encoding for Family 0FH

Table E-3 provides information on how to interpret processor family 0FH error code fields for internal watchdog timer timeout machine-checks.

|                                 | Bit<br>No. | Bit Function                     | Bit Description                                                                                                                               |  |

|---------------------------------|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architectural<br>MCA error code | 0-15       | 000001000000000                  | Internal watchdog timer timeout. Note that a watch-dog timer time-out only occurs if the BINIT driver is enabled.                             |  |

| Model-specific                  | 16-25      | Reserved                         | Reserved                                                                                                                                      |  |

| error code                      | 26-27      | Thread timeout<br>indicator (TT) | Contains the indication of the thread which time<br>out:<br>01 - Thread 0 timed out<br>10 - Thread 1 timed out<br>11 - Both threads timed out |  |

|                                 | 28-31      | Reserved                         | Reserved                                                                                                                                      |  |

| Other information               | 32-56      | Reserved                         | Reserved                                                                                                                                      |  |

#### Table E-3. Family 0FH Encoding of IA32\_MCi\_STATUS for Internal Watchdog Timer Errors

Table E-4 provides the information to interpret errors that occur on the external bus. Note that processor family 0FH uses the compound MCA code format for external bus errors. Refer to *Chapter 14, Machine-Check Architecture* for more information.

|                                   | Bit<br>No. | Bit Function                                               | Bit Description                                                                                                                                                                                          |  |

|-----------------------------------|------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architectural compound            | 0-1        | Memory hierarchy level (LL)                                | Refer to Table 14-5 for detailed decoding of the memory hierarchy level (LL) sub-field.                                                                                                                  |  |

| MCA error<br>codes                | 2-3        | Memory and I/O (II)                                        | Refer to Table 14-7 for a detailed decoding of the memory or IO (II) sub-field.                                                                                                                          |  |

|                                   | 4-7        | Request (RRRR)                                             | Refer to Table 14-6 for a detailed decoding of the request (RRRR) sub-field.                                                                                                                             |  |

|                                   | 8          | Timeout (T)                                                | Refer to Table 14-7 for a detailed decoding of the Timeout (T) Sub-Field.                                                                                                                                |  |

|                                   | 9-10       | Participation (PP)                                         | Refer to Table 14-7 for a detailed decoding of the participation (PP) sub-field.                                                                                                                         |  |

|                                   | 11-15      | 00001                                                      | Bus and interconnect errors                                                                                                                                                                              |  |

| Model-<br>specific error<br>codes | 16         | FSB address parity                                         | Address parity error detected:<br>1 = Address parity error detected<br>0 = No address parity error                                                                                                       |  |

|                                   | 17         | Response hard fail                                         | Hardware failure detected on response                                                                                                                                                                    |  |

|                                   | 18         | Response parity                                            | Parity error detected on response                                                                                                                                                                        |  |

|                                   | 19         | PIC and FSB data parity                                    | Data Parity detected on either PIC or FSB access                                                                                                                                                         |  |

|                                   | 20         | Processor Signature =<br>00000F04H: Invalid PIC<br>request | Processor Signature = 00000F04H. Indicates<br>error due to an invalid PIC request (access was<br>made to PIC space with WB memory):<br>1 = Invalid PIC request error<br>0 = No Invalid PIC request error |  |

|                                   |            | All other processors:<br>Reserved                          | Reserved                                                                                                                                                                                                 |  |

|                                   | 21         | Pad state machine                                          | The state machine that tracks P and N data-<br>strobe relative timing has become<br>unsynchronized or a glitch has been detected.                                                                        |  |

|                                   | 22         | Pad strobe glitch                                          | Data strobe glitch                                                                                                                                                                                       |  |

|                                   | 23         | Pad address glitch                                         | Address strobe glitch                                                                                                                                                                                    |  |

|                                   | 24-31      | Reserved                                                   | Reserved                                                                                                                                                                                                 |  |

| Other<br>Information              | 32-56      | Reserved                                                   | Reserved                                                                                                                                                                                                 |  |

Table E-4. Family 0FH Encoding of IA32\_MCi\_STATUS for External Bus Errors

Table E-5 provides information on how to interpret errors that occur within the memory hierarchy.

Table E-5. Family 0FH Encoding of IA32\_MCi\_STATUS for Memory Hierarchy Errors

|                               | Bit No. | Bit Function                | Bit Description                                                                                                                                                                                                                                           |

|-------------------------------|---------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architectural compound        | 0-1     | Memory Hierarchy Level (LL) | Refer to Table 14-5 for a detailed decoding of the memory hierarchy level (LL) sub-field.                                                                                                                                                                 |

| MCA error<br>code             | 2-3     | Transaction Type (TT)       | Refer to Table 14-5 for a detailed decoding of the transaction type (TT) sub-field.                                                                                                                                                                       |

|                               | 4-7     | Request (RRRR)              | Refer to Table 14-6 for a detailed decoding of the request type (RRRR) sub-field.                                                                                                                                                                         |

|                               | 8-15    | 0000001                     | Memory hierarchy error format                                                                                                                                                                                                                             |

| Model specific<br>error codes | 16-17   | Tag Error Code              | Contains the tag error code for this machine<br>check error:<br>00 = No error detected<br>01 = Parity error on tag miss with a clean<br>line<br>10 = Parity error/multiple tag match on tag<br>hit<br>11 = Parity error/multiple tag match on tag<br>miss |

|                               | 18-19   | Data Error Code             | Contains the data error code for this machine<br>check error:<br>00 = No error detected<br>01 = Single bit error<br>10 = Double bit error on a clean line<br>11 = Double bit error on a modified line                                                     |

|                               | 20      | L3 Error                    | This bit is set if the machine check error<br>originated in the L3 (it can be ignored for<br>invalid PIC request errors):<br>1 = L3 error<br>0 = L2 error                                                                                                 |

|                               | 21      | Invalid PIC Request         | Indicates error due to invalid PIC request<br>(access was made to PIC space with WB<br>memory):<br>1 = Invalid PIC request error<br>0 = No invalid PIC request error                                                                                      |

|                               | 22-31   | Reserved                    | Reserved                                                                                                                                                                                                                                                  |

| Other<br>Information          | 32-39   | 8-bit Error Count           | Holds a count of the number of errors since<br>reset. The counter begins at 0 for the first error<br>and saturates at a count of 254.                                                                                                                     |

|                               | 40-56   | Reserved                    | Reserved                                                                                                                                                                                                                                                  |

### 18. More information on the Functioning of Debug BPs after POP SS/MOV SS Has Been Provided

In Volume 3, Section 15.3.1.1; more information has been provided on the functioning of code instruction breakpoints immediately after POP SS/MOV SS instructions. This data is reprinted below (in context). Footnotes have been added to the POP and MOV sections in Volume 2 of the IA-32 Intel Architecture Software Developer's Manual which contain the same information for POP SS/ MOV SS (the footnotes are not reproduced here).

\_\_\_\_\_

### 15.3.1.1. INSTRUCTION-BREAKPOINT EXCEPTION CONDITION

The processor reports an instruction breakpoint when it attempts to execute an instruction at an address specified in a breakpoint-address register (DB0 through DR3) that has been set up to detect instruction execution (R/W flag is set to 0). Upon reporting the instruction breakpoint, the processor generates a fault-class, debug exception (#DB) before it executes the target instruction for the breakpoint.

Instruction breakpoints are the highest priority debug exceptions. They are serviced before any other exceptions detected during the decoding or execution of an instruction. Note, however, that if a code instruction breakpoint is placed on an instruction located immediately after a POP SS/MOV SS instruction, it may not be triggered. In most situations, POP SS/MOV SS will inhibit such interrupts (see "MOV-Move" and "POP-Pop a Value from the Stack" in the *IA-32 Intel Architecture Software Developer's Manual, Volume 2*).

#### 19.

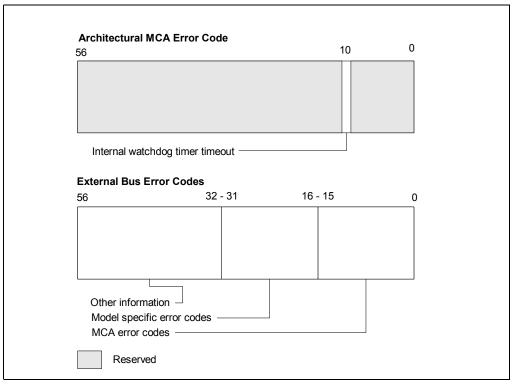

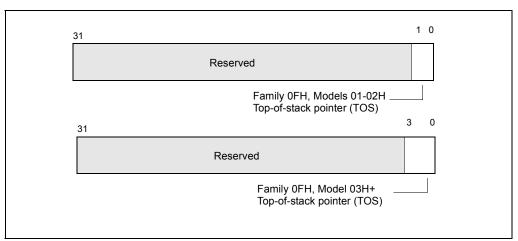

### More Information on the LBR Stack Has Been Provided

The following information has been added to Volume 3 of the IA-32 Intel Architecture Software Developer's Manual, Section 15.5. This information describes the LBR stack and MSR\_LASTBRANCH\_TOS

- Last Branch Record (LBR) Stack The LBR stack is a circular stack that consists of four MSRs (MSR\_LASTBRANCH\_0 through MSR\_LASTBRANCH\_3) for the Pentium 4 and Intel Xeon processor family [CPUID family 0FH, models 0H-02H]. The LBR stack consists of 16 MSR pairs (MSR\_LASTBRANCH\_0\_FROM\_LIP through MSR\_LASTBRANCH\_15\_FROM\_LIP and MSR\_LASTBRANCH\_0\_TO\_LIP through MSR\_LASTBRANCH\_15\_TO\_LIP) for the Pentium 4 and Intel Xeon processor family [CPUID family 0FH, model 03H].

- Last Branch Record Top-of-Stack (TOS) Pointer The TOS Pointer MSR contains a 2-bit pointer (0-3) to the MSR in the LBR stack that contains the most recent branch, interrupt, or exception recorded for the Pentium 4 and Intel Xeon processor family [CPUID family 0FH, models 0H-02H]. This pointer becomes a 4-bit pointer (0-15) for the Pentium 4 and Intel Xeon processor family [CPUID family 0FH, model 03H].

See also: Table 15-2, Figure 15-3, and Figure 15-4 below.

| LBR MSRs for Family 0FH, Models 0H-<br>02H; MSRs at locations 1DBH-1DEH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Decimal Value of TOS Pointer in<br>MSR_LASTBRANCH_TOS (bits<br>0-1)                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| MSR_LASTBRANCH_0<br>MSR_LASTBRANCH_1<br>MSR_LASTBRANCH_2<br>MSR_LASTBRANCH_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0<br>1<br>2<br>3                                                                   |

| LBR MSRs for Family 0FH, Models;<br>MSRs at locations 680H-68FH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decimal Value of TOS Pointer in<br>MSR_LASTBRANCH_TOS (bits<br>0-3)                |

| MSR_LASTBRANCH_0_FROM_LIP<br>MSR_LASTBRANCH_1_FROM_LIP<br>MSR_LASTBRANCH_2_FROM_LIP<br>MSR_LASTBRANCH_3_FROM_LIP<br>MSR_LASTBRANCH_4_FROM_LIP<br>MSR_LASTBRANCH_5_FROM_LIP<br>MSR_LASTBRANCH_6_FROM_LIP<br>MSR_LASTBRANCH_8_FROM_LIP<br>MSR_LASTBRANCH_9_FROM_LIP<br>MSR_LASTBRANCH_9_FROM_LIP<br>MSR_LASTBRANCH_10_FROM_LIP<br>MSR_LASTBRANCH_11_FROM_LIP<br>MSR_LASTBRANCH_12_FROM_LIP<br>MSR_LASTBRANCH_13_FROM_LIP<br>MSR_LASTBRANCH_14_FROM_LIP<br>MSR_LASTBRANCH_14_FROM_LIP<br>MSR_LASTBRANCH_15_FROM_LIP                                        | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 |

| LBR MSRs for Family 0FH, Model 03H;<br>MSRs at locations 6C0H-6CFH.<br>MSR_LASTBRANCH_0_TO_LIP<br>MSR_LASTBRANCH_1_TO_LIP<br>MSR_LASTBRANCH_2_TO_LIP<br>MSR_LASTBRANCH_3_TO_LIP<br>MSR_LASTBRANCH_4_TO_LIP<br>MSR_LASTBRANCH_6_TO_LIP<br>MSR_LASTBRANCH_6_TO_LIP<br>MSR_LASTBRANCH_8_TO_LIP<br>MSR_LASTBRANCH_10_TO_LIP<br>MSR_LASTBRANCH_10_TO_LIP<br>MSR_LASTBRANCH_11_TO_LIP<br>MSR_LASTBRANCH_12_TO_LIP<br>MSR_LASTBRANCH_12_TO_LIP<br>MSR_LASTBRANCH_13_TO_LIP<br>MSR_LASTBRANCH_13_TO_LIP<br>MSR_LASTBRANCH_13_TO_LIP<br>MSR_LASTBRANCH_14_TO_LIP | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 |

Figure 15-3. MSR\_LASTBRANCH\_TOS MSR Layout for the Pentium 4 and Intel Xeon Processor Family

| 33                                                       | 32 - 31                  |                     | 0                |

|----------------------------------------------------------|--------------------------|---------------------|------------------|

| To Linear Address                                        |                          | From Linear Address | s                |

| <b>CPUID Family 0FH, Model 0</b><br>MSR_LASTBRANCH_0_FRC |                          | h MSR_LASTBRANCH_   | 15_FROM_LIP      |

| MSR_LASTBRANCH_0_FRC                                     |                          | h MSR_LASTBRANCH_   | 15_FROM_LIP<br>0 |

| • ·                                                      | DM_LIP throug            | h MSR_LASTBRANCH_   |                  |

| MSR_LASTBRANCH_0_FRC<br>63                               | 0M_LIP throug<br>32 - 31 | From Linear Address | <br>s            |

Figure 15-4. LBR MSR Branch Record Layout for the Pentium 4 and Intel Xeon Processor Family

*Volume 3, Appendix B, Table B-1 has also been updated to reflect new LBR stack information. Impacted cells are reproduced below.*

\_\_\_\_\_

T

T

| Regi<br>Add | ister<br>ress | Register Name<br>Fields and Flags | Model<br>Avail-<br>ability | Shared/<br>Unique <sup>1</sup> | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------|-----------------------------------|----------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex         | Dec           |                                   | ability                    |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1DAH        | 474           | MSR_LASTBRANCH<br>_TOS            | 0, 1, 2,<br>3              | Unique                         | Last Branch Record Stack TOS. (R)<br>Contains an index (0-3 or 0-15) that<br>points to the top of the last branch<br>record stack (that is, that points the<br>index of the MSR containing the most<br>recent branch record.                                                                                                                                                                                                                                              |

| 1DBH        | 475           | MSR_LASTBRANCH<br>_0              | 0, 1, 2                    | Unique                         | Last Branch Record 0. (R/W) One o<br>four last branch record registers on th<br>last branch record stack. It contains<br>pointers to the source and destination<br>instruction for one of the last four<br>branches, exceptions, or interrupts that<br>the processor took.<br>NOTE: MSR_LASTBRANCH_0<br>through MSR_LASTBRANCH_3 at<br>1DBH-1DEH are available only on<br>family 0FH, models 0H-02H. They<br>have been replaced by the MSRs at<br>680H-68FH and 6C0H-6CFH |

| 1DCH        | 476           | MSR_LASTBRANCH                    | 0, 1, 2                    | Unique                         | Last Branch Record 1. See<br>description of the<br>MSR_LASTBRANCH_0 MSR at<br>1DBH.                                                                                                                                                                                                                                                                                                                                                                                       |

| 1DDH        | 477           | MSR_LASTBRANCH<br>_ <sup>2</sup>  | 0, 1, 2                    | Unique                         | Last Branch Record 2. See<br>description of the<br>MSR_LASTBRANCH_0 MSR at<br>1DBH.                                                                                                                                                                                                                                                                                                                                                                                       |

| 1DEH        | 478           | MSR_LASTBRANCH<br>_ <sup>3</sup>  | 0, 1, 2                    | Unique                         | Last Branch Record 3. See<br>description of the<br>MSR_LASTBRANCH_0 MSR at<br>1DBH.                                                                                                                                                                                                                                                                                                                                                                                       |

| 680H        | 1664          | MSR_LASTBRANCH<br>_0_FROM_LIP     | 3                          | Unique                         | Last Branch Record 0. (R/W) One of 16 pairs of last branch record register on the last branch record stack (680H 68FH). This part of the stack contains pointers to the source instruction for one of the last 16 branches, exceptions, or interrupts taken by the processor.<br>NOTE: The MSRs at 680H-68FH,                                                                                                                                                             |

|             |               |                                   |                            |                                | 6C0H-6CfH are not available in<br>processor releases before family 0FH<br>model 03H. These MSRs replace<br>MSRs previously located at 1DBH-<br>1DEH which performed the same<br>function for early releases.                                                                                                                                                                                                                                                              |

| 681H        | 1665          | MSR_LASTBRANCH<br>_1_FROM_LIP     | 3                          | Unique                         | Last Branch Record 1. See<br>description of MSR_LASTBRANCH_(<br>at 680H.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 682H        | 1666          | MSR_LASTBRANCH<br>_2_FROM_LIP     | 3                          | Unique                         | Last Branch Record 2. See<br>description of MSR_LASTBRANCH_<br>at 680H.                                                                                                                                                                                                                                                                                                                                                                                                   |

### Table B-1. MSRs in the Pentium 4 and Intel Xeon Processors