### IA-32 Intel<sup>®</sup> Architecture and Intel<sup>®</sup> Extended Memory 64 Technology Software Developer's Manual

**Documentation Changes**

May 2004

Note: 64-Bit Extension Technology Software Developer's Guide will be renamed to: Intel<sup>®</sup> Extended Memory 64 Technology Software Developer's Guide.

**Notice:** The IA-32 Intel<sup>®</sup> Architecture and Intel<sup>®</sup> Extended Memory 64 Technology may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IA-32 Intel<sup>®</sup> Architecture and Intel<sup>®</sup> Extended Memory 64 Technology may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Celeron, Intel SpeedStep, Intel Xeon and the Intel logo, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002-2004, Intel Corporation

# int<sub>el</sub>。 Contents

| Revision History         | . 4 |

|--------------------------|-----|

| Preface                  | . 5 |

| Summary Table of Changes | . 6 |

| Documentation Changes    | . 7 |

intel®

### **Revision History**

| Version | Description                                                                                                                                                                                                                        | Date           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001    | Initial Release                                                                                                                                                                                                                    | November 2002  |

| -002    | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                            | December 2002  |

| -003    | <ul> <li>Added 9 -17 Documentation Changes</li> <li>Removed Documentation Change #6 - References to bits Gen and<br/>Len Deleted</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI<br/>Discussion</li> </ul> | February 2003  |

| -004    | <ul><li>Removed Documentation changes 1-17</li><li>Added Documentation changes 1-24</li></ul>                                                                                                                                      | June 2003      |

| -005    | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-15</li></ul>                                                                                                                                      | September 2003 |

| -006    | Added Documentation Changes 16- 34                                                                                                                                                                                                 | November 2003  |

| -007    | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                                     | January 2004   |

| -008    | <ul><li>Removed Documentation Changes 1-45</li><li>Added Documentation Changes 1-5</li></ul>                                                                                                                                       | March 2004     |

| -009    | Added Documentation Changes 7-27                                                                                                                                                                                                   | May 2004       |

I

# intel® Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of documentation changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

### **Affected Documents/Related Documents**

| Document Title                                                                                          | Document<br>Number |

|---------------------------------------------------------------------------------------------------------|--------------------|

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 1, Basic Architecture         | 253665             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 2A, Instruction Set Reference | 253666             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 2B, Instruction Set Reference | 253667             |

| IA-32 Intel <sup>®</sup> Architecture Software Developer's Manual: Volume 3, System Programming Guide   | 253668             |

| Intel <sup>®</sup> Extended Memory 64 Technology Software Developer's Guide Volumes 1 and 2             | 300835             |

### **Nomenclature**

Documentation Changes include errors or omissions from the current published specifications. These changes will be incorporated in the next release of the Software Development Manual.

### **Summary Table of Changes**

The following table indicates documentation changes which apply to the IA-32 Intel Architecture. This table uses the following notations:

### **Codes Used in Summary Table**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

#### **Summary Table of Documentation Changes**

| Number | Documentation Changes                                              |  |

|--------|--------------------------------------------------------------------|--|

| 1.     | CPUID Sector Size, Cache Line Size Expressions Have Been Updated   |  |

| 2.     | LDDQU Description Text Has Been Added                              |  |

| 3.     | ANDNPD/ANDNPS Exception Lists Corrected                            |  |

| 4.     | PSADBW Instruction Description Section Corrected                   |  |

| 5.     | Reference to Wrong Step Corrected                                  |  |

| 6.     | APIC Chapter Updated                                               |  |

| 7.     | IA32_MC1_MISC, IA32_MC2_MISC, and IA32_MC2_ADDR Listings Corrected |  |

| 8.     | Ambiguity Correction                                               |  |

| 9.     | Invalid TSS Conditions Listing Has Been Updated                    |  |

| 10.    | Description Section Corrected                                      |  |

| 11.    | IA-32e Updates for LLDT, LMSW, LTR, SLDT, SMSW, STR                |  |

| 12.    | 66H Prefix in 64-bit Mode Information Added                        |  |

| 13.    | MOV—Move to/from Control Registers Section Has Been Updated        |  |

| 14.    | PUSH Description Correction                                        |  |

| 15.    | EFLAG Erroneous Statement Removed                                  |  |

| 16.    | Interrupt Handling Description Corrections                         |  |

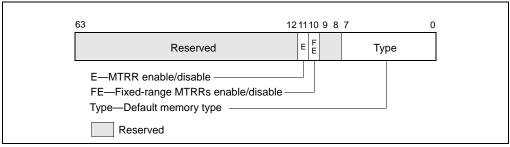

| 17.    | IA32_MTRR_DEF_TYPE MSR Definition Corrected                        |  |

| 18.    | Correction of Error in EFLAGS Treatment in Virtual-8086 Mode       |  |

| 19.    | Table B-3 Correction                                               |  |

| 20.    | Appendix E Edits                                                   |  |

| 21.    | MSR_PLATFORM_BRV Information Added                                 |  |

| 22.    | Support Pentium M Processor Section Added                          |  |

| 23.    | MSR Data for Pentium M Processor Has Been Updated                  |  |

| 24.    | Cache and TLB Descriptor Table Updated                             |  |

| 25.    | Brand String Table Updated                                         |  |

| 26.    | Pentium M Processor Sections Updated                               |  |

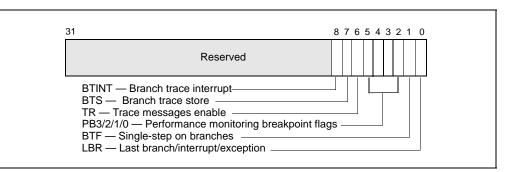

| 27.    | Name Change for IA32_DEBUGCTL                                      |  |

1.

### **Documentation Changes**

#### CPUID Sector Size, Cache Line Size Expressions Have Been Updated

*IA-32 Intel Architecture Software Developer's Manual, Volume 2A*, Chapter 3, CPUID-CPU Identification section, Table 3-13 has been corrected. A number of table cells have been updated to correct inconsistent expressions. An error in 78H has also been corrected. The affected table cells are shown below (not all text in the table has been reproduced).

\_\_\_\_\_

| 22H | 3rd-level cache: 512 KB, 4-way set associative, 64-byte line size, 2 lines per sector |

|-----|---------------------------------------------------------------------------------------|

| 23H | 3rd-level cache: 1 MB, 8-way set associative, 64-byte line size, 2 lines per sector   |

| 25H | 3rd-level cache: 2 MB, 8-way set associative, 64-byte line size, 2 lines per sector   |

| 29H | 3rd-level cache: 4 MB, 8-way set associative, 64-byte line size, 2 lines per sector   |

#### . . . . . . . . .

| 78H | 2nd-level cache: 1 MB, 4-way set associative, 64-byte line size                       |

|-----|---------------------------------------------------------------------------------------|

| 79H | 2nd-level cache: 128 KB, 8-way set associative, 64-byte line size, 2 lines per sector |

| 7AH | 2nd-level cache: 256 KB, 8-way set associative, 64-byte line size, 2 lines per sector |

| 7BH | 2nd-level cache: 512 KB, 8-way set associative, 64-byte line size, 2 lines per sector |

| 7CH | 2nd-level cache: 1 MB, 8-way set associative, 64-byte line size, 2 lines per sector   |

2.

I

#### LDDQU Description Text Has Been Added

*IA-32 Intel Architecture Software Developer's Manual, Volume 2B*, Chapter 3, LDDQU: Load Unaligned Integer 128 bits section: text has been added. The affected area is shown below. See the change bar for specific lines.

\_\_\_\_\_

... ... ...

#### **Implementation Notes**

- If the source is aligned to a 16-byte boundary, based on the implementation, the 16 bytes may be loaded more than once. For that reason, the usage of LDDQU should be avoided when using uncached or write-combining (WC) memory regions. For uncached or WC memory regions, keep using MOVDQU.

- This instruction is a replacement for MOVDQU (load) in situations where cache line splits significantly affect performance. It should not be used in situations where store-load forwarding is performance critical. If performance of store-load forwarding is critical to the application, use MOVDQA store-load pairs when data is 128-bit aligned or MOVDQU store-load pairs when data is 128-bit unaligned.

- If the memory address is not aligned on 16-byte boundary, some implementations may load up to 32 bytes and return 16 bytes in the destination. Some processor implementations may issue multiple loads to access the appropriate 16 bytes. Developers of multi-threaded or multi-processor software should be aware that on these processors the loads will be performed in a non-atomic way.

. . . . . . . . .

I

#### 3. ANDNPD/ANDNPS Exception Lists Corrected

*IA-32 Intel Architecture Software Developer's Manual, Volume 2B*, Chapter 3 - ANDNPD and ANDNPS sections: exception lists have been updated. The affected area for each section is shown below.

-----

#### ANDNPD—Bitwise Logical AND NOT of Packed Double-Precision Floating-Point Values

. . . . . . . . . .

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |  |

|-----------------|---------------------------------------------------------------------------------------|--|

|                 | If memory operand is not aligned on a 16-byte boundary, regardless of segment.        |  |

| #SS(0)          | For an illegal address in the SS segment.                                             |  |

| #PF(fault-code) | For a page fault.                                                                     |  |

| #NM             | If TS in CR0 is set.                                                                  |  |

| #UD             | If EM in CR0 is set.                                                                  |  |

|                 | If OSFXSR in CR4 is 0.                                                                |  |

|                 | If CPUID feature flag SSE2 is 0.                                                      |  |

#### **Real-Address Mode Exceptions**

| #GP(0) | If memory operand is not aligned on a 16-byte boundary, regardless of segment.       |

|--------|--------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside the effective address space from 0 to FFFFH. |

| #NM    | If TS in CR0 is set.                                                                 |

| #UD    | If EM in CR0 is set.                                                                 |

|        | If OSFXSR in CR4 is 0.                                                               |

|        | If CPUID feature flag SSE2 is 0.                                                     |

|        |                                                                                      |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode

#PF(fault-code) For a page fault.

•••• ••• •••

I

I

#### ANDNPS—Bitwise Logical AND NOT of Packed Single-Precision-Floating-Point Value

... ... ...

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |  |

|-----------------|---------------------------------------------------------------------------------------|--|

|                 | If memory operand is not aligned on a 16-byte boundary, regardless of segment.        |  |

| #SS(0)          | For an illegal address in the SS segment.                                             |  |

| #PF(fault-code) | For a page fault.                                                                     |  |

| #NM             | If TS in CR0 is set.                                                                  |  |

| #UD             | If EM in CR0 is set.                                                                  |  |

|                 | If OSFXSR in CR4 is 0.                                                                |  |

|                 | If CPUID feature flag SSE is 0.                                                       |  |

|                 |                                                                                       |  |

#### **Real-Address Mode Exceptions**

| #GP(0) | If memory operand is not aligned on a 16-byte boundary, regardless of segment.       |

|--------|--------------------------------------------------------------------------------------|

|        | If any part of the operand lies outside the effective address space from 0 to FFFFH. |

| #NM    | If TS in CR0 is set.                                                                 |

| #UD    | If EM in CR0 is set.                                                                 |

|        | If OSFXSR in CR4 is 0.                                                               |

|        | If CPUID feature flag SSE is 0.                                                      |

|        |                                                                                      |

#### Virtual-8086 Mode Exceptions

Same exceptions as in Real Address Mode #PF(fault-code) For a page fault.

#### 4. **PSADBW Instruction Description Section Corrected**

*IA-32 Intel Architecture Software Developer's Manual, Volume 2B*, Chapter 4, the PSADBW-Compute Sum of Absolute Differences section: an error has been corrected in the Description paragraph. The affected area is shown below (not all text in the section has been reproduced). The location of the change is indicated by the change bar.

\_\_\_\_\_

#### Description

Computes the absolute value of the difference of 8 unsigned byte integers from the source operand (**second operand**) and from the destination operand (**first operand**). These 8 differences are then summed to produce an unsigned word integer result that is stored in the destination operand. The source operand can be an MMX technology register or a 64-bit memory location or it can be an XMM register or a 128-bit memory location. The destination operand can be an MMX technology register or an XMM register. Figure 4-5 shows the operation of the PSADBW instruction when using 64-bit operands.

#### 5. Reference to Wrong Step Corrected

*IA-32 Intel Architecture Software Developer's Manual, Volume 3*, Chapter 7, section 7.5.4.1: contains an incorrect reference in a numbered list. This has been corrected. The affected step is shown below with a change bar to indicate the location of the error (not all steps have been included).

.....

15. Broadcasts an INIT-SIPI-SIPI IPI sequence to the APs to wake them up and initialize them:

```

MOV ESI, ICR_LOW; load address of ICR low dword into ESI

MOV EAX, 000C4500H; load ICR encoding for broadcast INIT IPI

; to all APs into EAX

MOV [ESI], EAX ; broadcast INIT IPI to all APs

; 10-millisecond delay loop

MOV EAX, 000C46XXH; load ICR encoding for broadcast SIPI IP

; to all APs into EAX, where xx is the

; vector computed in step 10.

MOV [ESI], EAX ; broadcast SIPI IPI to all APs

; 200-microsecond delay loop

MOV [ESI], EAX ; broadcast second SIPI IPI to all APs

; 200-microsecond delay loop

```

#### 6. APIC Chapter Updated

*IA-32 Intel Architecture Software Developer's Manual, Volume 3*, Chapter 8 has been updated. Information has been added to multiple sections; this information indicates the model-specific nature of some features. The new information is shown below (with enough of surrounding text to indicate the new text's location; not all text in the chapter is included). See the change bars to locate the updated lines.

\_\_\_\_\_

#### 8.4.6. Local APIC ID

At power up, system hardware assigns a unique APIC ID to each local APIC on the system bus (for Pentium 4 and Intel Xeon processors) or on the APIC bus (for P6 family and Pentium processors). The hardware assigned APIC ID is based on system topology and includes encoding for socket position and cluster information (see Figure 7-2).

In MP systems, the local APIC ID is also used as a processor ID by the BIOS and the operating system. However, the ability of software to modify the APIC ID is processor model specific. Because of this, operating system software should avoid writing to the local APIC ID register.

The processor receives the hardware assigned APIC ID by sampling pins A11# and A12# and pins BR0# through BR3# (for the Pentium 4, Intel Xeon, and P6 family processors) and pins BE0# through BE3# (for the Pentium processor). The APIC ID latched from these pins is stored in the APIC ID field of the local APIC ID register (see Figure 8-6), and is used as the initial APIC ID for the processor. It is also the value returned to the EBX register, when the CPUID instruction is executed with a source operand value of 1 in the EAX register.

| 31 24                                                                                                                             | 23       | 0 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------|---|

| APIC ID*                                                                                                                          | Reserved |   |

| Address: 0FEE0 0020H<br>Value after reset: 0000 0000H                                                                             |          |   |

| * For the P6 family and Pentium processors,<br>bits 28-31 are reserved. For Pentium 4<br>and Xeon processors, 21-31 are reserved. |          |   |

Figure 8-6. Local APIC ID Register

For the P6 family and Pentium processors, the local APIC ID field in the local APIC ID register is 4 bits, and encodings 0H through EH can be used to uniquely identify 15 different processors connected to the APIC bus. For the Pentium 4 and Intel Xeon processors, the xAPIC specification extends the local APIC ID field to 8 bits which can be used to identify up to 255 processors in the system.

Following power up or a hardware reset, software (typically the BIOS software) can modify the APIC ID field in the local APIC ID register for each processor in the system. When changing APIC IDs, software must insure that each APIC ID for each local APIC is unique throughout the system.

... ... omitted text....

#### 8.6. ISSUING INTERPROCESSOR INTERRUPTS

The following sections describe the local APIC facilities that are provided for issuing interprocessor interrupts (IPIs) from software. The primary local APIC facility for issuing IPIs is the interrupt command register (ICR). The ICR can be used for the following functions:

- To send an interrupt to another processor.

- To allow a processor to forward an interrupt that it received but did not service to another processor for servicing.

- To direct the processor to interrupt itself (perform a self interrupt).

- To deliver special IPIs, such as the start-up IPI (SIPI) message, to other processors.

Interrupts generated with this facility are delivered to the other processors in the system through the system bus (for Pentium 4 and Intel Xeon processors) or the APIC bus (for P6 family and Pentium processors). The ability for a processor to send a lowest priority IPI is model specific and should be avoided by BIOS and operating system software.

#### 8.6.1. Interrupt Command Register (ICR)

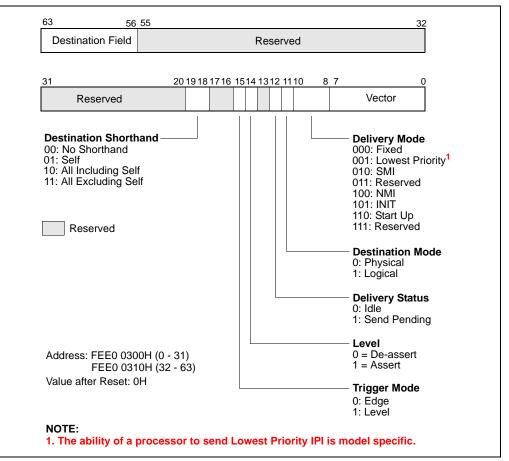

The interrupt command register (ICR) is a 64-bit local APIC register (see Figure 8-12) that allows software running on the processor to specify and send interprocessor interrupts (IPIs) to other IA-32 processors in the system.

To send an IPI, software must set up the ICR to indicate the type of IPI message to be sent and the destination processor or processors. (All fields of the ICR are read-write by software with the exception of the delivery status field, which is read-only.) The act of writing to the low doubleword of the ICR causes the IPI to be sent.

Figure 8-12. Interrupt Command Register (ICR)

The ICR consists of the following fields.

| Vector        | The vector number of the interrupt being sent.                                               |                                                                                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delivery Mode | Specifies the type of IPI to be sent. This field is also know as the IPI message type field. |                                                                                                                                                                                                                                                                                                                                            |

|               | 000 (Fixed)                                                                                  | Delivers the interrupt specified in the vector field to the target processor or processors.                                                                                                                                                                                                                                                |

|               | 001 (Lowest Pri                                                                              | Same as fixed mode, except that the interrupt is deliv-<br>ered to the processor executing at the lowest priority<br>among the set of processors specified in the destina-<br>tion field. The ability for a processor to send a low-<br>est priority IPI is model specific and should be<br>avoided by BIOS and operating system software. |

|               | 010 (SMI)                                                                                    | Delivers an SMI interrupt to the target processor or<br>processors. The vector field must be programmed to<br>00H for future compatibility.                                                                                                                                                                                                |

|                         | 011 (Reserved)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 100 (NMI)          | Delivers an NMI interrupt to the target processor or processors. The vector information is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                         | 101 (INIT)         | Delivers an INIT request to the target processor or pro-<br>cessors, which causes them to perform an INIT. As a<br>result of this IPI message, all the target processors per-<br>form an INIT. The vector field must be programmed to<br>00H for future compatibility.                                                                                                                                                                                                                                                                                                                                    |

|                         | 101 (INIT Level    | De-assert)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         |                    | (Not supported in the Pentium 4 and Intel Xeon pro-<br>cessors.) Sends a synchronization message to all the<br>local APICs in the system to set their arbitration IDs<br>(stored in their Arb ID registers) to the values of their<br>APIC IDs (see Section 8.7., "System and APIC Bus<br>Arbitration"). For this delivery mode, the level flag<br>must be set to 0 and trigger mode flag to 1. This IPI is<br>sent to all processors, regardless of the value in the<br>destination field or the destination shorthand field;<br>however, software should specify the "all including<br>self" shorthand. |

|                         | 110 (Start-Up)     | Sends a special "start-up" IPI (called a SIPI) to the tar-<br>get processor or processors. The vector typically<br>points to a start-up routine that is part of the BIOS<br>boot-strap code (see Section 7.5., "Multiple-Processor<br>(MP) Initialization"). Note that IPIs sent with this de-<br>livery mode are not automatically retried if the source<br>APIC is unable to deliver it. It is up to the software to<br>determine if the SIPI was not successfully delivered<br>and to reissue the SIPI if necessary.                                                                                   |

| Destination Mode        |                    | vsical (0) or logical (1) destination mode (see Section <i>ng IPI Destination</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Delivery Status (Read O |                    | delivery status, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                         | 0 (Idle)           | There is currently no IPI activity for this local APIC, or the previous IPI sent from this local APIC was de-<br>livered and accepted by the target processor or proces-<br>sors.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | 1 (Send Pending    | z)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | -                  | Indicates that the last IPI sent from this local APIC has<br>not yet been accepted by the target processor or pro-<br>cessors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Level                   | all other delivery | el de-assert delivery mode this flag must be set to 0; for<br>modes it must be set to 1. (This flag has no meaning in<br>tel Xeon processors, and will always be issued as a 1.)                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Trigger Mode            | mode: edge (0) o   | er mode when using the INIT level de-assert delivery<br>or level (1). It is ignored for all other delivery modes.<br>meaning in Pentium 4 and Intel Xeon processors, and<br>sued as a 0.)                                                                                                                                                                                                                                                                                                                                                                                                                 |

### int<sub>el</sub>.

**Destination Shorthand** Indicates whether a shorthand notation is used to specify the destination of the interrupt and, if so, which shorthand is used. Destination shorthands are used in place of the 8-bit destination field, and can be sent by software using a single write to the low doubleword of the ICR. Shorthands are defined for the following cases: software self interrupt, IPIs to all processors in the system including the sender, IPIs to all processors in the system excluding the sender.

#### 00: (No Shorthand)

The destination is specified in the destination field.

**01:** (Self) The issuing APIC is the one and only destination of the IPI. This destination shorthand allows software to interrupt the processor on which it is executing. An APIC implementation is free to deliver the self-interrupt message internally or to issue the message to the bus and "snoop" it as with any other IPI message.

#### 10: (All Including Self)

The IPI is sent to all processors in the system including the processor sending the IPI. The APIC will broadcast an IPI message with the destination field set to FH for Pentium and P6 family processors and to FFH for Pentium 4 and Intel Xeon processors.

#### 11: (All Excluding Self)

The IPI is sent to all processors in a system with the exception of the processor sending the IPI. The APIC broadcasts a message with the physical destination mode and destination field set to 0xFH for Pentium and P6 family processors and to 0xFFH for Pentium 4 and Intel Xeon processors. Support for this destination shorthand in conjunction with the lowest-priority delivery mode is model specific. For Pentium 4 and Intel Xeon processors, when this shorthand is used together with lowest priority delivery mode, the IPI may be redirected back to the issuing processor.

DestinationSpecifies the target processor or processors. This field is only used when<br/>the destination shorthand field is set to 00B. If the destination mode is set<br/>to physical, then bits 56 through 59 contain the APIC ID of the target<br/>processor for Pentium and P6 family processors and bits 56 through 63<br/>contain the APIC ID of the target processor the for Pentium 4 and Intel<br/>Xeon processors. If the destination mode is set to logical, the interpreta-<br/>tion of the 8-bit destination field depends on the settings of the DFR and<br/>LDR registers of the local APICs in all the processors in the system (see<br/>Section 8.6.2., Determining IPI Destination).

Note that not all the combinations of options for the ICR are valid. Table 8-2 shows the valid combinations for the fields in the ICR for the Pentium 4 and Intel Xeon processors; Table 8-3 shows the valid combinations for the fields in the ICR for the P6 family processors. I

| Destination<br>Shorthand | Valid/<br>Invalid    | Trigger<br>Mode | Delivery Mode                                                       | Destination Mode    |

|--------------------------|----------------------|-----------------|---------------------------------------------------------------------|---------------------|

| No Shorthand             | Valid                | Edge            | All Modes <sup>1</sup>                                              | Physical or Logical |

| No Shorthand             | Invalid <sup>2</sup> | Level           | All Modes                                                           | Physical or Logical |

| Self                     | Valid                | Edge            | Fixed                                                               | X <sup>3</sup>      |

| Self                     | Invalid <sup>2</sup> | Level           | Fixed                                                               | х                   |

| Self                     | Invalid              | Х               | Lowest Priority, NMI, INIT, SMI, Start-Up                           | х                   |

| All Including Self       | Valid                | Edge            | Fixed                                                               | х                   |

| All Including Self       | Invalid <sup>2</sup> | Level           | Fixed                                                               | х                   |

| All Including Self       | Invalid              | Х               | Lowest Priority, NMI, INIT, SMI, Start-Up                           | х                   |

| All Excluding Self       | Valid                | Edge            | Fixed, Lowest Priority <sup>1,4</sup> , NMI, INIT,<br>SMI, Start-Up | Х                   |

| All Excluding Self       | Invalid <sup>2</sup> | Level           | Flxed, Lowest Priority <sup>4</sup> , NMI, INIT, SMI, Start-Up      | Х                   |

#### Table 8-2. Valid Combinations for the Pentium 4 and Intel Xeon Processors' Local xAPIC Interrupt Command Register

#### NOTES:

The ability of a processor to send a lowest priority IPI is model specific.

For these interrupts, if the trigger mode bit is 1 (Level), the local xAPIC will override the bit setting and issue the interrupt as an edge triggered interrupt.

X—don't care.

When using the "lowest priority" delivery mode and the "all excluding self" destination, the IPI can be redirected back to the issuing APIC, which is essentially the same as the "all including self" destination mode.

| Table 8-3. Valid Combinations for the P6 Family Processors Local APIC Interrupt |

|---------------------------------------------------------------------------------|

| Command Register                                                                |

| Destination<br>Shorthand | Valid/<br>Invalid    | Trigger<br>Mode | Delivery Mode                                | Destination Mode    |

|--------------------------|----------------------|-----------------|----------------------------------------------|---------------------|

| No Shorthand             | Valid                | Edge            | All Modes <sup>1</sup>                       | Physical or Logical |

| No Shorthand             | Valid <sup>2</sup>   | Level           | Fixed, Lowest Priority <sup>1</sup> , NMI    | Physical or Logical |

| No Shorthand             | Valid <sup>3</sup>   | Level           | INIT                                         | Physical or Logical |

| Self                     | Valid                | Edge            | Fixed                                        | X <sup>4</sup>      |

| Self                     | 1                    | Level           | Fixed                                        | Х                   |

| Self                     | Invalid <sup>5</sup> | Х               | Lowest Priority, NMI, INIT, SMI,<br>Start-Up | Х                   |

| All including Self       | Valid                | Edge            | Fixed                                        | Х                   |

| All including Self       | Valid <sup>2</sup>   | Level           | Fixed                                        | Х                   |

| All including Self       | Invalid <sup>5</sup> | Х               | Lowest Priority, NMI, INIT, SMI,<br>Start-Up | Х                   |

| All excluding Self       | Valid                | Edge            | All Modes <sup>1</sup>                       | Х                   |

| All excluding Self       | Valid <sup>2</sup>   | Level           | Fixed, Lowest Priority <sup>1</sup> , NMI    | Х                   |

| All excluding Self       | Invalid <sup>5</sup> | Level           | SMI, Start-Up                                | Х                   |

| All excluding Self       | Valid <sup>3</sup>   | Level           | INIT                                         | Х                   |

| Х                        | Invalid <sup>5</sup> | Level           | SMI, Start-Up                                | Х                   |

#### NOTES:

1. The ability of a processor to send a lowest priority IPI is model specific.

2. Treated as edge triggered if level bit is set to 1, otherwise ignored.

- 3. Treated as edge triggered when Level bit is set to 1; treated as "INIT Level Deassert" message when level bit is set to 0 (deassert). Only INIT level deassert messages are allowed to have the level bit set to 0. For all other messages the level bit must be set to 1.

- 4. X—Don't care.

- 5. The behavior of the APIC is undefined.

#### 8.6.2. Determining IPI Destination

The destination of an IPI can be one, all, or a subset (group) of the processors on the system bus. The sender of the IPI specifies the destination of an IPI with the following APIC registers and fields within the registers:

- The ICR register—The following fields in the ICR register are used to specify the destination of an IPI:

- Destination Mode-selects one of two destination modes (physical or logical).

- Destination field—In physical destination mode, used to specify the APIC ID of the destination processor; in logical destination mode, used to specify a message destination address (MDA) that can be used to select specific processors in clusters.

- Destination Shorthand—A quick method of specifying all processors, all excluding self, or self as the destination.

- Delivery mode, Lowest Priority—Architecturally specifies that a lowest-priority arbitration mechanism be used to select a destination processor from a specified group of processors. The ability of a processor to send a lowest priority IPI is model specific and should be avoided by BIOS and operating system software.

- Local destination register (LDR)—Used in conjunction with the logical destination mode and MDAs to select the destination processors.

- Destination format register (DFR)—Used in conjunction with the logical destination mode and MDAs to select the destination processors.

How the ICR, LDR, and DFR are used to select an IPI destination depends on the destination mode used: physical, logical, broadcast/self, or lowest-priority delivery mode. These destination modes are described in the following sections.

#### 8.6.2.1. PHYSICAL DESTINATION MODE

In physical destination mode, the destination processor is specified by its local APIC ID (see Section 8.4.6., *Local APIC ID*). For Pentium 4 and Intel Xeon processors, either a single destination (local APIC IDs 00H through FEH) or a broadcast to all APICs (the APIC ID is FFH) may be specified in physical destination mode.

A broadcast IPI (bits 28-31 of the MDA are 1's) or I/O subsystem initiated interrupt with lowest priority delivery mode is not supported in physical destination mode and must not be configured by software. Also, for any non-broadcast IPI or I/O subsystem initiated interrupt with lowest priority delivery mode, software must ensure that APICs defined in the interrupt address are present and enabled to receive interrupts.

For the P6 family and Pentium processors, a single destination is specified in physical destination mode with a local APIC ID of 0H through 0EH, allowing up to 15 local APICs to be addressed on the APIC bus. A broadcast to all local APICs is specified with 0FH.

#### NOTE

The actual number of local APICs that can be addressed on the system bus may be restricted by hardware.

#### 8.6.2.2. LOGICAL DESTINATION MODE

In logical destination mode, IPI destination is specified using an 8-bit message destination address (MDA), which is entered in the destination field of the ICR. Upon receiving an IPI message that was sent using logical destination mode, a local APIC compares the MDA in the message with the values in its LDR and DFR to determine if it should accept and handle the IPI. For both configurations of logical destination mode, when combined with lowest priority delivery mode, software is responsible for ensuring that all of the local APICs included in or addressed by the IPI or I/O subsystem interrupt are present and enabled to receive the interrupt.

Figure 13 shows the layout of the logical destination register (LDR). The 8-bit logical APIC ID field in this register is used to create an identifier that can be compared with the MDA.

#### NOTE

The logical APIC ID should not be confused with the local APIC ID that is contained in the local APIC ID register.

| 31 | 24                                     |          | 0 |

|----|----------------------------------------|----------|---|

| Lo | gical APIC ID                          | Reserved |   |

|    | ess: 0FEE0 00D0<br>e after reset: 0000 | )H       |   |

Figure 8-13. Logical Destination Register (LDR)

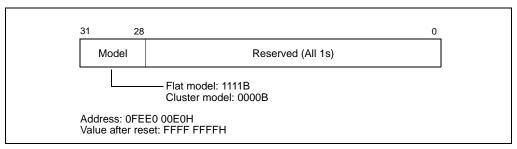

Figure 14 shows the layout of the destination format register (DFR). The 4-bit model field in this register selects one of two models (flat or cluster) that can be used to interpret the MDA when using logical destination mode.

Figure 8-14. Destination Format Register (DFR)

The interpretation of MDA for the two models is described in the following paragraphs.

**Flat Model.** This model is selected by programming DFR bits 28 through 31 to 1111. Here, a unique logical APIC ID can be established for up to 8 local APICs by setting a different bit in the logical APIC ID field of the LDR for each local APIC. An group of local APICs can then be selected by setting one or more bits in the MDA.

Each local APIC performs a bit-wise AND of the MDA and its logical APIC ID. If a true condition is detected, the local APIC accepts the IPI message. A broadcast to all APICs is achieved by setting the MDA to all 1s.

**Cluster Model**. This model is selected by programming DFR bits 28 through 31 to 0000. This model supports two basic destination schemes: flat cluster and hierarchical cluster.

The flat cluster destination model is only supported for P6 family and Pentium processors. Using this model, all APICs are assumed to be connected through the APIC bus. Bits 28 through 31 of the MDA contains the encoded address of the destination cluster, and bits 24 through 27 identify up to four local APICs within the cluster (each bit is assigned to one local APIC in the cluster, as in the flat connection model). To identify one or more local APICs, bits 28 through 31 of the MDA are compared with bits 28 through 31 of the LDR to determine if a local APIC is part of the cluster. Bits 24 through 27 of the MDA are compared with Bits 24 through 27 of the LDR to identify a local APICs within the cluster.

Sets of processors within a cluster can be specified by writing the target cluster address in bits 28 through 31 of the MDA and setting selected bits in bits 24 through 27 of the MDA, corresponding to the chosen members of the cluster. In this mode, 15 clusters (with cluster addresses of 0 through 14) each having 4 local APICs can be specified in the message. For the P6 and Pentium processor's local APICs, however, the APIC arbitration ID supports only 15 APIC agents, and hence the total number of processors and their local APICs supported in this mode is limited to 15. Broadcast to all local APICs is achieved by setting all destination bits to one. This guarantees a match on all clusters, and selects all APICs in each cluster. A broadcast IPI or I/O subsystem broadcast interrupt with lowest priority delivery mode is not supported in cluster mode and must not be configured by software.

The hierarchical cluster destination model can be used with Pentium 4, Intel Xeon, P6 family, or Pentium processors. With this model, a hierarchical network can be created by connecting different flat clusters via independent system or APIC buses. This scheme requires a cluster manager within each cluster, which is responsible for handling message passing between system or APIC buses. One cluster contains up to 4 agents. Thus 15 cluster managers, each with 4 agents, can form a network of up to 60 APIC agents. Note that hierarchical APIC networks requires a special cluster manager device, which is not part of the local or the I/O APIC units.

... ... omitted text....

#### 8.11.1. Message Address Register Format

The format of the Message Address Register (lower 32-bits) is shown in Figure .

| 0FEEH Destination ID Reserved RH DM XX |

|----------------------------------------|

Figure 8-23. Layout of the MSI Message Address Register

Fields in the Message Address Register are as follows:

- 1. Bits 31-20: These bits contain a fixed value for interrupt messages (0FEEH). This value locates interrupts at the 1MB area with a base address of 4G 18M. All accesses to this region are directed as interrupt messages. Care must to be taken to ensure that no other device claims the region as I/O space.

- 2. Destination ID: This field contains an 8-bit destination ID. It identifies the message's target processor(s). The destination ID corresponds to bits 63:56 of the I/O APIC Redirection Table Entry if the IOAPIC is used to dispatch the interrupt to the processor(s).

- 3. Redirection Hint Indication (RH): This bit indicates whether the message should be directed to the processor with the lowest interrupt priority among processors that can receive the interrupt.

- When RH is 0, the interrupt is directed to the processor listed in the Destination ID field.

- When RH is 1 and the physical destination mode is used, the Destination ID field must not be set to 0xFF; it must point to a processor that is present and enabled to receive the interrupt.

- When RH is 1 and the logical destination mode is active in a system using a flat addressing model, the Destination ID field must be set so that bits set to 1 identify processors that are present and enabled to receive the interrupt.

- If RH is set to 1 and the logical destination mode is active in a system using cluster addressing model, then Destination ID field must not be set to 0xFF; the processors identified with this field must be present and enabled to receive the interrupt.

Destination Mode (DM): This bit indicates whether the Destination ID field should be interpreted as logical or physical APIC ID for delivery of the lowest priority interrupt. If RH is 1 and DM is 0, the Destination ID field is in physical destination mode and only the processor in the system that has the matching APIC ID is considered for delivery of that interrupt (this means no re-direction). If RH is 1 and DM is 1, the Destination ID Field is interpreted as in logical destination mode and the redirection is limited to only those processors that are part of the logical group of processors based on the processor's logical APIC ID and the Destination ID field in the message. The logical group of processors consists of those identified by matching the 8-bit Destination ID with the logical destination identified by the Destination Format Register and the Logical Destination Register in each local APIC. The details are similar to those described in Section 8.6.2., *Determining IPI Destination*. If RH is 0, then the DM bit is ignored and the message is sent ahead independent of whether the physical or logical destination mode is used.

7.

I

#### IA32\_MC1\_MISC, IA32\_MC2\_MISC and IA32\_MC2\_ADDR Listings Corrected

For Table B-5, *IA-32 Intel Architecture Software Developer's Manual, Volume 3*; a footnote has been added to clarify when and why specific MSRs may or may not be present. The affected cells in the table are shown below (not all cells in the table have been included).

-----

| Registe | er Address |                            |             |                                         |

|---------|------------|----------------------------|-------------|-----------------------------------------|

| C C     |            | Architectural Name         | Former Name | IA-32 Processor<br>Family Introduced In |

|         |            |                            |             |                                         |

| 407H    | 1031       | IA32_MC1_MISC1             | MC1_MISC    | P6 Family Processors                    |

| 408H    | 1032       | IA32_MC2_CTL               | MC2_CTL     | P6 Family Processors                    |

| 409H    | 1033       | IA32_MC2_STATUS            | MC2_STATUS  | P6 Family Processors                    |

| 40AH    | 1034       | IA32_MC2_ADDR <sup>a</sup> | MC2_ADDR    | P6 Family Processors                    |

| 40BH    | 1035       | IA32_MC2_MISC1             | MC2_MISC    | P6 Family Processors                    |

| 40CH    | 1036       | IA32_MC3_CTL               | MC3_CTL     | P6 Family Processors                    |

| 40DH    | 1037       | IA32_MC3_STATUS            | MC3_STATUS  | P6 Family Processors                    |

| 40EH    | 1038       | IA32_MC3_ADDR              | MC3_ADDR    | P6 Family Processors                    |

| 40FH    | 1039       | IA32_MC3_MISC              | MC3_MISC    | P6 Family Processors                    |

| 600H    | 1536       | IA32_DS_AREA               |             | Pentium 4 Processor                     |

| Table B-5  | IA-32 Architectura  | I MSRs |

|------------|---------------------|--------|

| Table D-J. | IA-JZ AILIIILELLUIA | INIONS |

a. These MSRs may or may not be present; this depends on flag settings in IA32\_MC*i*\_STATUS. See Section 14.3.2.3. and Section 14.3.2.4. for more information.

#### 8. Ambiguity Correction

For Sections 4.11.3 and 4.12, IA-32 Intel Architecture Software Developer's Manual, Volume 3; the wording has been corrected to be more precise. Updated text and table cells are marked by change bars.

\_\_\_\_\_

#### 4.11.3. Page Type

The page-level protection mechanism recognizes two page types:

- Read-only access (R/W flag is 0).

- Read/write access (R/W flag is 1).

When the processor is in supervisor mode and the WP flag in register CR0 is clear (its state following reset initialization), all pages are both readable and writable (write-protection is ignored). When the processor is in user mode, it can write only to user-mode pages that are read/write accessible. User-mode pages which are read/write or read-only are readable; supervisor-mode pages are neither readable nor writable from user mode. A page-fault exception is generated on any attempt to violate the protection rules.

The P6 family, Pentium, and Intel486 processors allow user-mode pages to be write-protected against supervisor-mode access. Setting the WP flag in register CR0 to 1 enables supervisor-mode sensitivity to user-mode, write protected pages. Supervisor pages which are read-only are not writeable from any privilege level, regardless of WP setting. This supervisor write-protect feature is useful for implementing a "copy-on-write" strategy used by some operating systems, such as UNIX\*, for task creation (also called forking or spawning). When a new task is created, it is possible to copy the entire address space of the parent task. This gives the child task a complete, duplicate set of the parent's segments and pages. An alternative copy-on-write strategy saves memory space and time by mapping the child's segments and pages to the same segments and pages used by the parent task. A private copy of a page gets created only when one of the tasks writes to the page. By using the WP flag and marking the shared pages as read-only, the supervisor can detect an attempt to write to a user-level page, and can copy the page at that time.

#### 4.11.4. Combining Protection of Both Levels of Page Tables

For any one page, the protection attributes of its page-directory entry (first-level page table) may differ from those of its page-table entry (second-level page table). The processor checks the protection for a page in both its page-directory and the page-table entries. Table 4-4 shows the protection provided by the possible combinations of protection attributes when the WP flag is clear.

#### 4.11.5. Overrides to Page Protection

The following types of memory accesses are checked as if they are privilege-level 0 accesses, regardless of the CPL at which the processor is currently operating:

- Access to segment descriptors in the GDT, LDT, or IDT.

- Access to an inner-privilege-level stack during an inter-privilege-level call or a call to in exception or interrupt handler, when a change of privilege level occurs.

I

#### 4.12. COMBINING PAGE AND SEGMENT PROTECTION

When paging is enabled, the processor evaluates segment protection first, then evaluates page protection. If the processor detects a protection violation at either the segment level or the page level, the memory access is not carried out and an exception is generated. If an exception is generated by segmentation, no paging exception is generated.

Page-level protections cannot be used to override segment-level protection. For example, a code segment is by definition not writable. If a code segment is paged, setting the R/W flag for the pages to read-write does not make the pages writable. Attempts to write into the pages will be blocked by segment-level protection checks.

Page-level protection can be used to enhance segment-level protection. For example, if a large readwrite data segment is paged, the page-protection mechanism can be used to write-protect individual pages.

| Page-Directory Entry |             | Page-Table Entry |             | Combined Effect |             |

|----------------------|-------------|------------------|-------------|-----------------|-------------|

| Privilege            | Access Type | Privilege        | Access Type | Privilege       | Access Type |

| User                 | Read-Only   | User             | Read-Only   | User            | Read-Only   |

| User                 | Read-Only   | User             | Read-Write  | User            | Read-Only   |

| User                 | Read-Write  | User             | Read-Only   | User            | Read-Only   |

| User                 | Read-Write  | User             | Read-Write  | User            | Read/Write  |

| User                 | Read-Only   | Supervisor       | Read-Only   | Supervisor      | Read-Only   |

| User                 | Read-Only   | Supervisor       | Read-Write  | Supervisor      | Read/Write* |

| User                 | Read-Write  | Supervisor       | Read-Only   | Supervisor      | Read/Write* |

| User                 | Read-Write  | Supervisor       | Read-Write  | Supervisor      | Read/Write  |

| Supervisor           | Read-Only   | User             | Read-Only   | Supervisor      | Read-Only   |

| Supervisor           | Read-Only   | User             | Read-Write  | Supervisor      | Read/Write* |

| Supervisor           | Read-Write  | User             | Read-Only   | Supervisor      | Read/Write* |

| Supervisor           | Read-Write  | User             | Read-Write  | Supervisor      | Read/Write  |

| Supervisor           | Read-Only   | Supervisor       | Read-Only   | Supervisor      | Read-Only   |

| Supervisor           | Read-Only   | Supervisor       | Read-Write  | Supervisor      | Read/Write* |

| Supervisor           | Read-Write  | Supervisor       | Read-Only   | Supervisor      | Read/Write* |

| Supervisor           | Read-Write  | Supervisor       | Read-Write  | Supervisor      | Read/Write  |

Table 4-4. Combined Page-Directory and Page-Table Protection

#### NOTE:

\* If the WP flag of CR0 is set, the access type is determined by the R/W flags of the page-directory and pagetable entries.

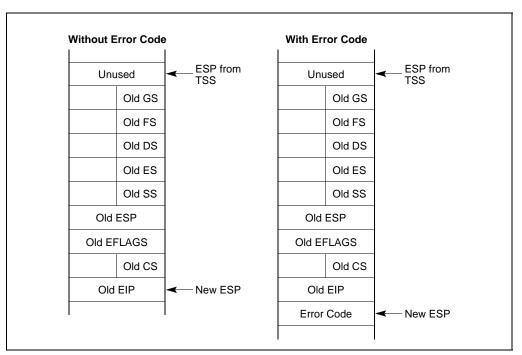

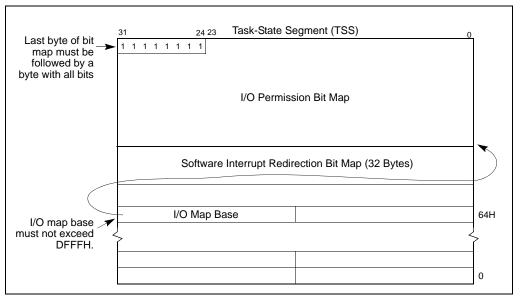

#### 9. Listing of Invalid TSS Conditions Has Been Updated

For Table 5-6, IA-32 Intel Architecture Software Developer's Manual, Volume 3; Additional invalid conditions have been listed. The updated table is as follows:

\_\_\_\_\_

#### Interrupt 10—Invalid TSS Exception (#TS)

#### **Exception Class** Fault.

#### Description

Indicates that there was an error related to a TSS. Such an error might be detected during a task switch or during the execution of instructions that use information from a TSS. Table 5-6 shows the conditions that cause an invalid TSS exception to be generated.

| Error Code Index             | Invalid Condition                                                                            |

|------------------------------|----------------------------------------------------------------------------------------------|

| TSS segment selector index   | The TSS segment limit is less than 67H for 32-bit TSS or less than 2CH for 16-bit TSS.       |

| TSS segment selector index   | During an IRET task switch, the TI flag in the TSS segment selector indicates the LDT.       |

| TSS segment selector index   | During an IRET task switch, the TSS segment selector exceeds descriptor table limit.         |

| TSS segment selector index   | During an IRET task switch, the busy flag in the TSS descriptor indicates an inactive task.  |

| TSS segment selector index   | During an IRET task switch, an attempt to load the backlink limit faults.                    |

| TSS segment selector index   | During an IRET task switch, the backlink is a NULL selector.                                 |

| TSS segment selector index   | During an IRET task switch, the backlink points to a descriptor which is not a busy TSS.     |

| TSS segment selector index   | The new TSS descriptor is beyond the GDT limit.                                              |

| TSS segment selector index   | The new TSS descriptor is not writeable.                                                     |

| TSS segment selector index   | Stores to the old TSS encounter a fault condition.                                           |

| TSS segment selector index   | The old TSS descriptor is not writeable for a jump or IRET task switch.                      |

| TSS segment selector index   | The new TSS backlink is not writeable for a call or exception task switch.                   |

| TSS segment selector index   | The new TSS selector is null on an attempt to lock the new TSS.                              |

| TSS segment selector index   | The new TSS selector has the TI bit set on an attempt to lock the new TSS.                   |

| TSS segment selector index   | The new TSS descriptor is not an available TSS descriptor on an attempt to lock the new TSS. |

| LDT segment selector index   | LDT or LDT not present.                                                                      |

| Stack segment selector index | The stack segment selector exceeds descriptor table limit.                                   |

| Stack segment selector index | The stack segment selector is NULL.                                                          |

| Stack segment selector index | The stack segment descriptor is a non-data segment.                                          |

| Stack segment selector index | The stack segment is not writable.                                                           |

| Stack segment selector index | The stack segment DPL != CPL.                                                                |

| Stack segment selector index | The stack segment selector RPL != CPL.                                                       |

#### Table 5-6. Invalid TSS Conditions

| Error Code Index            | Invalid Condition                                                            |

|-----------------------------|------------------------------------------------------------------------------|

| Code segment selector index | The code segment selector exceeds descriptor table limit.                    |

| Code segment selector index | The code segment selector is NULL.                                           |

| Code segment selector index | The code segment descriptor is not a code segment type.                      |

| Code segment selector index | The nonconforming code segment DPL != CPL.                                   |

| Code segment selector index | The conforming code segment DPL is greater than CPL.                         |

| Data segment selector index | The data segment selector exceeds the descriptor table limit.                |

| Data segment selector index | The data segment descriptor is not a readable code or data type.             |

| Data segment selector index | The data segment descriptor is a nonconforming code type and RPL > DPL.      |

| Data segment selector index | The data segment descriptor is a nonconforming code type and CPL > DPL.      |

| TSS segment selector index  | The TSS segment selector is NULL for LTR.                                    |

| TSS segment selector index  | The TSS segment selector has the TI bit set for LTR.                         |

| TSS segment selector index  | The TSS segment descriptor/upper descriptor is beyond the GDT segment limit. |

| TSS segment selector index  | The TSS segment descriptor is not an available TSS type.                     |

Table 5-6. Invalid TSS Conditions (Continued)

#### 10. Description Section Corrected

For the OUTS/OUTSB/OUTSW/OUTSD—Output String to Port section, *Chapter 4, IA-32 Intel Architecture Software Developer's Manual, Volume 2B;* text in the Description sub-section has been updated to correct an erroneous reference. The affected area is shown below in context; affected lines are marked by a change bar.

\_\_\_\_\_

#### OUTS/OUTSB/OUTSW/OUTSD—Output String to Port

| Opcode | Instruction  | Description                                                                                 |

|--------|--------------|---------------------------------------------------------------------------------------------|

| 6E     | OUTS DX, m8  | Output byte from memory location specified in DS:(E)SI to<br>I/O port specified in DX       |

| 6F     | OUTS DX, m16 | Output word from memory location specified in DS:(E)SI to I/O port specified in DX          |

| 6F     | OUTS DX, m32 | Output doubleword from memory location specified in<br>DS:(E)SI to I/O port specified in DX |

| 6E     | OUTSB        | Output byte from memory location specified in DS:(E)SI to<br>I/O port specified in DX       |

| 6F     | OUTSW        | Output word from memory location specified in DS:(E)SI to I/O port specified in DX          |

| 6F     | OUTSD        | Output doubleword from memory location specified in<br>DS:(E)SI to I/O port specified in DX |

#### Description

Copies data from the source operand (second operand) to the I/O port specified with the destination operand (first operand). The source operand is a memory location, the address of which is read from either the DS:ESI or the DS:SI registers (depending on the address-size attribute of the instruction, 32 or 16, respectively). (The DS segment may be overridden with a segment override prefix.) The destination operand is an I/O port address (from 0 to 65,535) that is read from the DX register. The size of the I/O port being accessed (that is, the size of the source and destination operands) is determined by the opcode for an 8-bit I/O port or by the operand-size attribute of the instruction for a 16-or 32-bit I/O port.

#### 11. IA-32e Updates for LLDT, LMSW, LTR, SLDT, SMSW, STR

For LLDT, LMSW, LTR, SLDT, SMSW, STR; Chapters 2 & 3 in the *Intel® Extended Memory* 64 *Technology Software Developer's Guide, Volumes 1 & 2;* IA-32e Mode Operation sections have been updated. Change bars mark the corrections.

\_\_\_\_\_

#### LLDT—Load Local Descriptor Table Register

| Opcode   | Instruction | 64-Bit<br>Mode | Compat/Leg Mode | Description                              |

|----------|-------------|----------------|-----------------|------------------------------------------|

| 0F 00 /2 | LLDT r/m16  | Valid          | Valid           | Load segment selector r/m16<br>into LDTR |

#### **Flags Affected**

None.

#### IA-32e Mode Operation

Operand size fixed at 16 bits.

References 64-bit mode descriptor to load 64-bit base.

\*\*\* \*\*\* \*\*\*

#### LMSW—Load Machine Status Word

| Opcode   | Instruction | 64-Bit Mode | Compat/Leg<br>Mode | Description                               |

|----------|-------------|-------------|--------------------|-------------------------------------------|

| 0F 01 /6 | LMSW r/m16  | Valid       | Valid              | Loads r/m16 in machine status word of CR0 |

#### **Flags Affected**

None.

#### IA-32e Mode Operation

Same as legacy mode.

Operand size fixed at 16 bits.

#### LTR—Load Task Register

| Opcode   | Instruction | 64-Bit Mode | Compat/Leg<br>Mode | Description                   |

|----------|-------------|-------------|--------------------|-------------------------------|

| 0F 00 /3 | LTR r/m16   | Valid       | Valid              | Load r/m16 into task register |

#### **Flags Affected**

None.

#### **IA-32e Mode Operation**

Operand size fixed at 16 bits.

References 64-bit mode descriptor to load 64-bit base.

\*\*\* \*\*\* \*\*\*

#### SLDT—Store Local Descriptor Table Register

| Opcode   | Instruction | 64-Bit<br>Mode | Compat/Leg<br>Mode | Description                                    |

|----------|-------------|----------------|--------------------|------------------------------------------------|

| 0F 00 /0 | SLDT r/m16  | Valid          | Valid              | Stores segment selector from LDTR in r/<br>m16 |

#### **Flags Affected**

None.

#### **IA-32e Mode Operation**

The behavior of the SLDT instruction is defined by the following examples.

- SLDT r16 operands size 16, store 16-bit selector in r16

- SLDT r32 operands size 32, zero-extend 16-bit selector and store in r32

- SLDT r64 operands size 64, zero-extend 16-bit selector and store in r64

- SLDT m16 operands size 16, store 16-bit selector in m16

- SLDT m16 operands size 32, store 16-bit selector in m16 (not m32)

- SLDT m16 operands size 64, store 16-bit selector in m16 (not m64)

#### SMSW—Store Machine Status Word

| Opcode   | Instruction | 64-Bit<br>Mode | Compat/Leg<br>Mode | Description                        |

|----------|-------------|----------------|--------------------|------------------------------------|

| 0F 01 /4 | SMSW r/m16  | Valid          | Valid              | Store machine status word to r/m16 |

#### **Flags Affected**

None.

#### IA-32e Mode Operation

The behavior of the SMSW instruction is defined by the following examples.

- SMSW r16 operands size 16, store CR0[15:0] in r16

- SMSW r32 operands size 32, zero-extend CR0[31:0], and store in r32

- SMSW r64 operands size 64, zero-extend CR0[63:0], and store in r64

- SMSW m16 operands size 16, store CR0[15:0] in m16

- SMSW m16 operands size 32, store CR0[15:0] in m16 (not m32)

- SMSW m16 operands size 64, store CR0[15:0] in m16 (not m64)

\*\*\* \*\*\* \*\*\*

#### STR—Store Task Register

| Opcode   | Instruction | 64-Bit<br>Mode | Compat/Leg<br>Mode | Description                                 |

|----------|-------------|----------------|--------------------|---------------------------------------------|

| 0F 00 /1 | STR r/m16   | Valid          | Valid              | Stores segment selector from TR in<br>r/m16 |

#### **Flags Affected**

None.

#### **IA-32e Mode Operation**

Same as legacy mode.

Memory operand fixed at 16 bits.

Zero extend 2 byte TR selector to 64 bits and store to register operand.

#### 12. 66H Prefix in 64-bit Mode Information Added

In Chapter 1, *Intel*® *Extended Memory 64 Technology Software Developer's Guide, Volume 1;* a section has been added to address the 66H prefix. This section is shown below.

\_\_\_\_\_

#### 1.7.1. Other guidelines

• In the initial implementation of Intel<sup>®</sup> EM64T, an operand-size prefix (66H) is ignored when used in 64-bit mode with a near branch. In 64-bit mode, a near branch uses 32-bit displacement (the instruction pointer is advanced to a linear address that is the next sequential instruction offset by a 32 bit displacement, sign extended to 64-bit). Software must not rely on this behavior as future implementations may be different.

\*\*\* \*\*\* \*\*\*

#### 13. MOV—Move to/from Control Registers Section Has Been Updated

In the MOV—Move to/from Control Registers section, *Chapter 4, Intel® Extended Memory 64 Technology Software Developer's Guide, Volume 2;* exception sub-sections have been updated. The entire section is shown below with affected areas marked with change bars.

\_\_\_\_\_

#### MOV—Move to/from Control Registers

| Opcode           | Instruction          | 64-Bit<br>Mode | Compat/<br>Leg<br>Mode | Description               |

|------------------|----------------------|----------------|------------------------|---------------------------|

| 0F 22 /r         | MOV CR0, <i>r</i> 32 | Valid          | Valid                  | Move r32 to CR0           |

| REX.W + 0F 22 /r | MOV CR0, <i>r64</i>  | Valid          | N.E.                   | Move r64 to extended CR0. |

| 0F 22 /r         | MOV CR2, <i>r3</i> 2 | Valid          | Valid                  | Move r32 to CR2           |

| REX.W + 0F 22 /r | MOV CR2, <i>r64</i>  | Valid          | N.E.                   | Move r64 to extended CR2. |

| 0F 22 /r         | MOV CR3, <i>r3</i> 2 | Valid          | Valid                  | Move r32 to CR3           |

| REX.W + 0F 22 /r | MOV CR3, <i>r64</i>  | Valid          | N.E.                   | Move r64 to extended CR3. |

| 0F 22 /r         | MOV CR4, <i>r</i> 32 | Valid          | Valid                  | Move r32 to CR4           |