# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

June 2009

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-024

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.  $I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Intel Core, Intel Xeon, Intel 64, Intel NetBurst, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002–2009, Intel Corporation. All rights reserved..

# Contents

| Revision History          | <br> | • |  | <br>• |   |       | <br>• | • | • • | <br>• | • |   | <br>• | • | • | <br>    | 4 |

|---------------------------|------|---|--|-------|---|-------|-------|---|-----|-------|---|---|-------|---|---|---------|---|

| Preface                   | <br> | • |  | <br>• |   | <br>• |       |   |     |       |   |   | <br>• | • | • | <br>    | 7 |

| Summary Tables of Changes |      | • |  |       |   |       |       | • |     |       |   |   |       | • |   | <br>•   | 8 |

| Documentation Changes     | <br> | • |  |       | • | <br>• |       |   |     |       |   | • |       | • |   | <br>• • | 9 |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul><li>Updated title.</li><li>There are no Documentation Changes for this revision of the document.</li></ul>                                                                                                               | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| Revision | Description                                                                                   | Date        |

|----------|-----------------------------------------------------------------------------------------------|-------------|

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>   | August 2008 |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>  | March 2009  |

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009   |

§

**Revision History**

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                             | Document<br>Number/Location |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture</i>              | 253665                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M</i> | 253666                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z</i> | 253667                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide</i>       | 253668                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide</i>       | 253669                      |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

The following table indicates documentation changes which apply to the  $Intel^{(R)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes**

| No. | DOCUMENTATION CHANGES            |

|-----|----------------------------------|

| 1   | Updates to Chapter 3, Volume 2A  |

| 2   | Updates to Chapter 5, Volume 2B  |

| 3   | Updates to Chapter 2, Volume 3A  |

| 4   | Updates to Chapter 3, Volume 3A  |

| 5   | New Chapter 4 added to Volume 3A |

| 6   | Updates to Chapter 5, Volume 3A  |

| 7   | Updates to Chapter 6, Volume 3A  |

| 8   | Updates to Chapter 9, Volume 3A  |

| 9   | Updates to Chapter 11, Volume 3A |

| 10  | Updates to Chapter 15, Volume 3A |

| 11  | Updates to Chapter 18, Volume 3A |

| 12  | Updates to Chapter 21, Volume 3B |

| 13  | Updates to Chapter 22, Volume 3B |

| 14  | Updates to Chapter 23, Volume 3B |

| 15  | Updates to Chapter 24, Volume 3B |

| 16  | Updates to Chapter 29, Volume 3B |

I

# **Documentation Changes**

#### 1. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

\_\_\_\_\_

•••

#### **CPUID**-**CPU Identification**

| Opcode | Instruction | 64-Bit Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                       |

|--------|-------------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OF A2  | CPUID       | Valid       | Valid               | Returns processor identification<br>and feature information to the<br>EAX, EBX, ECX, and EDX registers,<br>as determined by input entered in<br>EAX (in some cases, ECX as well). |

#### Description

The ID flag (bit 21) in the EFLAGS register indicates support for the CPUID instruction. If a software procedure can set and clear this flag, the processor executing the procedure supports the CPUID instruction. This instruction operates the same in non-64-bit modes and 64-bit mode.

CPUID returns processor identification and feature information in the EAX, EBX, ECX, and EDX registers. The instruction's output is dependent on the contents of the EAX register upon execution (in some cases, ECX as well). For example, the following pseudocode loads EAX with 00H and causes CPUID to return a Maximum Return Value and the Vendor Identification String in the appropriate registers:

Mov Eax, ooh Cpuid

I

Table Table 3-20. shows information returned, depending on the initial value loaded into the EAX register. Table 3-21 shows the maximum CPUID input value recognized for each family of IA-32 processors on which CPUID is implemented.

Two types of information are returned: basic and extended function information. If a value entered for CPUID.EAX is invalid for a particular processor, the data for the highest basic information leaf is returned. For example, using the Intel Core i7 processor, the following is true:

CPUID.EAX = 05H (\* Returns MONITOR/MWAIT leaf. \*) CPUID.EAX = 0AH (\* Returns Architectural Performance Monitoring leaf. \*) CPUID.EAX = 0BH (\* Returns Extended Topology Enumeration leaf. \*) CPUID.EAX = 0CH (\* INVALID: Returns the same information as CPUID.EAX = 0BH. \*) CPUID.EAX = 80000008H (\* Returns linear/physical address size data. \*) CPUID.EAX = 8000000AH (\* INVALID: Returns same information as CPUID.EAX = 0BH. \*)

When CPUID returns the highest basic leaf information as a result of an invalid input EAX value, any dependence on input ECX value in the basic leaf is honored.

| Table 3-20. | Information | Returned h | NV CPUID  | Instruction | (Continued) |   |

|-------------|-------------|------------|-----------|-------------|-------------|---|

|             | Information | Neturneu L | Jy CI OID | monuction   | (Continueu) | 1 |

| 10        |                          | Information Returned by CPUID Instruction (Continued)                                                                                                                                                                                                                                                                                                  |

|-----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | EDX                      | Bits 10-0: Reserved<br>Bit 11: SYSCALL/SYSRET available (when in 64-bit mode)<br>Bits 19-12: Reserved = 0<br>Bit 20: Execute Disable Bit available<br>Bits 26-21: Reserved = 0<br>Bit 27: RDTSCP and IA32_TSC_AUX are available if 1<br>Bits 28: Reserved = 0<br>Bit 29: Intel <sup>®</sup> 64 Architecture available if 1<br>Bits 31-30: Reserved = 0 |

| 8000002H  | EAX<br>EBX<br>ECX<br>EDX | Processor Brand String<br>Processor Brand String Continued<br>Processor Brand String Continued<br>Processor Brand String Continued                                                                                                                                                                                                                     |

| 8000003H  | eax<br>ebx<br>ecx<br>edx | Processor Brand String Continued<br>Processor Brand String Continued<br>Processor Brand String Continued<br>Processor Brand String Continued                                                                                                                                                                                                           |

| 80000004H | EAX<br>EBX<br>ECX<br>EDX | Processor Brand String Continued<br>Processor Brand String Continued<br>Processor Brand String Continued<br>Processor Brand String Continued                                                                                                                                                                                                           |

| 80000005H | EAX<br>EBX<br>ECX<br>EDX | Reserved = 0<br>Reserved = 0<br>Reserved = 0<br>Reserved = 0                                                                                                                                                                                                                                                                                           |

| 80000006H | EAX<br>EBX               | Reserved = 0<br>Reserved = 0                                                                                                                                                                                                                                                                                                                           |

|           | ECX<br>EDX               | Bits 7-0: Cache Line size in bytes<br>Bits 15-12: L2 Associativity field *<br>Bits 31-16: Cache size in 1K units<br>Reserved = 0                                                                                                                                                                                                                       |

|           |                          | NOTES:<br>* L2 associativity field encodings:<br>00H - Disabled<br>01H - Direct mapped<br>02H - 2-way<br>04H - 4-way<br>06H - 8-way<br>08H - 16-way<br>0FH - Fully associative                                                                                                                                                                         |

| 8000007H  | EAX<br>EBX<br>ECX<br>EDX | Reserved = 0<br>Reserved = 0<br>Reserved = 0<br>Bits 7-0: Reserved = 0<br>Bit 8: Invariant TSC available if 1<br>Bits 31-9: Reserved = 0                                                                                                                                                                                                               |

| 8000008H | EAX               | Linear/Physical Address size<br>Bits 7-0: #Physical Address Bits*<br>Bits 15-8: #Linear Address Bits<br>Bits 31-16: Reserved = 0    |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|          | EBX<br>ECX<br>EDX | Reserved = 0<br>Reserved = 0<br>Reserved = 0                                                                                        |

|          |                   | NOTES:<br>* If CPUID.80000008H:EAX[7:0] is supported, the maximum physical<br>address number supported should come from this field. |

•••

#### Table 3-24. More on Feature Information Returned in the EDX Register (Continued)

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | FPU      | Floating Point Unit On-Chip. The processor contains an x87 FPU.                                                                                                                                                                                                                                                                                                                                                                           |

| 1     | VME      | Virtual 8086 Mode Enhancements. Virtual 8086 mode enhancements, including CR4.VME for controlling the feature, CR4.PVI for protected mode virtual interrupts, software interrupt indirection, expansion of the TSS with the software indirection bitmap, and EFLAGS.VIF and EFLAGS.VIP flags.                                                                                                                                             |

| 2     | DE       | <b>Debugging Extensions.</b> Support for I/O breakpoints, including CR4.DE for controlling the feature, and optional trapping of accesses to DR4 and DR5.                                                                                                                                                                                                                                                                                 |

| 3     | PSE      | <b>Page Size Extension.</b> Large pages of size 4 MByte are supported, including CR4.PSE for controlling the feature, the defined dirty bit in PDE (Page Directory Entries), optional reserved bit trapping in CR3, PDEs, and PTEs.                                                                                                                                                                                                       |

| 4     | TSC      | <b>Time Stamp Counter.</b> The RDTSC instruction is supported, including CR4.TSD for controlling privilege.                                                                                                                                                                                                                                                                                                                               |

| 5     | MSR      | <b>Model Specific Registers RDMSR and WRMSR Instructions.</b> The RDMSR and WRMSR instructions are supported. Some of the MSRs are implementation dependent.                                                                                                                                                                                                                                                                              |

| 6     | PAE      | <b>Physical Address Extension.</b> Physical addresses greater than 32 bits are supported: extended page table entry formats, an extra level in the page translation tables is defined, 2-MByte pages are supported instead of 4 Mbyte pages if PAE bit is 1.                                                                                                                                                                              |

| 7     | MCE      | Machine Check Exception. Exception 18 is defined for Machine Checks, including CR4.MCE for controlling the feature. This feature does not define the model-specific implementations of machine-check error logging, reporting, and processor shutdowns. Machine Check exception handlers may have to depend on processor version to do model specific processing of the exception, or test for the presence of the Machine Check feature. |

| 8     | CX8      | <b>CMPXCHG8B Instruction.</b> The compare-and-exchange 8 bytes (64 bits) instruction is supported (implicitly locked and atomic).                                                                                                                                                                                                                                                                                                         |

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9     | APIC     | <b>APIC On-Chip.</b> The processor contains an Advanced Programmable Interrupt Controller (APIC), responding to memory mapped commands in the physical address range FFFE0000H to FFFE0FFFH (by default - some processors permit the APIC to be relocated).                                                                                                                     |

| 10    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                        |

| 11    | SEP      | SYSENTER and SYSEXIT Instructions. The SYSENTER and SYSEXIT and associated MSRs are supported.                                                                                                                                                                                                                                                                                  |

| 12    | MTRR     | <b>Memory Type Range Registers.</b> MTRRs are supported. The MTRRcap MSR contains feature bits that describe what memory types are supported, how many variable MTRRs are supported, and whether fixed MTRRs are supported.                                                                                                                                                     |

| 13    | PGE      | <b>Page Global Bit.</b> The global bit is supported in paging-structure entries (PDEs and PTEs) that map a page, indicating TLB entries that are common to different processes and need not be flushed. The CR4.PGE bit controls this feature.                                                                                                                                  |

| 14    | MCA      | Machine Check Architecture. The Machine Check Architecture, which<br>provides a compatible mechanism for error reporting in P6 family, Pentium<br>4, Intel Xeon processors, and future processors, is supported. The MCG_CAP<br>MSR contains feature bits describing how many banks of error reporting<br>MSRs are supported.                                                   |

| 15    | CMOV     | <b>Conditional Move Instructions.</b> The conditional move instruction CMOV is supported. In addition, if x87 FPU is present as indicated by the CPUID.FPU feature bit, then the FCOMI and FCMOV instructions are supported                                                                                                                                                     |

| 16    | PAT      | <b>Page Attribute Table.</b> Page Attribute Table is supported. This feature augments the Memory Type Range Registers (MTRRs), allowing an operating system to specify attributes of memory accessed through a linear address on a 4KB granularity.                                                                                                                             |

| 17    | PSE-36   | <b>36-Bit Page Size Extension.</b> 4-MByte pages addressing physical memory beyond 4 GBytes are supported with 32-bit paging. This feature indicates that upper bits of the physical address of a 4-MByte page are encoded in bits 20:13 of the page-directory entry. Such physical addresses are limited by MAXPHYADDR and may be up to 40 bits in size.                       |

| 18    | PSN      | <b>Processor Serial Number.</b> The processor supports the 96-bit processor identification number feature and the feature is enabled.                                                                                                                                                                                                                                           |

| 19    | CLFSH    | CLFLUSH Instruction. CLFLUSH Instruction is supported.                                                                                                                                                                                                                                                                                                                          |

| 20    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                        |

| 21    | DS       | <b>Debug Store.</b> The processor supports the ability to write debug information into a memory resident buffer. This feature is used by the branch trace store (BTS) and precise event-based sampling (PEBS) facilities (see Chapter 19, "Debugging and Performance Monitoring," in the Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B). |

| 22    | ACPI     | Thermal Monitor and Software Controlled Clock Facilities. The processor<br>implements internal MSRs that allow processor temperature to be<br>monitored and processor performance to be modulated in predefined duty<br>cycles under software control.                                                                                                                          |

| 23    | MMX      | Intel MMX Technology. The processor supports the Intel MMX technology.                                                                                                                                                                                                                                                                                                          |

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24    | FXSR     | <b>FXSAVE and FXRSTOR Instructions.</b> The FXSAVE and FXRSTOR instructions are supported for fast save and restore of the floating point context. Presence of this bit also indicates that CR4.0SFXSR is available for an operating system to indicate that it supports the FXSAVE and FXRSTOR instructions.                                                         |

| 25    | SSE      | SSE. The processor supports the SSE extensions.                                                                                                                                                                                                                                                                                                                       |

| 26    | SSE2     | SSE2. The processor supports the SSE2 extensions.                                                                                                                                                                                                                                                                                                                     |

| 27    | SS       | <b>Self Snoop.</b> The processor supports the management of conflicting memory types by performing a snoop of its own cache structure for transactions issued to the bus.                                                                                                                                                                                             |

| 28    | HTT      | <b>Multi-Threading.</b> The physical processor package is capable of supporting more than one logical processor.                                                                                                                                                                                                                                                      |

| 29    | ТМ       | <b>Thermal Monitor.</b> The processor implements the thermal monitor automatic thermal control circuitry (TCC).                                                                                                                                                                                                                                                       |

| 30    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                              |

| 31    | PBE      | <b>Pending Break Enable.</b> The processor supports the use of the FERR#/PBE# pin when the processor is in the stop-clock state (STPCLK# is asserted) to signal the processor that an interrupt is pending and that the processor should return to normal operation to handle the interrupt. Bit 10 (PBE enable) in the IA32_MISC_ENABLE MSR enables this capability. |

...

#### **IA-32 Architecture Compatibility**

CPUID is not supported in early models of the Intel486 processor or in any IA-32 processor earlier than the Intel486 processor.

#### Operation

IA32\_BIOS\_SIGN\_ID MSR ← Update with installed microcode revision number;

CASE (EAX) OF

EAX = 0:

$\mathsf{EAX} \leftarrow \mathsf{Highest} \text{ basic function input value understood by CPUID};$

$EBX \leftarrow Vendor identification string;$

EDX  $\leftarrow$  Vendor identification string;

ECX  $\leftarrow$  Vendor identification string;

BREAK;

EAX = 1H:

EAX[3:0]  $\leftarrow$  Stepping ID;

$EAX[7:4] \leftarrow Model;$

EAX[11:8]  $\leftarrow$  Family;

$EAX[13:12] \leftarrow Processor type;$

$EAX[15:14] \leftarrow Reserved;$

$EAX[19:16] \leftarrow Extended Model;$

$EAX[27:20] \leftarrow Extended Family;$

$EAX[31:28] \leftarrow Reserved;$

```

EBX[7:0] \leftarrow Brand Index; (* Reserved if the value is zero. *)

EBX[15:8] \leftarrow CLFLUSH Line Size;

EBX[16:23] ← Reserved; (* Number of threads enabled = 2 if MT enable fuse set. *)

EBX[24:31] \leftarrow Initial APIC ID;

ECX ← Feature flags; (* See Figure 3-7. *)

EDX \leftarrow Feature flags; (* See Figure 3-8. *)

BREAK;

EAX = 2H:

EAX ← Cache and TLB information;

EBX ← Cache and TLB information;

ECX ← Cache and TLB information;

EDX \leftarrow Cache and TLB information;

BREAK;

EAX = 3H:

EAX \leftarrow Reserved;

EBX \leftarrow Reserved;

ECX \leftarrow ProcessorSerialNumber[31:0];

(* Pentium III processors only, otherwise reserved. *)

EDX \leftarrow ProcessorSerialNumber[63:32];

(* Pentium III processors only, otherwise reserved. *

BREAK

EAX = 4H:

EAX ← Deterministic Cache Parameters Leaf; (* See Table Table 3-20.. *)

EBX ← Deterministic Cache Parameters Leaf;

ECX ← Deterministic Cache Parameters Leaf;

EDX ← Deterministic Cache Parameters Leaf;

BREAK;

EAX = 5H:

EAX ← MONITOR/MWAIT Leaf; (* See Table Table 3-20.. *)

EBX ← MONITOR/MWAIT Leaf;

ECX ← MONITOR/MWAIT Leaf;

EDX ← MONITOR/MWAIT Leaf;

BREAK;

EAX = 6H:

EAX \leftarrow Thermal and Power Management Leaf; (* See Table Table 3-20.. *)

EBX \leftarrow Thermal and Power Management Leaf;

ECX \leftarrow Thermal and Power Management Leaf;

EDX ← Thermal and Power Management Leaf;

BREAK;

EAX = 7H \text{ or } 8H:

EAX \leftarrow Reserved = 0;

EBX \leftarrow Reserved = 0;

ECX \leftarrow Reserved = 0;

EDX \leftarrow Reserved = 0;

BREAK;

EAX = 9H:

EAX ← Direct Cache Access Information Leaf; (* See Table Table 3-20.. *)

EBX ← Direct Cache Access Information Leaf;

ECX ← Direct Cache Access Information Leaf;

EDX ← Direct Cache Access Information Leaf;

```

```

BREAK;

EAX = AH:

EAX \leftarrow Architectural Performance Monitoring Leaf; (* See Table Table 3-20.. *)

EBX ← Architectural Performance Monitoring Leaf;

ECX ← Architectural Performance Monitoring Leaf;

EDX ← Architectural Performance Monitoring Leaf;

BREAK

EAX = BH:

EAX ← Extended Topology Enumeration Leaf; (* See Table Table 3-20.. *)

EBX ← Extended Topology Enumeration Leaf;

ECX ← Extended Topology Enumeration Leaf;

EDX ← Extended Topology Enumeration Leaf;

BREAK;

EAX = CH:

EAX \leftarrow Reserved = 0;

EBX \leftarrow Reserved = 0;

ECX \leftarrow Reserved = 0;

EDX \leftarrow Reserved = 0;

BREAK;

EAX = DH:

EAX ← Processor Extended State Enumeration Leaf; (* See Table Table 3-20.. *)

EBX ← Processor Extended State Enumeration Leaf;

ECX ← Processor Extended State Enumeration Leaf;

EDX ← Processor Extended State Enumeration Leaf;

BREAK;

BREAK;

EAX = 8000000H:

EAX \leftarrow Highest extended function input value understood by CPUID;

EBX \leftarrow Reserved:

ECX \leftarrow Reserved;

EDX \leftarrow Reserved;

BREAK;

EAX = 80000001H:

EAX \leftarrow Reserved;

EBX ← Reserved;

ECX \leftarrow Extended Feature Bits (* See Table Table 3-20..*);

EDX ← Extended Feature Bits (* See Table Table 3-20.. *);

BREAK;

EAX = 8000002H:

EAX ← Processor Brand String;

EBX ← Processor Brand String, continued;

ECX ← Processor Brand String, continued;

EDX ← Processor Brand String, continued;

BREAK;

EAX = 8000003H:

EAX ← Processor Brand String, continued;

EBX ← Processor Brand String, continued;

ECX ← Processor Brand String, continued;

EDX ← Processor Brand String, continued;

BREAK;

```

# (intel)

```

EAX = 8000004H:

EAX ← Processor Brand String, continued;

EBX ← Processor Brand String, continued;

ECX ← Processor Brand String, continued;

EDX ← Processor Brand String, continued;

BREAK;

EAX = 8000005H:

EAX \leftarrow Reserved = 0;

EBX \leftarrow Reserved = 0;

ECX \leftarrow Reserved = 0;

EDX \leftarrow Reserved = 0;

BREAK;

EAX = 8000006H:

EAX \leftarrow Reserved = 0;

EBX \leftarrow Reserved = 0;

ECX ← Cache information;

EDX \leftarrow Reserved = 0;

BREAK;

EAX = 8000007H:

EAX \leftarrow Reserved = 0;

EBX \leftarrow Reserved = 0;

ECX \leftarrow Reserved = 0;

EDX ← Reserved = Misc Feature Flags;

BREAK;

EAX = 8000008H:

EAX ← Reserved = Physical Address Size Information;

EBX ← Reserved = Virtual Address Size Information;

ECX \leftarrow Reserved = 0;

EDX \leftarrow Reserved = 0;

BREAK;

EAX >= 4000000H and EAX <= 4FFFFFFH:

DEFAULT: (* EAX = Value outside of recognized range for CPUID. *)

(* If the highest basic information leaf data depend on ECX input value, ECX is honored.*)

EAX ← Reserved; (* Information returned for highest basic information leaf. *)

EBX \leftarrow Reserved; (* Information returned for highest basic information leaf. *)

ECX \leftarrow Reserved; (* Information returned for highest basic information leaf. *)

EDX ← Reserved; (* Information returned for highest basic information leaf. *)

BREAK;

ESAC;

```

#### ...

#### 2. Updates to Chapter 5, Volume 2B

Change bars show changes to Chapter 2 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: xxxx.

\_\_\_\_\_

#### **INVVPID**— Invalidate Translations Based on VPID

• Single-context invalidation, retaining global translations: If the INVVPID type is 3, the logical processor invalidates all mappings tagged with the VPID specified in the INVVPID descriptor except global translations. In some cases, it may invalidate global translations (and mappings with other VPIDs) as well. See Section 4.10, "Caching Translation Information," in *IA-32 Intel Architecture Software Developer's Manual, Volumes 3A* for information about global translations.

# ...

3.

#### Updates to Chapter 2, Volume 3A

Change bars show changes to Chapter 2 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1.

\_\_\_\_\_

...

# 2.1.3 Task-State Segments and Task Gates

The TSS (see Figure 2-1) defines the state of the execution environment for a task. It includes the state of general-purpose registers, segment registers, the EFLAGS register, the EIP register, and segment selectors with stack pointers for three stack segments (one stack for each privilege level). The TSS also includes the segment selector for the LDT associated with the task and the base address of the paging-structure hierarchy.

All program execution in protected mode happens within the context of a task (called the current task). The segment selector for the TSS for the current task is stored in the task register. The simplest method for switching to a task is to make a call or jump to the new task. Here, the segment selector for the TSS of the new task is given in the CALL or JMP instruction. In switching tasks, the processor performs the following actions:

- 1. Stores the state of the current task in the current TSS.

- 2. Loads the task register with the segment selector for the new task.

- 3. Accesses the new TSS through a segment descriptor in the GDT.

- 4. Loads the state of the new task from the new TSS into the general-purpose registers, the segment registers, the LDTR, control register CR3 (base address of the paging-structure hierarchy), the EFLAGS register, and the EIP register.

- 5. Begins execution of the new task.

A task can also be accessed through a task gate. A task gate is similar to a call gate, except that it provides access (through a segment selector) to a TSS rather than a code segment.

#### 2.1.5 Memory Management

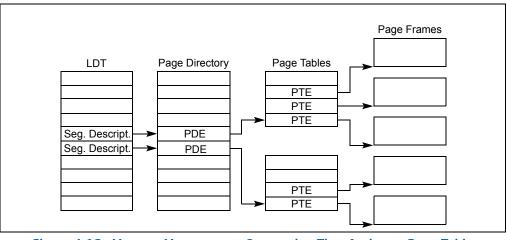

System architecture supports either direct physical addressing of memory or virtual memory (through paging). When physical addressing is used, a linear address is treated as a physical address. When paging is used: all code, data, stack, and system segments (including the GDT and IDT) can be paged with only the most recently accessed pages being held in physical memory.

The location of pages (sometimes called page frames) in physical memory is contained in the paging structures. These structures reside in physical memory (see Figure 2-1 for the case of 32-bit paging).

The base physical address of the paging-structure hierarchy is contained in control register CR3. The entries in the paging structures determine the physical address of the base of a page frame, access rights and memory management information.

To use this paging mechanism, a linear address is broken into parts. The parts provide separate offsets into the paging structures and the page frame. A system can have a single hierarchy of paging structures or several. For example, each task can have its own hierarchy.

#### 2.1.5.1 Memory Management in IA-32e Mode

In IA-32e mode, physical memory pages are managed by a set of system data structures. In compatibility mode and 64-bit mode, four levels of system data structures are used. These include:

- The page map level 4 (PML4) An entry in a PML4 table contains the physical address of the base of a page directory pointer table, access rights, and memory management information. The base physical address of the PML4 is stored in CR3.

- A set of page directory pointer tables An entry in a page directory pointer table contains the physical address of the base of a page directory table, access rights, and memory management information.

- Sets of page directories An entry in a page directory table contains the physical address of the base of a page table, access rights, and memory management information.

- Sets of page tables An entry in a page table contains the physical address of a page frame, access rights, and memory management information.

## 2.1.6 System Registers

To assist in initializing the processor and controlling system operations, the system architecture provides system flags in the EFLAGS register and several system registers:

- The system flags and IOPL field in the EFLAGS register control task and mode switching, interrupt handling, instruction tracing, and access rights. See also: Section 2.3, "System Flags and Fields in the EFLAGS Register."

- The control registers (CR0, CR2, CR3, and CR4) contain a variety of flags and data fields for controlling system-level operations. Other flags in these registers are used to indicate support for specific processor capabilities within the operating system or executive. See also: Section 2.5, "Control Registers."

- The debug registers (not shown in Figure 2-1) allow the setting of breakpoints for use in debugging programs and systems software. See also: Chapter 19, "Debugging and Performance Monitoring."

- The GDTR, LDTR, and IDTR registers contain the linear addresses and sizes (limits) of their respective tables. See also: Section 2.4, "Memory-Management Registers."

- The task register contains the linear address and size of the TSS for the current task. See also: Section 2.4, "Memory-Management Registers."

- Model-specific registers (not shown in Figure 2-1).

The model-specific registers (MSRs) are a group of registers available primarily to operating-system or executive procedures (that is, code running at privilege level 0). These registers control items such as the debug extensions, the performance-monitoring counters, the machine- check architecture, and the memory type ranges (MTRRs).

The number and function of these registers varies among different members of the Intel 64 and IA-32 processor families. See also: Section 9.4, "Model-Specific Registers (MSRs)," and Appendix B, "Model-Specific Registers (MSRs)."

Most systems restrict access to system registers (other than the EFLAGS register) by application programs. Systems can be designed, however, where all programs and procedures run at the most privileged level (privilege level 0). In such a case, application programs would be allowed to modify the system registers.

...

# 2.5 CONTROL REGISTERS

Control registers (CR0, CR1, CR2, CR3, and CR4; see Figure 2-6) determine operating mode of the processor and the characteristics of the currently executing task. These registers are 32 bits in all 32-bit modes and compatibility mode.

In 64-bit mode, control registers are expanded to 64 bits. The MOV CRn instructions are used to manipulate the register bits. Operand-size prefixes for these instructions are ignored. The following is also true:

- Bits 63:32 of CR0 and CR4 are reserved and must be written with zeros. Writing a nonzero value to any of the upper 32 bits results in a general-protection exception, #GP(0).

- All 64 bits of CR2 are writable by software.

- Bits 51:40 of CR3 are reserved and must be 0.

- The MOV CRn instructions do not check that addresses written to CR2 and CR3 are within the linear-address or physical-address limitations of the implementation.

- Register CR8 is available in 64-bit mode only.

The control registers are summarized below, and each architecturally defined control field in these control registers are described individually. In Figure 2-6, the width of the register in 64-bit mode is indicated in parenthesis (except for CR0).

- CR0 Contains system control flags that control operating mode and states of the processor.

- CR1 Reserved.

- CR2 Contains the page-fault linear address (the linear address that caused a page fault).

- CR3 Contains the physical address of the base of the paging-structure hierarchy and two flags (PCD and PWT). Only the most-significant bits (less the lower 12 bits) of the base address are specified; the lower 12 bits of the address are assumed to be 0. The first paging structure must thus be aligned to a page (4-KByte) boundary. The PCD and PWT flags control caching of that paging structure in the processor's internal data caches (they do not control TLB caching of page-directory information).

When using the physical address extension, the CR3 register contains the base address of the page-directory-pointer table In IA-32e mode, the CR3 register contains the base address of the PML4 table.

See also: Chapter 4, "Paging."

- CR4 Contains a group of flags that enable several architectural extensions, and indicate operating system or executive support for specific processor capabilities. The control registers can be read and loaded (or modified) using the move-to-or-from-control-registers forms of the MOV instruction. In protected mode, the MOV instructions allow the control registers to be read or loaded (at privilege level 0 only). This restriction means that application programs or operating-system procedures (running at privilege levels 1, 2, or 3) are prevented from reading or loading the control registers.

- CR8 Provides read and write access to the Task Priority Register (TPR). It specifies

the priority threshold value that operating systems use to control the priority class of

external interrupts allowed to interrupt the processor. This register is available only

in 64-bit mode. However, interrupt filtering continues to apply in compatibility mode.

# 8086 mode.

. . .

- WP Write Protect (bit 16 of CR0) Inhibits supervisor-level procedures from writing into user-level read-only pages when set; allows supervisor-level procedures to write into user-level read-only pages when clear (regardless of the U/S bit setting; see Section 4.1.3 and Section 4.6). This flag facilitates implementation of the copy-on-write method of creating a new process (forking) used by operating systems such as UNIX.

- •••

- MP Monitor Coprocessor (bit 1 of CR0). Controls the interaction of the WAIT (or FWAIT) instruction with the TS flag (bit 3 of CR0). If the MP flag is set, a WAIT instruction generates a device-not-available exception (#NM) if the TS flag is also set. If the MP flag is clear, the WAIT instruction ignores the setting of the TS flag. Table 9-2 shows the recommended setting of this flag, depending on the IA-32 processor and x87 FPU or math coprocessor present in the system. Table 2-1 shows the interaction of the MP, EM, and TS flags.

- PE **Protection Enable (bit 0 of CR0)** Enables protected mode when set; enables real-address mode when clear. This flag does not enable paging directly. It only enables segment-level protection. To enable paging, both the PE and PG flags must be set.

See also: Section 9.9, "Mode Switching."

PCD **Page-level Cache Disable (bit 4 of CR3)** — Controls caching of the first paging structure of the current paging-structure hierarchy. When the PCD flag is set, caching of the page-directory is prevented; when the flag is clear, the page-directory can be cached. This flag affects only the processor's internal caches (both L1 and L2, when present). The processor ignores this flag if paging is not used (the PG flag in register CR0 is clear) or the CD (cache disable) flag in CR0 is set.

See also: Chapter 11, "Memory Cache Control" (for more about the use of the PCD flag) and Section 4.9, "Paging and Memory Typing" (for a discussion of a companion PCD flag in page-directory and page-table entries).

PWT **Page-level Write-Through (bit 3 of CR3)** — Controls the write-through or write-back caching policy of the first paging structure of the current paging-structure hierarchy. When the PWT flag is set, write-through caching is enabled; when the flag is clear, write-back caching is enabled. This flag affects only internal caches (both L1 and L2, when present). The processor ignores this flag

if paging is not used (the PG flag in register CR0 is clear) or the CD (cache disable) flag in CR0 is set.

See also: Section 11.5, "Cache Control" (for more information about the use of this flag), and Section 4.9, "Paging and Memory Typing" (for a discussion of a companion PCD flag in the page-directory and page-table entries).

•••

PSE **Page Size Extensions (bit 4 of CR4)** — Enables 4-MByte pages with 32-bit paging when set; restricts 32-bit paging to pages to 4 KBytes when clear.

See also: Section 4.3, "32-Bit Paging."

PAE **Physical Address Extension (bit 5 of CR4)** — When set, enables paging to produce physical addresses with more than 32 bits. When clear, restricts physical addresses to 32 bits. PAE must be set before entering IA-32e mode. See also: Chapter 4, "Paging."

#### 4. Updates to Chapter 3, Volume 3A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1.

------

...

# 3.3 PHYSICAL ADDRESS SPACE

In protected mode, the IA-32 architecture provides a normal physical address space of 4 GBytes (2<sup>32</sup> bytes). This is the address space that the processor can address on its address bus. This address space is flat (unsegmented), with addresses ranging continuously from 0 to FFFFFFFH. This physical address space can be mapped to read-write memory, read-only memory, and memory mapped I/O. The memory mapping facilities described in this chapter can be used to divide this physical memory up into segments and/or pages.

Starting with the Pentium Pro processor, the IA-32 architecture also supports an extension of the physical address space to  $2^{36}$  bytes (64 GBytes); with a maximum physical address of FFFFFFFFH. This extension is invoked in either of two ways:

- Using the physical address extension (PAE) flag, located in bit 5 of control register CR4.

- Using the 36-bit page size extension (PSE-36) feature (introduced in the Pentium III processors).

Physical address support has since been extended beyond 36 bits. See Chapter 4, "Paging" for more information about 36-bit physical addressing.

•••

5.

#### New Chapter 4 added to Volume 3A

New Chapter 4 has been added to the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1.

\_\_\_\_\_

# CHAPTER 4 PAGING

Chapter 3 explains how segmentation converts logical addresses to linear addresses. **Paging** (or linear-address translation) is the process of translating linear addresses so that they can be used to access memory or I/O devices. Paging translates each linear address to a **physical address** and determines, for each translation, what accesses to the linear address are allowed (the address's **access rights**) and the type of caching used for such accesses (the address's **memory type**).

Intel-64 processors support three different paging modes. These modes are identified and defined in Section 4.1. Section 4.2 gives an overview of the translation mechanism that is used in all modes. Section 4.3, Section 4.4, and Section 4.5 discuss the three paging modes in detail.

Section 4.6 details how paging determines and uses access rights. Section 4.7 discusses exceptions that may be generated by paging (page-fault exceptions). Section 4.8 considers data which the processor writes in response to linear-address accesses (accessed and dirty flags).

Section 4.9 describes how paging determines the memory types used for accesses to linear addresses. Section 4.10 provides details of how a processor may cache information about linear-address translation. Section 4.11 outlines interactions between paging and certain VMX features. Section 4.12 gives an overview of how paging can be used to implement virtual memory.

# 4.1 PAGING MODES AND CONTROL BITS

Paging behavior is controlled by the following control bits:

- The WP and PG flags in control register CR0 (bit 16 and bit 31, respectively).

- The PSE, PAE, and PGE flags in control register CR4 (bit 4, bit 5, and bit 7, respectively).

- The LME and NXE flags in the IA32\_EFER MSR (bit 8 and bit 11, respectively).

Software enables paging by using the MOV to CR0 instruction to set CR0.PG. Before dong so, software should ensure that control register CR3 contains the physical address of the first paging structure that the processor will use for linear-address translation (see Section 4.2) and that that structure is initialized as desired. See Table Table 4-3., Table Table 4-7., and Table Table 4-12. for the use of CR3 in the different paging modes.

Section 4.1.1 describes how the values of CR0.PG, CR4.PAE, and IA32\_EFER.LME determine whether paging is in use and, if so, which of three paging modes is in use. Section 4.1.2 explains how to manage these bits to establish or make changes in paging modes. Section 4.1.3 discusses how CR0.WP, CR4.PSE, CR4.PGE, and IA32\_EFER.NXE modify the operation of the different paging modes.

#### 4.1.1 Three Paging Modes

If CR0.PG = 0, paging is not used. The logical processor treats all linear addresses as if they were physical addresses. CR4.PAE and IA32\_EFER.LME are ignored by the processor, as are CR0.WP, CR4.PSE, and CR4.PGE, and IA32\_EFER.NXE.

Paging is enabled if CR0.PG = 1. Paging can be enabled only if protection is enabled (CR0.PE = 1). If paging is enabled, one of three paging modes is used. The values of CR4.PAE and IA32\_EFER.LME determine which paging mode is used:

- If CR0.PG = 1 and CR4.PAE = 0, **32-bit paging** is used. 32-bit paging is detailed in Section 4.3. 32-bit paging uses CR0.WP, CR4.PSE, and CR4.PGE as described in Section 4.1.3.

- If CR0.PG = 1, CR4.PAE = 1, and IA32\_EFER.LME = 0, **PAE paging** is used. PAE paging is detailed in Section 4.4. PAE paging uses CR0.WP, CR4.PGE, and IA32\_EFER.NXE as described in Section 4.1.3.

- If CR0.PG = 1, CR4.PAE = 1, and IA32\_EFER.LME = 1, IA-32e paging is used.<sup>1</sup> IA-32e paging is detailed in Section 4.5. IA-32e paging uses CR0.WP, CR4.PGE, and IA32\_EFER.NXE as described in Section 4.1.3. IA-32e paging is available only on processors that support the Intel 64 architecture.

The three paging modes differ with regard to the following details:

- Linear-address width. The size of the linear addresses that can be translated.

- Physical-address width. The size of the physical addresses produced by paging.

- Page size. The granularity at which linear addresses are translated. Linear addresses on the same page are translated to corresponding physical addresses on the same page.

- Support for execute-disable access rights. In some paging modes, software can be prevented from fetching instructions from pages that are otherwise readable.

Table Table 4-1. illustrates the key differences between the three paging modes.

| Paging<br>Mode | CR0.PG | CR4.PAE | LME in<br>IA32_EFER | Linear-<br>Address<br>Width | Physical-<br>Address<br>Width <sup>1</sup> | Page<br>Size(s)                 | Supports<br>Execute-<br>Disable? |

|----------------|--------|---------|---------------------|-----------------------------|--------------------------------------------|---------------------------------|----------------------------------|

| None           | 0      | N/A     | N/A                 | 32                          | 32                                         | N/A                             | No                               |

| 32-bit         | 1      | 0       | 0 <sup>2</sup>      | 32                          | Up to 40 <sup>3</sup>                      | 4-KByte<br>4-MByte <sup>4</sup> | No                               |

| PAE            | 1      | 1       | 0                   | 32                          | Up to 52                                   | 4-KByte<br>2-MByte              | Yes <sup>5</sup>                 |

| IA-32e         | 1      | 1       | 2                   | 48                          | Up to 52                                   | 4-KByte<br>2-MByte              | Yes <sup>5</sup>                 |

Table 4-1. Properties of Different Paging Modes

#### NOTES:

1. The physical-address width is always bounded by MAXPHYADDR; see Section 4.1.4.

2. The processor ensures that IA32\_EFER.LME must be 0 if CR0.PG = 1 and CR4.PAE = 0.

3. 32-bit paging supports physical-address widths of more than 32 bits only for 4-MByte pages and only if the PSE-36 mechanism is supported; see Section 4.1.4 and Section 4.3.

4. 4-MByte pages are used with 32-bit paging only if CR4.PSE = 1; see Section 4.3.

5. Execute-disable access rights are applied only if IA32\_EFER.NXE = 1; see Section 4.6.

The LMA flag in the IA32\_EFER MSR (bit 10) is a status bit that indicates whether the logical processor is in IA-32e mode (and thus using IA-32e paging). The processor always sets IA32\_EFER.LMA to CR0.PG & IA32\_EFER.LME. Software cannot directly modify IA32\_EFER.LMA; an execution of WRMSR to the IA32\_EFER MSR ignores bit 10 of its source operand.

Because they are used only if IA32\_EFER.LME = 0, 32-bit paging and PAE paging is used only in legacy protected mode. Because legacy protected mode cannot produce linear addresses larger than 32 bits, 32-bit paging and PAE paging translate 32-bit linear addresses.

Because it is used only if IA32\_EFER.LME = 1, IA-32e paging is used only in IA-32e mode. (In fact, it is the use of IA-32e paging that defines IA-32 mode.) IA-32 mode has two sub-modes:

- Compatibility mode. This mode uses only 32-bit linear addresses. IA-32e paging treats bits 47:32 of such an address as all 0.

- 64-bit mode. While this mode produces 64-bit linear addresses, the processor ensures that bits 63:47 of such an address are identical.<sup>1</sup> IA-32e paging does not use bits 63:48 of such addresses.

## 4.1.2 Paging-Mode Enabling

If CR0.PG = 1, a logical processor is in one of three paging modes, depending on the values of CR4.PAE and IA32\_EFER.LME. Figure 4-1 illustrates how software can enable these modes and make transitions between them. The following items identify certain limitations and other details:

- IA32\_EFER.LME cannot be modified while paging is enabled (CR0.PG = 1). Attempts to do so using WRMSR cause a general-protection exception (#GP(0)).

- Paging cannot be enabled (by setting CR0.PG to 1) while CR4.PAE = 0 and IA32\_EFER.LME = 1. Attempts to do so using MOV to CR0 cause a general-protection exception (#GP(0)).

- CR4.PAE cannot be cleared while IA-32e paging is active (CR0.PG = 1 and IA32\_EFER.LME = 1). Attempts to do so using MOV to CR4 cause a generalprotection exception (#GP(0)).

- Software can always disable paging by clearing CR0.PG with MOV to CR0.

- Software can make transitions between 32-bit paging and PAE paging by changing the value of CR4.PAE with MOV to CR4.

- Software cannot make transitions directly between IA-32e paging and either of the other two paging modes. It must first disable paging (by clearing CR0.PG with MOV to CR0), then set CR4.PAE and IA32\_EFER.LME to the desired values (with MOV to CR4 and WRMSR), and then re-enable paging (by setting CR0.PG with MOV to CR0). As noted earlier, an attempt to clear either CR4.PAE or IA32\_EFER.LME cause a general-protection exception (#GP(0)).

- VMX transitions allow transitions between paging modes that are not possible using MOV to CR or WRMSR. This is because VMX transitions can load CR0, CR4, and IA32\_EFER in one operation. See Section 4.11.1.

## 4.1.3 Paging-Mode Modifiers

Details of how each paging mode operates are determined by the following control bits:

• The WP flag in CR0 (bit 16).

Such an address is called **canonical**. Use of a non-canonical linear address in 64-bit mode produces a general-protection exception (#GP(0)); the processor does not attempt to translate non-canonical linear addresses using IA-32e paging.

Figure 4-1 Enabling and Changing Paging Modes

- The PSE and PGE flags in CR4 (bit 4 and bit 7, respectively).

- The NXE flag in the IA32\_EFER MSR (bit 11).

CR0.WP allows pages to be protected from supervisor-mode writes. If CR0.WP = 0, software operating with CPL < 3 (supervisor mode) can write to linear addresses with readonly access rights; if CR0.WP = 1, it cannot. (Software operating with CPL = 3 - user mode - cannot write to linear addresses with read-only access rights, regardless of the value of CR0.WP.) Section 4.6 explains how access rights are determined.

CR4.PSE enables 4-MByte pages for 32-bit paging. If CR4.PSE = 0, 32-bit paging can use only 4-KByte pages; if CR4.PSE = 1, 32-bit paging can use both 4-KByte pages and 4-MByte pages. See Section 4.3 for more information. (PAE paging and IA-32e paging can use multiple page sizes regardless of the value of CR4.PSE.)

CR4.PGE enables global pages. If CR4.PGE = 0, no translations are shared across address spaces; if CR4.PGE = 1, specified translations may be shared across address spaces. See Section 4.10.1.4 for more information.

IA32\_EFER.NXE enables execute-disable access rights for PAE paging and IA-32e paging. If IA32\_EFER.NXE = 0, software may fetch instructions from any linear address

that paging allows the software to read; if IA32\_EFER.NXE = 1, instructions fetches can be prevented from specified linear addresses (even if data reads from the addresses are allowed). Section 4.6 explains how access rights are determined. (32-bit paging always allows software to fetch instructions from any linear address that may be read; IA32\_EFER.NXE has no effect with 32-bit paging. Software that wants to limit instruction fetches from readable pages must use either PAE paging or IA-32e paging.)

# 4.1.4 Enumeration of Paging Features by CPUID

Software can discover support for different paging features using the CPUID instruction:

- PSE: page-size extensions for 32-bit paging. If CPUID.01H:EDX.PSE [bit 3] = 1, CR4.PSE may be set to 1, enabling support for 4-MByte pages with 32-bit paging (see Section 4.3).

- PAE: physical-address extension. If CPUID.01H:EDX.PAE [bit 6] = 1, CR4.PAE may be set to 1, enabling PAE paging (this setting is also required for IA-32e paging).

- PGE: global-page support. If CPUID.01H:EDX.PGE [bit 13] = 1, CR4.PGE may be set to 1, enabling the global-page feature (see Section 4.10.1.4).

- PAT: page-attribute table. If CPUID.01H:EDX.PAT [bit 16] = 1, the 8-entry page-attribute table (PAT) is supported. When the PAT is supported, three bits in certain paging-structure entries select a memory type (used to determine type of caching used) from the PAT (see Section 4.9).

- PSE-36: 36-Bit page size extension. If CPUID.01H:EDX.PSE-36 [bit 17] = 1, the PSE-36 mechanism is supported, indicating that translations using 4-MByte pages with 32-bit paging may produce physical addresses with more than 32 bits (see Section 4.3).

- NX: execute disable. If CPUID.80000001H:EDX.NX [bit 20] = 1, IA32\_EFER.NXE may be set to 1, allowing PAE paging and IA-32e paging to disable execute access to selected pages (see Section 4.6). (Processors that do not support CPUID function 80000001H do not allow IA32\_EFER.NXE to be set to 1.)

- LM: IA-32e mode support. If CPUID.80000001H:EDX.LM [bit 29] = 1, IA32\_EFER.LME may be set to 1, enabling IA-32e paging. (Processors that do not support CPUID function 80000001H do not allow IA32\_EFER.LME to be set to 1.)

- CPUID.80000008H:EAX[7:0] reports the physical-address width supported by the processor. (For processors that do not support CPUID function 80000008H, the width is generally 36 if CPUID.01H:EDX.PAE [bit 6] = 1 and 32 otherwise.) This width is referred to as MAXPHYADDR. MAXPHYADDR is at most 52.

- CPUID.80000008H:EAX[15:8] reports the linear-address width supported by the processor. Generally, this value is 48 if CPUID.80000001H:EDX.LM [bit 29] = 1 and 32 otherwise. (Processors that do not support CPUID function 80000008H, support a linear-address width of 32.)

# 4.2 HIERARCHICAL PAGING STRUCTURES: AN OVERVIEW

All three paging modes translate linear addresses use **hierarchical paging structures**. This section provides an overview of their operation. Section 4.3, Section 4.4, and Section 4.5 provide details for the three paging modes.

Every paging structure is 4096 Bytes in size and comprises a number of individual **entries**. With 32-bit paging, each entry is 32 bits (4 bytes); there are thus 1024 entries in each structure. With PAE paging and IA-32e paging, each entry is 64 bits (8 bytes); there are thus 512 entries in each structure. (PAE paging includes one exception, a paging structure that is 32 bytes in size, containing 4 64-bit entries.)

The processor uses the upper portion of a linear address to identify a series of pagingstructure entries. The last of these entries identifies the physical address of the region to which the linear address translates (called the **page frame**). The lower portion of the linear address (called the **page offset**) identifies the specific address within that region to which the linear address translates.

Each paging-structure entry contains a physical address, which is either the address of another paging structure or the address of a page frame. In the first case, the entry is said to **reference** the other paging structure; in the latter, the entry is said to **map a page**.

The first paging structure used for any translation is located at the physical address in CR3. A linear address is translated using the following iterative procedure. A portion of the linear address (initially the uppermost bits) select an entry in a paging structure (initially the one located using CR3). If that entry references another paging structure, the process continues with that paging structure and with the portion of the linear address immediately below that just used. If instead the entry maps a page, the process completes: the physical address in the entry is that of the page frame and the remaining lower portion of the linear address is the page offset.

The following items give an example for each of the three paging modes (each example locates a 4-KByte page frame):

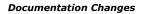

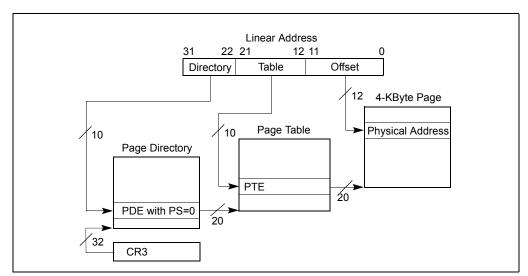

- With 32-bit paging, each paging structure comprises 1024 = 2<sup>10</sup> entries. For this reason, the translation process uses 10 bits at a time from a 32-bit linear address. Bits 31:22 identify the first paging-structure entry and bits 21:12 identify a second. The latter identifies the page frame. Bits 11:0 of the linear address are the page offset within the 4-KByte page frame. (See Figure 4-2 for an illustration.)

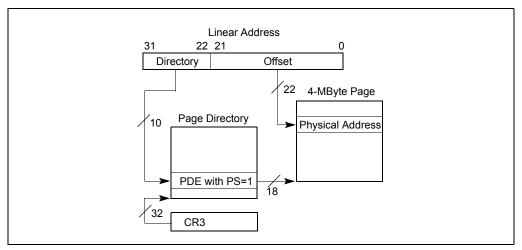

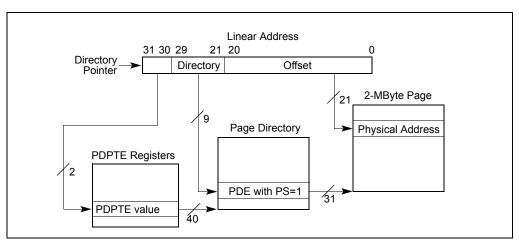

- With PAE paging, the first paging structure comprises only  $4 = 2^2$  entries. Translation thus begins by using bits 31:30 from a 32-bit linear address to identify the first paging-structure entry. Other paging structures comprise  $512 = 2^9$  entries, so the process continues by using 9 bits at a time. Bits 29:21 identify a second paging-structure entry and bits 20:12 identify a third. This last identifies the page frame. (See Figure 4-5 for an illustration.)

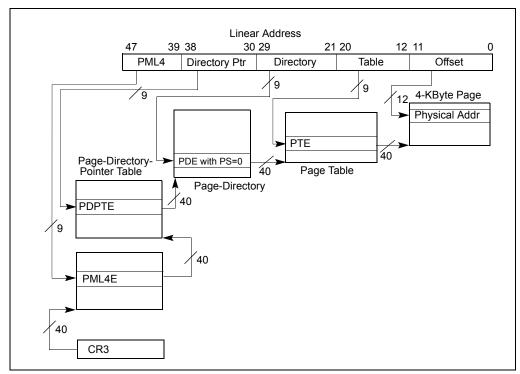

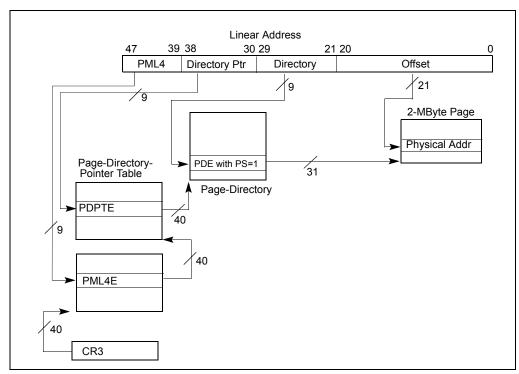

- With IA-32e paging, each paging structure comprises 512 = 2<sup>9</sup> entries and translation uses 9 bits at a time from a 48-bit linear address. Bits 47:39 identify the first paging-structure entry, bits 38:30 identify a second, bits 29:21 a third, and bits 20:12 identify a fourth. Again, the last identifies the page frame. (See Figure 4-8 for an illustration.)

The translation process in each of the examples above completes by identifying a page frame. However, the paging structures may be configured so that translation terminates before doing so. This occurs if process encounters a paging-structure entry that is marked "not present" (because its P flag — bit 0 — is clear) or in which a reserved bit is set. In this case, there is no translation for the linear address; an access to that address causes a page-fault exception (see Section 4.7).

In the examples above, a paging-structure entry maps a page with 4-KByte page frame when only 12 bits remain in the linear address; entries identified earlier always reference other paging structures. That may not apply in other cases. The following items identify when an entry maps a page and when it references another paging structure:

- If more than 12 bits remain in the linear address, bit 7 (PS page size) of the current paging-structure entry is consulted. If the bit is 0, the entry references another paging structure; if the bit is 1, the entry maps a page.

- If only 12 bits remain in the linear address, the current paging-structure entry always maps a page (bit 7 is used for other purposes).

If a paging-structure entry maps a page when more than 12 bits remain in the linear address, the entry identifies a page frame larger than 4 KBytes. For example, 32-bit paging uses the upper 10 bits of a linear address to locate the first paging-structure entry; 22 bits remain. If that entry maps a page, the page frame is  $2^{22}$  Bytes = 4 MBytes. 32-bit paging supports 4-MByte pages if CR4.PSE = 1. PAE paging and IA-32e paging support 2-MByte pages (regardless of the value of CR4.PSE).

Paging structures are given different names based their uses in the translation process. Table Table 4-2. gives the names of the different paging structures. It also provides, for each structure, the source of the physical address used to locate it (CR3 or a different paging-structure entry); the bits in the linear address used to select an entry from the structure; and details of about whether and how such an entry can map a page.

| Paging<br>Structure              | Entry<br>Name                    | Paging Mode | Physical<br>Address of<br>Structure | Bits<br>Selecting<br>Entry | Page Mapping                      |  |  |

|----------------------------------|----------------------------------|-------------|-------------------------------------|----------------------------|-----------------------------------|--|--|

| PML4 table                       | PML4 table PML4E 32-bit, PAE N/A |             |                                     |                            |                                   |  |  |

|                                  | FI'IL4C                          | IA-32e      | CR3                                 | 47:39                      | N/A (PS must be 0)                |  |  |

|                                  | 32-bit N/A                       |             |                                     |                            |                                   |  |  |

| Page-directory-<br>pointer table | PDPTE                            | PAE         | CR3                                 | 31:30                      | N/A (PS must be 0)                |  |  |

|                                  |                                  | IA-32e      | PML4E                               | 38:30                      | N/A (FS must be 0)                |  |  |

| Page directory                   | PDE                              | 32-bit      | CR3                                 | 31:22                      | 4-MByte page if PS=1 <sup>1</sup> |  |  |

| rage directory                   | FDL                              | PAE, IA-32e | PDPTE                               | 29:21                      | 2-MByte page if PS=1              |  |  |