# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

March 2010

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-027

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.  $I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Intel Core, Intel Xeon, Intel 64, Intel NetBurst, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002–2010, Intel Corporation. All rights reserved..

# Contents

| Revision History          | <br> |  | <br>• • |  | <br> | • |  |  |  |   |  |  | • | . 4 | 1 |

|---------------------------|------|--|---------|--|------|---|--|--|--|---|--|--|---|-----|---|

| Preface                   | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 7 | 7 |

| Summary Tables of Changes |      |  | <br>    |  | <br> | • |  |  |  | • |  |  | • | . 8 | 3 |

| Documentation Changes     | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 9 | ) |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                   | Date           |

|----------|-----------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul> | March 2010     |

§

**Revision History**

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                         | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture                | 253665                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M   | 253666                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z   | 253667                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1 | 253668                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2 | 253669                      |

## Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(B)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

## **Documentation Changes**

| ſ   | No. | DOCUMENTATION CHANGES            |

|-----|-----|----------------------------------|

| I [ | 1   | Updates to Chapter 2, Volume 1   |

|     | 2   | Updates to Chapter 12, Volume 1  |

| 1   | 3   | Updates to Appendix A, Volume 1  |

| 1   | 4   | Updates to Chapter 3, Volume 2A  |

|     | 5   | Updates to Chapter 4, Volume 2B  |

|     | 6   | Updates to Chapter 5, Volume 2B  |

|     | 7   | Updates to Appendix A, Volume 2B |

|     | 8   | Updates to Appendix B, Volume 2B |

|     | 9   | Updates to Appendix C, Volume 2B |

|     | 10  | Updates to Chapter 2, Volume 3A  |

|     | 11  | Updates to Chapter 4, Volume 3A  |

|     | 12  | Updates to Chapter 6, Volume 3A  |

|     | 13  | Updates to Chapter 10, Volume 3A |

|     | 14  | Updates to Chapter 11, Volume 3A |

|     | 15  | Updates to Chapter 22, Volume 3B |

|     | 16  | Updates to Chapter 23, Volume 3B |

| I [ | 17  | Updates to Chapter 24, Volume 3B |

| I [ | 18  | Updates to Chapter 25, Volume 3B |

| I [ | 19  | Updates to Chapter 26, Volume 3B |

|     | 20  | Updates to Chapter 27, Volume 3B |

|     | 21  | Updates to Chapter 30, Volume 3B |

|     | 22  | Updates to Appendix A, Volume 3B |

|     | 23  | Updates to Appendix B, Volume 3B |

|     | 24  | Updates to Appendix E, Volume 3B |

. . .

# **Documentation Changes**

#### 1. Updates to Chapter 2, Volume 1

Change bars show changes to Chapter 2 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

2.1.15 The Intel<sup>®</sup> Core<sup>™</sup>i7 Processor Family (2008-Current)

\_\_\_\_\_

The Intel Core i7 processor 900 series support Intel 64 architecture; they are based on Intel microarchitecture codename Nehalem using 45 nm process technology. The Intel Core i7 processor and Intel Xeon processor 5500 series include the following innovative features:

- Intel<sup>®</sup> Turbo Boost Technology converts thermal headroom into higher performance.

- Intel<sup>®</sup> HyperThreading Technology in conjunction with Quadcore to provide four cores and eight threads.

- Dedicated power control unit to reduce active and idle power consumption.

- Integrated memory controller on the processor supporting three channel of DDR3 memory.

- 8 MB inclusive Intel<sup>®</sup> Smart Cache.

- Intel<sup>®</sup> QuickPath interconnect (QPI) providing point-to-point link to chipset.

- Support for SSE4.2 and SSE4.1 instruction sets.

- Second generation Intel Virtualization Technology.

## 2.1.16 The Intel<sup>®</sup> Xeon<sup>®</sup> Processor 7500 Series (2010)

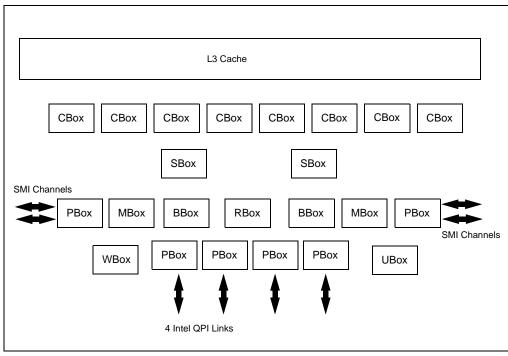

The Intel Xeon processor 7500 and 6500 series are based on Intel microarchitecture codename Nehalem using 45 nm process technology. They support the same features described in Section 2.1.15, plus the following innovative features:

- Up to eight cores per physical processor package.

- Up to 24 MB inclusive Intel<sup>®</sup> Smart Cache.

- Provides Intel<sup>®</sup> Scalable Memory Interconnect (Intel<sup>®</sup> SMI) channels with Intel<sup>®</sup> 7500 Scalable Memory Buffer to connect to system memory.

- Advanced RAS supporting software recoverable machine check architecture.

# 2.1.17 2010 Intel<sup>®</sup> Core<sup>™</sup> Processor Family (2010)

2010 Intel Core processor family spans Intel Core i7, i5 and i3 processors. They are based on Intel microarchitecture (Westmere) using 32 nm process technology. They provide the following innovative features:

• Deliver smart performance using Intel Hyper-Threading Technology plus Intel Turbo Boost Technology.

- Enhanced Intel Smart Cache and integrated memory controller.

- Intelligent power gating.

- Repartitioned platform with on-die integration of 45nm integrated graphics.

- Support for AESNI, PCLMULQDQ, SSE4.2 and SSE4.1 instruction sets.

# 2.1.18 The Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5600 Series (2010)

The Intel Xeon processor 5600 series are based on Intel microarchitecture (Westmere) using 32 nm process technology. They support the same features described in Section 2.1.15, plus the following innovative features:

- Up to six cores per physical processor package.

- Up to 12 MB enhanced Intel<sup>®</sup> Smart Cache.

- Support for AESNI, PCLMULQDQ, SSE4.2 and SSE4.1 instruction sets.

- Flexible Intel Virtualization Technologies across processor and I/O.

. . .

| Intel<br>Processor                                | Date<br>Intro-<br>duced | Micro-<br>architec-ture                                                                                                                                                                                           | Top-Bin<br>Fre-<br>quency<br>at Intro-<br>duction | Tran-<br>sistor<br>s | Register<br>Sizes                            | System<br>Bus/<br>QPI<br>Link<br>Speed  | Max.<br>Extern<br>. Addr.<br>Space | On-Die<br>Caches                   |

|---------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------|----------------------------------------------|-----------------------------------------|------------------------------------|------------------------------------|

|                                                   |                         |                                                                                                                                                                                                                   |                                                   |                      |                                              |                                         |                                    |                                    |

| Intel Core i7-965<br>Processor<br>Extreme Edition | 2008                    | Intel microarchitecture<br>codename Nehalem;<br>Quadcore;<br>Hyper Threading<br>Technology; Intel QPI;<br>Intel Virtualization<br>Technology.                                                                     | 3.20 GHz                                          | 731 M                | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | QPI: 6.4<br>GT/s;<br>Memory: 25<br>GB/s | 64 GB                              | L1: 64 KB<br>L2: 256KB<br>L3: 8MB  |

| Intel Core i7-<br>620M<br>Processor               | 2010                    | Intel Turbo Boost<br>Technology, Intel<br>microarchitecture<br>(Westmere);<br>Dualcore;<br>Hyper Threading<br>Technology; Intel 64<br>Architecture;<br>Intel Virtualization<br>Technology,<br>Integrated graphics | 2.66 GHz                                          | 383 M                | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 |                                         | 64 GB                              | L1: 64 KB<br>L2: 256KB<br>L3: 4MB  |

| Intel Xeon-<br>Processor 7560                     | 2010                    | Intel Turbo Boost<br>Technology, Intel<br>microarchitecture<br>codename Nehalem;<br>Eight core;<br>HyperThreading<br>Technology; Intel 64<br>Architecture;<br>Intel Virtualization<br>Technology.                 | 2.26 GHz                                          | 2.3B                 | GP: 32, 64<br>FPU: 80<br>MMX: 64<br>XMM: 128 | QPI: 6.4<br>GT/s;<br>Memory: 50<br>GB/s | 16 TB                              | L1: 64 KB<br>L2: 256KB<br>L3: 24MB |

#### Table 2-2 Key Features of Most Recent Intel 64 Processors

•••

#### 2. Updates to Chapter 12, Volume 1

Change bars show changes to Chapter 12 of the *Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1:* Basic Architecture.

# CHAPTER 12. PROGRAMMING WITH SSE3, SSSE3, SSE4 AND AESNI

The Pentium 4 processor supporting Hyper-Threading Technology (HT Technology) introduces Streaming SIMD Extensions 3 (SSE3). The Intel Xeon processor 5100 series, Intel Core 2 processor families introduced Supplemental Streaming SIMD Extensions 3 (SSSE3). SSE4 are introduced in Intel processor generations built from 45nm process technology. This chapter describes SSE3, SSSE3, SSE4, and provides information to assist in writing application programs that use these extensions.

AESNI and PCLMLQDQ are instruction extensions targeted to accelerate high-speed block encryption and cryptographic processing. Section 12.13 covers these instructions and their relationship to the Advanced Encryption Standard (AES).

. . .

## 12.13 AESNI OVERVIEW

The AESNI extension provides six instructions to accelerate symmetric block encryption/ decryption of 128-bit data blocks using the Advanced Encryption Standard (AES) specified by the NIST publication FIPS 197. Specifically, two instructions (AESENC, AESEN-CLAST) target the AES encryption rounds, two instructions (AESDEC, AESDECLAST) target AES decryption rounds using the Equivalent Inverse Cipher. One instruction (AESIMC) targets the Inverse MixColumn transformation primitive and one instruction (AESKEYGEN) targets generation of round keys from the cipher key for the AES encryption/decryption rounds.

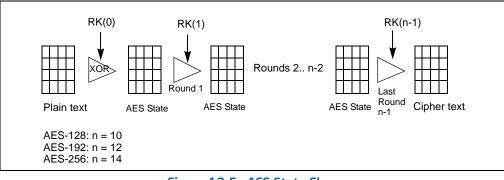

AES supports encryption/decryption using cipher key lengths of 128, 192, and 256 bits by processing the data block in 10, 12, 14 rounds of predefined transformations. Figure Figure 12-5 depicts the cryptographic processing of a block of 128-bit plain text into cipher text.

Figure 12-5 AES State Flow

The predefined AES transformation primitives are described in the next few sections, they are also referenced in the operation flow of instruction reference page of these instructions.

# 12.13.1 Little-Endian Architecture and Big-Endian Specification (FIPS 197)

FIPS 197 document defines the Advanced Encryption Standard (AES) and includes a set of test vectors for testing all of the steps in the algorithm, and can be used for testing and debugging.

The following observation is important for using the AES instructions offered in Intel 64 Architecture: FIPS 197 text convention is to write hex strings with the low-memory byte on the left and the high-memory byte on the right. Intel's convention is the reverse. It is similar to the difference between Big Endian and Little Endian notations.

In other words, a 128 bits vector in the FIPS document, when read from left to right, is encoded as [7:0, 15:8, 23:16, 31:24, ...127:120]. Note that inside the byte, the encoding is [7:0], so the first bit from the left is the most significant bit. In practice, the test vectors are written in hexadecimal notation, where pairs of hexadecimal digits define the different bytes. To translate the FIPS 197 notation to an Intel 64 architecture compatible ("Little Endian") format, each test vector needs to be byte-reflected to [127:120,... 31:24, 23:16, 15:8, 7:0].

Example A:

| FIPS Test vector:   | 0x000102030405060708090a0b0c0d0e0f |

|---------------------|------------------------------------|

| Intel AES Hardware: | 0x0f0e0d0c0b0a09080706050403020100 |

It should be pointed out that the only thing at issue is a textual convention, and programmers do not need to perform byte-reversal in their code, when using the AES instructions.

#### 12.13.1.1 AES Data Structure in Intel 64 Architecture

he AES instructions that are defined in this document operate on one or on two 128 bits source operands: State and Round Key. From the architectural point of view, the state is input in an xmm register and the Round key is input either in an xmm register or a 128-bit memory location.

In AES algorithm, the state (128 bits) can be viewed as 4 32-bit doublewords ("Word"s in AES terminology): X3, X2, X1, X0.

The state may also be viewed as a set of 16 bytes. The 16 bytes can also be viewed as a 4x4 matrix of bytes where S(i, j) with i, j = 0, 1, 2, 3 compose the 32-bit "word"s as follows:

XO = S(3, 0) S(2, 0) S(1, 0) S(0, 0)

X1 = S(3, 1) S(2, 1) S(1, 1) S(0, 1)

X2 = S(3, 2) S(2, 2) S(1, 2) S(0, 2)

X3 = S(3, 3) S(2, 3) S(1, 3) S(0, 3)

The following tables, Table Table 12-8 through Table Table 12-11, illustrate various representations of a 128-bit state.

| 10              | Table TE o byte and SE bit word hepresentation of a TEo bit State |                 |                 |                |           |           |           |           |           |           |           |           |           |           |          |          |

|-----------------|-------------------------------------------------------------------|-----------------|-----------------|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|

| Byte #          | 15                                                                | 14              | 13              | 12             | 11        | 10        | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1        | 0        |

| Bit<br>Position | 127<br>-<br>120                                                   | 119<br>-<br>112 | 111<br>-<br>103 | 103<br>-<br>96 | 95<br>-88 | 87<br>-80 | 79<br>-72 | 71<br>-64 | 63<br>-56 | 55<br>-48 | 47<br>-40 | 39<br>-32 | 31<br>-24 | 23<br>-16 | 15<br>-8 | 7 -<br>0 |

|                 |                                                                   | 127             | - 96            |                |           | 95        | - 64      |           |           | 64        | - 32      |           |           | 31        | 31 - 0   |          |

| State Word      |                                                                   | Х               | 3               |                | X2        |           |           | X1        |           |           |           | X0        |           |           |          |          |

| State Byte      | Р                                                                 | 0               | Ν               | М              | L         | K         | J         | Ι         | Н         | G         | F         | Е         | D         | С         | В        | А        |

#### Table 12-8 Byte and 32-bit Word Representation of a 128-bit State

#### Table 12-9 Matrix Representation of a 128-bit State

| А | Е | Ι | М | S(0, 0) | S(0, 1) | S(0, 2) | S(0, 3) |

|---|---|---|---|---------|---------|---------|---------|

| В | F | J | Ν | S(1, 0) | S(1, 1) | S(1, 2) | S(1, 3) |

| С | G | К | 0 | S(2, 0) | S(2, 1) | S(2, 2) | S(2, 3) |

| D | Н | L | Р | S(3, 0) | S(3, 1) | S(3, 2) | S(3, 3) |

Example:

FIPS vector: d4 bf 5d 30 e0 b4 52 ae b8 41 11 f1 1e 27 98 e5

This vector has the "least significant" byte d4 and the significant byte e5 (written in Big Endian format in the FIPS document). When it is translated to IA notations, the encoding is:

| Byte #      | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| State Byte  | Р  | 0  | N  | М  | L  | K  | J  | Ι  | Н  | G  | F  | Е  | D  | С  | В  | А  |

| State Value | e5 | 98 | 27 | 1e | f1 | 11 | 41 | b8 | ae | 52 | b4 | e0 | 30 | 5d | bf | d4 |

| Table 12-11 Little | Endian Re | presentation of | f a 4x4 B | yte Matrix |

|--------------------|-----------|-----------------|-----------|------------|

|--------------------|-----------|-----------------|-----------|------------|

| А | Е | Ι | М | d4 | e0 | b8 | 1e |

|---|---|---|---|----|----|----|----|

| В | F | J | Ν | bf | b4 | 41 | 27 |

| С | G | Κ | 0 | 5d | 52 | 11 | 98 |

| D | Н | L | Р | 30 | ae | f1 | e5 |

## 12.13.2 AES Transformations and Functions

The following functions and transformations are used in the algorithmic descriptions of AES instruction extensions AESDEC, AESDECLAST, AESENC, AESENCLAST, AESIMC, AESKEYGENASSIST.

Note that these transformations are expressed here in a Little Endian format (and not as in the FIPS 197 document).

• MixColumns(): A byte-oriented 4x4 matrix transformation on the matrix representation of a 128-bit AES state. A FIPS-197 defined 4x4 matrix is multiplied to each 4x1

column vector of the AES state. The columns are considered polynomials with coefficients in the Finite Field that is used in the definition of FIPS 197, the operations ("multiplication" and "addition") are in that Finite Field, and the polynomials are reduced modulo  $x^4$ +1.

The MixColumns() transformation defines the relationship between each byte of the result state, represented as S'(i, j) of a 4x4 matrix (see Section 12.13.1), as a function of input state bytes, S(i, j), as follows

$S'(0, j) \leftarrow FF_MUL(02H, S(0, j)) XOR FF_MUL(03H, S(1, j)) XOR S(2, j) XOR S(3, j)$

S'(1, j)  $\leftarrow$  S(0, j) XOR FF\_MUL( 02H, S(1, j) ) XOR FF\_MUL(03H, S(2, j) ) XOR S(3, j)

S'(2, j)  $\leftarrow$  S(0, j) XOR S(1, j) XOR FF\_MUL( 02H, S(2, j) ) XOR FF\_MUL(03H, S(3, j) )

S'(3, j) ← FF\_MUL(03H, S(0, j) ) XOR S(1, j) XOR S(2, j) XOR FF\_MUL(02H, S(3, j) )

where j = 0, 1, 2, 3. FF\_MUL(Byte1, Byte2) denotes the result of multiplying two elements (represented by Byte1 and byte2) in the Finite Field representation that defines AES. The result of produced bye FF\_MUL(Byte1, Byte2) is an element in the Finite Field (represented as a byte). A Finite Field is a field with a finite number of elements, and when this number can be represented as a power of 2 (2n), its elements can be represented as the set of 2n binary strings of length n. AES uses a finite field with n=8 (having 256 elements). With this representation, "addition" of two elements in that field is a bit-wise XOR of their binary-string representation, producing another element in the field. Multiplication of two elements in that field is defined using an irreducible polynomial (for AES, this polynomial is  $m(x) = x^{\beta} + x^{4}$  $+ x^{3} + x + 1$ ). In this Finite Field representation, the bit value of bit position k of a byte represents the coefficient of a polynomial of order k, e.g., 1010\_1101B (ADH) is represented by the polynomial  $(x^7 + x^5 + x^3 + x^2 + 1)$ . The byte value result of multiplication of two elements is obtained by a carry-less multiplication of the two corresponding polynomials, followed by reduction modulo the polynomial, where the remainder is calculated using operations defined in the field. For example, FF\_MUL(57H, 83H) = C1H, because the carry-less polynomial multiplication of the polynomials represented by 57H and 83H produces  $(x^{13} + x^{11} + x^9 + x^8 + x^6 + x^5)$  $+ x^{4} + x^{3} + 1$ ), and the remainder modulo m(x) is  $(x^{7} + x^{6} + 1)$ .

• RotWord(): performs a byte-wise cyclic permutation (rotate right in little-endian byte order) on a 32-bit AES word.

The output word X'[j] of RotWord(X[j]) where X[j] represent the four bytes of column j, S(i, j), in descending order X[j] = (S(3, j), S(2, j), S(1, j), S(0, j)); X'[j] = (S'(3, j), S'(2, j), S'(1, j), S'(0, j)) \leftarrow (S(0, j), S(3, j), S(2, j), S(1, j))

• ShiftRows(): A byte-oriented matrix transformation that processes the matrix representation of a 16-byte AES state by cyclically shifting the last three rows of the state by different offset to the left, see Table 12-12.

| Matrix | Representa | tion of Inp | ut State | Output of ShiftRows |   |   |   |  |  |  |

|--------|------------|-------------|----------|---------------------|---|---|---|--|--|--|

| А      | Е          | Ι           | М        | А                   | Е | Ι | М |  |  |  |

| В      | F          | J           | Ν        | F                   | J | Ν | В |  |  |  |

| С      | G          | K           | 0        | К                   | 0 | С | G |  |  |  |

| D      | Н          | L           | Р        | Р                   | D | Н | L |  |  |  |

Table 12-12 The ShiftRows Transformation

• SubBytes(): A byte-oriented transformation that processes the 128-bit AES state by applying a non-linear substitution table (S-BOX) on each byte of the state.

The SubBytes() function defines the relationship between each byte of the result state S'(i, j) as a function of input state byte S(i, j), by

$S'(i, j) \leftarrow S$ -Box (S(i, j)[7:4], S(i, j)[3:0])

where S-BOX(S[7:4], S[3:0]) represents a look-up operation on a 16x16 table to return a byte value, see Table 12-13.

|        |   |    | S[3:0] |    |    |    |    |    |           |    |    |            |    |    |    |           |           |

|--------|---|----|--------|----|----|----|----|----|-----------|----|----|------------|----|----|----|-----------|-----------|

|        |   | 0  | 1      | 2  | 3  | 4  | 5  | 6  | 7         | 8  | 9  | а          | b  | с  | d  | e         | f         |

|        | 0 | 63 | 7c     | 77 | 7b | f2 | 6b | 6f | c5        | 30 | 01 | 67         | 2b | fe | d7 | ab        | 76        |

|        | 1 | ca | 82     | c9 | 7d | fa | 59 | 47 | f0        | ad | d4 | a2         | af | 9c | a4 | 72        | <b>c0</b> |

|        | 2 | b7 | fd     | 93 | 26 | 36 | 3f | f7 | cc        | 34 | a5 | e5         | f1 | 71 | d8 | 31        | 15        |

|        | 3 | 04 | c7     | 23 | c3 | 18 | 96 | 05 | 9a        | 07 | 12 | 80         | e2 | eb | 27 | b2        | 75        |

|        | 4 | 09 | 83     | 2c | 1a | 1b | 6e | 5a | a0        | 52 | 3b | <b>d</b> 6 | b3 | 29 | e3 | <b>2f</b> | 84        |

|        | 5 | 53 | d1     | 00 | ed | 20 | fc | b1 | 5b        | 6a | cb | be         | 39 | 4a | 4c | 58        | cf        |

|        | 6 | d0 | ef     | aa | fb | 43 | 4d | 33 | 85        | 45 | f9 | 02         | 7f | 50 | 3c | 9f        | a8        |

| 0[7,4] | 7 | 51 | a3     | 40 | 8f | 92 | 9d | 38 | f5        | bc | b6 | da         | 21 | 10 | ff | f3        | d2        |

| S[7:4] | 8 | cd | 0c     | 13 | ec | 5f | 97 | 44 | 17        | c4 | a7 | 7e         | 3d | 64 | 5d | 19        | 73        |

|        | 9 | 60 | 81     | 4f | dc | 22 | 2a | 90 | 88        | 46 | ee | <b>b8</b>  | 14 | de | 5e | 0b        | db        |

|        | а | e0 | 32     | 3a | 0a | 49 | 06 | 24 | 5c        | c2 | d3 | ac         | 62 | 91 | 95 | e4        | 79        |

|        | b | e7 | c8     | 37 | 6d | 8d | d5 | 4e | a9        | 6c | 56 | f4         | ea | 65 | 7a | ae        | 08        |

|        | с | ba | 78     | 25 | 2e | 1c | a6 | b4 | <b>c6</b> | e8 | dd | 74         | 1f | 4b | bd | 8b        | 8a        |

|        | d | 70 | 3e     | b5 | 66 | 48 | 03 | f6 | 0e        | 61 | 35 | 57         | b9 | 86 | c1 | 1d        | 9e        |

|        | e | e1 | f8     | 98 | 11 | 69 | d9 | 8e | 94        | 9b | 1e | 87         | e9 | ce | 55 | 28        | df        |

|        | f | 8c | a1     | 89 | 0d | bf | e6 | 42 | 68        | 41 | 99 | 2d         | 0f | b0 | 54 | bb        | 16        |

Table 12-13 Look-up Table Associated with S-Box Transformation

• SubWord(): produces an output AES word (four bytes) from the four bytes of an input word using a non-linear substitution table (S-BOX).

$X'[j] = (S'(3, j), S'(2, j), S'(1, j), S'(0, j)) \leftarrow (S-Box(S(3, j)), S-Box(S(2, j)), S-Box(S(1, j)), S-Box(S(0, j)))$

- InvMixColumns(): The inverse transformation of MixColumns().

- The InvMixColumns() transformation defines the relationship between each byte of the result state S'(i, j) as a function of input state bytes, S(i, j), by

$S'(0, j) \leftarrow FF\_MUL( 0eH, S(0, j) ) XOR FF\_MUL(0bH, S(1, j) ) XOR FF\_MUL(0dH, S(2, j) ) XOR FF\_MUL( 09H, S(3, j) )$

S'(1, j)  $\leftarrow$  FF\_MUL(09H, S(0, j) ) XOR FF\_MUL( 0eH, S(1, j) ) XOR FF\_MUL(0bH, S(2, j) ) XOR FF\_MUL( 0dH, S(3, j) )

$$\begin{split} & S'(2, j) \leftarrow FF\_MUL(0dH, S(0, j) ) \text{ XOR FF}\_MUL( 09H, S(1, j) ) \text{ XOR FF}\_MUL( 0eH, S(2, j) ) \text{ XOR FF}\_MUL(0bH, S(3, j) ) \end{split}$$

$S'(3, j) \leftarrow FF_MUL(0bH, S(0, j)) XOR FF_MUL(0dH, S(1, j)) XOR FF_MUL(09H, S(2, j)) XOR FF_MUL(0eH, S(3, j)), where j = 0, 1, 2, 3.$

• InvShiftRows(): The inverse transformation of InvShiftRows(). The InvShiftRows() transforms the matrix representation of a 16-byte AES state by cyclically shifting the last three rows of the state by different offset to the right, see Table 12-14.

| Matrix | Representa | tion of Inp | ut State | Output of ShiftRows |   |   |   |  |  |  |

|--------|------------|-------------|----------|---------------------|---|---|---|--|--|--|

| А      | Е          | Ι           | М        | А                   | Е | Ι | М |  |  |  |

| В      | F          | J           | Ν        | Ν                   | В | F | J |  |  |  |

| С      | G          | K           | 0        | K                   | 0 | С | G |  |  |  |

| D      | Н          | L           | Р        | Н                   | L | Р | D |  |  |  |

Table 12-14 The InvShiftRows Transformation

• InvSubBytes(): The inverse transformation of SubBytes().

The InvSubBytes() transformation defines the relationship between each byte of the result state S'(i, j) as a function of input state byte S(i, j), by

$S'(i, j) \leftarrow InvS-Box (S(i, j)[7:4], S(i, j)[3:0])$

where InvS-BOX(S[7:4], S[3:0]) represents a look-up operation on a 16x16 table to return a byte value, see Table 12-15.

|        |   |    | S[3:0] |            |    |    |    |            |    |    |    |    |    |           |    |    |            |

|--------|---|----|--------|------------|----|----|----|------------|----|----|----|----|----|-----------|----|----|------------|

|        |   | 0  | 1      | 2          | 3  | 4  | 5  | 6          | 7  | 8  | 9  | а  | b  | c         | d  | e  | f          |

|        | 0 | 52 | 09     | 6a         | d5 | 30 | 36 | a5         | 38 | bf | 40 | a3 | 9e | 81        | f3 | d7 | fb         |

|        | 1 | 7c | e3     | 39         | 82 | 9b | 2f | ff         | 87 | 34 | 8e | 43 | 44 | c4        | de | e9 | cb         |

|        | 2 | 54 | 7b     | 94         | 32 | a6 | c2 | 23         | 3d | ee | 4c | 95 | 0b | 42        | fa | c3 | <b>4</b> e |

|        | 3 | 08 | 2e     | a1         | 66 | 28 | d9 | 24         | b2 | 76 | 5b | a2 | 49 | 6d        | 8b | d1 | 25         |

|        | 4 | 72 | f8     | f6         | 64 | 86 | 68 | 98         | 16 | d4 | a4 | 5c | сс | 5d        | 65 | b6 | 92         |

|        | 5 | 6c | 70     | 48         | 50 | fd | ed | b9         | da | 5e | 15 | 46 | 57 | a7        | 8d | 9d | 84         |

|        | 6 | 90 | d8     | ab         | 00 | 8c | bc | d3         | 0a | f7 | e4 | 58 | 05 | <b>b8</b> | b3 | 45 | 06         |

| ST7.41 | 7 | d0 | 2c     | 1e         | 8f | ca | 3f | 0f         | 02 | c1 | af | bd | 03 | 01        | 13 | 8a | 6b         |

| S[7:4] | 8 | 3a | 91     | 11         | 41 | 4f | 67 | dc         | ea | 97 | f2 | cf | ce | fO        | b4 | e6 | 73         |

|        | 9 | 96 | ac     | 74         | 22 | e7 | ad | 35         | 85 | e2 | f9 | 37 | e8 | 1c        | 75 | df | 6e         |

|        | а | 47 | f1     | <b>1</b> a | 71 | 1d | 29 | c5         | 89 | 6f | b7 | 62 | 0e | aa        | 18 | be | 1b         |

|        | b | fc | 56     | 3e         | 4b | c6 | d2 | 79         | 20 | 9a | db | c0 | fe | 78        | cd | 5a | f4         |

|        | с | 1f | dd     | a8         | 33 | 88 | 07 | c7         | 31 | b1 | 12 | 10 | 59 | 27        | 80 | ec | 5f         |

|        | d | 60 | 51     | 7f         | a9 | 19 | b5 | 4a         | 0d | 2d | e5 | 7a | 9f | 93        | c9 | 9c | ef         |

|        | e | a0 | eO     | 3b         | 4d | ae | 2a | f5         | b0 | c8 | eb | bb | 3c | 83        | 53 | 99 | 61         |

|        | f | 17 | 2b     | 04         | 7e | ba | 77 | <b>d</b> 6 | 26 | e1 | 69 | 14 | 63 | 55        | 21 | 0c | 7d         |

#### Table 12-15 Look-up Table Associated with InvS-Box Transformation

## 12.13.3 PCLMULQDQ

The PCLMULQDQ instruction performs carry-less multiplication of two 64-bit data into a 128-bit result. Carry-less multiplication of two 128-bit data into a 256-bit result can use PCLMULQDQ as building blocks.

Carry-less multiplication is a component of many cryptographic systems. It is an important piece of implementing Galois Counter Mode (GCM) operation of block ciphers. GCM operation can be used in conjunction with AES algorithms to add authentication capability. GCM usage models also include IPsec, storage standard, and security protocols over fiber channel. Additionally, PCLMULQDQ can be used in calculations of hash functions and CRC using arbitrary polynomials.

#### 12.13.4 Checking for AESNI Support

Before an application attempts to use AESNI instructions or PCLMULQDQ, the application should follow the steps illustrated in Section 11.6.2, "Checking for SSE/SSE2 Support." Next, use the additional step provided below:

Check that the processor supports AESNI (if CPUID.01H: ECX.AESNI[bit 25] = 1); Check that the processor supports PCLMULQDQ (if CPUID.01H: ECX.PCLMULQDQ[bit 1] = 1)

#### . . .

. . .

#### 3. Updates to Appendix A, Volume 1

Change bars show changes to Appendix A of the *Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1:* Basic Architecture.

|                |    | 10 |    | -2 L |    | 5 010 | 33-IV | elele | nce |    |    |

|----------------|----|----|----|------|----|-------|-------|-------|-----|----|----|

| Instruction    | OF | SF | ZF | AF   | PF | CF    | TF    | IF    | DF  | NT | RF |

|                |    |    |    |      |    |       |       |       |     |    |    |

| BT/BTS/BTR/BTC | —  | -  |    | —    | -  | М     |       |       |     |    |    |

|                |    |    |    |      |    |       |       |       |     |    |    |

#### Table A-2 EFLAGS Cross-Reference

• • •

#### 4. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

CHAPTER 3 INSTRUCTION SET REFERENCE, A-M

This chapter describes the instruction set for the Intel 64 and IA-32 architectures (A-M) in IA-32e, protected, Virtual-8086, and real modes of operation. The set includes general-purpose, x87 FPU, MMX, SSE/SSE2/SSE3/SSE3/SSE4, AESNI/PCLMULQDQ, and system instructions. See also Chapter 4, "Instruction Set Reference, N-Z," in the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B.*

...

#### AESDEC—Perform One Round of an AES Decryption Flow

| Opcode         | Instruction               | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                                 |

|----------------|---------------------------|-----------|----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 38 DE /r | AESDEC xmm1,<br>xmm2/m128 | A         | Valid          | Valid               | Perform one round of an<br>AES decryption flow, using<br>the Equivalent Inverse<br>Cipher, operating on a 128-<br>bit data (state) from xmm1<br>with a 128-bit round key<br>from xmm2/m128. |

| Instruction Operand Encoding |                  |               |          |          |  |  |  |  |

|------------------------------|------------------|---------------|----------|----------|--|--|--|--|

| Op/En                        | Operand 1        | Operand2      | Operand3 | Operand4 |  |  |  |  |

| А                            | ModRM:reg (r, w) | ModRM:r/m (r) | NA       | NA       |  |  |  |  |

#### Description

This instruction performs a single round of the AES decryption flow using the Equivalent Inverse Cipher, with the round key from the second source operand, operating on a 128bit data (state) from the first source operand, and store the result in the destination operand.

Use the AESDEC instruction for all but the last decryption round. For the last decryption round, use the AESDECCLAST instruction.

The first source operand and the destination operand are the same and must be an XMM register. The second source operand can be an XMM register or a 128-bit memory location.

#### Operation

AESDEC STATE  $\leftarrow$  SRC1; RoundKey  $\leftarrow$  SRC2;

STATE ← InvShiftRows( STATE ); STATE ← InvSubBytes( STATE ); STATE ← InvMixColumns( STATE ); DEST[127:0] ← STATE XOR RoundKey; DEST[255:128] (Unmodified)

#### Intel C/C++ Compiler Intrinsic Equivalent

AESDEC \_\_m128i \_mm\_aesdec (\_\_m128i, \_\_m128i)

#### SIMD Floating-Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|-----------------|---------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #SS(0)          | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                                                                     |

| #NM             | If CR0.TS[bit 3] = 1.                                                                 |

| #UD             | If $CRO.EM[bit 2] = 1$ .                                                              |

|                 | If CR4.OSFXSR[bit 9] = 0.                                                             |

|                 | If CPUID.01H: ECX.AESNI[bit 25] = 0.                                                  |

|                 | If the LOCK prefix is used.                                                           |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

|-----|---------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH.  |

| #NM | If CR0.TS[bit 3] = 1.                                                                 |

| #UD | If CR0.EM[bit 2] = 1.                                                                 |

|     | If CR4.OSFXSR[bit 9] = 0.                                                             |

|     | If CPUID.01H: ECX.AESNI[bit $25$ ] = 0.                                               |

|     | If the LOCK prefix is used.                                                           |

|     |                                                                                       |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### **64-Bit Mode Exceptions**

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM             | If CR0.TS[bit 3] = 1.                                                               |

| #UD             | If CR0.EM[bit 2] = 1.                                                               |

|                 | If $CR4.OSFXSR[bit 9] = 0.$                                                         |

|                 | If CPUID.01H: ECX.AESNI[bit 25] = 0.                                                |

|                 | If the LOCK prefix is used.                                                         |

#### AESDECLAST—Perform Last Round of an AES Decryption Flow

| Opcode         | Instruction                      | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                                      |

|----------------|----------------------------------|-----------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 0F 38 DF /r | AESDECLAST<br>xmm1,<br>xmm2/m128 | A         | Valid          | Valid               | Perform the last round of an<br>AES decryption flow, using<br>the Equivalent Inverse<br>Cipher, operating on a 128-<br>bit data (state) from xmm1<br>with a 128-bit round key<br>from xmm2/m128. |

| Instruction Operand Encoding |                                                                            |               |    |    |  |  |

|------------------------------|----------------------------------------------------------------------------|---------------|----|----|--|--|

| Op/En                        | Op/En         Operand 1         Operand2         Operand3         Operand4 |               |    |    |  |  |

| Α                            | ModRM:reg (r, w)                                                           | ModRM:r/m (r) | NA | NA |  |  |

#### Description

This instruction performs the last round of the AES decryption flow using the Equivalent Inverse Cipher, with the round key from the second source operand, operating on a 128bit data (state) from the first source operand, and store the result in the destination operand.

The first source operand and the destination operand are the same and must be an XMM register. The second source operand can be an XMM register or a 128-bit memory location.

#### Operation

AESDECLAST STATE ← SRC1; RoundKey ← SRC2; STATE ← InvShiftRows(STATE); STATE ← InvSubBytes(STATE); DEST[127:0] ← STATE XOR RoundKey; DEST[255:128] (Unmodified)

#### Intel C/C++ Compiler Intrinsic Equivalent

AESDECLAST \_\_m128i \_mm\_aesdeclast (\_\_m128i, \_\_m128i)

#### SIMD Floating-Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|-----------------|---------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #SS(0)          | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                                                                     |

| #NM             | If CR0.TS[bit 3] = 1.                                                                 |

| #UD             | If CR0.EM[bit 2] = 1.                                                                 |

|                 | If $CR4.OSFXSR[bit 9] = 0.$                                                           |

|                 | If CPUID.01H: ECX.AESNI[bit $25$ ] = 0.                                               |

|                 | If the LOCK prefix is used.                                                           |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

|-----|---------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH.  |

| #NM | If CR0.TS[bit 3] = 1.                                                                 |

| #UD | If CR0.EM[bit 2] = 1.                                                                 |

|     | If CR4.OSFXSR[bit 9] = 0.                                                             |

|     | If CPUID.01H: ECX.AESNI [bit $25$ ] = 0.                                              |

|     | If the LOCK prefix is used.                                                           |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### 64-Bit Mode Exceptions

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM | If CR0.TS[bit 3] = 1.              |

|-----|------------------------------------|

| #UD | If CRO.EM[bit 2] = 1.              |

|     | If CR4.OSFXSR[bit 9] = 0.          |

|     | If CPUID.01H:ECX.AESNI[bit 25] = 0 |

|     | If the LOCK prefix is used.        |

#### AESENC—Perform One Round of an AES Encryption Flow

| Opcode         | Instruction               | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                          |

|----------------|---------------------------|-----------|----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 38 DC /r | AESENC xmm1,<br>xmm2/m128 | A         | Valid          | Valid               | Perform one round of an<br>AES encryption flow, operat-<br>ing on a 128-bit data (state)<br>from xmm1 with a 128-bit<br>round key from<br>xmm2/m128. |

| Instruction Operand Encoding |                  |               |          |          |  |  |

|------------------------------|------------------|---------------|----------|----------|--|--|

| Op/En                        | Operand 1        | Operand2      | Operand3 | Operand4 |  |  |

| А                            | ModRM:reg (r, w) | ModRM:r/m (r) | NA       | NA       |  |  |

#### Description

This instruction performs a single round of an AES encryption flow using a round key from the second source operand, operating on 128-bit data (state) from the first source operand, and store the result in the destination operand.

Use the AESENC instruction for all but the last encryption rounds. For the last encryption round, use the AESENCCLAST instruction.

The first source operand and the destination operand are the same and must be an XMM register. The second source operand can be an XMM register or a 128-bit memory location.

#### Operation

AESENC STATE  $\leftarrow$  SRC1; RoundKey  $\leftarrow$  SRC2; STATE  $\leftarrow$  ShiftRows( STATE ); STATE  $\leftarrow$  SubBytes( STATE ); STATE  $\leftarrow$  MixColumns( STATE ); DEST[127:0]  $\leftarrow$  STATE XOR RoundKey; DEST[255:128] (Unmodified)

#### Intel C/C++ Compiler Intrinsic Equivalent

AESENC \_\_m128i \_mm\_aesenc (\_\_m128i, \_\_m128i)

#### SIMD Floating-Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|-----------------|---------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #SS(0)          | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                                                                     |

| #NM             | If CR0.TS[bit 3] = 1.                                                                 |

| #UD             | If CR0.EM[bit 2] = 1.                                                                 |

|                 | If $CR4.OSFXSR[bit 9] = 0.$                                                           |

|                 | If CPUID.01H: ECX.AESNI[bit 25] = 0.                                                  |

|                 | If the LOCK prefix is used.                                                           |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

|-----|---------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH.  |

| #NM | If CR0.TS[bit 3] = 1.                                                                 |

| #UD | If CR0.EM[bit 2] = 1.                                                                 |

|     | If CR4.OSFXSR[bit 9] = 0.                                                             |

|     | If CPUID.01H: ECX.AESNI[bit $25$ ] = 0.                                               |

|     | If the LOCK prefix is used.                                                           |

|     |                                                                                       |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### 64-Bit Mode Exceptions

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM             | If CR0.TS[bit 3] = 1.                                                               |

| #UD             | If CR0.EM[bit 2] = 1.                                                               |

|                 | If CR4.OSFXSR[bit 9] = 0.                                                           |

|                 | If CPUID.01H: ECX.AESNI[bit 25] = 0.                                                |

#### If the LOCK prefix is used.

#### **AESENCLAST—Perform Last Round of an AES Encryption Flow**

| Opcode         | Instruction                      | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                               |

|----------------|----------------------------------|-----------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 0F 38 DD /r | AESENCLAST<br>xmm1,<br>xmm2/m128 | A         | Valid          | Valid               | Perform the last round of an<br>AES encryption flow, operat-<br>ing on a 128-bit data (state)<br>from xmm1 with a 128-bit<br>round key from<br>xmm2/m128. |

| Instruction Operand Encoding |                                                                            |               |    |    |  |  |

|------------------------------|----------------------------------------------------------------------------|---------------|----|----|--|--|

| Op/En                        | Op/En         Operand 1         Operand2         Operand3         Operand4 |               |    |    |  |  |

| А                            | ModRM:reg (r, w)                                                           | ModRM:r/m (r) | NA | NA |  |  |

#### Description

This instruction performs the last round of an AES encryption flow using a round key from the second source operand, operating on 128-bit data (state) from the first source operand, and store the result in the destination operand.

The first source operand and the destination operand are the same and must be an XMM register. The second source operand can be an XMM register or a 128-bit memory location.

#### Operation

AESENCLAST STATE ← SRC1; RoundKey ← SRC2; STATE ← ShiftRows(STATE); STATE ← SubBytes(STATE); DEST[127:0] ← STATE XOR RoundKey; DEST[255:128] (Unmodified)

#### Intel C/C++ Compiler Intrinsic Equivalent

AESENCLAST \_\_m128i \_mm\_aesenclast (\_\_m128i, \_\_m128i)

#### SIMD Floating-Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0) | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|--------|---------------------------------------------------------------------------------------|

|        | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #SS(0) | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                       |

|-----------------|-----------------------------------------|

| #NM             | If CR0.TS[bit 3] = 1.                   |

| #UD             | If CR0.EM[bit 2] = 1.                   |

|                 | If CR4.OSFXSR[bit 9] = 0.               |

|                 | If CPUID.01H: ECX.AESNI[bit $25$ ] = 0. |

|                 | If the LOCK prefix is used.             |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

|-----|---------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH.  |

| #NM | If CR0.TS[bit 3] = 1.                                                                 |

| #UD | If CR0.EM[bit 2] = 1.                                                                 |

|     | If CR4.OSFXSR[bit 9] = 0.                                                             |

|     | If CPUID.01H: ECX.AESNI [bit $25$ ] = 0.                                              |

|     | If the LOCK prefix is used.                                                           |

|     |                                                                                       |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### 64-Bit Mode Exceptions

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM             | If CR0.TS[bit 3] = 1.                                                               |

| #UD             | If CRO.EM[bit 2] = 1.                                                               |

|                 | If CR4.OSFXSR[bit 9] = 0.                                                           |

|                 | If CPUID.01H: ECX.AESNI[bit 25] = 0.                                                |

|                 | If the LOCK prefix is used.                                                         |

|                 |                                                                                     |

#### AESIMC- Perform the AES InvMixColumn Transformation

| Opcode         | Instruction               | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                             |

|----------------|---------------------------|-----------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| 66 OF 38 DB /r | AESIMC xmm1,<br>xmm2/m128 | A         | Valid          | Valid               | Perform the InvMixColumn<br>transformation on a 128-bit<br>round key from<br>xmm2/m128 and store the<br>result in xmm1. |

| _     |               | Instruction Operand | Encoding |          |

|-------|---------------|---------------------|----------|----------|

| Op/En | Operand 1     | Operand2            | Operand3 | Operand4 |

| А     | ModRM:reg (w) | ModRM:r/m (r)       | NA       | NA       |

#### Description

Perform the InvMixColumns transformation on the source operand and store the result in the destination operand. The destination operand is an XMM register. The source operand can be an XMM register or a 128-bit memory location.

Note the AESIMC instruction should be applied to the expanded AES round keys (except for the first and last round key) in order to prepare them for decryption using the "Equivalent Inverse Cipher" (defined in FIPS 197).

#### Operation

DEST[127:0]  $\leftarrow$  InvMixColumns( SRC ); DEST[255:128] (Unmodified)

#### Intel C/C++ Compiler Intrinsic Equivalent

AESIMC \_\_m128i \_mm\_aesimc (\_\_m128i)

#### SIMD Floating-Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0)          | For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. |

|-----------------|---------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #SS(0)          | For an illegal address in the SS segment.                                             |

| #PF(fault-code) | For a page fault.                                                                     |

| #NM             | If CR0.TS[bit 3] = 1.                                                                 |

| #UD             | If CR0.EM[bit 2] = 1.                                                                 |

|                 | If CR4.OSFXSR[bit 9] = 0.                                                             |

|                 | If CPUID.01H: ECX.AESNI [bit $25$ ] = 0.                                              |

|                 | If the LOCK prefix is used.                                                           |

|                 |                                                                                       |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

|-----|---------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH.  |

| #NM | If CR0.TS[bit 3] = 1.                                                                 |

| #UD | If CR0.EM[bit 2] = 1.                                                                 |

|     | If CR4.OSFXSR[bit 9] = 0.                                                             |

|     | If CPUID.01H: ECX.AESNI [bit $25$ ] = 0.                                              |

|     | If the LOCK prefix is used.                                                           |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### Compatibility Mode Exceptions

Same exceptions as in protected mode.

#### 64-Bit Mode Exceptions

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM             | If CR0.TS[bit 3] = 1.                                                               |

| #UD             | If CR0.EM[bit 2] = 1.                                                               |

|                 | If $CR4.OSFXSR[bit 9] = 0.$                                                         |

|                 | If CPUID.01H: ECX.AESNI [bit $25$ ] = 0.                                            |

|                 | If the LOCK prefix is used.                                                         |

#### **AESKEYGENASSIST - AES Round Key Generation Assist**

| Opcode               | Instruction                                      | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                                                          |

|----------------------|--------------------------------------------------|-----------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A DF /r<br>ib | AESKEYGENAS-<br>SIST xmm1,<br>xmm2/m128,<br>imm8 | A         | Valid          | Valid               | Assist in AES round key gen-<br>eration using an 8 bits<br>Round Constant (RCON)<br>specified in the immediate<br>byte, operating on 128 bits<br>of data specified in<br>xmm2/m128 and stores the<br>result in xmm1. |

|       |               | Instruction Operand | Encoding |          |

|-------|---------------|---------------------|----------|----------|

| Op/En | Operand 1     | Operand2            | Operand3 | Operand4 |

| Α     | ModRM:reg (w) | ModRM:r/m (r)       | imm8     | NA       |

#### Description

Assist in expanding the AES cipher key, by computing steps towards generating a round key for encryption, using 128-bit data specified in the source operand and an 8-bit round constant specified as an immediate, store the result in the destination operand.

The destination operand is an XMM register. The source operand can be an XMM register or a 128-bit memory location.

#### Operation

X3[31:0]  $\leftarrow$  SRC [127: 96]; X2[31:0]  $\leftarrow$  SRC [95: 64]; X1[31:0]  $\leftarrow$  SRC [63: 32]; X0[31:0]  $\leftarrow$  SRC [31: 0]; RCON[31:0]  $\leftarrow$  ZeroExtend(Imm8[7:0]); DEST[31:0]  $\leftarrow$  SubWord(X1); DEST[63:32]  $\leftarrow$  RotWord(SubWord(X1)) XOR RCON; DEST[95:64]  $\leftarrow$  SubWord(X3); DEST[127:96]  $\leftarrow$  RotWord(SubWord(X3)) XOR RCON; DEST[255:128] (Unmodified)

Intel C/C++ Compiler Intrinsic Equivalent

AESKEYGENASSIST \_\_m128i \_mm\_aesimc (\_\_m128i, const int)

#### SIMD Floating-Point Exceptions

None

#### Protected Mode Exceptions

#GP(0)

For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments. If a memory operand is not aligned on a 16-byte boundary, regardless of segment.

| For an illegal address in the SS segment.                                            |

|--------------------------------------------------------------------------------------|

| For a page fault.                                                                    |

| If CR0.TS[bit 3] = 1.                                                                |

| If CR0.EM[bit 2] = 1.                                                                |

| If CR4.OSFXSR[bit 9] = 0.                                                            |

| If CPUID.01H:ECX.AESNI[bit 25] = 0.                                                  |

| If the LOCK prefix is used.                                                          |

| Exceptions                                                                           |

| If a memory operand is not aligned on a 16-byte boundary, regard-less of segment.    |

| If any part of the operand lies outside the effective address space from 0 to FFFFH. |

| If CR0.TS[bit 3] = 1.                                                                |

| If CR0.EM[bit 2] = 1.                                                                |

| If CR4.OSFXSR[bit 9] = 0.                                                            |

| If CPUID.01H:ECX.AESNI[bit 25] = 0.                                                  |

| If the LOCK prefix is used.                                                          |

|                                                                                      |

#### Virtual-8086 Mode Exceptions

Same exceptions as in real address mode. #PF(fault-code) For a page fault.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### 64-Bit Mode Exceptions

| #SS(0)          | If a memory address referencing the SS segment is in a non-canon-<br>ical form.     |

|-----------------|-------------------------------------------------------------------------------------|

| #GP(0)          | If the memory address is in a non-canonical form.                                   |

|                 | If memory operand is not aligned on a 16-byte boundary, regard-<br>less of segment. |

| #PF(fault-code) | For a page fault.                                                                   |

| #NM             | If CR0.TS[bit 3] = 1.                                                               |

| #UD             | If CR0.EM[bit 2] = 1.                                                               |

|                 | If CR4.OSFXSR[bit 9] = 0.                                                           |

|                 | If CPUID.01H: ECX.AESNI[bit $25$ ] = 0.                                             |

|                 | If the LOCK prefix is used.                                                         |

...

#### **BT**—**Bit Test**

...

#### Flags Affected

The CF flag contains the value of the selected bit. The ZF flag is unaffected. The OF, SF, AF, and PF flags are undefined.

...

#### **BTC**—Bit Test and Complement

...

#### **Flags Affected**

The CF flag contains the value of the selected bit before it is complemented. The ZF flag is unaffected. The OF, SF, AF, and PF flags are undefined.

• • •

#### **BTR**—Bit Test and Reset

. . .

#### **Flags Affected**

The CF flag contains the value of the selected bit before it is cleared. The ZF flag is unaffected. The OF, SF, AF, and PF flags are undefined.

...

#### **BTS**—Bit Test and Set

...

#### **Flags Affected**

The CF flag contains the value of the selected bit before it is set. The ZF flag is unaffected. The OF, SF, AF, and PF flags are undefined.

• • •

|        | Idsk-switcheu | гіду      | III CRU        |                     |                        |

|--------|---------------|-----------|----------------|---------------------|------------------------|

| Opcode | Instruction   | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description            |

| 0F 06  | CLTS          | А         | Valid          | Valid               | Clears TS flag in CRO. |

#### CLTS—Clear Task-Switched Flag in CRO

# Instruction Operand EncodingOp/EnOperand 1Operand 2Operand 3Operand 4ANANANANA

#### Description

Clears the task-switched (TS) flag in the CRO register. This instruction is intended for use in operating-system procedures. It is a privileged instruction that can only be executed at a CPL of 0. It is allowed to be executed in real-address mode to allow initialization for protected mode.

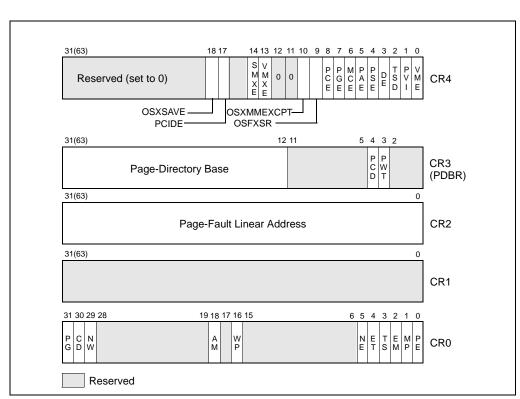

The processor sets the TS flag every time a task switch occurs. The flag is used to synchronize the saving of FPU context in multitasking applications. See the description of the TS flag in the section titled "Control Registers" in Chapter 2 of the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A*, for more information about this flag.

CLTS operation is the same in non-64-bit modes and 64-bit mode.