# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

June 2010

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-028

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.  $I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Intel Core, Intel Xeon, Intel 64, Intel NetBurst, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2002–2010, Intel Corporation. All rights reserved.

# Contents

| Revision History          | <br> | <br>• | • |  | • |       |  | • | • |  | • | • | • |  | • |       | •   | 4 |

|---------------------------|------|-------|---|--|---|-------|--|---|---|--|---|---|---|--|---|-------|-----|---|

| Preface                   | <br> | <br>• | • |  | • |       |  | • | • |  | • | • | • |  |   |       | •   | 7 |

| Summary Tables of Changes |      |       |   |  | • |       |  |   | • |  |   |   |   |  | • |       | . : | 8 |

| Documentation Changes     | <br> | <br>• | • |  | • | <br>• |  |   | • |  | • |   | • |  | • | <br>• | . ' | 9 |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                   | Date           |

|----------|-----------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul> | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul> | June 2010      |

§

**Revision History**

6

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                               | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture</i>                | 253665                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M</i>   | 253666                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z</i>   | 253667                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1</i> | 253668                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2</i> | 253669                      |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(R)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes (Sheet 1 of 2)**

| [ | No. | DOCUMENTATION CHANGES            |

|---|-----|----------------------------------|

|   | 1   | Updates to Chapter 7, Volume 1   |

| 1 | 2   | Updates to Chapter 9, Volume 1   |

| 1 | 3   | Updates to Chapter 11, Volume 1  |

| 1 | 4   | Updates to Chapter 12, Volume 1  |

|   | 5   | Updates to Chapter 13, Volume 1  |

|   | 6   | Updates to Appendix D, Volume 1  |

|   | 7   | Updates to Chapter 2, Volume 2A  |

|   | 8   | Updates to Chapter 3, Volume 2A  |

|   | 9   | Updates to Chapter 4, Volume 2B  |

|   | 10  | Updates to Chapter 5, Volume 2B  |

|   | 11  | Updates to Chapter 6, Volume 2B  |

|   | 12  | Updates to Appendix A, Volume 2B |

|   | 13  | Updates to Chapter 3, Volume 3A  |

|   | 14  | Updates to Chapter 6, Volume 3A  |

|   | 15  | Updates to Chapter 8, Volume 3A  |

|   | 16  | Updates to Chapter 10, Volume 3A |

|   | 17  | Updates to Chapter 14, Volume 3A |

|   | 18  | Updates to Chapter 16, Volume 3A |

|   | 19  | Updates to Chapter 20, Volume 3B |

|   | 20  | Updates to Chapter 22, Volume 3B |

| I | 21  | Updates to Chapter 23, Volume 3B |

| I | 22  | Updates to Chapter 24, Volume 3B |

| I | 23  | Updates to Chapter 25, Volume 3B |

| I | 24  | Updates to Chapter 26, Volume 3B |

| I | 25  | Updates to Chapter 29, Volume 3B |

| I | 26  | Updates to Chapter 30, Volume 3B |

# **Documentation Changes (Sheet 2 of 2)**

| ſ | No. | DOCUMENTATION CHANGES            |

|---|-----|----------------------------------|

| Γ | 27  | Updates to Appendix B, Volume 3B |

| Γ | 28  | Updates to Appendix E, Volume 3B |

|   | 29  | Updates to Appendix H, Volume 3B |

Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual Documentation Changes

# **Documentation Changes**

#### 1. Updates to Chapter 7, Volume 1

Change bars show changes to Chapter 7 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

• • •

### 7.3.8.2 Conditional Transfer Instructions

The conditional transfer instructions execute jumps or loops that transfer program control to another instruction in the instruction stream if specified conditions are met. The conditions for control transfer are specified with a set of condition codes that define various states of the status flags (CF, ZF, OF, PF, and SF) in the EFLAGS register.

...

**Jump if zero instructions** — The JECXZ (jump if ECX zero) instruction jumps to the location specified in the destination operand if the ECX register contains the value zero. This instruction can be used in combination with a loop instruction (LOOP, LOOPE, LOOPZ, LOOPNE, or LOOPNZ) to test the ECX register prior to beginning a loop. As described in "Loop instructions on page 7-24, the loop instructions decrement the contents of the ECX register before testing for zero. If the value in the ECX register is zero initially, it will be decremented to FFFFFFFH on the first loop instruction, causing the loop to be executed 2<sup>32</sup> times. To prevent this problem, a JECXZ instruction can be inserted at the beginning of the code block for the loop, causing a jump out the loop if the EAX register count is initially zero. When used with repeated string scan and compare instructions, the JECXZ instruction can determine whether the loop terminated because the count reached zero or because the scan or compare conditions were satisfied.

...

# 7.3.14.2 EFLAGS Transfer Instructions

The EFLAGS transfer instructions allow groups of flags in the EFLAGS register to be copied to a register or memory or be loaded from a register or memory.

The LAHF (load AH from flags) and SAHF (store AH into flags) instructions operate on five of the EFLAGS status flags (SF, ZF, AF, PF, and CF). The LAHF instruction copies the status flags to bits 7, 6, 4, 2, and 0 of the AH register, respectively. The contents of the remaining bits in the register (bits 5, 3, and 1) are unaffected, and the contents of the EFLAGS register remain unchanged. The SAHF instruction copies bits 7, 6, 4, 2, and 0 from the AH register into the SF, ZF, AF, PF, and CF flags, respectively in the EFLAGS register.

The PUSHF (push flags), PUSHFD (push flags double), POPF (pop flags), and POPFD (pop flags double) instructions copy the flags in the EFLAGS register to and from the stack. The PUSHF instruction pushes the lower word of the EFLAGS register onto the stack (see Figure 7-11). The PUSHFD instruction pushes the entire EFLAGS register onto the stack (with the RF and VM flags read as clear).

#### 2. Updates to Chapter 9, Volume 1

Change bars show changes to Chapter 9 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

# 9.4 MMX INSTRUCTIONS

The MMX instruction set consists of 47 instructions, grouped into the following categories:

- Data transfer

- Arithmetic

- Comparison

- Conversion

- Unpacking

- Logical

- Shift

- Empty MMX state instruction (EMMS)

Table 9-2 gives a summary of the instructions in the MMX instruction set. The following sections give a brief overview of the instructions within each group.

#### NOTES

The MMX instructions described in this chapter are those instructions that are available in an IA-32 processor when CPUID.01H:EDX.MMX[bit 23] = 1.

Section 10.4.4, "SSE 64-Bit SIMD Integer Instructions," and Section 11.4.2, "SSE2 64-Bit and 128-Bit SIMD Integer Instructions," list additional instructions included with SSE/SSE2 extensions that operate on the MMX registers but are not considered part of the MMX instruction set.

...

3.

#### Updates to Chapter 11, Volume 1

Change bars show changes to Chapter 11 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 1:* Basic Architecture.

\_\_\_\_\_

...

## 11.6.4 Initialization of SSE/SSE2 Extensions

The SSE and SSE2 state is contained in the XMM and MXCSR registers. Upon a hardware reset of the processor, this state is initialized as follows (see Table 11-2):

• All SIMD floating-point exceptions are masked (bits 7 through 12 of the MXCSR register is set to 1).

- All SIMD floating-point exception flags are cleared (bits 0 through 5 of the MXCSR register is set to 0).

- The rounding control is set to round-nearest (bits 13 and 14 of the MXCSR register are set to 00B).

- The flush-to-zero mode is disabled (bit 15 of the MXCSR register is set to 0).

- The denormals-are-zeros mode is disabled (bit 6 of the MXCSR register is set to 0). If the denormals-are-zeros mode is not supported, this bit is reserved and will be set to 0 on initialization.

- Each of the XMM registers is cleared (set to all zeros).

...

4.

#### Updates to Chapter 12, Volume 1

Change bars show changes to Chapter 12 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 1:* Basic Architecture.

\_\_\_\_\_

...

## 12.12.3 Checking for SSE4.2 Support

Before an application attempts to use the following SSE4.2 instructions: PCMPESTRI/ PCMPESTRM/PCMPISTRI/PCMPISTRM, PCMPGTQ; the application should follow the steps illustrated in Section 11.6.2, "Checking for SSE/SSE2 Support." Next, use the additional step provided below:

Check that the processor supports SSE4.2 (if CPUID.01H:ECX.SSE4\_2[bit 20] = 1), SSE4.1 (if CPUID.01H:ECX.SSE4\_1[bit 19] = 1), and SSSE3 (if CPUID.01H:ECX.SSE3[bit 9] = 1).

Before an application attempts to use the CRC32 instruction, it must check that the processor supports SSE4.2 (if CPUID.01H:ECX.SSE4\_2[bit 20] = 1).

Before an application attempts to use the POPCNT instruction, it must check that the processor supports SSE4.2 (if CPUID.01H:ECX.SSE4\_2[bit 20] = 1) and POPCNT (if CPUID.01H:ECX.POPCNT[bit 23] = 1).

...

#### 5. Updates to Chapter 13, Volume 1

Change bars show changes to Chapter 13 of the *Intel*<sup>®</sup> 64 and *IA-32* Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

...

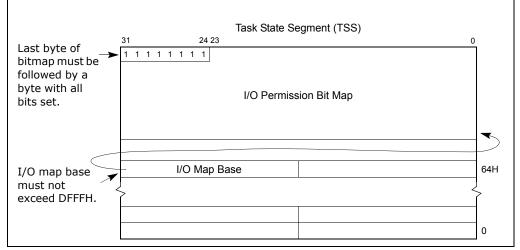

Figure 13-2 I/O Permission Bit Map

...

#### 6. Updates to Appendix D, Volume 1

Change bars show changes to Appendix D of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

```

. . .

Example D-4. Reduced-Latency Exception Handler

SAVE_ENVIRONMENTPROC

;SAVE REGISTERS, ALLOCATE STACK SPACE FOR x87 FPU ENVIRONMENT

PUSH

EBP

MOV

EBP, ESP

ESP, 28 ;ALLOCATES 28 BYTES (32-bit PROTECTED MODE SIZE)

SUB

;SAVE ENVIRONMENT, RESTORE INTERRUPT ENABLE FLAG (IF)

FNSTENV

[EBP - 28]

[EBP + OFFSET_TO_EFLAGS] ; COPY OLD EFLAGS TO STACK TOP

PUSH

POPFD ;RESTORE IF TO VALUE BEFORE x87 FPU EXCEPTION

;APPLICATION-DEPENDENT EXCEPTION HANDLING CODE GOES HERE

;CLEAR EXCEPTION FLAGS IN STATUS WORD (WHICH IS IN MEMORY)

BYTE PTR [EBP-24], OH

MOV

FLDENV [EBP-28]

;DE-ALLOCATE STACK SPACE, RESTORE REGISTERS

MOV

ESP, EBP

```

. POP EBP ; ;RETURN TO INTERRUPTED CALCULATION IRETD SAVE\_ENVIRONMENT ENDP ;RESTORE MODIFIED ENVIRONMENT IMAGE

...

#### Case #2: x87 FPU State Swap with Discarded Numeric Exception

Again, assume two threads A and B, both using the floating-point unit. Let A be the thread to have most recently executed a floating-point instruction, but this time let there be a pending numeric exception. Let B be the currently executing thread. When B starts to execute a floating-point instruction the instruction will fault with the DNA exception and enter the DNA handler. (If both numeric and DNA exceptions are pending, the DNA exception takes precedence, in order to support handling the numeric exception in its own context.)

When the FNSAVE starts, it will trigger an interrupt via FERR# because of the pending numeric exception. After some system dependent delay, the numeric exception handler is entered. It may be entered before the FNSAVE starts to execute, or it may be entered shortly after execution of the FNSAVE. Since the x87 FPU Owner is the kernel, the numeric exception handler simply exits, discarding the exception. The DNA handler resumes execution, completing the FNSAVE of the old floating-point context of thread A and the FRSTOR of the floating-point context for thread B.

Thread A eventually gets an opportunity to handle the exception that was discarded during the task switch. After some time, thread B is suspended, and thread A resumes execution. When thread A starts to execute an floating-point instruction, once again the DNA exception handler is entered. B's x87 FPU state is saved with FNSAVE, and A's x87 FPU state is restored with FRSTOR. Note that in restoring the x87 FPU state from A's save area, the pending numeric exception flags are reloaded into the floating-point status word. Now when the DNA exception handler returns, thread A resumes execution of the faulting floating-point instruction just long enough to immediately generate a numeric exception, which now gets handled in the normal way. The net result is that the task switch and resulting x87 FPU state swap via the DNA exception handler causes an extra numeric exception which can be safely discarded.

•••

### D.4.2 Changes with Intel486, Pentium and Pentium Pro Processors with CR0.NE[bit 5] = 1

With these three generations of the IA-32 architecture, more enhancements and speedup features have been added to the corresponding x87 FPUs. Also, the x87 FPU is now built into the same chip as the processor, which allows further increases in the speed at which the x87 FPU can operate as part of the integrated system. This also means that the native mode of x87 FPU exception handling, selected by setting bit NE of register CR0 to 1, is now entirely internal.

If an unmasked exception occurs during an x87 FPU instruction, the x87 FPU records the exception internally, and triggers the exception handler through interrupt 16 immedi-

ately before execution of the next WAIT or x87 FPU instruction (except for no-wait instructions, which will be executed as described in Section D.4.1, "Origin with the Intel 286 and Intel 287, and Intel386 and Intel 387 Processors").

An unmasked numerical exception causes the FERR# output to be activated even with NE = 1, and at exactly the same point in the program flow as it would have been asserted if NE were zero. However, the system would not connect FERR# to a PIC to generate INTR when operating in the native, internal mode. (If the hardware of a system has FERR# connected to trigger IRQ13 in order to support MS-DOS, but an operating system using the native mode is actually running the system, it is the operating system's responsibility to make sure that IRQ13 is not enabled in the slave PIC.) With this configuration a system is immune to the problem discussed in Section D.2.1.3, "No-Wait x87 FPU Instructions Can Get x87 FPU Interrupt in Window," where for Intel486 and Pentium processors a no-wait x87 FPU instruction can get an x87 FPU exception.

...

#### 7. Updates to Chapter 2, Volume 2A

Change bars show changes to Chapter 2 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 2A:* Instruction Set Reference, A-M.

------

...

Table 2-5 Special Cases of REX Encodings

| ModR/M or<br>SIB | Sub-field<br>Encodings | Compatibility<br>Mode Operation           | Compatibility<br>Mode Implications                                                                   | Additional Implications                                                                                                                                  |

|------------------|------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ModR/M Byte      | mod != 11              | SIB byte present.                         | SIB byte required                                                                                    | REX prefix adds a fourth                                                                                                                                 |

|                  | r/m =<br>b*100(ESP)    |                                           | for ESP-based<br>addressing.                                                                         | bit (b) which is not<br>decoded (don't care).                                                                                                            |

|                  |                        |                                           |                                                                                                      | SIB byte also required for R12-based addressing.                                                                                                         |

| ModR/M Byte      | mod = 0                | Base register not                         | EBP without a                                                                                        | REX prefix adds a fourth                                                                                                                                 |

|                  | r/m =<br>b*101(EBP)    | used.                                     | displacement must<br>be done using                                                                   | bit (b) which is not<br>decoded (don't care).                                                                                                            |

|                  |                        | mod = 01 with<br>displacement of 0.       | Using RBP or R13 without<br>displacement must be<br>done using mod = 01 with<br>a displacement of 0. |                                                                                                                                                          |

| SIB Byte         | index =<br>0100(ESP)   | Index register not<br>used.               | ESP cannot be used<br>as an index                                                                    | REX prefix adds a fourth<br>bit (b) which is decoded.                                                                                                    |

|                  |                        |                                           | register.                                                                                            | There are no additional<br>implications. The<br>expanded index field<br>allows distinguishing RSP<br>from R12, therefore R12<br>can be used as an index. |

| SIB Byte         | base =<br>0101(EBP)    | Base register is<br>unused if<br>mod = 0. | Base register<br>depends on mod<br>encoding.                                                         | REX prefix adds a fourth<br>bit (b) which is not<br>decoded.                                                                                             |

|                  |                        |                                           |                                                                                                      | This requires explicit<br>displacement to be used<br>with EBP/RBP or R13.                                                                                |

NOTES:

\* Don't care about value of REX.B

...

# Table 2-7 RIP-Relative Addressing

| ModR/M and<br>Encodings | SIB Sub-field      | Compatibility<br>Mode Operation | 64-bit Mode<br>Operation | Additional Implications<br>in 64-bit mode      |

|-------------------------|--------------------|---------------------------------|--------------------------|------------------------------------------------|

| ModR/M                  | mod = 00           | Disp32                          | RIP + Disp32             | Must use SIB form with                         |

| Byte                    | r/m = 101 (none)   |                                 |                          | normal (zero-based)<br>displacement addressing |

| SIB Byte                | 5                  |                                 | Same as                  | None                                           |

|                         | index = 100 (none) | Disp32                          | legacy                   |                                                |

|                         | scale = 0, 1, 2, 4 |                                 |                          |                                                |

•••

### 8. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

\_\_\_\_\_

•••

# **BLENDPD** — Blend Packed Double Precision Floating-Point Values

| Opcode               | Instruction                         | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                 |

|----------------------|-------------------------------------|-----------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A OD /r<br>ib | BLENDPD xmm1,<br>xmm2/m128,<br>imm8 | A         | Valid          | Valid               | Select packed DP-FP values<br>from xmm1 and xmm2/<br>m128 from mask specified<br>in imm8 and store the<br>values into xmm1. |

| Instruction Operand Encoding |                  |               |           |           |  |  |  |  |  |

|------------------------------|------------------|---------------|-----------|-----------|--|--|--|--|--|

| Op/En                        | Operand 1        | Operand 2     | Operand 3 | Operand 4 |  |  |  |  |  |

| А                            | ModRM:reg (r, w) | ModRM:r/m (r) | imm8      | NA        |  |  |  |  |  |

#### Description

Packed double-precision floating-point values from the source operand (second operand) are conditionally copied to the destination operand depending on the mask bits in the immediate operand. The mask bits are bits [1:0] of the immediate byte (third operand). Each mask bit corresponds to a quadword element in a 128-bit operand.

If a mask bit is "1", then the corresponding quadword in the source operand is copied to the destination, else the quadword element in the destination operand is left unchanged.

#### Operation

| IF (imm8[0] = 1)                                 |

|--------------------------------------------------|

| THEN DEST[63:0] $\leftarrow$ SRC[63:0];          |

| ELSE DEST[63:0] $\leftarrow$ DEST[63:0]; FI;     |

| IF (imm8[1] = 1)                                 |

| THEN DEST[127:64] $\leftarrow$ SRC[127:64];      |

| ELSE DEST[127:64] $\leftarrow$ DEST[127:64]; FI; |

|                                                  |

...

### BLENDPS — Blend Packed Single Precision Floating-Point Values

| Opcode               | Instruction                         | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                          |

|----------------------|-------------------------------------|-----------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A OC /r<br>ib | BLENDPS xmm1,<br>xmm2/m128,<br>imm8 | A         | Valid          | Valid               | Select packed single<br>precision floating-point<br>values from <i>xmm1</i> and<br><i>xmm2/m128</i> from mask<br>specified in <i>imm8</i> and store<br>the values into <i>xmm1</i> . |

|       |                  | Instruction Operand E | ncoding   |           |

|-------|------------------|-----------------------|-----------|-----------|

| Op/En | Operand 1        | Operand 2             | Operand 3 | Operand 4 |

| А     | ModRM:reg (r, w) | ModRM:r/m (r)         | imm8      | NA        |

#### Description

Packed single-precision floating-point values from the source operand (second operand) are conditionally copied to the destination operand (first operand) depending on the mask bits in the immediate operand. The mask bits are bits [3:0] of the immediate byte (third operand). Each mask bit corresponds to a dword element in a 128-bit operand.

If a mask bit is "1", then the corresponding dword in the source operand is copied to the destination, else the dword element in the destination operand is left unchanged.

#### Operation

| 1 | IF (imm8[0] = 1)<br>THEN DEST[31:0] ← SRC[31:0]; |

|---|--------------------------------------------------|

|   | ELSE DEST[31:0] $\leftarrow$ DEST[31:0]; FI;     |

| 1 | IF (imm8[1] = 1)                                 |

| - | THEN DEST[63:32] $\leftarrow$ SRC[63:32];        |

|   | ELSE DEST[63:32] ← DEST[63:32]; FI;              |

| 1 | IF (imm8[2] = 1)                                 |

|   | Then dest[95:64] $\leftarrow$ SRC[95:64];        |

|   | ELSE DEST[95:64] ← DEST[95:64]; FI;              |

| 1 | IF (imm8[3] = 1)                                 |

|   | THEN DEST[127:96] ← SRC[127:96];                 |

|   | ELSE DEST[127:96] ← DEST[127:96]; FI;            |

...

# **BLENDVPD** — Variable Blend Packed Double Precision Floating-Point Values

| Opcode         | Instruction                                    | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                      |

|----------------|------------------------------------------------|-----------|----------------|---------------------|------------------------------------------------------------------------------------------------------------------|

| 66 0F 38 15 /r | BLENDVPD xmm1,<br>xmm2/m128 ,<br><xmm0></xmm0> | A         | Valid          | Valid               | Select packed DP FP values<br>from xmm1 and xmm2 from<br>mask specified in XMM0 and<br>store the values in xmm1. |

|       |                  | Instruction Operand E | ncoding       |           |

|-------|------------------|-----------------------|---------------|-----------|

| Op/En | Operand 1        | Operand 2             | Operand 3     | Operand 4 |

| А     | ModRM:reg (r, w) | ModRM:r/m (r)         | implicit XMM0 | NA        |

#### Description

Packed double-precision floating-point values from the source operand (second argument) are conditionally copied to the destination operand (first argument) depending on the mask bits in the implicit third register argument, XMM0. The mask bits are the most significant bit in each qword element of XMM0. Each mask bit corresponds to a quadword element in a 128-bit operand.

If a mask bit is "1", then the corresponding quadword element in the source operand is copied to the destination, else the quadword element in the destination operand is left unchanged.

The register assignment of the third operand is defined to be the architectural register  $\mathsf{XMM0}.$

#### Operation

```

MASK ← XMM0;

IF (MASK[63] = 1)

THEN DEST[63:0] ← SRC[63:0];

ELSE DEST[63:0] ← DEST[63:0]; FI;

IF (MASK[127] = 1)

THEN DEST[127:64] ← SRC[127:64];

ELSE DEST[127:64] ← DEST[127:64]; FI;

```

...

# **BLENDVPS** — Variable Blend Packed Single Precision Floating-Point Values

| Opcode         | Instruction                                   | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                          |

|----------------|-----------------------------------------------|-----------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 0F 38 14 /r | BLENDVPS xmm1,<br>xmm2/m128,<br><xmm0></xmm0> | A         | Valid          | Valid               | Select packed single<br>precision floating-point<br>values from <i>xmm1</i> and<br><i>xmm2/m128</i> from mask<br>specified in <i>XMM0</i> and store<br>the values into <i>xmm1</i> . |

|       |                  | Instruction Operand E | ncoding       |           |

|-------|------------------|-----------------------|---------------|-----------|

| Op/En | Operand 1        | Operand 2             | Operand 3     | Operand 4 |

| А     | ModRM:reg (r, w) | ModRM:r/m (r)         | implicit XMM0 | NA        |

#### Description

Packed single-precision floating-point values from the source operand (second argument) are conditionally written to the destination operand (first argument) depending on the mask bits in the third register argument. The mask bits are the most significant bit in each dword element of XMMO. Each mask bit corresponds to a dword element in a 128bit operand.

If a mask bit is "1", then the corresponding dword element in the source operand is copied to the destination, else the dword element in the destination operand is left unchanged.

The register assignment of the third operand is defined to be the architectural register  $\mathsf{XMM0}.$

#### Operation

|   | Mask $\leftarrow$ XMM0;                       |

|---|-----------------------------------------------|

| 1 | IF (MASK[31] = 1)                             |

|   | THEN DEST[31:0] $\leftarrow$ SRC[31:0];       |

|   | ELSE DEST[31:0] $\leftarrow$ DEST[31:0]); FI; |

| 1 | IF (MASK[63] = 1)                             |

|   | THEN DEST[63:32] $\leftarrow$ SRC[63:32]);    |

|   | ELSE DEST[63:32] ← DEST[63:32]); FI;          |

| 1 | IF (MASK[95] = 1)                             |

|   | THEN DEST[95:64] ← SRC[95:64]);               |

|   | ELSE DEST[95:64] ← DEST[95:64]); FI;          |

| 1 | IF (MASK[127] = 1)                            |

|   | THEN DEST[127:96] ← SRC[127:96]);             |

|   | ELSE DEST[127:96] ← DEST[127:96]); FI;        |

|   |                                               |

...

### CMOVcc—Conditional Move

• • •

#### Operation

```

\begin{array}{c} \mathsf{temp} \leftarrow \mathsf{SRC} \\ \mathsf{IF} \text{ condition TRUE} \\ \mathsf{THEN} \\ \mathsf{DEST} \leftarrow \mathsf{temp}; \\ \mathsf{FI}; \\ \mathsf{ELSE} \\ \mathsf{IF} (\mathsf{OperandSize} = 32 \; \mathsf{and} \; \mathsf{IA}\text{-}32e \; \mathsf{mode} \; \mathsf{active}) \\ \mathsf{THEN} \\ \mathsf{DEST[63:32]} \leftarrow \mathsf{0}; \\ \mathsf{FI}; \end{array}

```

FI;

...

## **CPUID—CPU Identification**

...

| Table 3-12 | Information Returned by | / CPUID Instruction |

|------------|-------------------------|---------------------|

|            |                         |                     |

| Initial EAX<br>Value |            | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | Thermal ar | nd Power Management Leaf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 06H                  | EAX        | Bit 00: Digital temperature sensor is supported if set<br>Bit 01: Intel Turbo Boost Technology Available (see description of<br>IA32_MISC_ENABLES[38]).<br>Bit 02: ARAT. APIC-Timer-always-running feature is supported if set.<br>Bit 03: Reserved<br>Bit 04: PLN. Power limit notification controls are supported if set.<br>Bit 05: ECMD. Clock modulation duty cycle extension is supported if set.<br>Bit 06: PTM. Package thermal management is supported if set.<br>Bits 31 - 07: Reserved                                                                                              |

|                      | EBX        | Bits 03 - 00: Number of Interrupt Thresholds in Digital Thermal Sensor<br>Bits 31 - 04: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | ECX        | Bit 00: Hardware Coordination Feedback Capability (Presence of<br>IA32_MPERF and IA32_APERF). The capability to provide a measure of<br>delivered processor performance (since last reset of the counters), as<br>a percentage of expected processor performance at frequency speci-<br>fied in CPUID Brand String<br>Bits 02 - 01: Reserved = 0<br>Bit 03: The processor supports performance-energy bias preference if<br>CPUID.06H:ECX.SETBH[bit 3] is set and it also implies the presence of a<br>new architectural MSR called IA32_ENERGY_PERF_BIAS (1B0H)<br>Bits 31 - 04: Reserved = 0 |

|                      | EDX        | Reserved = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

• • •

# INPUT EAX = 0: Returns CPUID's Highest Value for Basic Processor Information and the Vendor Identification String

When CPUID executes with EAX set to 0, the processor returns the highest value the CPUID recognizes for returning basic processor information. The value is returned in the EAX register (see Table 3-13) and is processor specific.

A vendor identification string is also returned in EBX, EDX, and ECX. For Intel processors, the string is "GenuineIntel" and is expressed:

EBX  $\leftarrow$  756e6547h (\* "Genu", with G in the low eight bits of BL \*)

EDX  $\leftarrow$  49656e69h (\* "inel", with i in the low eight bits of DL \*)

ECX  $\leftarrow$  6c65746eh (\* "ntel", with n in the low eight bits of CL \*)

. . .

#### INPUT EAX = 80000000H: Returns CPUID's Highest Value for Extended Processor Information

When CPUID executes with EAX set to 80000000H, the processor returns the highest value the processor recognizes for returning extended processor information.

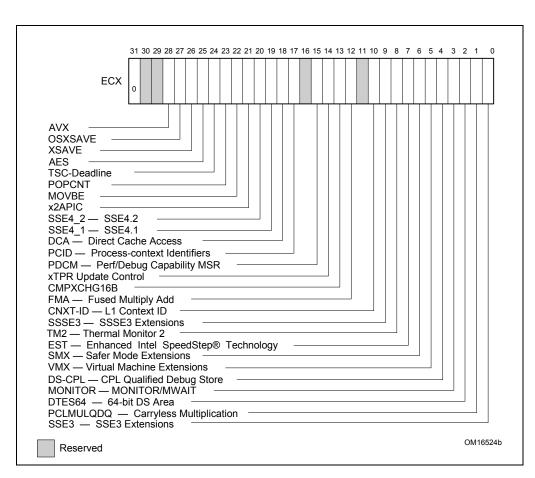

#### Figure 3-6 Feature Information Returned in the ECX Register

| Bit # | Mnemonic  | Description                                                                                               |

|-------|-----------|-----------------------------------------------------------------------------------------------------------|

| 0     | SSE3      | <b>Streaming SIMD Extensions 3 (SSE3).</b> A value of 1 indicates the processor supports this technology. |

| 1     | PCLMULQDQ | <b>PCLMULQDQ</b> . A value of 1 indicates the processor supports the PCLMULQDQ instruction                |

| 2     | DTES64    | <b>64-bit DS Area</b> . A value of 1 indicates the processor supports DS area using 64-bit layout         |

#### Table 3-15 Feature Information Returned in the ECX Register

| Bit # | Mnemonic               | Description                                                                                                                                                                                                                                                                   |  |  |

|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3     | MONITOR                | <b>MONITOR/MWAIT</b> . A value of 1 indicates the processor supports this feature.                                                                                                                                                                                            |  |  |

| 4     | DS-CPL                 | <b>CPL Qualified Debug Store</b> . A value of 1 indicates the processor supports the extensions to the Debug Store feature to allow for branch message storage qualified by CPL.                                                                                              |  |  |

| 5     | VMX                    | Virtual Machine Extensions. A value of 1 indicates that the processor supports this technology                                                                                                                                                                                |  |  |

| 6     | SMX                    | Safer Mode Extensions. A value of 1 indicates that the processor supports this technology. See Chapter 6, "Safer Mode Extensions Reference".                                                                                                                                  |  |  |

| 7     | EST                    | <b>Enhanced Intel SpeedStep<sup>•</sup> technology</b> . A value of 1 indicates that the processor supports this technology.                                                                                                                                                  |  |  |

| 8     | TM2                    | <b>Thermal Monitor 2</b> . A value of 1 indicates whether the processor supports this technology.                                                                                                                                                                             |  |  |

| 9     | SSSE3                  | A value of 1 indicates the presence of the Supplemental<br>Streaming SIMD Extensions 3 (SSSE3). A value of 0 indicates the<br>instruction extensions are not present in the processor                                                                                         |  |  |

| 10    | CNXT-ID                | L1 Context ID. A value of 1 indicates the L1 data cache mode car<br>be set to either adaptive mode or shared mode. A value of 0<br>indicates this feature is not supported. See definition of the<br>IA32_MISC_ENABLE MSR Bit 24 (L1 Data Cache Context Mode)<br>for details. |  |  |

| 11    | Reserved               | Reserved                                                                                                                                                                                                                                                                      |  |  |

| 12    | FMA                    | A value of 1 indicates the processor supports FMA extensions using YMM state.                                                                                                                                                                                                 |  |  |

| 13    | CMPXCHG16B             | <b>CMPXCHG16B Available.</b> A value of 1 indicates that the feature is available. See the "CMPXCHG8B/CMPXCHG16B—Compare and Exchange Bytes" section in this chapter for a description.                                                                                       |  |  |

| 14    | xTPR Update<br>Control | <b>xTPR Update Control</b> . A value of 1 indicates that the processor supports changing IA32_MISC_ENABLES[bit 23].                                                                                                                                                           |  |  |

| 15    | PDCM                   | <b>Perfmon and Debug Capability</b> : A value of 1 indicates the processor supports the performance and debug feature indication MSR IA32_PERF_CAPABILITIES.                                                                                                                  |  |  |

| 16    | Reserved               | Reserved                                                                                                                                                                                                                                                                      |  |  |

| 17    | PCID                   | <b>Process-context identifiers</b> . A value of 1 indicates that the processor supports PCIDs and that software may set CR4.PCIDE to 1.                                                                                                                                       |  |  |

| 18    | DCA                    | A value of 1 indicates the processor supports the ability to prefetch data from a memory mapped device.                                                                                                                                                                       |  |  |

| 19    | SSE4.1                 | A value of 1 indicates that the processor supports SSE4.1.                                                                                                                                                                                                                    |  |  |

| 20    | SSE4.2                 | A value of 1 indicates that the processor supports SSE4.2.                                                                                                                                                                                                                    |  |  |

| 21    | x2APIC                 | A value of 1 indicates that the processor supports x2APIC feature.                                                                                                                                                                                                            |  |  |

| 22    | MOVBE                  | A value of 1 indicates that the processor supports MOVBE instruction.                                                                                                                                                                                                         |  |  |

# Table 3-15 Feature Information Returned in the ECX Register (Continued)

| Bit #   | Mnemonic     | Description                                                                                                                                                                                            |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | POPCNT       | A value of 1 indicates that the processor supports the POPCNT instruction.                                                                                                                             |

| 24      | TSC-Deadline | A value of 1 indicates that the processor's local APIC timer<br>supports one-shot operation using a TSC deadline value.                                                                                |

| 25      | AESNI        | A value of 1 indicates that the processor supports the AESNI instruction extensions.                                                                                                                   |

| 26      | XSAVE        | A value of 1 indicates that the processor supports the XSAVE/<br>XRSTOR processor extended states feature, the XSETBV/<br>XGETBV instructions, and the XFEATURE_ENABLED_MASK<br>register (XCR0).       |

| 27      | OSXSAVE      | A value of 1 indicates that the OS has enabled XSETBV/XGETBV instructions to access the XFEATURE_ENABLED_MASK register (XCR0), and support for processor extended state management using XSAVE/XRSTOR. |

| 28      | AVX          | A value of 1 indicates the processor supports the AVX instruction extensions.                                                                                                                          |

| 30 - 29 | Reserved     | Reserved                                                                                                                                                                                               |

| 31      | Not Used     | Always returns 0                                                                                                                                                                                       |

#### Table 3-15 Feature Information Returned in the ECX Register (Continued)

...

### Table 3-17 Encoding of CPUID Leaf 2 Descriptors

| Value | Туре     | Description                                                         |  |  |  |  |  |

|-------|----------|---------------------------------------------------------------------|--|--|--|--|--|

|       |          |                                                                     |  |  |  |  |  |

| E4H   | Cache    | 3rd-level cache: 8 MByte, 16-way set associative, 64 byte line size |  |  |  |  |  |

| EAH   | Cache    | 3rd-level cache: 12MByte, 24-way set associative, 64 byte line size |  |  |  |  |  |

| EBH   | Cache    | 3rd-level cache: 18MByte, 24-way set associative, 64 byte line size |  |  |  |  |  |

| ECH   | Cache    | 3rd-level cache: 24MByte, 24-way set associative, 64 byte line size |  |  |  |  |  |

| FOH   | Prefetch | 64-Byte prefetching                                                 |  |  |  |  |  |

|       |          |                                                                     |  |  |  |  |  |

...

# DPPS — Dot Product of Packed Single Precision Floating-Point Values

...

# Operation

```

IF (imm8[4] = 1)

THEN Temp1[31:0] \leftarrow DEST[31:0] * SRC[31:0];

ELSE Temp1[31:0] \leftarrow +0.0; FI;

IF (imm8[5] = 1)

THEN Temp1[63:32] \leftarrow DEST[63:32] * SRC[63:32];

ELSE Temp1[63:32] \leftarrow +0.0; FI;

IF (imm8[6] = 1)

```

| I  | THEN Temp1[95:64] ← DEST[95:64] * SRC[95:64];<br>ELSE Temp1[95:64] ← +0.0; FI;<br>IF (imm8[7] = 1)<br>THEN Temp1[127:96] ← DEST[127:96] * SRC[127:96];<br>ELSE Temp1[127:96] ← +0.0; FI; |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Temp2[31:0] ← Temp1[31:0] + Temp1[63:32];                                                                                                                                                |

|    | Temp3[31:0] ← Temp1[95:64] + Temp1[127:96];                                                                                                                                              |

|    | $Temp4[31:0] \leftarrow Temp2[31:0] + Temp3[31:0];$                                                                                                                                      |

| I. | IF (imm8[0] = 1)<br>THEN DEST[31:0] ← Temp4[31:0];                                                                                                                                       |

|    | ELSE DEST[31:0] ← +0.0; FI;                                                                                                                                                              |

| I. | IF (imm8[1] = 1)<br>THEN DEST[63:32] ← Temp4[31:0];                                                                                                                                      |

|    | ELSE DEST[63:32] ← +0.0; FI;                                                                                                                                                             |

| 1  | IF (imm8[2] = 1)                                                                                                                                                                         |

| •  | THEN DEST[95:64] ← Temp4[31:0];                                                                                                                                                          |

|    | ELSE DEST[95:64] ← +0.0; FI;                                                                                                                                                             |

| I  | IF (imm8[3] = 1)                                                                                                                                                                         |

|    | THEN DEST[127:96] $\leftarrow$ Temp4[31:0];                                                                                                                                              |

|    | ELSE DEST[127:96] ← +0.0; FI;                                                                                                                                                            |

```

...

```

## **INSERTPS** — Insert Packed Single Precision Floating-Point Value

...

#### Operation

IF (SRC = REG) THEN COUNT\_S  $\leftarrow$  imm8[7:6]; ELSE COUNT\_S  $\leftarrow$  0; FI; COUNT\_D  $\leftarrow$  imm8[5:4]; ZMASK  $\leftarrow$  imm8[3:0];

CASE (COUNT\_S) OF

- 0: TMP ← SRC[31:0];

- 1: TMP ← SRC[63:32];

- 2: TMP ← SRC[95:64];

- 3: TMP ← SRC[127:96];

CASE (COUNT\_D) OF

- 0: TMP2[31:0] ← TMP;

- TMP2[127:32] ← DEST[127:32];

1: TMP2[63:32] ← TMP;

- TMP2[31:0]  $\leftarrow$  DEST[31:0]; TMP2[127:64]  $\leftarrow$  DEST[127:64];

- 2: TMP2[95:64] ← TMP; TMP2[63:0] ← DEST[63:0]; TMP2[127:96] ← DEST[127:96];

|   | 3: TMP2[127:96] ← TMP;                                      |

|---|-------------------------------------------------------------|

|   | TMP2[95:0] ← DEST[95:0];                                    |

|   |                                                             |

|   | IF (ZMASK[0] = 1) THEN DEST[31:0] $\leftarrow$ 00000000H;   |

|   | ELSE DEST[31:0] $\leftarrow$ TMP2[31:0];                    |

| 1 | IF (ZMASK[1] = 1) THEN DEST[63:32] ← 00000000H;             |

|   | ELSE DEST[63:32] ← TMP2[63:32];                             |

| 1 | IF (ZMASK[2] = 1) THEN DEST[95:64] $\leftarrow$ 0000000H;   |

|   | ELSE DEST[95:64] ← TMP2[95:64];                             |

| 1 | IF (ZMASK[3] = 1) THEN DEST[127:96] $\leftarrow$ 00000000H; |

| • | ELSE DEST[127:96] ← TMP2[127:96];                           |

|   | Fl;                                                         |

|   | FI;                                                         |

|   | FI;                                                         |

|   | FI:                                                         |

|   |                                                             |

|   |                                                             |

|   |                                                             |

# INT n/INTO/INT 3—Call to Interrupt Procedure

...

#### Operation

The following operational description applies not only to the INT n and INTO instructions, but also to external interrupts and exceptions.

```

IF PE = 0

THEN

GOTO REAL-ADDRESS-MODE;

ELSE (* PE = 1 *)

IF (VM = 1 and IOPL < 3 AND INT n)

THEN

#GP(0);

ELSE (* Protected mode, IA-32e mode, or virtual-8086 mode interrupt *)

IF (IA32_EFER.LMA = 0)

THEN (* Protected mode, or virtual-8086 mode interrupt *)

GOTO PROTECTED-MODE;

ELSE (* IA-32e mode interrupt *)

GOTO IA-32e-MODE;

FI;

FI;

FI;

REAL-ADDRESS-MODE:

IF ((vector_number * 4) + 3) is not within IDT limit

THEN #GP; FI;

IF stack not large enough for a 6-byte return information

THEN #SS; FI;

Push (EFLAGS[15:0]);

IF \leftarrow 0; (* Clear interrupt flag *)

TF \leftarrow 0; (* Clear trap flag *)

```

```

AC \leftarrow 0; (* Clear AC flag *)

Push(CS);

Push(IP);

(* No error codes are pushed *)

CS \leftarrow IDT(Descriptor (vector_number * 4), selector));

EIP ← IDT(Descriptor (vector_number * 4), offset)); (* 16 bit offset AND 0000FFFFH *)

END;

PROTECTED-MODE:

IF ((vector_number « 3) + 7) is not within IDT limits

or selected IDT descriptor is not an interrupt-, trap-, or task-gate type

THEN #GP((vector_number * 8) + 2 + EXT); FI;

(* EXT is bit 0 in error code *)

IF software interrupt (* Generated by INT n, INT 3, or INTO *)

THEN

IF gate DPL < CPL

THEN #GP((vector_number * 8) + 2); FI;

(* PE = 1, DPL<CPL, software interrupt *)

FI:

IF gate not present

THEN #NP((vector_number << 3) + 2 + EXT); FI;

IF task gate (* Specified in the selected interrupt table descriptor *)

THEN GOTO TASK-GATE;

ELSE GOTO TRAP-OR-INTERRUPT-GATE; (* PE = 1, trap/interrupt gate *)

FI;

END:

IA-32e-MODE:

IF ((vector_number * 16) + 15) is not in IDT limits

or selected IDT descriptor is not an interrupt-, or trap-gate type

THEN #GP((vector_number << 3) + 2 + EXT);

(* EXT is bit 0 in error code *)

FI;

IF software interrupt (* Generated by INT n, INT 3, but not INTO *)

THEN

IF gate DPL < CPL

THEN #GP((vector_number « 3) + 2);

(* PE = 1, DPL < CPL, software interrupt *)

FI;

ELSE (* Generated by INTO *)

#UD;

FI:

IF gate not present

THEN #NP((vector_number << 3) + 2 + EXT);

FI;

GOTO TRAP-OR-INTERRUPT-GATE; (* Trap/interrupt gate *)

END;

TASK-GATE: (* PE = 1, task gate *)

Read TSS selector in task gate (IDT descriptor);

IF local/global bit is set to local or index not within GDT limits

THEN #GP(TSS selector); FI;

Access TSS descriptor in GDT;

```

```

IF TSS descriptor specifies that the TSS is busy (low-order 5 bits set to 00001)

THEN #GP(TSS selector); FI;

IF TSS not present

THEN #NP(TSS selector); FI;

SWITCH-TASKS (with nesting) to TSS;

IF interrupt caused by fault with error code

THEN

IF stack limit does not allow push of error code

THEN #SS(0); FI;

Push(error code);

FI;

IF EIP not within code segment limit

THEN #GP(0); FI;

END;

TRAP-OR-INTERRUPT-GATE:

Read new code-segment selector for trap or interrupt gate (IDT descriptor);

IF new code-segment selector is NULL

THEN #GP(OH + EXT); FI; (* NULL selector with EXT flag set *)

IF new code-segment selector is not within its descriptor table limits

THEN #GP(new code-segment selector + EXT); FI;

Read descriptor referenced by new code-segment selector;

IF descriptor does not indicate a code segment

or new code-segment DPL > CPL

THEN #GP(new code-segment selector + EXT); FI;

IF new code-segment descriptor is not present,

THEN #NP(new code-segment selector + EXT); FI;

IF new code segment is non-conforming with DPL < CPL

THEN

IF VM = 0

THEN

GOTO INTER-PRIVILEGE-LEVEL-INTERRUPT;

(* PE = 1, VM = 0, interrupt or trap gate, nonconforming code segment,

DPL < CPL *)

ELSE (* VM = 1 *)

IF new code-segment DPL \neq 0

THEN #GP(new code-segment selector);

GOTO INTERRUPT-FROM-VIRTUAL-8086-MODE; FI;

(* PE = 1, interrupt or trap gate, DPL < CPL, VM = 1 *)

FI;

ELSE (* PE = 1, interrupt or trap gate, DPL \ge CPL *)

IF VM = 1

THEN #GP(new code-segment selector); FI;

IF new code segment is conforming or new code-segment DPL = CPL

THEN

GOTO INTRA-PRIVILEGE-LEVEL-INTERRUPT;

ELSE

#GP(new code-segment selector + EXT);

(* PE = 1, interrupt or trap gate, nonconforming code segment, DPL > CPL *)

FI;

FI;

```

```

END;

INTER-PRIVILEGE-LEVEL-INTERRUPT:

(* PE = 1, interrupt or trap gate, non-conforming code segment, DPL < CPL *)

IF (IA32_EFER.LMA = 0) (* Not IA-32e mode *)

THEN

(* Identify stack-segment selector for new privilege level in current TSS *)

IF current TSS is 32-bit

THEN

TSSstackAddress \leftarrow (new code-segment DPL * 8) + 4;

IF (TSSstackAddress + 5) > current TSS limit

THEN #TS(current TSS selector); FI;

NewSS \leftarrow 2 bytes loaded from (TSS base + TSSstackAddress + 4);

NewESP \leftarrow 4 bytes loaded from (TSS base + TSSstackAddress);

ELSE

(* current TSS is 16-bit *)

TSSstackAddress \leftarrow (new code-segment DPL * 4) + 2

IF (TSSstackAddress + 3) > current TSS limit

THEN #TS(current TSS selector); FI;

NewSS \leftarrow 2 bytes loaded from (TSS base + TSSstackAddress + 2);

NewESP \leftarrow 2 bytes loaded from (TSS base + TSSstackAddress);

FI;

IF NewSS is NULL

THEN #TS(EXT); FI;

IF NewSS index is not within its descriptor-table limits

or NewSS RPL \neq new code-segment DPL

THEN #TS(NewSS + EXT); FI;

Read new stack-segment descriptor for NewSS in GDT or LDT;

IF new stack-segment DPL \neq new code-segment DPL

or new stack-segment Type does not indicate writable data segment

THEN #TS(NewSS + EXT); FI;

IF NewSS is not present

THEN #SS(NewSS + EXT); FI;

ELSE (* IA-32e mode *)

IF IDT-gate IST = 0

THEN TSSstackAddress \leftarrow (new code-segment DPL * 8) + 4;

ELSE TSSstackAddress \leftarrow (IDT gate IST * 8) + 28;

FI:

IF (TSSstackAddress + 7) > current TSS limit

THEN #TS(current TSS selector); FI;

NewRSP ← 8 bytes loaded from (current TSS base + TSSstackAddress);

NewSS \leftarrow new code-segment DPL; (* null selector with RPL = new CPL *)

FI;

IF IDT gate is 32-bit

THEN

IF new stack does not have room for 24 bytes (error code pushed)

or 20 bytes (no error code pushed)

THEN #SS(NewSS + EXT); FI;

FI

ELSE

IF IDT gate is 16-bit

THEN

```

| IF new stack does not have room for 12 bytes (error code pushed)                               |

|------------------------------------------------------------------------------------------------|

| or 10 bytes (no error code pushed);                                                            |

| THEN #SS(NewSS + EXT); FI;                                                                     |

| ELSE (* 64-bit IDT gate*)                                                                      |

| IF StackAddress is non-canonical                                                               |

| THEN #SS(0);FI;                                                                                |

| Fl;                                                                                            |

| FI;                                                                                            |

| IF (IA32_EFER.LMA = 0) (* Not IA-32e mode *)                                                   |

| THEN                                                                                           |

| IF instruction pointer from IDT gate is not within new code-segment limits<br>THEN #GP(0); FI; |

| $ESP \leftarrow NewESP;$                                                                       |

| SS $\leftarrow$ NewSS; (* Segment descriptor information also loaded *)                        |

| ELSE (* IA-32e mode *)                                                                         |

| IF instruction pointer from IDT gate contains a non-canonical address<br>THEN #GP(0); FI:      |

| $RSP \leftarrow NewRSP \And FFFFFFFFFFFFFF;$                                                   |

| $SS \leftarrow NewSS;$                                                                         |

| FI;                                                                                            |

| IF IDT gate is 32-bit                                                                          |

| THEN                                                                                           |

| CS:EIP $\leftarrow$ Gate(CS:EIP); (* Segment descriptor information also loaded *)             |

| ELSE                                                                                           |

| IF IDT gate 16-bit                                                                             |

| THEN                                                                                           |

| $CS:IP \leftarrow Gate(CS:IP);$                                                                |

| (* Segment descriptor information also loaded *)                                               |

| ELSE (* 64-bit IDT gate *)                                                                     |

| CS:RIP ← Gate(CS:RIP);<br>(* Segment descriptor information also loaded *)                     |

| FI;                                                                                            |

| Fl;                                                                                            |

| IF IDT gate is 32-bit                                                                          |

| THEN                                                                                           |

| Push(far pointer to old stack);                                                                |

| (* Old SS and ESP, 3 words padded to 4 *)                                                      |

| Push(EFLAGS);                                                                                  |

| Push(far pointer to return instruction);                                                       |

| (* Old CS and EIP, 3 words padded to 4 *)                                                      |

| Push(ErrorCode); (* If needed, 4 bytes *)                                                      |

| ELSE                                                                                           |

| IF IDT gate 16-bit<br>THEN                                                                     |

| Push(far pointer to old stack);                                                                |

| (* Old SS and SP, 2 words *)                                                                   |

| Push(EFLAGS(15-0]);                                                                            |

| Push(far pointer to return instruction);                                                       |

| (* Old CS and IP, 2 words *)                                                                   |

| Push(ErrorCode); (* If needed, 2 bytes *)                                                      |

| ···(-·, ( ···········,,,                                                                       |

| ELSE (* 64-bit IDT gate *)                                                                 |

|--------------------------------------------------------------------------------------------|

| Push(far pointer to old stack);                                                            |

| (* Old SS and SP, each an 8-byte push *)                                                   |

| Push(RFLAGS); (* 8-byte push *)                                                            |

| Push(far pointer to return instruction);                                                   |

| (* Old CS and RIP, each an 8-byte push *)                                                  |

| Push(ErrorCode); (* If needed, 8-bytes *)                                                  |

| FI;                                                                                        |

| Fl;                                                                                        |