# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

September 2010

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-029

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel<sup>®</sup> 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.  $I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, Intel Core, Intel Xeon, Intel 64, Intel NetBurst, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright @ 2002–2010, Intel Corporation. All rights reserved.

# Contents

| Revision History          | <br> |  | <br>• • |  | <br> | • |  |  |  |   |  |  | • | . 4 | 1 |

|---------------------------|------|--|---------|--|------|---|--|--|--|---|--|--|---|-----|---|

| Preface                   | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 7 | 7 |

| Summary Tables of Changes |      |  | <br>    |  | <br> | • |  |  |  | • |  |  | • | . 8 | 3 |

| Documentation Changes     | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 9 | ) |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                   | Date           |

|----------|-----------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul> | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul> | June 2010      |

| -029     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-24</li></ul> | September 2010 |

§

**Revision History**

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                         | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume<br>1: Basic Architecture             | 253665                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M   | 253666                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z   | 253667                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1 | 253668                      |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2 | 253669                      |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(B)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes**

|    | No. | DOCUMENTATION CHANGES            |

|----|-----|----------------------------------|

|    | 1   | Updates to Chapter 3, Volume 1   |

|    | 2   | Updates to Chapter 3, Volume 2A  |

| I  | 3   | Updates to Chapter 4, Volume 2B  |

|    | 4   | Updates to Chapter 5, Volume 2B  |

|    | 5   | Updates to Chapter 6, Volume 2B  |

|    | 6   | Updates to Chapter 2, Volume 3A  |

| I  | 7   | Updates to Chapter 4, Volume 3A  |

| 1  | 8   | Updates to Chapter 6, Volume 3A  |

|    | 9   | Updates to Chapter 8, Volume 3A  |

|    | 10  | Updates to Chapter 9, Volume 3A  |

| 1  | 11  | Updates to Chapter 10, Volume 3A |

| 1  | 12  | Updates to Chapter 13, Volume 3A |

| I. | 13  | Updates to Chapter 15, Volume 3A |

| I. | 14  | Updates to Chapter 16, Volume 3A |

| I. | 15  | Updates to Chapter 22, Volume 3B |

| I. | 16  | Updates to Chapter 23, Volume 3B |

|    | 17  | Updates to Chapter 24, Volume 3B |

| I. | 18  | Updates to Chapter 25, Volume 3B |

|    | 19  | Updates to Chapter 27, Volume 3B |

|    | 20  | Updates to Chapter 30, Volume 3B |

|    | 21  | Updates to Appendix B, Volume 3B |

|    | 22  | Updates to Appendix E, Volume 3B |

|    | 23  | Updates to Appendix G, Volume 3B |

# **Documentation Changes**

#### 1. Updates to Chapter 3, Volume 1

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

-----

# 3.7.5.1 Specifying an Offset in 64-Bit Mode

The offset part of a memory address in 64-bit mode can be specified directly as a static value or through an address computation made up of one or more of the following components:

- Displacement An 8-bit or 32-bit value.

- Base The value in a 32-bit (or 64-bit if REX.W is set) general-purpose register.

- Index The value in a 32-bit (or 64-bit if REX.W is set) general-purpose register.

- Scale factor A value of 2, 4, or 8 that is multiplied by the index value.

• • •

. . .

#### 2. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

\_\_\_\_\_

...

### 3.1.1.8 Operation Section

The "Operation" section contains an algorithm description (frequently written in pseudocode) for the instruction. Algorithms are composed of the following elements:

- Comments are enclosed within the symbol pairs "(\*" and "\*)".

- Compound statements are enclosed in keywords, such as: IF, THEN, ELSE and FI for an if statement; DO and OD for a do statement; or CASE... OF for a case statement.

- A register name implies the contents of the register. A register name enclosed in brackets implies the contents of the location whose address is contained in that register. For example, ES: [DI] indicates the contents of the location whose ES segment relative address is in register DI. [SI] indicates the contents of the address contained in register SI relative to the SI register's default segment (DS) or the overridden segment.

- Parentheses around the "E" in a general-purpose register name, such as (E)SI, indicates that the offset is read from the SI register if the address-size attribute is 16, from the ESI register if the address-size attribute is 32. Parentheses around the "R" in a general-purpose register name, (R)SI, in the presence of a 64-bit register

definition such as (R)SI, indicates that the offset is read from the 64-bit RSI register if the address-size attribute is 64.

- Brackets are used for memory operands where they mean that the contents of the memory location is a segment-relative offset. For example, [SRC] indicates that the content of the source operand is a segment-relative offset.

- A ← B indicates that the value of B is assigned to A.

- The symbols =, ≠, >, <, ≥, and ≤ are relational operators used to compare two values: meaning equal, not equal, greater or equal, less or equal, respectively. A relational expression such as A ← B is TRUE if the value of A is equal to B; otherwise it is FALSE.</li>

- The expression "« COUNT" and "» COUNT" indicates that the destination operand should be shifted left or right by the number of bits indicated by the count operand.

The following identifiers are used in the algorithmic descriptions:

OperandSize and AddressSize — The OperandSize identifier represents the

operand-size attribute of the instruction, which is 16, 32 or 64-bits. The AddressSize

identifier represents the address-size attribute, which is 16, 32 or 64-bits. For

example, the following pseudo-code indicates that the operand-size attribute

depends on the form of the MOV instruction used.

```

IF Instruction \leftarrow MOVW

THEN OperandSize = 16;

ELSE

IF Instruction \leftarrow MOVD

THEN OperandSize = 32;

ELSE

IF Instruction \leftarrow MOVQ

THEN OperandSize = 64;

FI;

FI;

```

See "Operand-Size and Address-Size Attributes" in Chapter 3 of the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1*, for guidelines on how these attributes are determined.

#### . . .

#### AND—Logical AND

| Opcode             | Instruction                  | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description    |

|--------------------|------------------------------|-----------|----------------|---------------------|----------------|

| <br>REX + 80 /4 ib | AND r/m8 <sup>*</sup> , imm8 | В         | Valid          | N.E.                | r/m8 AND imm8. |

|                    |                              |           |                |                     |                |

• • •

## **CALL—Call Procedure**

..

#### Operation

```

CALL-GATE:

IF call gate (DPL < CPL) or (RPL > DPL)

THEN #GP(call-gate selector); FI;

IF call gate not present

THEN #NP(call-gate selector); FI:

IF call-gate code-segment selector is NULL

THEN #GP(0); FI;

IF call-gate code-segment selector index is outside descriptor table limits

THEN #GP(call-gate code-segment selector); FI;

Read call-gate code-segment descriptor;

IF call-gate code-segment descriptor does not indicate a code segment

or call-gate code-segment descriptor DPL > CPL

THEN #GP(call-gate code-segment selector); FI;

IF IA32_EFER.LMA = 1 AND (call-gate code-segment descriptor is

not a 64-bit code segment or call-gate code-segment descriptor has both L-bit and D-bit set)

THEN #GP(call-gate code-segment selector); FI;

IF call-gate code segment not present

THEN #NP(call-gate code-segment selector); FI;

IF call-gate code segment is non-conforming and DPL < CPL

THEN go to MORE-PRIVILEGE;

ELSE go to SAME-PRIVILEGE;

FI;

END:

MORE-PRIVILEGE:

IF current TSS is 32-bit

THEN

TSSstackAddress \leftarrow (new code-segment DPL * 8) + 4;

IF (TSSstackAddress + 5) > current TSS limit

THEN #TS(current TSS selector); FI;

```

```

NewSS \leftarrow 2 bytes loaded from (TSS base + TSSstackAddress + 4);

```

```

NewESP \leftarrow 4 bytes loaded from (TSS base + TSSstackAddress);

```

#### ELSE

```

IF current TSS is 16-bit

THEN

TSSstackAddress ← (new code-segment DPL * 4) + 2

IF (TSSstackAddress + 3) > current TSS limit

THEN #TS(current TSS selector); FI;

NewSS ← 2 bytes loaded from (TSS base + TSSstackAddress + 2);

NewESP ← 2 bytes loaded from (TSS base + TSSstackAddress);

ELSE (* current TSS is 64-bit *)

TSSstackAddress ← (new code-segment DPL * 8) + 4;

IF (TSSstackAddress + 7) > current TSS limit

THEN #TS(current TSS selector); FI;

```

```

NewSS \leftarrow new code-segment DPL; (* NULL selector with RPL = new CPL *)

NewRSP ← 8 bytes loaded from (current TSS base + TSSstackAddress);

FI:

FI;

IF IA32 EFER.LMA = 0 and NewSS is NULL

THEN #TS(NewSS); FI;

Read new code-segment descriptor and new stack-segment descriptor;

IF IA32 EFER.LMA = 0 and (NewSS RPL \neq new code-segment DPL

or new stack-segment DPL ≠ new code-segment DPL or new stack segment is not a

writable data segment)

THEN #TS(NewSS); FI

IF IA32_EFER.LMA = 0 and new stack segment not present

THEN #SS(NewSS); FI;

IF CallGateSize = 32

THEN

IF new stack does not have room for parameters plus 16 bytes

THEN #SS(NewSS); FI;

IF CallGate(InstructionPointer) not within new code-segment limit

THEN #GP(0); FI;

SS \leftarrow newSS; (* Segment descriptor information also loaded *)

ESP \leftarrow newESP;

CS:EIP ← CallGate(CS:InstructionPointer);

(* Segment descriptor information also loaded *)

Push(oldSS:oldESP); (* From calling procedure *)

temp \leftarrow parameter count from call gate, masked to 5 bits;

Push(parameters from calling procedure's stack, temp)

Push(oldCS:oldEIP); (* Return address to calling procedure *)

ELSE

IF CallGateSize = 16

THEN

IF new stack does not have room for parameters plus 8 bytes

THEN #SS(NewSS); FI;

IF (CallGate(InstructionPointer) AND FFFFH) not in new code-segment limit

THEN #GP(0); FI;

SS \leftarrow newSS; (* Segment descriptor information also loaded *)

ESP \leftarrow newESP;

CS:IP ← CallGate(CS:InstructionPointer);

(* Segment descriptor information also loaded *)

Push(oldSS:oldESP); (* From calling procedure *)

temp \leftarrow parameter count from call gate, masked to 5 bits;

Push(parameters from calling procedure's stack, temp)

Push(oldCS:oldEIP); (* Return address to calling procedure *)

ELSE (* CallGateSize = 64 *)

IF pushing 32 bytes on the stack would use a non-canonical address

THEN #SS(NewSS); FI;

IF (CallGate(InstructionPointer) is non-canonical)

THEN #GP(0); FI;

SS \leftarrow NewSS; (* NewSS is NULL)

RSP \leftarrow NewESP;

CS:IP \leftarrow CallGate(CS:InstructionPointer);

```

. . .

END;

## CMOVcc—Conditional Move

| Opcode              | Instruction             | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description              |

|---------------------|-------------------------|-----------|----------------|---------------------|--------------------------|

|                     |                         |           |                |                     |                          |

| 0F 40 /r            | CMOVO r16, r/m16        | А         | Valid          | Valid               | Move if overflow (OF=1). |

| 0F 40 /r            | CMOVO <i>r32, r/m32</i> | А         | Valid          | Valid               | Move if overflow (OF=1). |

| REX.W + 0F 40<br>/r | CMOVO <i>r64, r/m64</i> | А         | Valid          | N.E.                | Move if overflow (OF=1). |

|                     |                         |           |                |                     |                          |

...

# **CPUID—CPU Identification**

• • •

## INPUT EAX = 1: Returns Model, Family, Stepping Information

. . .

The Extended Family ID needs to be examined only when the Family ID is 0FH. Integrate the fields into a display using the following rule:

|   | IF Family_ID $\neq$ OFH                                                                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | THEN DisplayFamily = Family_ID;                                                                                                                   |

|   | ELSE DisplayFamily = Extended_Family_ID + Family_ID;                                                                                              |

|   | (* Right justify and zero-extend 4-bit field. *)                                                                                                  |

|   | Fl;                                                                                                                                               |

| 1 | (* Show DisplayFamily as HEX field. *)                                                                                                            |

|   | The Extended Model ID needs to be examined only when the Family ID is 06H or 0FH.<br>Integrate the field into a display using the following rule: |

|   | IF (Family_ID = 06H or Family_ID = 0FH)                                                                                                           |

| 1 | THEN DisplayModel = (Extended_Model_ID « 4) + Model_ID;                                                                                           |

|   | (* Right justify and zero-extend 4-bit field; display Model_ID as HEX field.*)                                                                    |

| 1 | ELSE DisplayModel = Model_ID;                                                                                                                     |

|   | FI;                                                                                                                                               |

| 1 | (* Show DisplayModel as HEX field. *)                                                                                                             |

|   |                                                                                                                                                   |

|   |                                                                                                                                                   |

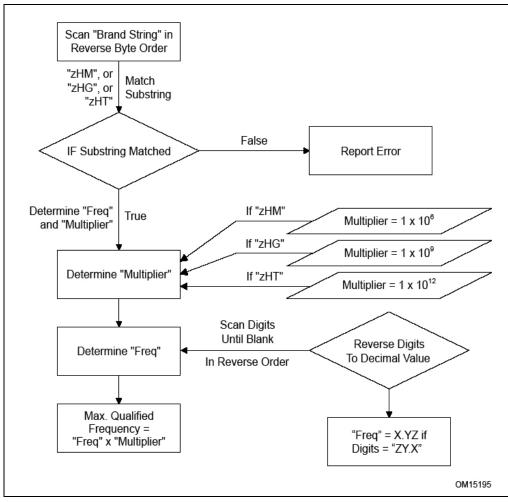

Figure 3-9. Algorithm for Extracting Maximum Processor Frequency

# CVTPI2PD—Convert Packed Dword Integers to Packed Double-Precision FP Values

#### SIMD Floating-Point Exceptions

Precision

. . .

. . .

. . .

# CVTSI2SD—Convert Dword Integer to Scalar Double-Precision FP Value

#### SIMD Floating-Point Exceptions

Precision

# FXSAVE—Save x87 FPU, MMX Technology, and SSE State

...

. . .

. . .

The fields in Table 3-48 are defined in Table 3-49.

#### Table 3-49 Field Definitions

| Field        | Definition                                                                                                                                                                                                                                                      |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCW          | x87 FPU Control Word (16 bits). See Figure 8-6 in the Intel <sup>®</sup> 64 and IA-32<br>Architectures Software Developer's Manual, Volume 1, for the layout of<br>the x87 FPU control word.                                                                    |

| FSW          | x87 FPU Status Word (16 bits). See Figure 8-4 in the Intel <sup>®</sup> 64 and IA-32<br>Architectures Software Developer's Manual, Volume 1, for the layout of<br>the x87 FPU status word.                                                                      |

| Abridged FTW | x87 FPU Tag Word (8 bits). The tag information saved here is abridged, as described in the following paragraphs.                                                                                                                                                |

| FOP          | x87 FPU Opcode (16 bits). The lower 11 bits of this field contain the opcode, upper 5 bits are reserved. See Figure 8-8 in the Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1, for the layout of the x87 FPU opcode field. |

| FPU IP       | x87 FPU Instruction Pointer Offset (32 bits). The contents of this field differ depending on the current addressing mode (32-bit or 16-bit) of the processor when the FXSAVE instruction was executed:                                                          |

|              | 32-bit mode — 32-bit IP offset.                                                                                                                                                                                                                                 |

|              | 16-bit mode — low 16 bits are IP offset; high 16 bits are reserved.                                                                                                                                                                                             |

|              | See "x87 FPU Instruction and Operand (Data) Pointers" in Chapter 8 of the Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1, for a description of the x87 FPU instruction pointer.                                            |

| CS           | x87 FPU Instruction Pointer Selector (16 bits).                                                                                                                                                                                                                 |

| FPU DP       | x87 FPU Instruction Operand (Data) Pointer Offset (32 bits). The contents of this field differ depending on the current addressing mode (32-bit or 16-bit) of the processor when the FXSAVE instruction was executed:                                           |

|              | 32-bit mode — 32-bit DP offset.                                                                                                                                                                                                                                 |

|              | 16-bit mode — low 16 bits are DP offset; high 16 bits are reserved.                                                                                                                                                                                             |

|              | See "x87 FPU Instruction and Operand (Data) Pointers" in Chapter 8 of the Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1, for a description of the x87 FPU operand pointer.                                                |

| DS           | x87 FPU Instruction Operand (Data) Pointer Selector (16 bits).                                                                                                                                                                                                  |

| Field                      | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MXCSR                      | MXCSR Register State (32 bits). See Figure 10-3 in the Intel <sup>®</sup> 64 and IA-32<br>Architectures Software Developer's Manual, Volume 1, for the layout of<br>the MXCSR register. If the OSFXSR bit in control register CR4 is not set, the<br>FXSAVE instruction may not save this register. This behavior is<br>implementation dependent.                                                                                                                                                                                                                                                             |

| MXCSR_<br>MASK             | MXCSR_MASK (32 bits). This mask can be used to adjust values written to<br>the MXCSR register, ensuring that reserved bits are set to 0. Set the mask<br>bits and flags in MXCSR to the mode of operation desired for SSE and SSE2<br>SIMD floating-point instructions. See "Guidelines for Writing to the MXCSR<br>Register" in Chapter 11 of the Intel <sup>®</sup> 64 and IA-32 Architectures Software<br>Developer's Manual, Volume 1, for instructions for how to determine and<br>use the MXCSR_MASK value.                                                                                             |

| STO/MM0 through<br>ST7/MM7 | x87 FPU or MMX technology registers. These 80-bit fields contain the x87 FPU data registers or the MMX technology registers, depending on the state of the processor prior to the execution of the FXSAVE instruction. If the processor had been executing x87 FPU instruction prior to the FXSAVE instruction, the x87 FPU data registers are saved; if it had been executing MMX instructions (or SSE or SSE2 instructions that operated on the MMX technology registers), the MMX technology registers are saved. When the MMX technology registers are saved, the high 16 bits of the field are reserved. |

| XMM0 through<br>XMM7       | XMM registers (128 bits per field). If the OSFXSR bit in control register CR4 is not set, the FXSAVE instruction may not save these registers. This behavior is implementation dependent.                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 3-49 Field Definitions (Continued)

. . .

# INT n/INTO/INT 3—Call to Interrupt Procedure

. . .

. . .

#### Description

The INT *n* instruction generates a call to the interrupt or exception handler specified with the destination operand (see the section titled "Interrupts and Exceptions" in Chapter 6 of the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1*). The destination operand specifies an interrupt vector number from 0 to 255, encoded as an 8-bit unsigned intermediate value. Each interrupt vector number provides an index to a gate descriptor in the IDT. The first 32 interrupt vector numbers are reserved by Intel for system use. Some of these interrupts are used for internally generated exceptions.

The INT *n* instruction is the general mnemonic for executing a software-generated call to an interrupt handler. The INTO instruction is a special mnemonic for calling overflow exception (#OF), interrupt vector number 4. The overflow interrupt checks the OF flag in the EFLAGS register and calls the overflow interrupt handler if the OF flag is set to 1. (The INTO instruction cannot be used in 64-bit mode.)

#### Operation

The following operational description applies not only to the INT *n* and INTO instructions, but also to external interrupts, nonmaskable interrupts (NMIs), and exceptions. Some of these events push onto the stack an error code.

The operational description specifies numerous checks whose failure may result in delivery of a nested exception. In these cases, the original event is not delivered.

The operational description specifies the error code delivered by any nested exception. In some cases, the error code is specified with a pseudofunction error\_code(num,idt,ext), where idt and ext are bit values. The pseudofunction produces an error code as follows: (1) if idt is 0, the error code is (num & FCH) | ext; (2) if idt is 1, the error code is (num « 3) | 2 | ext.

In many cases, the pseudofunction error\_code is invoked with a pseudovariable EXT. The value of EXT depends on the nature of the event whose delivery encountered a nested exception: if that event is a software interrupt, EXT is 0; otherwise, EXT is 1.

```

IFPE = 0

THEN

GOTO REAL-ADDRESS-MODE;

ELSE (* PE = 1 *)

IF (VM = 1 and IOPL < 3 AND INT n)

THEN

#GP(0); (* Bit 0 of error code is 0 because INT n *)

ELSE (* Protected mode, IA-32e mode, or virtual-8086 mode interrupt *)

IF (IA32\_EFER.LMA = 0)

THEN (* Protected mode, or virtual-8086 mode interrupt *)

GOTO PROTECTED-MODE:

ELSE (* IA-32e mode interrupt *)

GOTO IA-32e-MODE;

FI;

FI;

FI:

REAL-ADDRESS-MODE:

IF ((vector_number « 2) + 3) is not within IDT limit

THEN #GP; FI;

IF stack not large enough for a 6-byte return information

THEN #SS; FI;

Push (EFLAGS[15:0]);

IF \leftarrow 0; (* Clear interrupt flag *)

TF \leftarrow 0; (* Clear trap flag *)

AC \leftarrow 0; (* Clear AC flag *)

Push(CS);

Push(IP);

(* No error codes are pushed in real-address mode*)

CS \leftarrow IDT(Descriptor (vector_number \ll 2), selector));

EIP ← IDT(Descriptor (vector_number « 2), offset)); (* 16 bit offset AND 0000FFFFH *)

END;

PROTECTED-MODE:

IF ((vector_number « 3) + 7) is not within IDT limits

or selected IDT descriptor is not an interrupt-, trap-, or task-gate type

THEN #GP(error_code(vector_number,1,EXT)); FI;

```

```

(* idt operand to error code set because vector is used *)

IF software interrupt (* Generated by INT n, INT3, or INTO *)

THEN

IF gate DPL < CPL (* PE = 1, DPL < CPL, software interrupt *)

THEN #GP(error_code(vector_number,1,0)); FI;

(* idt operand to error_code set because vector is used *)

(* ext operand to error_code is 0 because INT n, INT3, or INT0*)

FI;

IF gate not present

THEN #NP(error_code(vector_number,1,EXT)); FI;

(* idt operand to error_code set because vector is used *)

IF task gate (* Specified in the selected interrupt table descriptor *)

THEN GOTO TASK-GATE;

ELSE GOTO TRAP-OR-INTERRUPT-GATE; (* PE = 1, trap/interrupt gate *)

FI;

END;

IA-32e-MODE:

IF INTO and CS.L = 1 (64-bit mode)

THEN #UD;

FI;

IF ((vector_number « 4) + 15) is not in IDT limits

or selected IDT descriptor is not an interrupt-, or trap-gate type

THEN #GP(error code(vector number,1,EXT));

(* idt operand to error_code set because vector is used *)

FI:

IF software interrupt (* Generated by INT n, INT 3, or INTO *)

THEN

IF gate DPL < CPL (* PE = 1, DPL < CPL, software interrupt *)

THEN #GP(error_code(vector_number,1,0));

(* idt operand to error code set because vector is used *)

(* ext operand to error_code is 0 because INT n, INT3, or INT0*)

FI;

FI;

IF gate not present

THEN #NP(error_code(vector_number,1,EXT));

(* idt operand to error_code set because vector is used *)

FI;

GOTO TRAP-OR-INTERRUPT-GATE; (* Trap/interrupt gate *)

END;

TASK-GATE: (* PE = 1, task gate *)

Read TSS selector in task gate (IDT descriptor);

IF local/global bit is set to local or index not within GDT limits

THEN #GP(error_code(TSS selector,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

Access TSS descriptor in GDT;

IF TSS descriptor specifies that the TSS is busy (low-order 5 bits set to 00001)

THEN #GP(TSS selector,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

IF TSS not present

THEN #NP(TSS selector,0,EXT)); FI;

```

FI; END; INTER-PRIVILEGE-LEVEL-INTERRUPT: (\* PE = 1, interrupt or trap gate, non-conforming code segment, DPL < CPL \*) IF (IA32\_EFER.LMA = 0) (\* Not IA-32e mode \*) THEN (\* Identify stack-segment selector for new privilege level in current TSS \*) IF current TSS is 32-bit THEN TSSstackAddress  $\leftarrow$  (new code-segment DPL  $\ll$  3) + 4; IF (TSSstackAddress + 5) > current TSS limit THEN #TS(error code(current TSS selector,0,EXT)); FI; (\* idt operand to error\_code is 0 because selector is used \*) NewSS  $\leftarrow$  2 bytes loaded from (TSS base + TSSstackAddress + 4); NewESP  $\leftarrow$  4 bytes loaded from (TSS base + TSSstackAddress); ELSE (\* current TSS is 16-bit \*) TSSstackAddress  $\leftarrow$  (new code-segment DPL  $\ll$  2) + 2 IF (TSSstackAddress + 3) > current TSS limit THEN #TS(error code(current TSS selector,0,EXT)); FI; (\* idt operand to error\_code is 0 because selector is used \*) NewSS  $\leftarrow$  2 bytes loaded from (TSS base + TSSstackAddress + 2); NewESP  $\leftarrow$  2 bytes loaded from (TSS base + TSSstackAddress); FI; IF NewSS is NULL THEN #TS(EXT); FI; IF NewSS index is not within its descriptor-table limits or NewSS RPL ≠ new code-segment DPL THEN #TS(error\_code(NewSS,0,EXT)); FI; (\* idt operand to error\_code is 0 because selector is used \*) Read new stack-segment descriptor for NewSS in GDT or LDT; IF new stack-segment DPL  $\neq$  new code-segment DPL or new stack-segment Type does not indicate writable data segment THEN #TS(error\_code(NewSS,0,EXT)); FI; (\* idt operand to error code is 0 because selector is used \*) IF NewSS is not present THEN #SS(error\_code(NewSS,0,EXT)); FI; (\* idt operand to error\_code is 0 because selector is used \*) ELSE (\* IA-32e mode \*) IF IDT-gate IST = 0 THEN TSSstackAddress  $\leftarrow$  (new code-segment DPL  $\ll$  3) + 4; ELSE TSSstackAddress  $\leftarrow$  (IDT gate IST  $\ll$  3) + 28; FI; IF (TSSstackAddress + 7) > current TSS limit THEN #TS(error\_code(current TSS selector,0,EXT); FI; (\* idt operand to error code is 0 because selector is used \*) NewRSP  $\leftarrow$  8 bytes loaded from (current TSS base + TSSstackAddress); NewSS  $\leftarrow$  new code-segment DPL; (\* NULL selector with RPL = new CPL \*) FI; IF IDT gate is 32-bit THEN

| IF new stack does not have room for 24 bytes (error code pushed)                           |     |

|--------------------------------------------------------------------------------------------|-----|

| or 20 bytes (no error code pushed)                                                         |     |

| THEN #SS(error_code(NewSS,0,EXT)); FI;                                                     |     |

| (* idt operand to error_code is 0 because selector is used *)                              |     |

| FI                                                                                         |     |

| ELSE                                                                                       |     |

| IF IDT gate is 16-bit                                                                      |     |

| THEN                                                                                       |     |

| IF new stack does not have room for 12 bytes (error code pushe                             | ed) |

| or 10 bytes (no error code pushed);                                                        |     |

| THEN #SS(error_code(NewSS,0,EXT)); FI;                                                     | 、   |

| (* idt operand to error_code is 0 because selector is used *                               | )   |

| ELSE (* 64-bit IDT gate*)                                                                  |     |

| IF StackAddress is non-canonical                                                           |     |

| THEN #SS(EXT); FI; (* Error code contains NULL selector *)                                 |     |

| FI;<br>FI;                                                                                 |     |

| IF (IA32_EFER.LMA = 0) (* Not IA-32e mode *)                                               |     |

| THEN                                                                                       |     |

| IF instruction pointer from IDT gate is not within new code-segment limits                 | S   |

| THEN #GP(EXT); FI; (* Error code contains NULL selector *)                                 |     |

| $ESP \leftarrow NewESP;$                                                                   |     |

| SS $\leftarrow$ NewSS; (* Segment descriptor information also loaded *)                    |     |

| ELSE (* IA-32e mode *)                                                                     |     |

| IF instruction pointer from IDT gate contains a non-canonical address                      |     |

| THEN #GP(EXT); FI; (* Error code contains NULL selector *)                                 |     |

| $RSP \leftarrow NewRSP \And FFFFFFFFFFFFFFFFFFFFFFFF$                                      |     |

| $SS \leftarrow NewSS;$                                                                     |     |

| FI;                                                                                        |     |

| IF IDT gate is 32-bit                                                                      |     |

|                                                                                            |     |

| CS:EIP $\leftarrow$ Gate(CS:EIP); (* Segment descriptor information also loaded *)<br>ELSE |     |

| IF IDT gate 16-bit                                                                         |     |

| THEN                                                                                       |     |

| $CS:IP \leftarrow Gate(CS:IP);$                                                            |     |

| (* Segment descriptor information also loaded *)                                           |     |

| ELSE (* 64-bit IDT gate *)                                                                 |     |

| $CS:RIP \leftarrow Gate(CS:RIP);$                                                          |     |

| (* Segment descriptor information also loaded *)                                           |     |

| FI;                                                                                        |     |

| FI;                                                                                        |     |

| IF IDT gate is 32-bit                                                                      |     |

| THEN                                                                                       |     |

| Push(far pointer to old stack);                                                            |     |

| (* Old SS and ESP, 3 words padded to 4 *)                                                  |     |

| Push(EFLAGS);                                                                              |     |

| Push(far pointer to return instruction);                                                   |     |

| (* Old CS and EIP, 3 words padded to 4 *)                                                  |     |

| Push(ErrorCode); (* If needed, 4 bytes *)                                                  |     |

```

ELSE

IF IDT gate 16-bit

THEN

Push(far pointer to old stack);

(* Old SS and SP, 2 words *)

Push(EFLAGS(15-0]);

Push(far pointer to return instruction);

(* Old CS and IP, 2 words *)

Push(ErrorCode); (* If needed, 2 bytes *)

ELSE (* 64-bit IDT gate *)

Push(far pointer to old stack);

(* Old SS and SP, each an 8-byte push *)

Push(RFLAGS); (* 8-byte push *)

Push(far pointer to return instruction);

(* Old CS and RIP, each an 8-byte push *)

Push(ErrorCode); (* If needed, 8-bytes *)

FI;

FI:

CPL \leftarrow new code-segment DPL;

CS(RPL) \leftarrow CPL;

IF IDT gate is interrupt gate

THEN IF \leftarrow 0 (* Interrupt flag set to 0, interrupts disabled *); FI;

TF \leftarrow 0;

VM \leftarrow 0;

RF \leftarrow 0;

NT \leftarrow 0;

END;

INTERRUPT-FROM-VIRTUAL-8086-MODE:

(* Identify stack-segment selector for privilege level 0 in current TSS *)

IF current TSS is 32-bit

THEN

IF TSS limit < 9

THEN #TS(error_code(current TSS selector,0,EXT)); FI;

(* idt operand to error code is 0 because selector is used *)

NewSS \leftarrow 2 bytes loaded from (current TSS base + 8);

NewESP \leftarrow 4 bytes loaded from (current TSS base + 4);

ELSE (* current TSS is 16-bit *)

IF TSS limit < 5

THEN #TS(error_code(current TSS selector,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

NewSS \leftarrow 2 bytes loaded from (current TSS base + 4);

NewESP \leftarrow 2 bytes loaded from (current TSS base + 2);

FI;

IF NewSS is NULL

THEN #TS(EXT); FI; (* Error code contains NULL selector *)

IF NewSS index is not within its descriptor table limits

or NewSS RPL \neq 0

THEN #TS(error_code(NewSS,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

Read new stack-segment descriptor for NewSS in GDT or LDT;

```

```

IF new stack-segment DPL \neq 0 or stack segment does not indicate writable data segment

THEN #TS(error_code(NewSS,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

IF new stack segment not present

THEN #SS(error_code(NewSS,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

IF IDT gate is 32-bit

THEN

IF new stack does not have room for 40 bytes (error code pushed)

or 36 bytes (no error code pushed)

THEN #SS(error_code(NewSS,0,EXT)); FI;

(* idt operand to error code is 0 because selector is used *)

ELSE (* IDT gate is 16-bit)

IF new stack does not have room for 20 bytes (error code pushed)

or 18 bytes (no error code pushed)

THEN #SS(error_code(NewSS,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

FI:

IF instruction pointer from IDT gate is not within new code-segment limits

THEN #GP(EXT); FI; (* Error code contains NULL selector *)

tempEFLAGS \leftarrow EFLAGS;

VM \leftarrow 0;

TF \leftarrow 0;

RF \leftarrow 0;

NT \leftarrow 0;

IF service through interrupt gate

THEN IF = 0; FI;

TempSS \leftarrow SS;

TempESP \leftarrow ESP;

SS \leftarrow NewSS;

ESP \leftarrow NewESP;

(* Following pushes are 16 bits for 16-bit IDT gates and 32 bits for 32-bit IDT gates;

Segment selector pushes in 32-bit mode are padded to two words *)

Push(GS);

Push(FS);

Push(DS);

Push(ES);

Push(TempSS);

Push(TempESP);

Push(TempEFlags);

Push(CS);

Push(EIP);

GS \leftarrow 0; (* Segment registers made NULL, invalid for use in protected mode *)

FS \leftarrow 0;

DS \leftarrow 0;

ES \leftarrow 0;

CS:IP ← Gate(CS); (* Segment descriptor information also loaded *)

IF OperandSize = 32

THEN

EIP \leftarrow Gate(instruction pointer);

```

```

ELSE (* OperandSize is 16 *)

EIP ← Gate(instruction pointer) AND 0000FFFFH;

FI:

(* Start execution of new routine in Protected Mode *)

END;

INTRA-PRIVILEGE-LEVEL-INTERRUPT:

(* PE = 1, DPL = CPL or conforming segment *)

IF IA32 EFER.LMA = 1 (* IA-32e mode *)

IF IDT-descriptor IST \neq 0

THEN

TSSstackAddress \leftarrow (IDT-descriptor IST \ll 3) + 28;

IF (TSSstackAddress + 7) > TSS limit

THEN #TS(error_code(current TSS selector,0,EXT)); FI;

(* idt operand to error_code is 0 because selector is used *)

NewRSP ← 8 bytes loaded from (current TSS base + TSSstackAddress);

FI;

IF 32-bit gate (* implies IA32_EFER.LMA = 0 *)

THEN

IF current stack does not have room for 16 bytes (error code pushed)

or 12 bytes (no error code pushed)

THEN #SS(EXT); FI; (* Error code contains NULL selector *)

ELSE IF 16-bit gate (* implies IA32_EFER.LMA = 0 *)

IF current stack does not have room for 8 bytes (error code pushed)

or 6 bytes (no error code pushed)

THEN #SS(EXT); FI; (* Error code contains NULL selector *)

ELSE (* IA32_EFER.LMA = 1, 64-bit gate*)

IF NewRSP contains a non-canonical address

THEN #SS(EXT); (* Error code contains NULL selector *)

FI;

FI;

IF (IA32_EFER.LMA = 0) (* Not IA-32e mode *)

THEN

IF instruction pointer from IDT gate is not within new code-segment limit

THEN #GP(EXT); FI; (* Error code contains NULL selector *)

ELSE

IF instruction pointer from IDT gate contains a non-canonical address

THEN #GP(EXT); FI; (* Error code contains NULL selector *)

RSP ← NewRSP & FFFFFFFFFFFFFFFFFF;

FI;

IF IDT gate is 32-bit (* implies IA32_EFER.LMA = 0 *)

THEN

Push (EFLAGS);

Push (far pointer to return instruction); (* 3 words padded to 4 *)

CS:EIP ← Gate(CS:EIP); (* Segment descriptor information also loaded *)

Push (ErrorCode); (* If any *)

ELSE

IF IDT gate is 16-bit (* implies IA32_EFER.LMA = 0 *)

THEN

Push (FLAGS);

Push (far pointer to return location); (* 2 words *)

```

```

CS:IP \leftarrow Gate(CS:IP);

(* Segment descriptor information also loaded *)

Push (ErrorCode); (* If any *)

ELSE (* IA32_EFER.LMA = 1, 64-bit gate*)

Push(far pointer to old stack);

(* Old SS and SP, each an 8-byte push *)

Push(RFLAGS); (* 8-byte push *)

Push(far pointer to return instruction);

(* Old CS and RIP, each an 8-byte push *)

Push(ErrorCode); (* If needed, 8 bytes *)

CS:RIP \leftarrow GATE(CS:RIP);

(* Segment descriptor information also loaded *)

FI;

FI;

CS(RPL) \leftarrow CPL;

IF IDT gate is interrupt gate

THEN IF \leftarrow 0; FI; (* Interrupt flag set to 0; interrupts disabled *)

TF \leftarrow 0;

NT \leftarrow 0;

VM \leftarrow 0;

RF \leftarrow 0;

END;

```

```

• • •

```

#### **Protected Mode Exceptions**

|                 | F                                                                                                                                                           |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| #GP(error_code) | If the instruction pointer in the IDT or in the interrupt-, trap-, or task gate is beyond the code segment limits.                                          |  |  |  |

|                 | If the segment selector in the interrupt-, trap-, or task gate is NULL.                                                                                     |  |  |  |

|                 | If an interrupt-, trap-, or task gate, code segment, or TSS segment selector index is outside its descriptor table limits.                                  |  |  |  |

|                 | If the interrupt vector number is outside the IDT limits.                                                                                                   |  |  |  |

|                 | If an IDT descriptor is not an interrupt-, trap-, or task-descriptor.                                                                                       |  |  |  |

|                 | If an interrupt is generated by the INT <i>n</i> , INT 3, or INTO instruction and the DPL of an interrupt-, trap-, or task-descriptor is less than the CPL. |  |  |  |

|                 | If the segment selector in an interrupt- or trap-gate does not point to a segment descriptor for a code segment.                                            |  |  |  |

|                 | If the segment selector for a TSS has its local/global bit set for local.                                                                                   |  |  |  |

|                 | If a TSS segment descriptor specifies that the TSS is busy or not available.                                                                                |  |  |  |

| #SS(error_code) | If pushing the return address, flags, or error code onto the stack exceeds the bounds of the stack segment and no stack switch occurs.                      |  |  |  |

|                 | If the SS register is being loaded and the segment pointed to is marked not present.                                                                        |  |  |  |

|                 | If pushing the return address, flags, error code, or stack segment<br>pointer exceeds the bounds of the new stack segment when a stack<br>switch occurs.    |  |  |  |

| #NP(error_code) | If code segment, interrupt-, trap-, or task gate, or TSS is not present.                                                                                                          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #TS(error_code) | If the RPL of the stack segment selector in the TSS is not equal to the DPL of the code segment being accessed by the interrupt or trap gate.                                     |

|                 | If DPL of the stack segment descriptor pointed to by the stack segment selector in the TSS is not equal to the DPL of the code segment descriptor for the interrupt or trap gate. |

|                 | If the stack segment selector in the TSS is NULL.                                                                                                                                 |

|                 | If the stack segment for the TSS is not a writable data segment.                                                                                                                  |

|                 | If segment-selector index for stack segment is outside descriptor table limits.                                                                                                   |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                           |

| #UD             | If the LOCK prefix is used.                                                                                                                                                       |

| #AC(EXT)        | If alignment checking is enabled, the gate DPL is 3, and a stack push is unaligned.                                                                                               |

|                 |                                                                                                                                                                                   |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                   |

|-----|-------------------------------------------------------------------------------------------------------------|

|     | If the interrupt vector number is outside the IDT limits.                                                   |

| #SS | If stack limit violation on push.                                                                           |

|     | If pushing the return address, flags, or error code onto the stack exceeds the bounds of the stack segment. |

| #UD | If the LOCK prefix is used.                                                                                 |

#### Virtual-8086 Mode Exceptions

#GP(error\_code) (For INT n, INTO, or BOUND instruction) If the IOPL is less than 3 or the DPL of the interrupt-, trap-, or task-gate descriptor is not equal to 3. If the instruction pointer in the IDT or in the interrupt-, trap-, or task gate is beyond the code segment limits. If the segment selector in the interrupt-, trap-, or task gate is NULL. If a interrupt-, trap-, or task gate, code segment, or TSS segment selector index is outside its descriptor table limits. If the interrupt vector number is outside the IDT limits. If an IDT descriptor is not an interrupt-, trap-, or task-descriptor. If an interrupt is generated by the INT *n* instruction and the DPL of an interrupt-, trap-, or task-descriptor is less than the CPL. If the segment selector in an interrupt- or trap-gate does not point to a segment descriptor for a code segment. If the segment selector for a TSS has its local/global bit set for local. #SS(error\_code) If the SS register is being loaded and the segment pointed to is marked not present.

> If pushing the return address, flags, error code, stack segment pointer, or data segments exceeds the bounds of the stack

segment.

| #NP(error_code) | If code segment, interrupt-, trap-, or task gate, or TSS is not present.                                                                                          |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #TS(error_code) | If the RPL of the stack segment selector in the TSS is not equal to<br>the DPL of the code segment being accessed by the interrupt or trap<br>gate.               |

|                 | If DPL of the stack segment descriptor for the TSS's stack segment<br>is not equal to the DPL of the code segment descriptor for the inter-<br>rupt or trap gate. |

|                 | If the stack segment selector in the TSS is NULL.                                                                                                                 |

|                 | If the stack segment for the TSS is not a writable data segment.                                                                                                  |

|                 | If segment-selector index for stack segment is outside descriptor table limits.                                                                                   |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                           |

| #BP             | If the INT 3 instruction is executed.                                                                                                                             |

| #OF             | If the INTO instruction is executed and the OF flag is set.                                                                                                       |

| #UD             | If the LOCK prefix is used.                                                                                                                                       |

| #AC(EXT)        | If alignment checking is enabled, the gate DPL is 3, and a stack push is unaligned.                                                                               |

## Compatibility Mode Exceptions

Same exceptions as in protected mode.

## 64-Bit Mode Exceptions

| #GP(€ | error_code) | If the instruction pointer in the 64-bit interrupt gate or 64-bit trap gate is non-canonical.                                                                      |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |             | If the segment selector in the 64-bit interrupt or trap gate is NULL.                                                                                              |

|       |             | If the interrupt vector number is outside the IDT limits.                                                                                                          |

|       |             | If the interrupt vector number points to a gate which is in non-<br>canonical space.                                                                               |

|       |             | If the interrupt vector number points to a descriptor which is not a 64-bit interrupt gate or 64-bit trap gate.                                                    |

|       |             | If the descriptor pointed to by the gate selector is outside the descriptor table limit.                                                                           |

|       |             | If the descriptor pointed to by the gate selector is in non-canonical space.                                                                                       |

|       |             | If the descriptor pointed to by the gate selector is not a code segment.                                                                                           |

|       |             | If the descriptor pointed to by the gate selector doesn't have the L-<br>bit set, or has both the L-bit and D-bit set.                                             |

|       |             | If the descriptor pointed to by the gate selector has DPL > CPL.                                                                                                   |

| #SS(e | error_code) | If a push of the old EFLAGS, CS selector, EIP, or error code is in non-<br>canonical space with no stack switch.                                                   |

|       |             | If a push of the old SS selector, ESP, EFLAGS, CS selector, EIP, or error code is in non-canonical space on a stack switch (either CPL change or no-CPL with IST). |

| #NP(€ | error_code) | If the 64-bit interrupt-gate, 64-bit trap-gate, or code segment is not present.                                                                                    |

|       |             |                                                                                                                                                                    |

| #TS(error_code) | If an attempt to load RSP from the TSS causes an access to non-canonical space.     |

|-----------------|-------------------------------------------------------------------------------------|

|                 | If the RSP from the TSS is outside descriptor table limits.                         |

| #PF(fault-code) | If a page fault occurs.                                                             |

| #UD             | If the LOCK prefix is used.                                                         |

|                 | If INTO.                                                                            |

| #AC(EXT)        | If alignment checking is enabled, the gate DPL is 3, and a stack push is unaligned. |

#### •••

### IRET/IRETD—Interrupt Return

#### ...

#### Operation

```

IF PE = 0

THEN

GOTO REAL-ADDRESS-MODE;

ELSE

IF (IA32_EFER.LMA = 0)

THEN (* Protected mode *)

GOTO PROTECTED-MODE;

ELSE (* IA-32e mode *)

GOTO IA-32e-MODE;

FI;

FI;

REAL-ADDRESS-MODE;

IF OperandSize = 32

THEN

IF top 12 bytes of stack not within stack limits

THEN #SS; FI;

tempEIP \leftarrow 4 bytes at end of stack

IF tempEIP[31:16] is not zero THEN #GP(0); FI;

EIP \leftarrow Pop();

CS \leftarrow Pop(); (* 32-bit pop, high-order 16 bits discarded *)

tempEFLAGS \leftarrow Pop();

EFLAGS ← (tempEFLAGS AND 257FD5H) OR (EFLAGS AND 1A0000H);

ELSE (* OperandSize = 16 *)

IF top 6 bytes of stack are not within stack limits

THEN #SS; FI;

EIP \leftarrow Pop(); (* 16-bit pop; clear upper 16 bits *)

CS \leftarrow Pop(); (* 16-bit pop *)

EFLAGS[15:0] \leftarrow Pop();

FI;

END;

PROTECTED-MODE:

IF VM = 1 (* Virtual-8086 mode: PE = 1, VM = 1 *)

THEN

```

```

GOTO RETURN-FROM-VIRTUAL-8086-MODE; (* PE = 1, VM = 1 *)

FI;

IF NT = 1

THEN

GOTO TASK-RETURN; (* PE = 1, VM = 0, NT = 1 *)

FI;

IF OperandSize = 32

THEN

IF top 12 bytes of stack not within stack limits

THEN #SS(0); FI;

tempEIP \leftarrow Pop();

tempCS \leftarrow Pop();

tempEFLAGS \leftarrow Pop();

ELSE (* OperandSize = 16 *)

IF top 6 bytes of stack are not within stack limits

THEN #SS(0); FI;

tempEIP \leftarrow Pop();

tempCS \leftarrow Pop();

tempEFLAGS \leftarrow Pop();

tempEIP \leftarrow tempEIP AND FFFFH;

tempEFLAGS ← tempEFLAGS AND FFFFH;

FI;

IF tempEFLAGS(VM) = 1 and CPL = 0

THEN

GOTO RETURN-TO-VIRTUAL-8086-MODE;

ELSE

GOTO PROTECTED-MODE-RETURN;

FI;

IA-32e-MODE:

IF NT = 1

THEN #GP(0);

ELSE IF OperandSize = 32

THEN

IF top 12 bytes of stack not within stack limits

THEN #SS(0); FI;

tempEIP \leftarrow Pop();

tempCS \leftarrow Pop();

tempEFLAGS \leftarrow Pop();

ELSE IF OperandSize = 16

THEN

IF top 6 bytes of stack are not within stack limits

THEN #SS(0); FI;

tempEIP \leftarrow Pop();

tempCS \leftarrow Pop();

tempEFLAGS \leftarrow Pop();

tempEIP \leftarrow tempEIP AND FFFFH;

tempEFLAGS ← tempEFLAGS AND FFFFH;

FI;

ELSE (* OperandSize = 64 *)

THEN

```

Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual Documentation Changes

```

tempRIP \leftarrow Pop();

tempCS \leftarrow Pop();

tempEFLAGS \leftarrow Pop();

tempRSP \leftarrow Pop();

tempSS \leftarrow Pop();

```

```

FI;

```

GOTO IA-32e-MODE-RETURN;

...

# JMP—Jump

...

#### Operation

```

IF near jump

IF 64-bit Mode

THEN

IF near relative jump

THEN

tempRIP \leftarrow RIP + DEST; (* RIP is instruction following JMP instruction*)

ELSE (* Near absolute jump *)

tempRIP \leftarrow DEST;

FI;

ELSE

IF near relative jump

THEN

tempEIP \leftarrow EIP + DEST; (* EIP is instruction following JMP instruction*)

ELSE (* Near absolute jump *)

tempEIP \leftarrow DEST;

FI;

FI;

IF (IA32_EFER.LMA = 0 or target mode = Compatibility mode)

and tempEIP outside code segment limit

THEN #GP(0); FI

IF 64-bit mode and tempRIP is not canonical

THEN #GP(0);

FI;

IF OperandSize = 32

THEN

EIP \leftarrow tempEIP;

ELSE

IF OperandSize = 16

THEN (* OperandSize = 16 *)

EIP ← tempEIP AND 0000FFFFH;

ELSE (* OperandSize = 64)

RIP \leftarrow tempRIP;

FI;

FI;

FI;

```

```

IF far jump and (PE = 0 or (PE = 1 AND VM = 1)) (* Real-address or virtual-8086 mode *)

THEN

tempEIP \leftarrow DEST(Offset); (* DEST is ptr16:32 or [m16:32] *)

IF tempEIP is beyond code segment limit

THEN #GP(0); FI;

CS \leftarrow DEST(segment selector); (* DEST is ptr16:32 or [m16:32] *)

IF OperandSize = 32

THEN

EIP \leftarrow tempEIP; (* DEST is ptr16:32 or [m16:32] *)

ELSE (* OperandSize = 16 *)

EIP ← tempEIP AND 0000FFFFH; (* Clear upper 16 bits *)

FI;

FI;

IF far jump and (PE = 1 and VM = 0)

(* IA-32e mode or protected mode, not virtual-8086 mode *)

THEN

IF effective address in the CS, DS, ES, FS, GS, or SS segment is illegal

or segment selector in target operand NULL

THEN #GP(0); FI;

IF segment selector index not within descriptor table limits

THEN #GP(new selector); FI;

Read type and access rights of segment descriptor;

IF (EFER.LMA = 0)

THEN

IF segment type is not a conforming or nonconforming code

segment, call gate, task gate, or TSS

THEN #GP(segment selector); FI;

ELSE

IF segment type is not a conforming or nonconforming code segment

call gate

THEN #GP(segment selector); FI;

FI:

Depending on type and access rights:

GO TO CONFORMING-CODE-SEGMENT;

GO TO NONCONFORMING-CODE-SEGMENT;

GO TO CALL-GATE:

GO TO TASK-GATE:

GO TO TASK-STATE-SEGMENT;

ELSE

#GP(segment selector);

FI;

. . .

LSL—Load Segment Limit

```

#### **Real-Address Mode Exceptions**

#UD

The LSL instruction cannot be executed in real-address mode.

#UD

#### Virtual-8086 Mode Exceptions

The LSL instruction cannot be executed in virtual-8086 mode.

#### 3. Updates to Chapter 4, Volume 2B

Change bars show changes to Chapter 4 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z.

\_\_\_\_\_

## PMOVMSKB—Move Byte Mask

| Opcode              | Instruction          | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                            |

|---------------------|----------------------|-----------|----------------|---------------------|----------------------------------------------------------------------------------------|

| 0F D7 <i>Ir</i>     | PMOVMSKB reg,<br>mm  | A         | Valid          | Valid               | Move a byte mask of <i>mm</i> to <i>reg</i> . The upper bits of r32 or r64 are zeroed  |

| 66 0F D7 / <i>r</i> | PMOVMSKB reg,<br>xmm | A         | Valid          | Valid               | Move a byte mask of <i>xmm</i> to <i>reg</i> . The upper bits of r32 or r64 are zeroed |

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| А     | ModRM:reg (w) | ModRM:reg (r) | NA        | NA        |

#### Description

Creates a mask made up of the most significant bit of each byte of the source operand (second operand) and stores the result in the low byte or word of the destination operand (first operand). The source operand is an MMX technology register or an XMM register; the destination operand is a general-purpose register. When operating on 64-bit operands, the byte mask is 8 bits; when operating on 128-bit operands, the byte mask is 16-bits.

In 64-bit mode, the instruction can access additional registers (XMM8-XMM15, R8-R15) when used with a REX.R prefix. The default operand size is 64-bit in 64-bit mode.

### PUSH—Push Word, Doubleword or Quadword Onto the Stack

| Opcode* | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                  |

|---------|-------------|-----------|----------------|---------------------|------------------------------------------------------------------------------|

| <br>68  | PUSH imm16  | C         | Valid          | Valid               | Push imm16. Stack pointer<br>is decremented by the size<br>of stack pointer. |

|         |             |           |                |                     |                                                                              |

. . .

Table 4-12 lists valid indices of the general-purpose and special-purpose performance counters according to the derived DisplayFamily\_DisplayModel values of CPUID encoding for each processor family (see CPUID instruction in Chapter 3, "Instruction Set Reference, A-M" in the *Intel*<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A).

| Processor Family                                                                                                                                                     | DisplayFamily_Display<br>Model/ Other<br>Signatures                             | Valid PMC<br>Index Range | General-<br>purpose<br>Counters |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|---------------------------------|

| P6                                                                                                                                                                   | 06H_01H, 06H_03H,<br>06H_05H, 06H_06H,<br>06H_07H, 06H_08H,<br>06H_0AH, 06H_0BH | 0, 1                     | 0, 1                            |

| Pentium <sup>®</sup> 4, Intel <sup>®</sup> Xeon<br>processors                                                                                                        | 0FH_00H, 0FH_01H,<br>0FH_02H                                                    | $\geq$ 0 and $\leq$ 17   | $\geq$ 0 and $\leq$ 17          |

| Pentium 4, Intel Xeon processors                                                                                                                                     | (OFH_O3H, OFH_O4H,<br>OFH_O6H) and (L3 is<br>absent)                            | $\geq$ 0 and $\leq$ 17   | $\geq$ 0 and $\leq$ 17          |