# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

March 2012

**Notice:** The  $Intel^{(R)}$  64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-035

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Intel, the Intel logo, Pentium, Xeon, Intel NetBurst, Intel Core, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo, Intel Core 2 Extreme, Intel Pentium D, Itanium, Intel SpeedStep, MMX, Intel Atom, and VTune are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright © 1997-2012 Intel Corporation. All rights reserved.

# Contents

| Revision History          | <br> | <br>• | • |  | • |       |  | • | • |  | • | • | • |  | • |       | •   | 4 |

|---------------------------|------|-------|---|--|---|-------|--|---|---|--|---|---|---|--|---|-------|-----|---|

| Preface                   | <br> | <br>• | • |  | • |       |  | • | • |  | • | • | • |  |   |       | •   | 7 |

| Summary Tables of Changes |      |       |   |  | • |       |  |   | • |  |   |   |   |  | • |       | . : | 8 |

| Documentation Changes     | <br> | <br>• | • |  | • | <br>• |  |   | • |  | • |   | • |  | • | <br>• | . ' | 9 |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                      | Date           |

|----------|--------------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul>    | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul>    | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul>    | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul>    | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul>    | June 2010      |

| -029     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | September 2010 |

| -030     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | January 2011   |

| -031     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | April 2011     |

| -032     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-14</li></ul>    | May 2011       |

| -033     | <ul> <li>Removed Documentation Changes 1-14</li> <li>Added Documentation Changes 1-38</li> </ul> | October 2011   |

| -034     | <ul><li>Removed Documentation Changes 1-38</li><li>Added Documentation Changes 1-16</li></ul>    | December 2011  |

| -035     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul>    | March 2012     |

§

**Revision History**

6

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                               | Document<br>Number/Location |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture</i>                | 253665                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M</i>   | 253666                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z</i>   | 253667                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2C: Instruction Set Reference</i>        | 326018                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1</i> | 253668                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2</i> | 253669                      |

| <i>Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3C: System Programming Guide, Part 3</i> | 326019                      |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(R)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes**

|    | No. | DOCUMENTATION CHANGES            |

|----|-----|----------------------------------|

| 1  | 1   | Updates to Chapter 1, Volume 1   |

| 1  | 2   | Updates to Chapter 1, Volume 2A  |

|    | 3   | Updates to Chapter 3, Volume 2A  |

|    | 4   | Updates to Chapter 4, Volume 2B  |

|    | 5   | Updates to Appendix A, Volume 2C |

|    | 6   | Updates to Appendix B, Volume 2C |

|    | 7   | Updates to Chapter 1, Volume 3A  |

|    | 8   | Updates to Chapter 4, Volume 3A  |

|    | 9   | Updates to Chapter 10, Volume 3A |

|    | 10  | Updates to Chapter 14, Volume 3B |

|    | 11  | Updates to Chapter 17, Volume 3B |

| 1  | 12  | Updates to Chapter 18, Volume 3B |

| 1  | 13  | Updates to Chapter 19, Volume 3B |

| I. | 14  | Updates to Chapter 25, Volume 3C |

| I. | 15  | Updates to Chapter 26, Volume 3C |

| 1  | 16  | Updates to Chapter 27, Volume 3C |

| 1  | 17  | Update to Volume 3C              |

| I. | 18  | Updates to Chapter 33, Volume 3C |

# **Documentation Changes**

#### 1. Updates to Chapter 1, Volume 1

Change bars show changes to Chapter 1 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 1:* Basic Architecture.

\_\_\_\_\_

...

# 1.1 INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>TM</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor

- Intel<sup>®</sup> Core<sup>™</sup>i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3 family

- Intel<sup>®</sup> Core<sup>TM</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>TM</sup> Duo, Intel<sup>®</sup> Core<sup>TM</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200 and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>TM</sup>2 Duo, Intel<sup>®</sup> Core<sup>TM</sup>2 Quad, and Intel<sup>®</sup> Core<sup>TM</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>TM</sup> microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000, X9000 series, Intel<sup>®</sup> Core<sup>™</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>TM</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>TM</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>TM</sup>i7 processor and the Intel<sup>®</sup> Core<sup>TM</sup>i5 processor are based on the Intel<sup>®</sup> microarchitecture code name Nehalem and support Intel 64 architecture.

Processors based on  ${\rm Intel}^{\textcircled{R}}$  microarchitecture code name Westmere support Intel 64 architecture.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>TM</sup> Solo, Intel<sup>®</sup> Core<sup>TM</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>TM</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3 family, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup> 2 Duo, Intel<sup>®</sup> Core<sup>™</sup> 2 Extreme processors, Intel Core 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors.

Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

2.

# Updates to Chapter 1, Volume 2A

Change bars show changes to Chapter 1 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 2A:* Instruction Set Reference, A-L.

•••

. . .

# 1.1 INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>™</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup>i7 processor

- Intel<sup>®</sup> Core<sup>™</sup>i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3 family

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>m</sup> Duo, Intel<sup>®</sup> Core<sup>m</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200, and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>m</sup>2 Duo, Intel<sup>®</sup> Core<sup>m</sup>2 Quad, and Intel<sup>®</sup> Core<sup>m</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>m</sup> microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>TM</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>TM</sup>2 Extreme processors QX9000, X9000 series, Intel<sup>®</sup> Core<sup>TM</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>TM</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>TM</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>TM</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>TM</sup> i7 processor and the Intel<sup>®</sup> Core<sup>TM</sup> i5 processor are based on the Intel<sup>®</sup> microarchitecture code name Nehalem and support Intel 64 architecture.

Processors based on  ${\rm Intel}^{(\! 8\!)}$  microarchitecture code name Westmere support Intel 64 architecture.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>™</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3 family, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup> 2 Duo, Intel<sup>®</sup> Core<sup>™</sup> 2 Extreme, Intel<sup>®</sup> Core<sup>™</sup> 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors.

Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

...

#### 3. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 2A:* Instruction Set Reference, A-L.

\_\_\_\_\_

•••

#### AAS—ASCII Adjust AL After Subtraction

| Opcode | Instruction | Op/<br>En | 64-bit<br>Mode | Compat/<br>Leg Mode | Description                        |

|--------|-------------|-----------|----------------|---------------------|------------------------------------|

| ЗF     | AAS         | NP        | Invalid        | Valid               | ASCII adjust AL after subtraction. |

|       |           | Instruction Operand 6 | Encoding  |           |

|-------|-----------|-----------------------|-----------|-----------|

| Op/En | Operand 1 | Operand 2             | Operand 3 | Operand 4 |

| NP    | NA        | NA                    | NA        | NA        |

#### Description

Adjusts the result of the subtraction of two unpacked BCD values to create a unpacked BCD result. The AL register is the implied source and destination operand for this instruction. The AAS instruction is only useful when it follows a SUB instruction that subtracts (binary subtraction) one unpacked BCD value from another and stores a byte result in the AL register. The AAA instruction then adjusts the contents of the AL register to contain the correct 1-digit unpacked BCD result.

If the subtraction produced a decimal carry, the AH register decrements by 1, and the CF and AF flags are set. If no decimal carry occurred, the CF and AF flags are cleared, and the AH register is unchanged. In either case, the AL register is left with its top four bits set to 0.

This instruction executes as described in compatibility mode and legacy mode. It is not valid in 64-bit mode.

#### Operation

```

IF 64-bit mode

THEN

#UD;

ELSE

IF ((AL AND OFH) > 9) or (AF = 1)

THEN

AX \leftarrow AX - 6;

AH \leftarrow AH - 1;

AF \leftarrow 1;

CF \leftarrow 1;

AL \leftarrow AL AND OFH;

ELSE

```

$$CF \leftarrow 0;$$

$AF \leftarrow 0;$

$AL \leftarrow AL AND OFH;$

FI;

FI;

...

| Opcode                         | Instruction             | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                  |

|--------------------------------|-------------------------|-----------|----------------|---------------------|----------------------------------------------|

| F2 0F 38 F0 <i>/r</i>          | CRC32 <i>r32, r/m8</i>  | RM        | Valid          | Valid               | Accumulate CRC32 on <i>r/m8</i> .            |

| F2 REX OF 38<br>F0 <i>/r</i>   | CRC32 <i>r32, r/m8*</i> | RM        | Valid          | N.E.                | Accumulate CRC32 on <i>r/m8.</i>             |

| F2 0F 38 F1 <i>/r</i>          | CRC32 <i>r32, r/m16</i> | RM        | Valid          | Valid               | Accumulate CRC32 on r/<br>m16.               |

| F2 0F 38 F1 <i>/r</i>          | CRC32 <i>r32, r/m32</i> | RM        | Valid          | Valid               | Accumulate CRC32 on r/<br>m32.               |

| F2 REX.W OF 38<br>F0 <i>/r</i> | CRC32 <i>r64, r/m8</i>  | RM        | Valid          | N.E.                | Accumulate CRC32 on <i>r/m8.</i>             |

| F2 REX.W OF 38<br>F1 <i>/r</i> | CRC32 <i>r64, r/m64</i> | RM        | Valid          | N.E.                | Accumulate CRC32 on <i>r/</i><br><i>m64.</i> |

#### NOTES:

\*In 64-bit mode, r/m8 can not be encoded to access the following byte registers if a REX prefix is used: AH, BH, CH, DH.

|       |                  | Instruction Operand E | ncoding   |           |

|-------|------------------|-----------------------|-----------|-----------|

| Op/En | Operand 1        | Operand 2             | Operand 3 | Operand 4 |

| RM    | ModRM:reg (r, w) | ModRM:r/m (r)         | NA        | NA        |

#### Description

Starting with an initial value in the first operand (destination operand), accumulates a CRC32 (polynomial 0x11EDC6F41) value for the second operand (source operand) and stores the result in the destination operand. The source operand can be a register or a memory location. The destination operand must be an r32 or r64 register. If the destination is an r64 register, then the 32-bit result is stored in the least significant double word and 00000000H is stored in the most significant double word of the r64 register.

The initial value supplied in the destination operand is a double word integer stored in the r32 register or the least significant double word of the r64 register. To incrementally accumulate a CRC32 value, software retains the result of the previous CRC32 operation in the destination operand, then executes the CRC32 instruction again with new input data in the source operand. Data contained in the source operand is processed in reflected bit order. This means that the most significant bit of the source operand is treated as the least significant bit of the quotient, and so on, for all the bits of the source operand in reflected bit order. This means that the most significant bit of the resulting CRC (bit 31) is stored in the least significant bit of the destination operand (bit 0), and so on, for all the bits of the CRC.

#### Operation

#### Notes:

BIT\_REFLECT64: DST[63-0] = SRC[0-63] BIT\_REFLECT32: DST[31-0] = SRC[0-31] BIT\_REFLECT16: DST[15-0] = SRC[0-15] BIT\_REFLECT8: DST[7-0] = SRC[0-7] MOD2: Remainder from Polynomial division modulus 2

CRC32 instruction for 64-bit source operand and 64-bit destination operand:

$$\begin{split} \mathsf{TEMP1[63-0]} &\leftarrow \mathsf{BIT\_REFLECT64} (\mathsf{SRC[63-0]}) \\ \mathsf{TEMP2[31-0]} &\leftarrow \mathsf{BIT\_REFLECT32} (\mathsf{DEST[31-0]}) \\ \mathsf{TEMP3[95-0]} &\leftarrow \mathsf{TEMP1[63-0]} &\ll 32 \\ \mathsf{TEMP4[95-0]} &\leftarrow \mathsf{TEMP2[31-0]} &\ll 64 \\ \mathsf{TEMP5[95-0]} &\leftarrow \mathsf{TEMP3[95-0]} \mathsf{XOR} \mathsf{TEMP4[95-0]} \\ \mathsf{TEMP6[31-0]} &\leftarrow \mathsf{TEMP5[95-0]} \mathsf{MOD2} \mathsf{11EDC6F41H} \\ \mathsf{DEST[31-0]} &\leftarrow \mathsf{BIT\_REFLECT} (\mathsf{TEMP6[31-0]}) \\ \mathsf{DEST[63-32]} &\leftarrow \mathsf{0000000H} \\ \end{split}$$

CRC32 instruction for 32-bit source operand and 32-bit destination operand:

TEMP1[31-0] ← BIT\_REFLECT32 (SRC[31-0]) TEMP2[31-0] ← BIT\_REFLECT32 (DEST[31-0]) TEMP3[63-0] ← TEMP1[31-0]  $\ll$  32 TEMP4[63-0] ← TEMP2[31-0]  $\ll$  32 TEMP5[63-0] ← TEMP3[63-0] XOR TEMP4[63-0] TEMP6[31-0] ← TEMP5[63-0] MOD2 11EDC6F41H DEST[31-0] ← BIT\_REFLECT (TEMP6[31-0])

CRC32 instruction for 16-bit source operand and 32-bit destination operand:

TEMP1[15-0] ← BIT\_REFLECT16 (SRC[15-0]) TEMP2[31-0] ← BIT\_REFLECT32 (DEST[31-0]) TEMP3[47-0] ← TEMP1[15-0]  $\ll$  32 TEMP4[47-0] ← TEMP2[31-0]  $\ll$  16 TEMP5[47-0] ← TEMP3[47-0] XOR TEMP4[47-0] TEMP6[31-0] ← TEMP5[47-0] MOD2 11EDC6F41H DEST[31-0] ← BIT\_REFLECT (TEMP6[31-0])

CRC32 instruction for 8-bit source operand and 64-bit destination operand:

TEMP1[7-0] ← BIT\_REFLECT8(SRC[7-0]) TEMP2[31-0] ← BIT\_REFLECT32 (DEST[31-0]) TEMP3[39-0] ← TEMP1[7-0]  $\ll$  32 TEMP4[39-0] ← TEMP2[31-0]  $\ll$  8 TEMP5[39-0] ← TEMP3[39-0] XOR TEMP4[39-0] TEMP6[31-0] ← TEMP5[39-0] MOD2 11EDC6F41H DEST[31-0] ← BIT\_REFLECT (TEMP6[31-0]) DEST[63-32] ← 0000000H

CRC32 instruction for 8-bit source operand and 32-bit destination operand:

TEMP1[7-0]  $\leftarrow$  BIT\_REFLECT8(SRC[7-0])

TEMP2[31-0] ← BIT\_REFLECT32 (DEST[31-0]) TEMP3[39-0] ← TEMP1[7-0]  $\ll$  32 TEMP4[39-0] ← TEMP2[31-0]  $\ll$  8 TEMP5[39-0] ← TEMP3[39-0] XOR TEMP4[39-0] TEMP6[31-0] ← TEMP5[39-0] MOD2 11EDC6F41H DEST[31-0] ← BIT\_REFLECT (TEMP6[31-0])

#### **Flags Affected**

None

#### Intel C/C++ Compiler Intrinsic Equivalent

unsigned int \_mm\_crc32\_u8( unsigned int crc, unsigned char data ) unsigned int \_mm\_crc32\_u16( unsigned int crc, unsigned short data ) unsigned int \_mm\_crc32\_u32( unsigned int crc, unsigned int data ) unsinged \_\_int64 \_mm\_crc32\_u64( unsinged \_\_int64 crc, unsigned \_\_int64 data )

#### SIMD Floating Point Exceptions

None

#### **Protected Mode Exceptions**

| #GP(0)                      | If a memory operand effective address is outside the CS, DS, ES, FS or GS segments.                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory operand effective address is outside the SS segment limit.                                                  |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                                                       |

| #AC(0)                      | If alignment checking is enabled and an unaligned memory refer-<br>ence is made while the current privilege level is 3. |

| #UD                         | If CPUID.01H:ECX.SSE4_2 [Bit 20] = $0$ .                                                                                |

|                             | If LOCK prefix is used.                                                                                                 |

#### **Real Mode Exceptions**

| #GP(0) | If any part of the operand lies outside of the effective address space |

|--------|------------------------------------------------------------------------|

|        | from 0 to 0FFFFH.                                                      |

| #SS(0) | If a memory operand effective address is outside the SS segment limit. |

|--------|------------------------------------------------------------------------|

|        |                                                                        |

#UD If CPUID.01H:ECX.SSE4\_2 [Bit 20] = 0. If LOCK prefix is used.

#### Virtual 8086 Mode Exceptions

| #GP(0)                      | If any part of the operand lies outside of the effective address space from 0 to 0FFFFH. |

|-----------------------------|------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory operand effective address is outside the SS segment limit.                   |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                        |

| " • ~ ( ~ )                 |                                                                                          |

- #AC(0) If alignment checking is enabled and an unaligned memory reference is made.

- #UD If CPUID.01H:ECX.SSE4\_2 [Bit 20] = 0.

If LOCK prefix is used.

#### **Compatibility Mode Exceptions**

Same exceptions as in Protected Mode.

#### **64-Bit Mode Exceptions**

| #GP(0)                      | If the memory address is in a non-canonical form.                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory address referencing the SS segment is in a non-canon-<br>ical form.                                         |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                                                       |

| #AC(0)                      | If alignment checking is enabled and an unaligned memory refer-<br>ence is made while the current privilege level is 3. |

| #UD                         | If CPUID.01H:ECX.SSE4_2 [Bit 20] = $0$ .                                                                                |

|                             | If LOCK prefix is used.                                                                                                 |

•••

# LAR—Load Access Rights Byte

| Opcode           | Instruction                       | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                |

|------------------|-----------------------------------|-----------|----------------|---------------------|------------------------------------------------------------|

| 0F 02 /r         | LAR <i>r16, r16/m16</i>           | RM        | Valid          | Valid               | r16 ← access rights<br>referenced by r16/m16               |

| 0F 02 / <i>r</i> | LAR reg, r32/<br>m16 <sup>1</sup> | RM        | Valid          | Valid               | <i>reg</i> ← access rights<br>referenced by <i>r32/m16</i> |

#### NOTES:

1. For all loads (regardless of source or destination sizing) only bits 16-0 are used. Other bits are ignored.

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RM    | ModRM:reg (w) | ModRM:r/m (r) | NA        | NA        |

#### Description

Loads the access rights from the segment descriptor specified by the second operand (source operand) into the first operand (destination operand) and sets the ZF flag in the flag register. The source operand (which can be a register or a memory location) contains the segment selector for the segment descriptor being accessed. If the source operand is a memory address, only 16 bits of data are accessed. The destination operand is a general-purpose register.

The processor performs access checks as part of the loading process. Once loaded in the destination register, software can perform additional checks on the access rights information.

The access rights for a segment descriptor include fields located in the second doubleword (bytes 4–7) of the segment descriptor. The following fields are loaded by the LAR instruction:

• Bits 7:0 are returned as 0

- Bits 11:8 return the segment type.

- Bit 12 returns the S flag.

- Bits 14:13 return the DPL.

- Bit 15 returns the P flag.

- The following fields are returned only if the operand size is greater than 16 bits:

- Bits 19:16 are undefined.

- Bit 20 returns the software-available bit in the descriptor.

- Bit 21 returns the L flag.

- Bit 22 returns the D/B flag.

- Bit 23 returns the G flag.

- Bits 31:24 are returned as 0.

This instruction performs the following checks before it loads the access rights in the destination register:

- Checks that the segment selector is not NULL.

- Checks that the segment selector points to a descriptor that is within the limits of the GDT or LDT being accessed

- Checks that the descriptor type is valid for this instruction. All code and data segment descriptors are valid for (can be accessed with) the LAR instruction. The valid system segment and gate descriptor types are given in Table 3-62.

- If the segment is not a conforming code segment, it checks that the specified segment descriptor is visible at the CPL (that is, if the CPL and the RPL of the segment selector are less than or equal to the DPL of the segment selector).

If the segment descriptor cannot be accessed or is an invalid type for the instruction, the ZF flag is cleared and no access rights are loaded in the destination operand.

The LAR instruction can only be executed in protected mode and IA-32e mode.

| Туре | Protected Mode          |     | IA-32e Mode          | •     |

|------|-------------------------|-----|----------------------|-------|

|      | Name Valid              |     | Name                 | Valid |

| 0    | Reserved                | No  | Reserved             | No    |

| 1    | Available 16-bit TSS    | Yes | Reserved             | No    |

| 2    | LDT                     | Yes | LDT                  | No    |

| 3    | Busy 16-bit TSS         | Yes | Reserved             | No    |

| 4    | 16-bit call gate        | Yes | Reserved             | No    |

| 5    | 16-bit/32-bit task gate | Yes | Reserved             | No    |

| 6    | 16-bit interrupt gate   | No  | Reserved             | No    |

| 7    | 16-bit trap gate        | No  | Reserved             | No    |

| 8    | Reserved                | No  | Reserved             | No    |

| 9    | Available 32-bit TSS    | Yes | Available 64-bit TSS | Yes   |

| А    | Reserved                | No  | Reserved             | No    |

| В    | Busy 32-bit TSS         | Yes | Busy 64-bit TSS      | Yes   |

#### Table 3-62 Segment and Gate Types

| С | 32-bit call gate      | Yes | 64-bit call gate      | Yes |  |  |

|---|-----------------------|-----|-----------------------|-----|--|--|

| D | Reserved              | No  | Reserved              | No  |  |  |

| Е | 32-bit interrupt gate | No  | 64-bit interrupt gate | No  |  |  |

| F | 32-bit trap gate      | No  | 64-bit trap gate      | No  |  |  |

#### Table 3-62 Segment and Gate Types

#### Operation

$\begin{array}{ll} \mbox{IF Offset(SRC) > descriptor table limit} \\ \mbox{THEN} & \mbox{ZF} \leftarrow 0; \\ \mbox{ELSE} & \mbox{SegmentDescriptor} \leftarrow descriptor referenced by SRC; \\ \mbox{IF SegmentDescriptor(Type) $\neq$ conforming code segment} \\ \mbox{and (CPL > DPL) or (RPL > DPL)} \\ \mbox{or SegmentDescriptor(Type) is not valid for instruction} \\ \mbox{THEN} & \mbox{ZF} \leftarrow 0; \\ \mbox{ELSE} & \mbox{DEST} \leftarrow access rights from SegmentDescriptor as given in Description section; } \\ \mbox{ZF} \leftarrow 1; \\ \mbox{Fl;} \end{array}$

FI;

# **Flags Affected**

The ZF flag is set to 1 if the access rights are loaded successfully; otherwise, it is cleared to 0.

#### **Protected Mode Exceptions**

| #GP(0)                     | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                            | If the DS, ES, FS, or GS register is used to access memory and it contains a NULL segment selector.                            |

| #SS(0)                     | If a memory operand effective address is outside the SS segment limit.                                                         |

| <pre>#PF(fault-code)</pre> | If a page fault occurs.                                                                                                        |

| #AC(0)                     | If alignment checking is enabled and the memory operand effective address is unaligned while the current privilege level is 3. |

| #UD                        | If the LOCK prefix is used.                                                                                                    |

|                            |                                                                                                                                |

# **Real-Address Mode Exceptions**

#UD The LAR instruction is not recognized in real-address mode.

#### Virtual-8086 Mode Exceptions

| #UD The LAR instruction cannot be executed in virtual-8086 mode |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### **64-Bit Mode Exceptions**

| #SS(0)                     | If the memory operand effective address referencing the SS segment is in a non-canonical form.                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| #GP(0)                     | If the memory operand effective address is in a non-canonical form.                                                            |

| <pre>#PF(fault-code)</pre> | If a page fault occurs.                                                                                                        |

| #AC(0)                     | If alignment checking is enabled and the memory operand effective address is unaligned while the current privilege level is 3. |

| #UD                        | If the LOCK prefix is used.                                                                                                    |

...

#### LOCK—Assert LOCK# Signal Prefix

| Opcode | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                              |

|--------|-------------|-----------|----------------|---------------------|--------------------------------------------------------------------------|

| FO     | LOCK        | NP        | Valid          | Valid               | Asserts LOCK# signal for<br>duration of the<br>accompanying instruction. |

NOTES:

\* See IA-32 Architecture Compatibility section below.

| Instruction Operand Encoding |           |           |           |           |  |  |

|------------------------------|-----------|-----------|-----------|-----------|--|--|

| Op/En                        | Operand 1 | Operand 2 | Operand 3 | Operand 4 |  |  |

| NP                           | NA        | NA        | NA        | NA        |  |  |

#### Description

Causes the processor's LOCK# signal to be asserted during execution of the accompanying instruction (turns the instruction into an atomic instruction). In a multiprocessor environment, the LOCK# signal ensures that the processor has exclusive use of any shared memory while the signal is asserted.

Note that, in later Intel 64 and IA-32 processors (including the Pentium 4, Intel Xeon, and P6 family processors), locking may occur without the LOCK# signal being asserted. See the "IA-32 Architecture Compatibility" section below.

The LOCK prefix can be prepended only to the following instructions and only to those forms of the instructions where the destination operand is a memory operand: ADD, ADC, AND, BTC, BTR, BTS, CMPXCHG, CMPXCH8B, CMPXCHG16B, DEC, INC, NEG, NOT, OR, SBB, SUB, XOR, XADD, and XCHG. If the LOCK prefix is used with one of these instructions and the source operand is a memory operand, an undefined opcode exception (#UD) may be generated. An undefined opcode exception will also be generated if the LOCK prefix is used with any instruction not in the above list. The XCHG instruction always asserts the LOCK# signal regardless of the presence or absence of the LOCK prefix.

The LOCK prefix is typically used with the BTS instruction to perform a read-modify-write operation on a memory location in shared memory environment.

The integrity of the LOCK prefix is not affected by the alignment of the memory field. Memory locking is observed for arbitrarily misaligned fields.

This instruction's operation is the same in non-64-bit modes and 64-bit mode.

•••

#### 4. Updates to Chapter 4, Volume 2B

Change bars show changes to Chapter 4 of the *Intel*<sup>®</sup> 64 and *IA-32 Architectures Software Developer's Manual, Volume 2B:* Instruction Set Reference, M-Z.

\_\_\_\_\_

...

# MASKMOVDQU—Store Selected Bytes of Double Quadword

| Opcode/<br>Instruction                            | Op/<br>En | 64/32-bit<br>Mode | CPUID<br>Feature<br>Flag | Description                                                                                                                                                 |

|---------------------------------------------------|-----------|-------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66 OF F7 /r<br>MASKMOVDQU xmm1, xmm2              | RM        | V/V               | SSE2                     | Selectively write bytes from <i>xmm1</i> to memory location using the byte mask in <i>xmm2</i> . The default memory location is specified by DS:DI/EDI/RDI. |

| VEX.128.66.0F.WIG F7 /r<br>VMASKMOVDQU xmm1, xmm2 | RM        | V/V               | AVX                      | Selectively write bytes from<br>xmm1 to memory location<br>using the byte mask in<br>xmm2. The default memory<br>location is specified by<br>DS:DI/EDI/RDI. |

•••

## MFENCE—Memory Fence

| Opcode   | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                           |

|----------|-------------|-----------|----------------|---------------------|---------------------------------------|

| OF AE /6 | MFENCE      | NP        | Valid          | Valid               | Serializes load and store operations. |

# Instruction Operand Encoding Op/En Operand 1 Operand 2 Operand 3 Operand 4 NP NA NA NA NA

#### Description

Performs a serializing operation on all load-from-memory and store-to-memory instructions that were issued prior the MFENCE instruction. This serializing operation guarantees that every load and store instruction that precedes the MFENCE instruction in program order becomes globally visible before any load or store instruction that follows the MFENCE instruction.<sup>1</sup> The MFENCE instruction is ordered with respect to all load and store instructions, other MFENCE instructions, any LFENCE and SFENCE instructions, and any serializing instructions (such as the CPUID instruction). MFENCE does not serialize the instruction stream.

Weakly ordered memory types can be used to achieve higher processor performance through such techniques as out-of-order issue, speculative reads, write-combining, and write-collapsing. The degree to which a consumer of data recognizes or knows that the data is weakly ordered varies among applications and may be unknown to the producer of this data. The MFENCE instruction provides a performance-efficient way of ensuring load and store ordering between routines that produce weakly-ordered results and routines that consume that data.

Processors are free to fetch and cache data speculatively from regions of system memory that use the WB, WC, and WT memory types. This speculative fetching can occur at any time and is not tied to instruction execution. Thus, it is not ordered with respect to executions of the MFENCE instruction; data can be brought into the caches speculatively just before, during, or after the execution of an MFENCE instruction.

This instruction's operation is the same in non-64-bit modes and 64-bit mode.

• • •

<sup>1.</sup> A load instruction is considered to become globally visible when the value to be loaded into its destination register is determined.

NA

## MONITOR—Set Up Monitor Address

NA

| Opcode          | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                                                             |

|-----------------|-------------|-----------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OF 01 <i>C8</i> | MONITOR     | NP        | Valid          | Valid               | Sets up a linear address<br>range to be monitored by<br>hardware and activates the<br>monitor. The address range<br>should be a write-back<br>memory caching type. The<br>address is DS:EAX (DS:RAX<br>in 64-bit mode). |

|           | Instruction Operand E | ncoding   |           |

|-----------|-----------------------|-----------|-----------|

| Operand 1 | Operand 2             | Operand 3 | Operand 4 |

NA

NA

#### Description

Op/En

NP

The MONITOR instruction arms address monitoring hardware using an address specified in EAX (the address range that the monitoring hardware checks for store operations can be determined by using CPUID). A store to an address within the specified address range triggers the monitoring hardware. The state of monitor hardware is used by MWAIT.

The content of EAX is an effective address (in 64-bit mode, RAX is used). By default, the DS segment is used to create a linear address that is monitored. Segment overrides can be used.

ECX and EDX are also used. They communicate other information to MONITOR. ECX specifies optional extensions. EDX specifies optional hints; it does not change the architectural behavior of the instruction. For the Pentium 4 processor (family 15, model 3), no extensions or hints are defined. Undefined hints in EDX are ignored by the processor; undefined extensions in ECX raises a general protection fault.

The address range must use memory of the write-back type. Only write-back memory will correctly trigger the monitoring hardware. Additional information on determining what address range to use in order to prevent false wake-ups is described in Chapter 8, "Multiple-Processor Management" of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

The MONITOR instruction is ordered as a load operation with respect to other memory transactions. The instruction is subject to the permission checking and faults associated with a byte load. Like a load, MONITOR sets the A-bit but not the D-bit in page tables.

CPUID.01H:ECX.MONITOR[bit 3] indicates the availability of MONITOR and MWAIT in the processor. When set, MONITOR may be executed only at privilege level 0 (use at any other privilege level results in an invalid-opcode exception). The operating system or system BIOS may disable this instruction by using the IA32\_MISC\_ENABLE MSR; disabling MONITOR clears the CPUID feature flag and causes execution to generate an invalid-opcode exception.

The instruction's operation is the same in non-64-bit modes and 64-bit mode.

•••

| MOVHLPS— Move Packed Single-Precision Floating-Point Values High | to |

|------------------------------------------------------------------|----|

| Low                                                              |    |

| Opcode/<br>Instruction                                | Op/<br>En | 64/32-bit<br>Mode | CPUID<br>Feature<br>Flag | Description                                                                                                                            |

|-------------------------------------------------------|-----------|-------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| OF 12 /r<br>MOVHLPS xmm1, xmm2                        | RM        | V/V               | SSE                      | Move two packed single-<br>precision floating-point<br>values from high quadword<br>of <i>xmm2</i> to low quadword<br>of <i>xmm1</i> . |

| VEX.NDS.128.0F.WIG 12 /r<br>VMOVHLPS xmm1, xmm2, xmm3 | RVM       | V/V               | AVX                      | Merge two packed single-<br>precision floating-point<br>values from high quadword<br>of xmm3 and low quadword<br>of xmm2.              |

•••

#### MWAIT—Monitor Wait

| Opcode          | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                   |

|-----------------|-------------|-----------|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F 01 <i>C9</i> | MWAIT       | NP        | Valid          | Valid               | A hint that allow the<br>processor to stop<br>instruction execution and<br>enter an implementation-<br>dependent optimized state<br>until occurrence of a class of<br>events. |

|       |             | Instruction Operand | d Encoding |           |

|-------|-------------|---------------------|------------|-----------|

| Op/Ei | n Operand 1 | Operand 2           | Operand 3  | Operand 4 |

| NP    | NA          | NA                  | NA         | NA        |

#### Description

MWAIT instruction provides hints to allow the processor to enter an implementationdependent optimized state. There are two principal targeted usages: address-range monitor and advanced power management. Both usages of MWAIT require the use of the MONITOR instruction.

CPUID.01H:ECX.MONITOR[bit 3] indicates the availability of MONITOR and MWAIT in the processor. When set, MWAIT may be executed only at privilege level 0 (use at any other privilege level results in an invalid-opcode exception). The operating system or system BIOS may disable this instruction by using the IA32\_MISC\_ENABLE MSR; disabling MWAIT clears the CPUID feature flag and causes execution to generate an invalid-opcode exception.

This instruction's operation is the same in non-64-bit modes and 64-bit mode.

ECX specifies optional extensions for the MWAIT instruction. EAX may contain hints such as the preferred optimized state the processor should enter. The first processors to

implement MWAIT supported only the zero value for EAX and ECX. Later processors allowed setting ECX[0] to enable masked interrupts as break events for MWAIT (see below). Software can use the CPUID instruction to determine the extensions and hints supported by the processor.

#### MWAIT for Address Range Monitoring

For address-range monitoring, the MWAIT instruction operates with the MONITOR instruction. The two instructions allow the definition of an address at which to wait (MONITOR) and a implementation-dependent-optimized operation to commence at the wait address (MWAIT). The execution of MWAIT is a hint to the processor that it can enter an implementation-dependent-optimized state while waiting for an event or a store operation to the address range armed by MONITOR.

The following cause the processor to exit the implementation-dependent-optimized state: a store to the address range armed by the MONITOR instruction, an NMI or SMI, a debug exception, a machine check exception, the BINIT# signal, the INIT# signal, and the RESET# signal. Other implementation-dependent events may also cause the processor to exit the implementation-dependent-optimized state.

In addition, an external interrupt causes the processor to exit the implementationdependent-optimized state either (1) if the interrupt would be delivered to software (e.g., as it would be if HLT had been executed instead of MWAIT); or (2) if ECX[0] = 1. Software can execute MWAIT with ECX[0] = 1 only if CPUID.05H:ECX[bit 1] = 1. (Implementation-specific conditions may result in an interrupt causing the processor to exit the implementation-dependent-optimized state even if interrupts are masked and ECX[0] = 0.)

Following exit from the implementation-dependent-optimized state, control passes to the instruction following the MWAIT instruction. A pending interrupt that is not masked (including an NMI or an SMI) may be delivered before execution of that instruction. Unlike the HLT instruction, the MWAIT instruction does not support a restart at the MWAIT instruction following the handling of an SMI.

If the preceding MONITOR instruction did not successfully arm an address range or if the MONITOR instruction has not been executed prior to executing MWAIT, then the processor will not enter the implementation-dependent-optimized state. Execution will resume at the instruction following the MWAIT.

#### **MWAIT for Power Management**

MWAIT accepts a hint and optional extension to the processor that it can enter a specified target C state while waiting for an event or a store operation to the address range armed by MONITOR. Support for MWAIT extensions for power management is indicated by CPUID.05H:ECX[bit 0] reporting 1.

EAX and ECX are used to communicate the additional information to the MWAIT instruction, such as the kind of optimized state the processor should enter. ECX specifies optional extensions for the MWAIT instruction. EAX may contain hints such as the preferred optimized state the processor should enter. Implementation-specific conditions may cause a processor to ignore the hint and enter a different optimized state. Future processor implementations may implement several optimized "waiting" states and will select among those states based on the hint argument.

Table 4-10 describes the meaning of ECX and EAX registers for MWAIT extensions.

| Bits  | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0     | Treat interrupts as break events even if masked (e.g., even if EFLAGS.IF=0).<br>May be set only if CPUID.05H:ECX[bit 1] = 1. |

| 31: 1 | Reserved                                                                                                                     |

#### Table 4-10 MWAIT Extension Register (ECX)

#### Table 4-11 MWAIT Hints Register (EAX)

| Bits  | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 3:0   | Sub C-state within a C-state, indicated by bits [7:4]                                             |

| 7:4   | Target C-state*                                                                                   |

|       | Value of 0 means C1; 1 means C2 and so on                                                         |

|       | Value of 01111B means C0                                                                          |

|       | Note: Target C states for MWAIT extensions are processor-specific C-<br>states, not ACPI C-states |

| 31: 8 | Reserved                                                                                          |

Note that if MWAIT is used to enter any of the C-states that are numerically higher than C1, a store to the address range armed by the MONITOR instruction will cause the processor to exit MWAIT only if the store was originated by other processor agents. A store from non-processor agent might not cause the processor to exit MWAIT in such cases.

For additional details of MWAIT extensions, see Chapter 14, "Power and Thermal Management," of Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

#### Operation

(\* MWAIT takes the argument in EAX as a hint extension and is architected to take the argument in ECX as an instruction extension MWAIT EAX, ECX \*)

{

WHILE ( ("Monitor Hardware is in armed state")) {

implementation\_dependent\_optimized\_state(EAX, ECX); }

Set the state of Monitor Hardware as triggered; }

#### Intel C/C++ Compiler Intrinsic Equivalent

MWAIT: void \_mm\_mwait(unsigned extensions, unsigned hints)

#### Example

MONITOR/MWAIT instruction pair must be coded in the same loop because execution of the MWAIT instruction will trigger the monitor hardware. It is not a proper usage to execute MONITOR once and then execute MWAIT in a loop. Setting up MONITOR without executing MWAIT has no adverse effects.

Typically the MONITOR/MWAIT pair is used in a sequence, such as:

```

EAX = Logical Address(Trigger)

ECX = 0 (*Hints *)

EDX = 0 (* Hints *)

IF (!trigger_store_happened) {

MONITOR EAX, ECX, EDX

IF (!trigger_store_happened) {

MWAIT EAX, ECX

}

}

```

The above code sequence makes sure that a triggering store does not happen between the first check of the trigger and the execution of the monitor instruction. Without the second check that triggering store would go un-noticed. Typical usage of MONITOR and MWAIT would have the above code sequence within a loop.

#### Numeric Exceptions

None

#### Protected Mode Exceptions

| #GP(0) | If $ECX[31:1] \neq 0$ .                          |

|--------|--------------------------------------------------|

|        | If $ECX[0] = 1$ and $CPUID.05H:ECX[bit 1] = 0$ . |

| #UD    | If CPUID.01H:ECX.MONITOR[bit 3] = 0.             |

|        | If current privilege level is not 0.             |

#### **Real Address Mode Exceptions**

| #GP | If $ECX[31:1] \neq 0$ .                          |

|-----|--------------------------------------------------|

|     | If $ECX[0] = 1$ and $CPUID.05H:ECX[bit 1] = 0$ . |

| #UD | If CPUID.01H:ECX.MONITOR[bit 3] = 0.             |

#### Virtual 8086 Mode Exceptions

#UD The MWAIT instruction is not recognized in virtual-8086 mode (even if CPUID.01H:ECX.MONITOR[bit 3] = 1).

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### **64-Bit Mode Exceptions**

| #GP(0) | If $RCX[63:1] \neq 0$ .                          |

|--------|--------------------------------------------------|

|        | If $RCX[0] = 1$ and $CPUID.05H:ECX[bit 1] = 0$ . |

| #UD    | If the current privilege level is not 0.         |

|        | If CPUID.01H:ECX.MONITOR[bit 3] = 0.             |

•••

# PAUSE—Spin Loop Hint

| Opcode | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                 |

|--------|-------------|-----------|----------------|---------------------|-----------------------------------------------------------------------------|

| F3 90  | PAUSE       | NP        | Valid          | Valid               | Gives hint to processor that<br>improves performance of<br>spin-wait loops. |

#### Instruction Operand Encoding

|       |           |           | •         |           |

|-------|-----------|-----------|-----------|-----------|

| Op/En | Operand 1 | Operand 2 | Operand 3 | Operand 4 |

| NP    | NA        | NA        | NA        | NA        |

#### Description

Improves the performance of spin-wait loops. When executing a "spin-wait loop," processors will suffer a severe performance penalty when exiting the loop because it detects a possible memory order violation. The PAUSE instruction provides a hint to the processor that the code sequence is a spin-wait loop. The processor uses this hint to avoid the memory order violation in most situations, which greatly improves processor performance. For this reason, it is recommended that a PAUSE instruction be placed in all spin-wait loops.

An additional function of the PAUSE instruction is to reduce the power consumed by a processor while executing a spin loop. A processor can execute a spin-wait loop extremely quickly, causing the processor to consume a lot of power while it waits for the resource it is spinning on to become available. Inserting a pause instruction in a spin-wait loop greatly reduces the processor's power consumption.

This instruction was introduced in the Pentium 4 processors, but is backward compatible with all IA-32 processors. In earlier IA-32 processors, the PAUSE instruction operates like a NOP instruction. The Pentium 4 and Intel Xeon processors implement the PAUSE instruction as a delay. The delay is finite and can be zero for some processors. This instruction does not change the architectural state of the processor (that is, it performs essentially a delaying no-op operation).

This instruction's operation is the same in non-64-bit modes and 64-bit mode.

...

| Opcode               | Instruction                  | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description            |

|----------------------|------------------------------|-----------|----------------|---------------------|------------------------|

| F3 0F B8 /r          | POPCNT r16, r/<br>m16        | RM        | Valid          | Valid               | POPCNT on <i>r/m16</i> |

| F3 0F B8 /r          | POPCNT <i>r32, r/</i><br>m32 | RM        | Valid          | Valid               | POPCNT on r/m32        |

| F3 REX.W OF B8<br>/r | Popcnt r64, r/<br>m64        | RM        | Valid          | N.E.                | POPCNT on r/m64        |

# POPCNT — Return the Count of Number of Bits Set to 1

| Instruction | Operand | Encoding |

|-------------|---------|----------|

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RM    | ModRM:reg (w) | ModRM:r/m (r) | NA        | NA        |

#### Description

This instruction calculates of number of bits set to 1 in the second operand (source) and returns the count in the first operand (a destination register).

#### Operation

Count = 0; For (i=0; i < OperandSize; i++) { IF (SRC[ i] = 1) // i'th bit THEN Count++; FI; } DEST ← Count;

#### **Flags Affected**

OF, SF, ZF, AF, CF, PF are all cleared. ZF is set if SRC = 0, otherwise ZF is cleared

#### Intel C/C++ Compiler Intrinsic Equivalent

| POPCNT: | int _mm_popcnt_u32(unsigned int a);      |

|---------|------------------------------------------|

| POPCNT: | int64_t _mm_popcnt_u64(unsignedint64 a); |

#### **Protected Mode Exceptions**

| #GP(0)                      | If a memory operand effective address is outside the CS, DS, ES, FS or GS segments.                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory operand effective address is outside the SS segment limit.                                                  |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                                                       |

| #AC(0)                      | If an unaligned memory reference is made while the current privi-<br>lege level is 3 and alignment checking is enabled. |

| #UD                         | If CPUID.01H:ECX.POPCNT [Bit 23] = 0.                                                                                   |

|                             | If LOCK prefix is used.                                                                                                 |

|                             | Either the prefix REP (F3h) or REPN (F2H) is used.                                                                      |

|                             |                                                                                                                         |

#### **Real Mode Exceptions**

| #GP(0) | If any part of the operand lies outside of the effective address space from 0 to 0FFFFH. |

|--------|------------------------------------------------------------------------------------------|

| #SS(0) | If a memory operand effective address is outside the SS segment limit.                   |

| #UD    | If CPUID.01H:ECX.POPCNT [Bit 23] = $0$ .                                                 |

If LOCK prefix is used.

Either the prefix REP (F3h) or REPN (F2H) is used.

# Virtual 8086 Mode Exceptions

| #GP(0)                      | If any part of the operand lies outside of the effective address space from 0 to 0FFFFH. |

|-----------------------------|------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory operand effective address is outside the SS segment limit.                   |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                        |

| #AC(0)                      | If an unaligned memory reference is made while alignment checking is enabled.            |

| #UD                         | If CPUID.01H:ECX.POPCNT [Bit 23] = 0.                                                    |

|                             | If LOCK prefix is used.                                                                  |

|                             | Either the prefix REP (F3h) or REPN (F2H) is used.                                       |

# **Compatibility Mode Exceptions**

Same exceptions as in Protected Mode.

# 64-Bit Mode Exceptions

| #GP(0)                      | If the memory address is in a non-canonical form.                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------|

| #SS(0)                      | If a memory address referencing the SS segment is in a non-canon-<br>ical form.                                         |

| <pre>#PF (fault-code)</pre> | For a page fault.                                                                                                       |

| #AC(0)                      | If alignment checking is enabled and an unaligned memory refer-<br>ence is made while the current privilege level is 3. |

| #UD                         | If CPUID.01H:ECX.POPCNT [Bit 23] = $0$ .                                                                                |

|                             | If LOCK prefix is used.                                                                                                 |

|                             | Either the prefix REP (F3h) or REPN (F2H) is used.                                                                      |

|                             |                                                                                                                         |

•••

#### WRMSR—Write to Model Specific Register

| Opcode | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                         |

|--------|-------------|-----------|----------------|---------------------|-----------------------------------------------------|

| 0F 30  | WRMSR       | NP        | Valid          | Valid               | Write the value in EDX:EAX to MSR specified by ECX. |

#### Instruction Operand Encoding

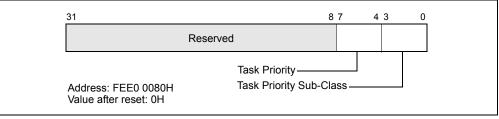

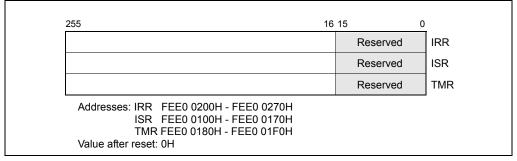

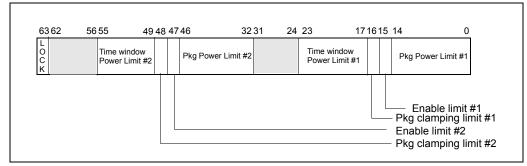

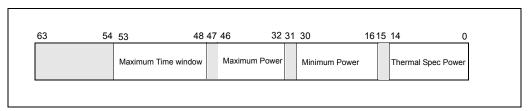

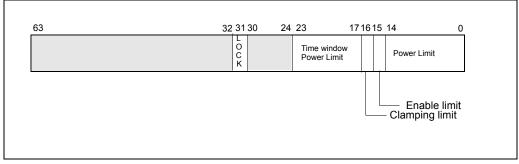

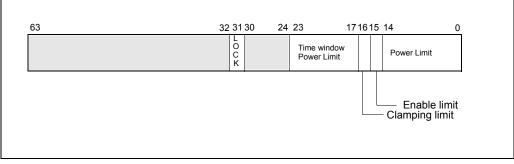

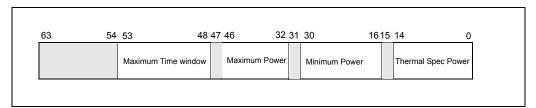

| Op/En | Operand 1 | Operand 2 | Operand 3 | Operand 4 |