# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

February 2014

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-042

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Intel, the Intel logo, Pentium, Xeon, Intel NetBurst, Intel Core, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo, Intel Core 2 Extreme, Intel Pentium D, Itanium, Intel SpeedStep, MMX, Intel Atom, and VTune are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright © 1997-2014 Intel Corporation. All rights reserved.

# Contents

| Revision History          | <br> |  | <br>• • |  | <br> | • |  |  |  |   |  |  | • | . 4 | 1 |

|---------------------------|------|--|---------|--|------|---|--|--|--|---|--|--|---|-----|---|

| Preface                   | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 7 | 7 |

| Summary Tables of Changes |      |  | <br>    |  | <br> | • |  |  |  | • |  |  | • | . 8 | 3 |

| Documentation Changes     | <br> |  | <br>    |  | <br> | • |  |  |  |   |  |  | • | . 9 | ) |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul> <li>Removed Documentation Changes 1-6</li> <li>Added Documentation Changes 1-6</li> </ul>                                                                                                                               | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                   | Date           |

|----------|-----------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul> | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul> | June 2010      |

| -029     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | September 2010 |

| -030     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | January 2011   |

| -031     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | April 2011     |

| -032     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-14</li></ul> | May 2011       |

| -033     | <ul><li>Removed Documentation Changes 1-14</li><li>Added Documentation Changes 1-38</li></ul> | October 2011   |

| -034     | <ul><li>Removed Documentation Changes 1-38</li><li>Added Documentation Changes 1-16</li></ul> | December 2011  |

| -035     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | March 2012     |

| -036     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-17</li></ul> | May 2012       |

| -037     | <ul><li>Removed Documentation Changes 1-17</li><li>Added Documentation Changes 1-28</li></ul> | August 2012    |

| -038     | <ul><li>Removed Documentation Changes 1-28</li><li>Add Documentation Changes 1-22</li></ul>   | January 2013   |

| -039     | <ul><li>Removed Documentation Changes 1-22</li><li>Add Documentation Changes 1-17</li></ul>   | June 2013      |

| -040     | <ul><li>Removed Documentation Changes 1-17</li><li>Add Documentation Changes 1-24</li></ul>   | September 2013 |

| -041     | <ul><li>Removed Documentation Changes 1-24</li><li>Add Documentation Changes 1-20</li></ul>   | February 2014  |

| -042     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-8</li></ul>    | February 2014  |

§

**Revision History**

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                         | Document Number/<br>Location |

|------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture                | 253665                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M   | 253666                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z   | 253667                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2C: Instruction Set Reference        | 326018                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1 | 253668                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2 | 253669                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3C: System Programming Guide, Part 3 | 326019                       |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(B)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

## **Documentation Changes**

| No. | DOCUMENTATION CHANGES            |

|-----|----------------------------------|

| 1   | Updates to Chapter 1, Volume 1   |

| 2   | Updates to Chapter 2, Volume 1   |

| 3   | Updates to Chapter 1, Volume 2A  |

| 4   | Updates to Chapter 3, Volume 2A  |

| 5   | Updates to Chapter 4, Volume 2B  |

| 6   | Updates to Chapter 1, Volume 3A  |

| 7   | Updates to Chapter 15, Volume 3B |

| 8   | Updates to Chapter 35, Volume 3C |

# **Documentation Changes**

#### 1. Updates to Chapter 1, Volume 1

Change bars show changes to Chapter 1 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

• • •

# 1.1 INTEL<sup>®</sup> 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>™</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor

- Intel<sup>®</sup> Core<sup>™</sup> i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 product family

- 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families

- 4th generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>™</sup> Duo, Intel<sup>®</sup> Core<sup>™</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200 and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Quad, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>™</sup> microar-chitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000, X9000 series, Intel<sup>®</sup> Core<sup>™</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>™</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>™</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>™</sup> i7 processor and Intel<sup>®</sup> Xeon<sup>®</sup> processor 3400, 5500, 7500 series are based on 45 nm Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> microarchitecture code name Westmere is a 32nm version of Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> Xeon<sup>®</sup> processor 5600 series, Intel Xeon processor E7 and various Intel Core i7, i5, i3 processors are based on Intel<sup>®</sup> microarchitecture code name Westmere. These processors support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/ 4800/2800 product families, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, and 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series are based on the Intel<sup>®</sup> microarchitecture code name Sandy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family and the 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families and Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge-EP and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family and 4th Generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Haswell and support Intel 64 architecture.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>™</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors, Intel Core 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors. Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

# 1.2 OVERVIEW OF VOLUME 1: BASIC ARCHITECTURE

A description of this manual's content follows:

**Chapter 1 — About This Manual.** Gives an overview of all five volumes of the *Intel® 64 and IA-32 Architectures Software Developer's Manual.* It also describes the notational conventions in these manuals and lists related Intel manuals and documentation of interest to programmers and hardware designers.

**Chapter 2 — Intel**<sup>®</sup> **64 and IA-32 Architectures.** Introduces the Intel 64 and IA-32 architectures along with the families of Intel processors that are based on these architectures. It also gives an overview of the common features found in these processors and brief history of the Intel 64 and IA-32 architectures.

**Chapter 3 — Basic Execution Environment**. Introduces the models of memory organization and describes the register set used by applications.

**Chapter 4** — **Data Types.** Describes the data types and addressing modes recognized by the processor; provides an overview of real numbers and floating-point formats and of floating-point exceptions.

**Chapter 5 — Instruction Set Summary.** Lists all Intel 64 and IA-32 instructions, divided into technology groups.

**Chapter 6** — **Procedure Calls, Interrupts, and Exceptions.** Describes the procedure stack and mechanisms provided for making procedure calls and for servicing interrupts and exceptions.

**Chapter 7** — **Programming with General-Purpose Instructions.** Describes basic load and store, program control, arithmetic, and string instructions that operate on basic data types, general-purpose and segment registers; also describes system instructions that are executed in protected mode.

**Chapter 8** — **Programming with the x87 FPU.** Describes the x87 floating-point unit (FPU), including floating-point registers and data types; gives an overview of the floating-point instruction set and describes the processor's floating-point exception conditions.

**Chapter 9 — Programming with Intel<sup>®</sup> MMX<sup>™</sup> Technology.** Describes Intel MMX technology, including MMX registers and data types; also provides an overview of the MMX instruction set.

**Chapter 10 — Programming with Streaming SIMD Extensions (SSE).** Describes SSE extensions, including XMM registers, the MXCSR register, and packed single-precision floating-point data types; provides an overview of the SSE instruction set and gives guidelines for writing code that accesses the SSE extensions.

**Chapter 11 — Programming with Streaming SIMD Extensions 2 (SSE2).** Describes SSE2 extensions, including XMM registers and packed double-precision floating-point data types; provides an overview of the SSE2 instruction set and gives guidelines for writing code that accesses SSE2 extensions. This chapter also describes SIMD floating-point exceptions that can be generated with SSE and SSE2 instructions. It also provides general guidelines for incorporating support for SSE and SSE2 extensions into operating system and applications code.

**Chapter 12 — Programming with SSE3, SSSE3 and SSE4.** Provides an overview of the SSE3 instruction set, Supplemental SSE3, SSE4, and guidelines for writing code that accesses these extensions.

**Chapter 13 — Managing State Using the XSAVE Feature Set.** Describes the XSAVE feature set instructions and explains how software can enable the XSAVE feature set and XSAVE-enabled features.

**Chapter 14 — Programming with AVX, FMA and AVX2.** Provides an overview of the Intel<sup>®</sup> AVX instruction set, FMA and Intel AVX2 extensions and gives guidelines for writing code that accesses these extensions.

**Chapter 15 — Programming with Intel Transactional Synchronization Extensions.** Describes the instruction extensions that support lock elision techniques to improve the performance of multi-threaded software with contended locks.

**Chapter 16 — Input/Output.** Describes the processor's I/O mechanism, including I/O port addressing, I/O instructions, and I/O protection mechanisms.

**Chapter 17 — Processor Identification and Feature Determination.** Describes how to determine the CPU type and features available in the processor.

**Appendix A — EFLAGS Cross-Reference.** Summarizes how the IA-32 instructions affect the flags in the EFLAGS register.

**Appendix B** — **EFLAGS Condition Codes.** Summarizes how conditional jump, move, and 'byte set on condition code' instructions use condition code flags (OF, CF, ZF, SF, and PF) in the EFLAGS register.

**Appendix C** — **Floating-Point Exceptions Summary.** Summarizes exceptions raised by the x87 FPU floating-point and SSE/SSE2/SSE3 floating-point instructions.

**Appendix D** — **Guidelines for Writing x87 FPU Exception Handlers.** Describes how to design and write MS-DOS\* compatible exception handling facilities for FPU exceptions (includes software and hardware requirements and assembly-language code examples). This appendix also describes general techniques for writing robust FPU exception handlers.

**Appendix E — Guidelines for Writing SIMD Floating-Point Exception Handlers.** Gives guidelines for writing exception handlers for exceptions generated by SSE/SSE2/SSE3 floating-point instructions.

. . .

#### 2. Updates to Chapter 2, Volume 1

Change bars show changes to Chapter 2 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

. . .

# 2.1.20 The Second Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family (2011)

The Second Generation Intel Core processor family spans Intel Core i7, i5 and i3 processors based on the Sandy Bridge microarchitecture. They are built from 32 nm process technology and have innovative features including:

- Intel Turbo Boost Technology for Intel Core i5 and i7 processors

- Intel Hyper-Threading Technology.

- Enhanced Intel Smart Cache and integrated memory controller.

- Processor graphics and built-in visual features like Intel<sup>®</sup> Quick Sync Video, Intel<sup>®</sup> Insider<sup>TM</sup> etc.

- Range of instruction set support up to AVX, AESNI, PCLMULQDQ, SSE4.2 and SSE4.1.

Intel Xeon processor E3-1200 product family is also based on the Sandy Bridge microarchitecture.

Intel Xeon processor E5-2400/1400 product families are based on the Sandy Bridge-EP microarchitecture.

Intel Xeon processor E5-4600/2600/1600 product families are based on the Sandy Bridge-EP microarchitecture and provide support for multiple sockets.

# 2.1.21 The Third Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family (2012)

The Third Generation Intel Core processor family spans Intel Core i7, i5 and i3 processors based on the Ivy Bridge microarchitecture. The Intel Xeon processor E7-8800/4800/2800 v2 product families and Intel Xeon processor E3-1200 v2 product family are also based on the Ivy Bridge microarchitecture.

The Intel Xeon processor E5-2400/1400 v2 product families are based on the Ivy Bridge-EP microarchitecture.

The Intel Xeon processor E5-4600/2600/1600 v2 product families are based on the Ivy Bridge-EP microarchitecture and provide support for multiple sockets.

# 2.1.22 The Fourth Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family (2013)

The Fourth Generation Intel Core processor family spans Intel Core i7, i5 and i3 processors based on the Haswell microarchitecture. Intel Xeon processor E3-1200 v3 product family is also based on the Haswell microarchitecture.

. . .

#### 3. Updates to Chapter 1, Volume 2A

Change bars show changes to Chapter 1 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

\_\_\_\_\_

• • •

# 1.1 INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>™</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor

- Intel<sup>®</sup> Core<sup>™</sup> i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 product family

- 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families

- 4th generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>™</sup> Duo, Intel<sup>®</sup> Core<sup>™</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200 and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Quad, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>™</sup> microar-chitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000, X9000 series, Intel<sup>®</sup> Core<sup>™</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>™</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>™</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>™</sup> i7 processor and Intel<sup>®</sup> Xeon<sup>®</sup> processor 3400, 5500, 7500 series are based on 45 nm Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> microarchitecture code name Westmere is a 32nm version of Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> Xeon<sup>®</sup> processor 5600 series, Intel Xeon processor E7 and various Intel Core i7, i5, i3 processors are based on Intel<sup>®</sup> microarchitecture code name Westmere. These processors support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/ 4800/2800 product families, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, and 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series are based on the Intel<sup>®</sup> microarchitecture code name Sandy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family and the 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families and Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge-EP and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family and 4th Generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Haswell and support Intel 64 architecture.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>™</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors, Intel Core 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors. Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

• • •

#### 4. Updates to Chapter 3, Volume 2A

Change bars show changes to Chapter 3 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M.

\_\_\_\_\_

## **CPUID—CPU Identification**

. . .

#### NOTE

Software must confirm that a processor feature is present using feature flags returned by CPUID prior to using the feature. Software should not depend on future offerings retaining all features.

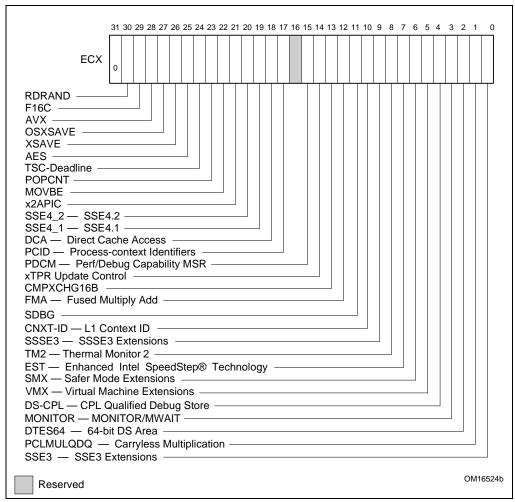

Figure 3-6 Feature Information Returned in the ECX Register

#### 5. Updates to Chapter 4, Volume 2B

Change bars show changes to Chapter 4 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z.

\_\_\_\_\_

• • •

...

| Opcode*       | Instruction     | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description        |

|---------------|-----------------|-----------|----------------|---------------------|--------------------|

| FF /6         | PUSH r/m16      | М         | Valid          | Valid               | Push <i>r/m16.</i> |

| FF /6         | PUSH r/m32      | М         | N.E.           | Valid               | Push <i>r/m32.</i> |

| FF /6         | PUSH r/m64      | М         | Valid          | N.E.                | Push <i>r/m64.</i> |

| 50+ <i>rw</i> | PUSH r16        | 0         | Valid          | Valid               | Push <i>r16.</i>   |

| 50+ <i>rd</i> | PUSH <i>r32</i> | 0         | N.E.           | Valid               | Push <i>r32.</i>   |

| 50+ <i>rd</i> | PUSH r64        | 0         | Valid          | N.E.                | Push <i>r64.</i>   |

| 6A ib         | PUSH imm8       | Ι         | Valid          | Valid               | Push imm8.         |

| 68 iw         | PUSH imm16      | Ι         | Valid          | Valid               | Push imm16.        |

| 68 id         | PUSH imm32      | Ι         | Valid          | Valid               | Push imm32.        |

| 0E            | PUSH CS         | NP        | Invalid        | Valid               | Push CS.           |

| 16            | PUSH SS         | NP        | Invalid        | Valid               | Push SS.           |

| 1E            | PUSH DS         | NP        | Invalid        | Valid               | Push DS.           |

| 06            | PUSH ES         | NP        | Invalid        | Valid               | Push ES.           |

| OF AO         | PUSH FS         | NP        | Valid          | Valid               | Push FS.           |

| OF A8         | PUSH GS         | NP        | Valid          | Valid               | Push GS.           |

## PUSH—Push Word, Doubleword or Quadword Onto the Stack

**NOTES:**

\* See IA-32 Architecture Compatibility section below.

## Instruction Operand Encoding

| Op/En | Operand 1       | Operand 2 | Operand 3 | Operand 4 |

|-------|-----------------|-----------|-----------|-----------|

| М     | ModRM:r/m (r)   | NA        | NA        | NA        |

| 0     | opcode + rd (r) | NA        | NA        | NA        |

| I     | imm8/16/32      | NA        | NA        | NA        |

| NP    | NA              | NA        | NA        | NA        |

...

## XSAVES—Save Processor Extended States Supervisor

| Opcode          | Instruction  | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                       |

|-----------------|--------------|-----------|----------------|---------------------|---------------------------------------------------------------------------------------------------|

| 0F C7 /5        | XSAVES mem   | Μ         | Valid          | Valid               | Save state components specified by EDX:EAX to <i>mem</i> with compaction, optimizing if possible. |

| REX.W+ 0F C7 /5 | XSAVES64 mem | Μ         | Valid          | N.E.                | Save state components specified by EDX:EAX to <i>mem</i> with compaction, optimizing if possible. |

|       |               | Instruction Operan | d Encoding |           |

|-------|---------------|--------------------|------------|-----------|

| Op/En | Operand 1     | Operand 2          | Operand 3  | Operand 4 |

| М     | ModRM:r/m (w) | NA                 | NA         | NA        |

#### Description

Performs a full or partial save of processor state components to the XSAVE area located at the memory address specified by the destination operand. The implicit EDX: EAX register pair specifies a 64-bit instruction mask. The specific state components saved correspond to the bits set in the requested-feature bitmap (RFBM), the logical-AND of EDX: EAX and the logical-OR of XCRO with the IA32\_XSS MSR. XSAVES may be executed only if CPL = 0.

The format of the XSAVE area is detailed in Section 13.4, "XSAVE Area," of Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1.

Section 13.10, "Operation of XSAVES," of Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1 provides a detailed description of the operation of the XSAVES instruction. The following items provide a high-level outline:

- Execution of XSAVES is similar to that of XSAVEC. XSAVES differs from XSAVEC in that it can save state components corresponding to bits set in the IA32\_XSS MSR and that it may use the modified optimization.

- XSAVES saves state component *i* only if RFBM[*i*] = 1 and XINUSE[*i*] = 1.<sup>1</sup> (XINUSE is a bitmap by which the processor tracks the status of various state components. See Section 13.5.4, "Processor Tracking of XSAVE-Managed State.") Even if both bits are 1, XSAVES may optimize and not save state component *i* if (1) state component *i* has not been modified since the last execution of XRTOR or XRSTORS; and (2) this execution of XSAVES correspond to that last execution of XRTOR or XRSTORS as determined by XRSTOR\_INFO (see the Operation section below).

- XSAVES does not modify bytes 511:464 of the legacy region of the XSAVE area (see Section 13.4.1, "Legacy Region of an XSAVE Area").

- XSAVES writes the logical AND of RFBM and XINUSE to the XSTATE\_BV field of the XSAVE header.<sup>2</sup> (See Section 13.4.2, "XSAVE Header.") XSAVES sets bit 63 of the XCOMP\_BV field and sets bits 62:0 of that field to RFBM[62:0]. XSAVES does not write to any parts of the XSAVE header other than the XSTATE\_BV and XCOMP\_BV fields.

- XSAVES always uses the compacted format of the extended region of the XSAVE area (see Section 13.4.3, "Extended Region of an XSAVE Area").

Use of a destination operand not aligned to 64-byte boundary (in either 64-bit or 32-bit modes) results in a general-protection (#GP) exception. In 64-bit mode, the upper 32 bits of RDX and RAX are ignored.

#### Operation

```

\label{eq:RFBM} \begin{array}{l} \leftarrow \text{XCRO AND EDX:EAX;} \quad /* \text{ bitwise logical AND */} \\ \mbox{IF in VMX non-root operation} \\ & \mbox{THEN VMXNR} \leftarrow 1; \\ & \mbox{ELSE VMXNR} \leftarrow 0; \\ \mbox{FI;} \\ \mbox{LAXA} \leftarrow \mbox{linear address of XSAVE area;} \\ \mbox{COMPMASK} \leftarrow \mbox{RFBM OR 80000000_0000000H;} \end{array}

```

2. There is an exception for state component 1 (SSE). MXCSR is part of SSE state, but XINUSE[1] may be 0 even if MXCSR does not have its initial value of 1F80H. In this case, XSAVES sets XSTATE\_BV[1] to 1 as long as RFBM[1] = 1.

There is an exception for state component 1 (SSE). MXCSR is part of SSE state, but XINUSE[1] may be 0 even if MXCSR does not have its initial value of 1F80H. In this case, the init optimization does not apply and XSAVEC will save SSE state as long as RFBM[1] = 1 and the modified optimization is not being applied.

```

IF XRSTOR_INFO = (CPL, VMXNR, LAXA, COMPMASK)

THEN MODOPT \leftarrow 1;

ELSE MODOPT \leftarrow 0;

FI;

IF RFBM[0] = 1 and XINUSE[0] = 1

THEN store x87 state into legacy region of XSAVE area;

/* might avoid saving if x87 state is not modified and MODOPT = 1 */

FI;

IF RFBM[1] = 1 and (XINUSE[1] = 1 or MXCSR \neq 1F80H)

THEN store SSE state into legacy region of XSAVE area;

/* might avoid saving if SSE state is not modified and MODOPT = 1 */

FI;

IF RFBM[2] = 1 AND XINUSE[2] = 1

THEN store AVX state into extended region of XSAVE area;

/* might avoid saving if AVX state is not modified and MODOPT = 1 */

FI;

```

$\label{eq:comp_state} \begin{array}{l} \mbox{XSTATE_BV field in XSAVE header} \leftarrow \mbox{XINUSE AND RFBM;} \\ \mbox{XCOMP_BV field in XSAVE header} \leftarrow \mbox{COMPMASK;} \end{array}$

#### **Flags Affected**

None.

#### Intel C/C++ Compiler Intrinsic Equivalent

XSAVES: void \_xsaves( void \* , unsigned \_\_int64); XSAVES64: void \_xsaves64( void \* , unsigned \_\_int64);

#### **Protected Mode Exceptions**

| #GP(0)          | If a memory operand effective address is outside the CS, DS, ES, FS, or GS segment limit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 64-byte boundary, regardless of segment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| #SS(0)          | If a memory operand effective address is outside the SS segment limit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| #NM             | If CR0.TS[bit 3] = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| #UD             | If CPUID.01H: ECX.XSAVE[bit 26] = 0 or CPUID. (EAX=0DH, ECX=1): EAX.XSS[bit 3] = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | If CR4.OSXSAVE[bit 18] = $0.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | If any of the LOCK, 66H, F3H or F2H prefixes is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| #AC             | If this exception is disabled a general protection exception (#GP) is signaled if the memory operand is not aligned on a 16-byte boundary, as described above. If the alignment check exception (#AC) is enabled (and the CPL is 3), signaling of #AC is not guaranteed and may vary with implementation, as follows. In all implementations where #AC is not signaled, a general protection exception is signaled in its place. In addition, the width of the alignment check may also vary with implementation. For instance, for a given implementation, an alignment check exception might be signaled for a 2-byte misalignment, whereas a general protection exception might be signaled for all other misalignments (4-, 8-, or 16-byte misalignments). |

#### **Real-Address Mode Exceptions**

| #GP | If a memory operand is not aligned on a 64-byte boundary, regardless of segment.     |

|-----|--------------------------------------------------------------------------------------|

|     | If any part of the operand lies outside the effective address space from 0 to FFFFH. |

| #NM | If CR0.TS[bit 3] = 1.                                                                |

| #UD | If CPUID.01H: ECX.XSAVE[bit 26] = 0 or CPUID.(EAX=0DH,ECX=1):EAX.XSS[bit 3] = 0.     |

|     | If CR4.OSXSAVE[bit $18$ ] = 0.                                                       |

|     | If any of the LOCK, 66H, F3H or F2H prefixes is used.                                |

|     |                                                                                      |

#### Virtual-8086 Mode Exceptions

Same exceptions as in protected mode.

#### **Compatibility Mode Exceptions**

Same exceptions as in protected mode.

#### **64-Bit Mode Exceptions**

| #GP(0)          | If the memory address is in a non-canonical form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | If a memory operand is not aligned on a 64-byte boundary, regardless of segment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| #SS(0)          | If a memory address referencing the SS segment is in a non-canonical form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| #PF(fault-code) | If a page fault occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| #NM             | If CR0.TS[bit 3] = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| #UD             | If CPUID.01H: ECX.XSAVE[bit 26] = 0 or CPUID.(EAX=0DH,ECX=1): EAX.XSS[bit 3] = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 | If CR4.OSXSAVE[bit 18] = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | If any of the LOCK, 66H, F3H or F2H prefixes is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| #AC             | If this exception is disabled a general protection exception (#GP) is signaled if the memory operand is not aligned on a 16-byte boundary, as described above. If the alignment check exception (#AC) is enabled (and the CPL is 3), signaling of #AC is not guaranteed and may vary with implementation, as follows. In all implementations where #AC is not signaled, a general protection exception is signaled in its place. In addition, the width of the alignment check may also vary with implementation. For instance, for a given implementation, an alignment check exception might be signaled for a 2-byte misalignment, whereas a general protection exception might be signaled for all other misalignments (4-, 8-, or 16-byte misalignments). |

. . .

#### 6. Updates to Chapter 1, Volume 3A

Change bars show changes to Chapter 1 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1.

\_\_\_\_\_

...

# 1.1 INTEL® 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>™</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor

- Intel<sup>®</sup> Core<sup>™</sup> i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 product family

- 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families

- 4th generation Intel<sup>®</sup> Core<sup>™</sup> processors

• Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>™</sup> Duo, Intel<sup>®</sup> Core<sup>™</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200 and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Quad, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000, X9000 series, Intel<sup>®</sup> Core<sup>™</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>™</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>™</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>™</sup> i7 processor and Intel<sup>®</sup> Xeon<sup>®</sup> processor 3400, 5500, 7500 series are based on 45 nm Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> microarchitecture code name Westmere is a 32nm version of Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> Xeon<sup>®</sup> processor 5600 series, Intel Xeon processor E7 and various Intel Core i7, i5, i3 processors are based on Intel<sup>®</sup> microarchitecture code name Westmere. These processors support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/ 4800/2800 product families, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, and 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series are based on the Intel<sup>®</sup> microarchitecture code name Sandy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family and the 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families and Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge-EP and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family and 4th Generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Haswell and support Intel 64 architecture.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>™</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors, Intel Core 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors. Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

#### 7. Updates to Chapter 15, Volume 3B

Change bars show changes to Chapter 15 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2.

\_\_\_\_\_

...

## 15.3.1 Machine-Check Global Control MSRs

The machine-check global control MSRs include the IA32\_MCG\_CAP, IA32\_MCG\_STATUS, and optionally IA32\_MCG\_CTL and IA32\_MCG\_EXT\_CTL. See Chapter 35, "Model-Specific Registers (MSRs)," for the addresses of these registers.

### 15.3.1.1 IA32\_MCG\_CAP MSR

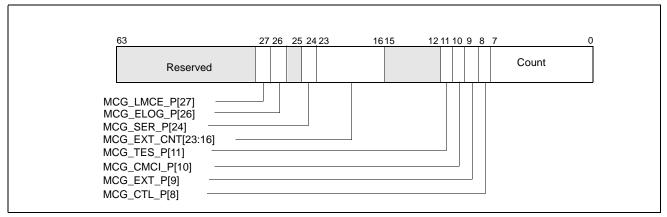

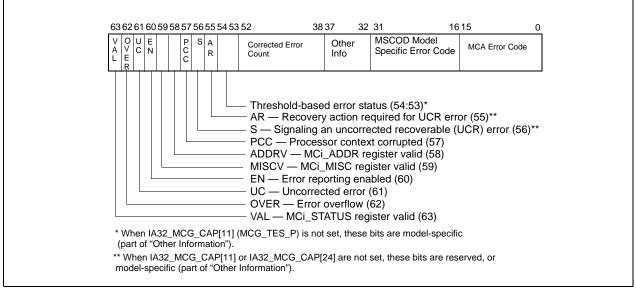

The IA32\_MCG\_CAP MSR is a read-only register that provides information about the machine-check architecture of the processor. Figure Figure 15-2 shows the layout of the register.

Figure 15-2 IA32\_MCG\_CAP Register

Where:

- Count field, bits 7:0 Indicates the number of hardware unit error-reporting banks available in a particular processor implementation.

- MCG\_CTL\_P (control MSR present) flag, bit 8 Indicates that the processor implements the IA32\_MCG\_CTL MSR when set; this register is absent when clear.

- MCG\_EXT\_P (extended MSRs present) flag, bit 9 Indicates that the processor implements the

extended machine-check state registers found starting at MSR address 180H; these registers are absent

when clear.

- MCG\_CMCI\_P (Corrected MC error counting/signaling extension present) flag, bit 10 Indicates (when set) that extended state and associated MSRs necessary to support the reporting of an interrupt on a corrected MC error event and/or count threshold of corrected MC errors, is present. When this bit is set, it does not imply this feature is supported across all banks. Software should check the availability of the necessary logic on a bank by bank basis when using this signaling capability (i.e. bit 30 settable in individual IA32\_MCi\_CTL2 register).

- MCG\_TES\_P (threshold-based error status present) flag, bit 11 Indicates (when set) that bits 56:53 of the IA32\_MCi\_STATUS MSR are part of the architectural space. Bits 56:55 are reserved, and bits 54:53 are used to report threshold-based error status. Note that when MCG\_TES\_P is not set, bits 56:53 of the IA32\_MCi\_STATUS MSR are model-specific.

- MCG\_EXT\_CNT, bits 23:16 Indicates the number of extended machine-check state registers present. This field is meaningful only when the MCG\_EXT\_P flag is set.

- MCG\_SER\_P (software error recovery support present) flag, bit 24— Indicates (when set) that the processor supports software error recovery (see Section 15.6), and IA32\_MCi\_STATUS MSR bits 56:55 are used to report the signaling of uncorrected recoverable errors and whether software must take recovery actions for uncorrected errors. Note that when MCG\_TES\_P is not set, bits 56:53 of the IA32\_MCi\_STATUS MSR are model-specific. If MCG\_TES\_P is set but MCG\_SER\_P is not set, bits 56:55 are reserved.

- MCG\_ELOG\_P (extended error logging) flag, bit 26 Indicates (when set) that the processor allows platform firmware to be invoked when an error is detected so that it may provide additional platform specific information in an ACPI format "Generic Error Data Entry" that augments the data included in machine check bank registers.

For additional information about extended error logging interface, see http://www.intel.com/content/www/us/en/architecture-and-technology/enhanced-mca-logging-xeon-paper.html

- MCG\_LMCE\_P (local machine check exception) flag, bit 27 Indicates (when set) that the following interfaces are present:

- an extended state LMCE\_S (located in bit 3 of IA32\_MCG\_STATUS), and

- the IA32\_MCG\_EXT\_CTL MSR, necessary to support Local Machine Check Exception (LMCE).

A non-zero MCG\_LMCE\_P indicates that, when LMCE is enabled as described in Section 15.3.1.5, some machine check errors may be delivered to only a single logical processor.

The effect of writing to the IA32\_MCG\_CAP MSR is undefined.

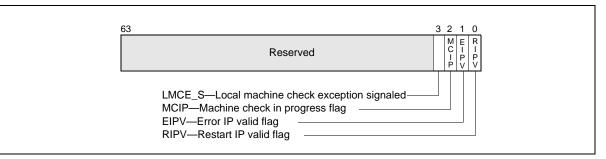

### 15.3.1.2 IA32\_MCG\_STATUS MSR

The IA32\_MCG\_STATUS MSR describes the current state of the processor after a machine-check exception has occurred (see Figure 15-3).

Figure 15-3 IA32\_MCG\_STATUS Register

Where:

• **RIPV (restart IP valid) flag, bit 0**— Indicates (when set) that program execution can be restarted reliably at the instruction pointed to by the instruction pointer pushed on the stack when the machine-check exception is generated. When clear, the program cannot be reliably restarted at the pushed instruction pointer.

- EIPV (error IP valid) flag, bit 1 Indicates (when set) that the instruction pointed to by the instruction pointer pushed onto the stack when the machine-check exception is generated is directly associated with the error. When this flag is cleared, the instruction pointed to may not be associated with the error.

- MCIP (machine check in progress) flag, bit 2 Indicates (when set) that a machine-check exception was generated. Software can set or clear this flag. The occurrence of a second Machine-Check Event while MCIP is set will cause the processor to enter a shutdown state. For information on processor behavior in the shutdown state, please refer to the description in Chapter 6, "Interrupt and Exception Handling": "Interrupt 8—Double Fault Exception (#DF)".

- LMCE\_S (local machine check exception signaled), bit 3 Indicates (when set) that a local machinecheck exception was generated. This indicates that the current machine-check event was delivered to only this logical processor.

Bits 63:04 in IA32\_MCG\_STATUS are reserved. An attempt to write to IA32\_MCG\_STATUS with any value other than 0 would result in #GP.

• • •

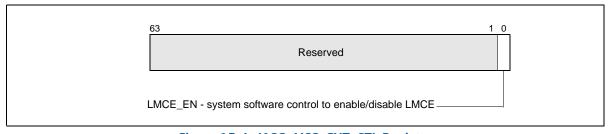

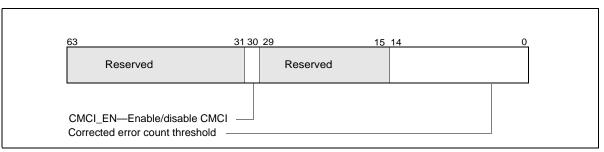

### 15.3.1.4 IA32\_MCG\_EXT\_CTL MSR

The IA32\_MCG\_EXT\_CTL MSR is present if the capability flag MCG\_LMCE\_P is set in the IA32\_MCG\_CAP MSR.

IA32\_MCG\_EXT\_CTL.LMCE\_EN (bit 0) allows the processor to signal some MCEs to only a single logical processor in the system.

If MCG\_LMCE\_P is not set in IA32\_MCG\_CAP, or platform software has not enabled LMCE by setting IA32\_FEATURE\_CONTROL.LMCE\_ON (bit 20), any attempt to write or read IA32\_MCG\_EXT\_CTL will result in #GP.

The IA32\_MCG\_EXT\_CTL MSR is cleared on RESET.

Figure Figure 15-4 shows the layout of the IA32\_MCG\_EXT\_CTL register

Figure 15-4 IA32\_MCG\_EXT\_CTL Register

where

LMCE\_EN (local machine check exception enable) flag, bit 0 - System software sets this to allow hardware to signal some MCEs to only a single logical processor. System software can set LMCE\_EN only if the platform software has configured IA32\_FEATURE\_CONTROL as described in Section 15.3.1.5.