# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

January 2015

**Notice**: The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-045

Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>.

Intel, the Intel logo, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 1997-2015, Intel Corporation. All Rights Reserved.

# Contents

| Revision History            | <br> | <br>    | <br> |       |       |  | • |  | <br>• |   | <br>•   | 4 |

|-----------------------------|------|---------|------|-------|-------|--|---|--|-------|---|---------|---|

| Preface                     | <br> | <br>    | <br> |       |       |  | • |  | <br>• |   | <br>•   | 7 |

| Summary Tables of Changes . | <br> | <br>    | <br> |       | <br>• |  | • |  | <br>• |   | <br>. : | 8 |

| Documentation Changes       | <br> | <br>• • | <br> | <br>• | <br>• |  | • |  | <br>• | • | <br>. ' | 9 |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul><li>Updated title.</li><li>There are no Documentation Changes for this revision of the document.</li></ul>                                                                                                               | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-21</li></ul>                                                                                                                                 | March 2009     |

| Revision | Description                                                                                      | Date           |

|----------|--------------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul>    | June 2009      |

| -025     | <ul> <li>Removed Documentation Changes 1-16</li> <li>Added Documentation Changes 1-18</li> </ul> | September 2009 |

| -026     | <ul> <li>Removed Documentation Changes 1-18</li> <li>Added Documentation Changes 1-15</li> </ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul>    | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul>    | June 2010      |

| -029     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | September 2010 |

| -030     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | January 2011   |

| -031     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul>    | April 2011     |

| -032     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-14</li></ul>    | May 2011       |

| -033     | <ul><li>Removed Documentation Changes 1-14</li><li>Added Documentation Changes 1-38</li></ul>    | October 2011   |

| -034     | <ul><li>Removed Documentation Changes 1-38</li><li>Added Documentation Changes 1-16</li></ul>    | December 2011  |

| -035     | <ul> <li>Removed Documentation Changes 1-16</li> <li>Added Documentation Changes 1-18</li> </ul> | March 2012     |

| -036     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-17</li></ul>    | May 2012       |

| -037     | <ul> <li>Removed Documentation Changes 1-17</li> <li>Added Documentation Changes 1-28</li> </ul> | August 2012    |

| -038     | <ul><li>Removed Documentation Changes 1-28</li><li>Add Documentation Changes 1-22</li></ul>      | January 2013   |

| -039     | <ul><li>Removed Documentation Changes 1-22</li><li>Add Documentation Changes 1-17</li></ul>      | June 2013      |

| -040     | <ul><li>Removed Documentation Changes 1-17</li><li>Add Documentation Changes 1-24</li></ul>      | September 2013 |

| -041     | <ul><li>Removed Documentation Changes 1-24</li><li>Add Documentation Changes 1-20</li></ul>      | February 2014  |

| -042     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-8</li></ul>       | February 2014  |

| -043     | <ul><li>Removed Documentation Changes 1-8</li><li>Add Documentation Changes 1-43</li></ul>       | June 2014      |

| -044     | <ul><li>Removed Documentation Changes 1-43</li><li>Add Documentation Changes 1-12</li></ul>      | September 2014 |

| -045     | <ul><li>Removed Documentation Changes 1-12</li><li>Add Documentation Changes 1-22</li></ul>      | January 2015   |

§

**Revision History**

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                         | Document Number/<br>Location |

|------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture                | 253665                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M   | 253666                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z   | 253667                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2C: Instruction Set Reference        | 326018                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1 | 253668                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2 | 253669                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3C: System Programming Guide, Part 3 | 326019                       |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(R)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes**

| No. | DOCUMENTATION CHANGES            |

|-----|----------------------------------|

| 1   | Updates to Chapter 1, Volume 1   |

| 2   | Updates to Chapter 4, Volume 1   |

| 3   | Updates to Chapter 5, Volume 1   |

| 4   | Updates to Chapter 8, Volume 1   |

| 5   | Updates to Chapter 11, Volume 1  |

| 6   | Updates to Chapter 13, Volume 1  |

| 7   | Updates to Appendix E, Volume 1  |

| 8   | Updates to Chapter 1, Volume 2A  |

| 9   | Updates to Chapter 3, Volume 2A  |

| 10  | Updates to Chapter 4, Volume 2B  |

| 11  | Updates to Chapter 1, Volume 3A  |

| 12  | Updates to Chapter 2, Volume 3A  |

| 13  | Updates to Chapter 4, Volume 3A  |

| 14  | Updates to Chapter 6, Volume 3A  |

| 15  | Updates to Chapter 8, Volume 3A  |

| 16  | Updates to Chapter 11, Volume 3A |

| 17  | Updates to Chapter 17, Volume 3B |

| 18  | Updates to Chapter 19, Volume 3B |

| 19  | Updates to Chapter 22, Volume 3B |

| 20  | Updates to Chapter 29, Volume 3B |

| 21  | Updates to Chapter 33, Volume 3C |

| 22  | Updates to Chapter 35, Volume 3C |

# **Documentation Changes**

### 1. Updates to Chapter 1, Volume 1

Change bars show changes to Chapter 1 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

• • •

# 1.1 INTEL<sup>®</sup> 64 AND IA-32 PROCESSORS COVERED IN THIS MANUAL

This manual set includes information pertaining primarily to the most recent Intel 64 and IA-32 processors, which include:

- Pentium<sup>®</sup> processors

- P6 family processors

- Pentium<sup>®</sup> 4 processors

- Pentium<sup>®</sup> M processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Pentium<sup>®</sup> D processors

- Pentium<sup>®</sup> processor Extreme Editions

- 64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors

- Intel<sup>®</sup> Core<sup>™</sup> Duo processor

- Intel<sup>®</sup> Core<sup>™</sup> Solo processor

- Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5100, 5300 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor X7000 and X6800 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX6000 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7100 series

- Intel<sup>®</sup> Pentium<sup>®</sup> Dual-Core processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 7200, 7300 series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000 and X9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series

- Intel<sup>®</sup> Core<sup>™</sup>2 Duo processor E8000, T9000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7 processor

- Intel<sup>®</sup> Core<sup>™</sup> i5 processor

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 product families

- Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor

- 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i5-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 product family

- 3rd generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families

- 4th generation Intel<sup>®</sup> Core<sup>™</sup> processors

- The Intel<sup>®</sup> Core<sup>™</sup> M processor family

- Intel<sup>®</sup> Core<sup>™</sup> i7-59xx Processor Extreme Edition

- Intel<sup>®</sup> Core<sup>™</sup> i7-49xx Processor Extreme Edition

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family

- Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600/1600 v3 product families

- 5th generation Intel<sup>®</sup> Core<sup>™</sup> processors

- Intel<sup>®</sup> Atom<sup>™</sup> processor Z8000 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor Z3400 series

- Intel<sup>®</sup> Atom<sup>™</sup> processor Z3500 series

P6 family processors are IA-32 processors based on the P6 family microarchitecture. This includes the Pentium<sup>®</sup> Pro, Pentium<sup>®</sup> II, Pentium<sup>®</sup> III, and Pentium<sup>®</sup> III Xeon<sup>®</sup> processors.

The Pentium<sup>®</sup> 4, Pentium<sup>®</sup> D, and Pentium<sup>®</sup> processor Extreme Editions are based on the Intel NetBurst<sup>®</sup> microarchitecture. Most early Intel<sup>®</sup> Xeon<sup>®</sup> processors are based on the Intel NetBurst<sup>®</sup> microarchitecture. Intel Xeon processor 5000, 7100 series are based on the Intel NetBurst<sup>®</sup> microarchitecture.

The Intel<sup>®</sup> Core<sup>™</sup> Duo, Intel<sup>®</sup> Core<sup>™</sup> Solo and dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV are based on an improved Pentium<sup>®</sup> M processor microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5100, 5300, 7200 and 7300 series, Intel<sup>®</sup> Pentium<sup>®</sup> dual-core, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Quad, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors are based on Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 5200, 5400, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Quad processor Q9000 series, and Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processor QX9000, X9000 series, Intel<sup>®</sup> Core<sup>™</sup>2 processor E8000 series are based on Enhanced Intel<sup>®</sup> Core<sup>™</sup> microarchitecture.

The Intel<sup>®</sup> Atom<sup>™</sup> processor family is based on the Intel<sup>®</sup> Atom<sup>™</sup> microarchitecture and supports Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>™</sup> i7 processor and Intel<sup>®</sup> Xeon<sup>®</sup> processor 3400, 5500, 7500 series are based on 45 nm Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> microarchitecture code name Westmere is a 32nm version of Intel<sup>®</sup> microarchitecture code name Nehalem. Intel<sup>®</sup> Xeon<sup>®</sup> processor 5600 series, Intel Xeon processor E7 and various Intel Core i7, i5, i3 processors are based on Intel<sup>®</sup> microarchitecture code name Westmere. These processors support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 family, Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/ 4800/2800 product families, Intel<sup>®</sup> Core<sup>™</sup> i7-3930K processor, and 2nd generation Intel<sup>®</sup> Core<sup>™</sup> i7-2xxx, Intel<sup>®</sup> Core<sup>™</sup> i3-2xxx processor series are based on the Intel<sup>®</sup> microarchitecture code name Sandy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E7-8800/4800/2800 v2 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v2 product family and the 3rd generation Intel<sup>®</sup> Core<sup>m</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-4600/2600/1600 v2 product families, Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2400/1400 v2 product families and Intel<sup>®</sup> Core<sup>m</sup> i7-49xx Processor Extreme Edition are based on the Intel<sup>®</sup> microarchitecture code name Ivy Bridge-E and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E3-1200 v3 product family and 4th Generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Haswell and support Intel 64 architecture.

The Intel<sup>®</sup> Core<sup>™</sup> M processor family and 5th generation Intel<sup>®</sup> Core<sup>™</sup> processors are based on the Intel<sup>®</sup> microarchitecture code name Broadwell and support Intel 64 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600/1600 v3 product families and the Intel<sup>®</sup> Core<sup>™</sup> i7-59xx Processor Extreme Edition are based on the Intel<sup>®</sup> microarchitecture code name Haswell-E and support Intel 64 architecture.

The Intel<sup>®</sup> Atom<sup>™</sup> processor Z8000 series is based on the Intel microarchitecture code name Airmont.

The Intel<sup>®</sup> Atom<sup>™</sup> processor Z3400 series and the Intel<sup>®</sup> Atom<sup>™</sup> processor Z3500 series are based on the Intel microarchitecture code name Silvermont.

P6 family, Pentium<sup>®</sup> M, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo processors, dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processor LV, and early generations of Pentium 4 and Intel Xeon processors support IA-32 architecture. The Intel<sup>®</sup> Atom<sup>™</sup> processor Z5xx series support IA-32 architecture.

The Intel<sup>®</sup> Xeon<sup>®</sup> processor 3000, 3200, 5000, 5100, 5200, 5300, 5400, 7100, 7200, 7300, 7400 series, Intel<sup>®</sup> Core<sup>™</sup>2 Duo, Intel<sup>®</sup> Core<sup>™</sup>2 Extreme processors, Intel Core 2 Quad processors, Pentium<sup>®</sup> D processors, Pentium<sup>®</sup> Dual-Core processor, newer generations of Pentium 4 and Intel Xeon processor family support Intel<sup>®</sup> 64 architecture.

IA-32 architecture is the instruction set architecture and programming environment for Intel's 32-bit microprocessors. Intel<sup>®</sup> 64 architecture is the instruction set architecture and programming environment which is the superset of Intel's 32-bit and 64-bit architectures. It is compatible with the IA-32 architecture.

•••

#### 2. Updates to Chapter 4, Volume 1

Change bars show changes to Chapter 4 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

• • •

### 4.8.3.2 Normalized and Denormalized Finite Numbers

Non-zero, finite numbers are divided into two classes: normalized and denormalized. The normalized finite numbers comprise all the non-zero finite values that can be encoded in a normalized real number format between zero and  $\infty$ . In the single-precision floating-point format shown in Figure 4-12, this group of numbers includes all the numbers with biased exponents ranging from 1 to  $254_{10}$  (unbiased, the exponent range is from  $-126_{10}$  to  $+127_{10}$ ).

When floating-point numbers become very close to zero, the normalized-number format can no longer be used to represent the numbers. This is because the range of the exponent is not large enough to compensate for shifting the binary point to the right to eliminate leading zeros.

When the biased exponent is zero, smaller numbers can only be represented by making the integer bit (and perhaps other leading bits) of the significand zero. The numbers in this range are called **denormalized** numbers. The use of leading zeros with denormalized numbers allows smaller numbers to be represented. However, this denormalization may cause a loss of precision (the number of significant bits is reduced by the leading zeros).

When performing normalized floating-point computations, an IA-32 processor normally operates on normalized numbers and produces normalized numbers as results. Denormalized numbers represent an **underflow** condition. The exact conditions are specified in Section , "4.9.1.5 Numeric Underflow Exception (#U)."

A denormalized number is computed through a technique called gradual underflow. Table 4-6 gives an example of gradual underflow in the denormalization process. Here the single-precision format is being used, so the minimum exponent (unbiased) is  $-126_{10}$ . The true result in this example requires an exponent of  $-129_{10}$  in order to have a normalized number. Since  $-129_{10}$  is beyond the allowable exponent range, the result is denormalized by inserting leading zeros until the minimum exponent of  $-126_{10}$  is reached.

| Operation       | Sign | Exponent* | Significand     |  |  |  |

|-----------------|------|-----------|-----------------|--|--|--|

| True Result     | 0    | –129      | 1.0101110000000 |  |  |  |

| Denormalize     | 0    | -128      | 0.1010111000000 |  |  |  |

| Denormalize     | 0    | –127      | 0.0101011100000 |  |  |  |

| Denormalize     | 0    | -126      | 0.0010101110000 |  |  |  |

| Denormal Result | 0    | -126      | 0.0010101110000 |  |  |  |

#### Table 4-6 Denormalization Process

\* Expressed as an unbiased, decimal number.

In the extreme case, all the significant bits are shifted out to the right by leading zeros, creating a zero result.

- The Intel 64 and IA-32 architectures deal with denormal values in the following ways:

- It avoids creating denormals by normalizing numbers whenever possible.

- It provides the floating-point underflow exception to permit programmers to detect cases when denormals are created.

- It provides the floating-point denormal-operand exception to permit procedures or programs to detect when denormals are being used as source operands for computations.

...

## 4.9.1.5 Numeric Underflow Exception (#U)

The processor detects a potential floating-point numeric underflow condition whenever the result of rounding with unbounded exponent (taking into account precision control for x87) is non-zero and tiny; that is, non-zero and less than the smallest possible normalized, finite value that will fit into the destination operand. Table 4-11 shows the threshold range for numeric underflow for each of the floating-point formats (assuming normalized results); underflow occurs when a rounded result falls strictly within the threshold range. The ability to detect and handle underflow is provided to prevent a very small result from propagating through a computation and causing another exception (such as overflow during division) to be generated at a later time. Results which trigger underflow are also potentially less accurate.

| Floating-Point Format     | Underflow Thresholds*           |

|---------------------------|---------------------------------|

| Single Precision          | x   < 1.0 * 2 <sup>-126</sup>   |

| Double Precision          | x   < 1.0 * 2 <sup>-1022</sup>  |

| Double Extended Precision | x   < 1.0 * 2 <sup>-16382</sup> |

#### Table 4-11 Numeric Underflow (Normalized) Thresholds

\* Where 'x' is the result rounded to destination precision with an unbounded exponent range.

How the processor handles an underflow condition, depends on two related conditions:

- creation of a tiny, non-zero result

- creation of an inexact result; that is, a result that cannot be represented exactly in the destination format

Which of these events causes an underflow exception to be reported and how the processor responds to the exception condition depends on whether the underflow exception is masked:

- Underflow exception masked The underflow exception is reported (the UE flag is set) only when the

result is both tiny and inexact. The processor returns a correctly signed result whose magnitude is less than

or equal to the smallest positive normal floating-point number to the destination operand, regardless of

inexactness.

- Underflow exception not masked The underflow exception is reported when the result is non-zero tiny, regardless of inexactness. The processor leaves the source and destination operands unaltered or stores a biased result in the destination operand (depending whether the underflow exception was generated during an SSE/SSE2/SSE3 floating-point operation or an x87 FPU operation) and invokes a software exception handler.

See the following sections for information regarding the numeric underflow exception when detected while executing x87 FPU instructions or while executing SSE/SSE2/SSE3 instructions:

- x87 FPU; Section 8.5.5, "Numeric Underflow Exception (#U)"

- SIMD floating-point exceptions; Section 11.5.2.5, "Numeric Underflow Exception (#U)"

• • •

## 3. Updates to Chapter 5, Volume 1

Change bars show changes to Chapter 5 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

-----

This chapter provides an abridged overview of Intel 64 and IA-32 instructions. Instructions are divided into the following groups:

- General purpose

- x87 FPU

- x87 FPU and SIMD state management

- Intel® MMX technology

- SSE extensions

- SSE2 extensions

- SSE3 extensions

- SSSE3 extensions

- SSE4 extensions

- AESNI and PCLMULQDQ

- Intel® AVX extensions

- F16C, RDRAND, RDSEED, FS/GS base access

- FMA extensions

- Intel® AVX2 extensions

- Intel® Transactional Synchronization extensions

- System instructions

- IA-32e mode: 64-bit mode instructions

- VMX instructions

- SMX instructions

- ADCX and ADOX

Table 5-1 lists the groups and IA-32 processors that support each group. More recent instruction set extensions are listed in Table 5-2. Within these groups, most instructions are collected into functional subgroups.

| Instruction Set<br>Architecture          | Intel 64 and IA-32 Processor Support                                                                                                                                                                                                                                     |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                          | All Intel 64 and IA-32 processors                                                                                                                                                                                                                                        |

| x87 FPU                                  | Intel486, Pentium, Pentium with MMX Technology, Celeron, Pentium Pro, Pentium II, Pentium II Xeon,<br>Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Atom processors |

| x87 FPU and SIMD State<br>Management     | Pentium II, Pentium II Xeon, Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M,<br>Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors, Intel Atom processors                                                                          |

| MMX Technology                           | Pentium with MMX Technology, Celeron, Pentium II, Pentium II Xeon, Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors, Intel Atom processors                                       |

| SSE Extensions                           | Pentium III, Pentium III Xeon, Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Atom processors                                                                                                       |

| SSE2 Extensions                          | Pentium 4, Intel Xeon processors, Pentium M, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo processors,<br>Intel Atom processors                                                                                                                                      |

| SSE3 Extensions                          | Pentium 4 supporting HT Technology (built on 90nm process technology), Intel Core Solo, Intel Core Duo,<br>Intel Core 2 Duo processors, Intel Xeon processor 3xxxx, 5xxx, 7xxx Series, Intel Atom processors                                                             |

| SSSE3 Extensions                         | Intel Xeon processor 3xxx, 5100, 5200, 5300, 5400, 5500, 5600, 7300, 7400, 7500 series, Intel Core 2<br>Extreme processors QX6000 series, Intel Core 2 Duo, Intel Core 2 Quad processors, Intel Pentium Dual-Core<br>processors, Intel Atom processors                   |

| IA-32e mode: 64-bit<br>mode instructions | Intel 64 processors                                                                                                                                                                                                                                                      |

| System Instructions                      | Intel 64 and IA-32 processors                                                                                                                                                                                                                                            |

| VMX Instructions                         | Intel 64 and IA-32 processors supporting Intel Virtualization Technology                                                                                                                                                                                                 |

| SMX Instructions                         | Intel Core 2 Duo processor E6x50, E8xxx; Intel Core 2 Quad processor Q9xxx                                                                                                                                                                                               |

#### Table 5-1 Instruction Groups in Intel 64 and IA-32 Processors

| Instruction Set<br>Architecture        | Processor Generation Introduction                                                                                                                                                                               |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSE4.1 Extensions                      | Intel Xeon processor 3100, 3300, 5200, 5400, 7400, 7500 series, Intel Core 2 Extreme processors QX9000 series, Intel Core 2 Quad processor Q9000 series, Intel Core 2 Duo processors 8000 series, T9000 series. |

| SSE4.2 Extensions,<br>CRC32, POPCNT    | Intel Core i7 965 processor, Intel Xeon processors X3400, X3500, X5500, X6500, X7500 series.                                                                                                                    |

| AESNI, PCLMULQDQ                       | InteL Xeon processor E7 series, Intel Xeon processors X3600, X5600, Intel Core i7 980X processor; Use CPUID to verify presence of AESNI and PCLMULQDQ across Intel Core processor families.                     |

| Intel AVX                              | Intel Xeon processor E3 and E5 families; 2nd Generation Intel Core i7, i5, i3 processor 2xxx families.                                                                                                          |

| F16C, RDRAND, FS/GS<br>base access     | 3rd Generation Intel Core processors, Intel Xeon processor E3-1200 v2 product family, Next Generation<br>Intel Xeon processors, Intel Xeon processor E5 v2 and E7 v2 families.                                  |

| FMA, AVX2, BMI1, BMI2,<br>TSX, INVPCID | Intel Xeon processor E3-1200 v3 product family; 4th Generation Intel Core processor family.                                                                                                                     |

| ADX, RDSEED, CLAC,<br>STAC             | Intel Core M processor family; 5th Generation Intel Core processor family.                                                                                                                                      |

Table 5-2 Recent Instruction Set Extensions Introduction in Intel 64 and IA-32 Processors

The following sections list instructions in each major group and subgroup. Given for each instruction is its mnemonic and descriptive names. When two or more mnemonics are given (for example, CMOVA/CMOVNBE), they represent different mnemonics for the same instruction opcode. Assemblers support redundant mnemonics for some instructions to make it easier to read code listings. For instance, CMOVA (Conditional move if above) and CMOVNBE (Conditional move if not below or equal) represent the same condition. For detailed information about specific instructions, see the *Intel® 64 and IA-32 Architectures Software Developer's Manual, Volumes 3A & 3B.*

• • •

## 5.1.15 BMI1, BMI2

| ANDN   | Bitwise AND of first source with inverted 2nd source operands. |

|--------|----------------------------------------------------------------|

| BEXTR  | Contiguous bitwise extract                                     |

| BLSI   | Extract lowest set bit                                         |

| BLSMSK | Set all lower bits below first set bit to 1                    |

| BLSR   | Reset lowest set bit                                           |

| BZHI   | Zero high bits starting from specified bit position            |

| LZCNT  | Count the number leading zero bits                             |

| MULX   | Unsigned multiply without affecting arithmetic flags           |

| PDEP   | Parallel deposit of bits using a mask                          |

| PEXT   | Parallel extraction of bits using a mask                       |

| RORX   | Rotate right without affecting arithmetic flags                |

| SARX   | Shift arithmetic right                                         |

| SHLX   | Shift logic left                                               |

| SHRX   | Shift logic right                                              |

| TZCNT  | Count the number trailing zero bits                            |

## 5.1.15.1 Detection of VEX-encoded GPR Instructions, LZCNT and TZCNT, PREFETCHW

VEX-encoded general-purpose instructions do not operate on any vector registers.

There are separate feature flags for the following subsets of instructions that operate on general purpose registers, and the detection requirements for hardware support are:

CPUID.(EAX=07H, ECX=0H):EBX.BMI1[bit 3]: if 1 indicates the processor supports the first group of advanced bit manipulation extensions (ANDN, BEXTR, BLSI, BLSMSK, BLSR, TZCNT);

CPUID.(EAX=07H, ECX=0H):EBX.BMI2[bit 8]: if 1 indicates the processor supports the second group of advanced bit manipulation extensions (BZHI, MULX, PDEP, PEXT, RORX, SARX, SHLX, SHRX);

CPUID.EAX=80000001H:ECX.LZCNT[bit 5]: if 1 indicates the processor supports the LZCNT instruction.

CPUID.EAX=80000001H:ECX.PREFTEHCHW[bit 8]: if 1 indicates the processor supports the PREFTEHCHW instruction. CPUID.(EAX=07H, ECX=0H):ECX.PREFTEHCHWT1[bit 0]: if 1 indicates the processor supports the PREFTEHCHWT1 instruction.

...

#### 4. Updates to Chapter 8, Volume 1

Change bars show changes to Chapter 8 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

...

## 8.3.7 Trigonometric Instructions

The following instructions perform four common trigonometric functions:

| FSIN    | Sine            |

|---------|-----------------|

| FCOS    | Cosine          |

| FSINCOS | Sine and cosine |

| FPTAN   | Tangent         |

| FPATAN  | Arctangent      |

These instructions operate on the top one or two registers of the x87 FPU register stack and they return their results to the stack. The source operands for the FSIN, FCOS, FSINCOS, and FPTAN instructions must be given in radians; the source operand for the FPATAN instruction is given in rectangular coordinate units.

The FSINCOS instruction returns both the sine and the cosine of a source operand value. It operates faster than executing the FSIN and FCOS instructions in succession.

The FPATAN instruction computes the arctangent of ST(1) divided by ST(0), returning a result in radians. It is useful for converting rectangular coordinates to polar coordinates.

See Section 8.3.8, "Approximation of Pi" and Section 8.3.10, "Transcendental Instruction Accuracy" for information regarding the accuracy of these instructions.

## 8.3.8 Approximation of Pi

When the argument (source operand) of a trigonometric function is within the domain of the function, the argument is automatically reduced by the appropriate multiple of  $2\pi$  through the same reduction mechanism used by the FPREM and FPREM1 instructions. The internal value of  $\pi$  (3.1415926...) that the x87 FPU uses for argument

reduction and other computations, denoted as Pi in the expression below. The numerical value of Pi can be written as:

Pi = 0.f \* 2<sup>2</sup>

where the fraction f is expressed in binary form as:

f = C90FDAA2 2168C234 C

(The spaces in the fraction above indicate 32-bit boundaries.)

The internal approximation Pi of the value  $\pi$  has a 66 significant bits. Since the exact value of  $\pi$  represented in binary has the next 3 bits equal to 0, it means that Pi is the value of  $\pi$  rounded to nearest-even to 68 bits, and also the value of  $\pi$  rounded toward zero (truncated) to 69 bits.

However, accuracy problems may arise because this relatively short finite approximation Pi of the number  $\pi$  is used for calculating the reduced argument of the trigonometric function approximations in the implementations of FSIN, FCOS, FSINCOS, and FPTAN. Alternately, this means that FSIN (x), FCOS (x), and FPTAN (x) are really approximating the mathematical functions sin (x \*  $\pi$  /Pi), cos (x \*  $\pi$  / Pi), and tan (x \*  $\pi$  / Pi), and not exactly sin (x), cos (x), and tan (x). (Note that FSINCOS is the equivalent of FSIN and FCOS combined together). The period of sin (x \*  $\pi$  /Pi) for example is 2\* Pi, and not  $2\pi$ .

See also Section 8.3.10, "Transcendental Instruction Accuracy" for more information on the accuracy of these functions.

•••

## 8.3.10 Transcendental Instruction Accuracy

New transcendental instruction algorithms were incorporated into the IA-32 architecture beginning with the Pentium processors. These new algorithms (used in transcendental instructions FSIN, FCOS, FSINCOS, FPTAN, FPATAN, F2XM1, FYL2X, and FYL2XP1) allow a higher level of accuracy than was possible in earlier IA-32 processors and x87 math coprocessors. The accuracy of these instructions is measured in terms of **units in the last place (ulp)**. For a given argument *x*, let *f*(*x*) and *F*(*x*) be the correct and computed (approximate) function values, respectively. The error in ulps is defined to be:

$$rror = \frac{f(x) - F(x)}{2^{k - 63}}$$

where *k* is an integer such that:

$$1 \le 2^{-k} f(x) < 2.$$

With the Pentium processor and later IA-32 processors, the worst case error on transcendental functions is less than 1 ulp when rounding to the nearest (even) and less than 1.5 ulps when rounding in other modes. The functions are guaranteed to be monotonic, with respect to the input operands, throughout the domain supported by the instruction.

However, for FSIN, FCOS, FSINCOS, and FPTAN which approximate periodic trigonometric functions, the previous statement about maximum ulp errors is true only when these instructions are applied to reduced argument (see Section 8.3.8, "Approximation of Pi"). This is due to the fact that only 66 significant bits are retained in the finite approximation Pi of the number  $\pi$  (3.1415926...), used internally for calculating the reduced argument in FSIN, FCOS, FSINCOS, and FPTAN. This approximation of  $\pi$  is not always sufficiently accurate for good argument reduction.

For single precision, the argument of FSIN, FCOS, FSINCOS, and FPTAN must exceed 200,000 radians in order for the error of the result to exceed 1 ulp when rounding to the nearest (even), or 1.5 ulps when rounding in other (directed) rounding modes.

For double and double-extended precision, the ulp errors will grow above these thresholds for arguments much smaller in magnitude. The ulp errors increase significantly when the argument approaches the value of  $\pi$  (or Pi) for FSIN, and when it approaches  $\pi/2$ (or Pi/2) for FCOS, FSINCOS, and FPTAN.

For all three IEEE precisions supported (32-bit single precision, 64-bit double precision, and 80-bit doubleextended precision), applying FSIN, FCOS, FSINCOS, or FPTAN to arguments larger than a certain value can lead to reduced arguments (calculated internally) that are inaccurate or even very inaccurate in some cases. This leads to equally inaccurate approximations of the corresponding mathematical functions. In particular, arguments that are close to certain values will lose significance when reduced, leading to increased relative (and ulp) errors in the results of FSIN, FCOS, FSINCOS, and FPTAN. These values are:

- any non-zero multiple of  $\pi$  for FSIN,

- any multiple of  $\pi$ , plus  $\pi/2$  for FCOS, and

- any non-zero multiple of  $\pi/2$  for FSINCOS and FPTAN.

If the arguments passed to FSIN, FCOS, FSINCOS, and FPTAN are not close to these values then even the finite approximation Pi of  $\pi$  used internally for argument reduction will allow for results that have good accuracy.

Therefore, in order to avoid such errors it is recommended to perform accurate argument reduction in software, and to apply FSIN, FCOS, FSINCOS, and FPTAN to reduced arguments only. Regardless of the target precision (single, double, or double-extended), it is safe to reduce the argument to a value smaller in absolute value than about  $3\pi/4$  for FSIN, and smaller than about  $3\pi/8$  for FCOS, FSINCOS, and FPTAN.

The thresholds shown above are not exact. For example, accuracy measurements show that the double-extended precision result of FSIN will not have errors larger than 0.72 ulp for |x| < 2.82 (so  $|x| < 3\pi/4$  will ensure good accuracy, as  $3\pi/4 < 2.82$ ). On the same interval, double precision results from FSIN will have errors at most slightly larger than 0.5 ulp, and single precision results will be correctly rounded in the vast majority of cases.

Likewise, the double-extended precision result of FCOS will not have errors larger than 0.82 ulp for |x| < 1.31 (so  $|x| < 3\pi/8$  will ensure good accuracy, as  $3\pi/8 < 1.31$ ). On the same interval, double precision results from FCOS will have errors at most slightly larger than 0.5 ulp, and single precision results will be correctly rounded in the vast majority of cases.

FSINCOS behaves similarly to FSIN and FCOS, combined as a pair.

Finally, the double-extended precision result of FPTAN will not have errors larger than 0.78 ulp for |x| < 1.25 (so  $|x| < 3\pi/8$  will ensure good accuracy, as  $3\pi/8 < 1.25$ ). On the same interval, double precision results from FPTAN will have errors at most slightly larger than 0.5 ulp, and single precision results will be correctly rounded in the vast majority of cases.

A recommended alternative in order to avoid the accuracy issues that might be caused by FSIN, FCOS, FSINCOS, and FPTAN, is to use good quality mathematical library implementations of the sin, cos, sincos, and tan functions, for example those from the Intel® Math Library available in the Intel® Compiler.

The instructions FYL2X and FYL2XP1 are two operand instructions and are guaranteed to be within 1 ulp only when y equals 1. When y is not equal to 1, the maximum ulp error is always within 1.35 ulps in round to nearest mode. (For the two operand functions, monotonicity was proved by holding one of the operands constant.)

• • •

## 8.5.5 Numeric Underflow Exception (#U)

The x87 FPU detects a potential floating-point numeric underflow condition whenever the result of an arithmetic instruction is non-zero and tiny; that is, the magnitude of the rounded result with unbounded exponent is non-zero and less than the smallest possible normalized, finite value that will fit into the floating-point format of the destination operand. (See Section 4.9.1.5, "Numeric Underflow Exception (#U)," for additional information about the numeric underflow exception.)

Like numeric overflow, numeric underflow can occur on arithmetic operations where the result is stored in an x87 FPU data register. It can also occur on store floating-point operations (with the FST and FSTP instructions), where a within-range value in a data register is stored in memory in the smaller single-precision or double-precision floating-point formats. A numeric underflow exception cannot occur when storing values in an integer or BCD integer format, because a value with magnitude less than 1 is always rounded to an integral value of 0 or 1, depending on the rounding mode in effect.

The flag (UE) for the numeric-underflow exception is bit 4 of the x87 FPU status word, and the mask bit (UM) is bit 4 of the x87 FPU control word.

When a numeric-underflow condition occurs and the exception is masked, the x87 FPU performs the operation described in Section 4.9.1.5, "Numeric Underflow Exception (#U)."

When the exception is not masked, the action of the x87 FPU depends on whether the instruction is supposed to store the result in a memory location or on the x87 FPU resister stack.

Destination is a memory location — (Can occur only with a store instruction.) The UE flag is set and a

software exception handler is invoked (see Section 8.7, "Handling x87 FPU Exceptions in Software"). The topof-stack pointer (TOP) and source and destination operands remain unchanged, and no result is stored in

memory.

Because the data in the stack is in double extended-precision format, the exception handler has the option either of re-exchanges the store instruction after proper adjustment of the operand or of rounding the significand on the stack to the destination's precision as the standard requires. The exception handler should ultimately store a value into the destination location in memory if the program is to continue.

• Destination is the register stack — The significand of the result is rounded according to current settings of the precision and rounding control bits in the x87 FPU control word and the exponent of the result is adjusted by multiplying it by 2<sup>24576</sup>. (For instructions not affected by the precision field, the significand is rounded to double extended precision.) The resulting value is stored in the destination operand. Condition code bit C1 in the x87 FPU status register (acting here as a "round-up bit") is set if the significand was rounded upward and cleared if the result was rounded toward 0. After the result is stored, the UE flag is set and a software exception handler is invoked. The scaling bias value 24,576 is the same as is used for the overflow exception and has the same effect, which is to translate the result as nearly as possible to the middle of the double extended-precision floating-point exponent range.

When using the FSCALE instruction, massive underflow can occur, where the magnitude of the result is too small to be represented, even with a bias-adjusted exponent. Here, if underflow occurs again after the result has been biased, a properly signed 0 is stored in the destination operand.

•••

#### 5. Updates to Chapter 11, Volume 1

Change bars show changes to Chapter 11 of the  $Intel^{\ensuremath{\mathbb{R}}}$  64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

\_\_\_\_\_

• • •

## 11.5.2.5 Numeric Underflow Exception (#U)

The processor reports a numeric underflow exception whenever the magnitude of the rounded result of an arithmetic instruction, with unbounded exponent, is less than the smallest possible normalized, finite value that will fit in the destination operand and the numeric-underflow exception is not masked. If the numeric underflow exception is masked, both underflow and the inexact-result condition must be detected before numeric underflow is reported. This exception can be generated with the ADDPS, ADDSS, ADDPD, ADDSD, SUBPS, SUBSS, SUBPD, SUBSD, MULPS, MULSS, MULPD, MULSD, DIVPS, DIVSS, DIVPD, DIVSD, CVTPD2PS, CVTSD2SS, ADDSUBPD, ADDSUBPS, HADDPD, HADDPS, HSUBPD, and HSUBPS instructions. The flag (UE) and mask (UM) bits for the numeric underflow exception are bits 4 and 11, respectively, in the MXCSR register.

The flush-to-zero flag (bit 15) of the MXCSR register provides an additional option for handling numeric underflow exceptions. When this flag is set and the numeric underflow exception is masked, tiny results are returned as a zero with the sign of the true result (see Section 10.2.3.3, "Flush-To-Zero").

Underflow will occur when a tiny non-zero result is detected (the result has to be also inexact if underflow exceptions are masked), as described in the IEEE Standard 754-2008. While DAZ does not affect the rules for signaling IEEE exceptions, operations on denormal inputs might have different results when DAZ=1. As a consequence, DAZ can have an effect on the floating-point exceptions - including the underflow exception - when observed for a given operation involving denormal inputs.

See Section 4.9.1.5, "Numeric Underflow Exception (#U)," for more information about the numeric underflow exception. See Section 11.5.4, "Handling SIMD Floating-Point Exceptions in Software," for information on handling unmasked exceptions.

...

#### 6. Updates to Chapter 13, Volume 1

Change bars show changes to Chapter 13 of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture.

#### \_\_\_\_\_

The XSAVE feature set extends the functionality of the FXSAVE and FXRSTOR instructions (see Section 10.5, "FXSAVE and FXRSTOR Instructions") by supporting the saving and restoring of processor state in addition to the x87 execution environment (**x87 state**) and the registers used by the streaming SIMD extensions (**SSE state**).

The **XSAVE feature set** comprises eight instructions. XGETBV and XSETBV allow software to read and write the extended control register XCR0, which controls the operation of the XSAVE feature set. XSAVE, XSAVEOPT, XSAVEC, and XSAVES are four instructions that save processor state to memory; XRSTOR and XRSTORS are corresponding instructions that load processor state from memory. XGETBV, XSAVE, XSAVEOPT, XSAVEC, and XRSTOR can be executed at any privilege level; XSETBV, XSAVES, and XRSTORS can be executed only if CPL = 0.

The XSAVE feature set organizes the state that manages into **state components**. Operation of the instructions is based on **state-component bitmaps** that have the same format as XCR0: each bit corresponds to a state component. Section 13.1 discusses these state components and bitmaps in more detail.

Section 13.2 describes how the processor enumerates support for the XSAVE feature set and for **XSAVE-enabled features** (those features that require use of the XSAVE feature set for their enabling). Section 13.3 explains how software can enable the XSAVE feature set and XSAVE-enabled features.

The XSAVE feature set allows saving and loading processor state from a region of memory called an **XSAVE area**. Section 13.4 presents details of the XSAVE area and its organization. Each XSAVE-managed state component is associated with a section of the XSAVE area. Section 13.5 describes in detail each of the XSAVE-managed state components.

Section 13.6 through Section 13.11 describe the operation of XSAVE, XRSTOR, XSAVEOPT, XSAVEC, XSAVES, and XRSTORS, respectively.

# 13.1 XSAVE-SUPPORTED FEATURES AND STATE-COMPONENT BITMAPS

The XSAVE feature set supports the saving and restoring of **state components**, each of which is a discrete set of processor registers (or parts of registers). In general, each such state component corresponds to a particular CPU feature. Such a feature is **XSAVE-supported**. Some XSAVE-supported features use registers in multiple XSAVE-managed state components.

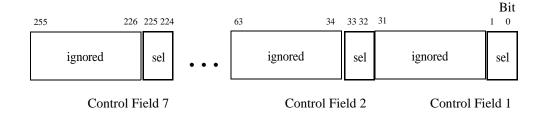

The XSAVE feature set organizes the state components of the XSAVE-supported features using **state-component bitmaps**. A state-component bitmap comprises 64 bits; each bit in such a bitmap corresponds to a single state component. The following bits are defined in state-component bitmaps:

- Bit 0 corresponds to the state component used for the x87 FPU execution environment (x87 state). See Section 13.5.1.

- Bit 1 corresponds to the state component used for registers used by the streaming SIMD extensions (**SSE** state). See Section 13.5.2.

- Bit 2 corresponds to the state component used for the additional register state used by the Intel<sup>®</sup> Advanced Vector Extensions (AVX state). See Section 13.5.3.

Other bits in the range 62:3 are not currently defined in state-component bitmaps and are reserved for future expansion. As individual state component is defined within bits 62:3, additional sub-sections are updated within Section 13.5 over time. Bit 63 is used for special functionality in some bitmaps and does not correspond to any state component.

The state component corresponding to bit *i* of state-component bitmaps is called **state component** *i*. Thus, x87 state is state component 0; SSE state is state component 1; and AVX state is state component 2.

The XSAVE feature set uses state-component bitmaps in multiple ways. Most of the instructions use an implicit operand (in EDX:EAX), called the **instruction mask**, which is the state-component bitmap that specifies the state components on which the instruction operates.

Extended control register XCR0 contains a state-component bitmap that specifies the state components that software has enabled the full XSAVE feature set to manage. If the bit corresponding to a state component is clear in XCR0, the following instructions in the XSAVE feature set will not operate on that state component, regardless of the value of the instruction mask: XSAVE, XRSTOR, XSAVEOPT, and XSAVEC. Details of the operation of these instructions are given in Section 13.6 through Section 13.9.

The IA32\_XSS MSR (index DA0H) contains a state-component bitmap that specifies the state components that software has enabled XSAVES and XRSTORS to manage. If the bit corresponding to a state component is clear in the logical-OR of XCR0 and IA32\_XSS (XCR0 | IA32\_XSS), XSAVES and XRSTORS will not operate on that state component, regardless of the value of the instruction mask. Details of the operation of these instructions are given in Section 13.10 and Section 13.11.

Some XSAVE-supported features can be used only if XCR0 has been configured so that the features' state components can be managed by the XSAVE feature set. Such state components and features are **XSAVE-enabled**. In general, the processor will not modify (or allow modification of) the registers of a state component of an XSAVEenabled feature if the bit corresponding to that state component is clear in XCR0. (If software clears such a bit in XCR0, the processor preserves the corresponding state component.) If an XSAVE-enabled feature has not been fully enabled in XCR0, execution of any instruction defined for that feature causes an invalid-opcode exception (#UD).

As will be explained in Section 13.3, the XSAVE feature set is enabled only if CR4.OSXSAVE[bit 18] = 1. If CR4.OSXSAVE = 0, the processor treats XSAVE-enabled state features and their state components as if all bits in XCR0 were clear; the state components cannot be modified and the features' instructions cannot be executed.

The state components for x87 state and for SSE state are XSAVE-managed but the corresponding features are not XSAVE-enabled. Processors allow modification of this state, as well as execution of x87 FPU instructions and SSE instructions, regardless of the value of CR4.OSXSAVE and XCR0.

•••

# **13.3 ENABLING THE XSAVE FEATURE SET AND XSAVE-ENABLED FEATURES**

Software enables the XSAVE feature set by setting CR4.OSXSAVE[bit 18] to 1 (e.g., with the MOV to CR4 instruction). If this bit is 0, execution of any of XGETBV, XRSTOR, XRSTORS, XSAVE, XSAVEC, XSAVEOPT, XSAVES, and XSETBV causes an invalid-opcode exception (#UD). When CR4.OSXSAVE = 1 and CPL = 0, executing the XSETBV instruction with ECX = 0 writes the 64-bit value in EDX:EAX to XCR0 (EAX is written to XCR0[31:0] and EDX to XCR0[63:32]). (Execution of the XSETBV instruction causes a general-protection fault - #GP - if CPL > 0.) The following items provide details regarding individual bits in XCR0:

- XCR0[0] is associated with x87 state. (See Section 13.5.1.) XCR0[0] is always 1. It has that value coming out of RESET. Executing the XSETBV instruction causes a general-protection fault (#GP) if ECX = 0 and EAX[0] is 0.

- XCR0[1] is associated with SSE state. (See Section 13.5.2.) Software can use the XSAVE feature set to manage SSE state only if XCR0[1] = 1. The value of XCR0[1] in no way determines whether software can execute SSE instructions (these instructions can be executed even if XCR0[1] = 0).

XCR0[1] is 0 coming out of RESET. As noted in Section 13.2, every processor that supports the XSAVE feature set allows software to set XCR0[1].

XCR0[2] is associated with AVX state. (See Section 13.5.3.) Software can use the XSAVE feature set to

manage AVX state only if XCR0[2] = 1. In addition, software can execute AVX instructions only if

CR4.OSXSAVE = XCR0[1] = XCR0[2] = 1. Otherwise, any execution of an AVX instruction causes an invalidopcode exception (#UD).

XCR0[2] is 0 coming out of RESET. As noted in Section 13.2, a processor allows software to set XCR0[2] if and only if CPUID.(EAX=0DH,ECX=0):EAX[2] = 1. In addition, executing the XSETBV instruction causes a general-protection fault (#GP) if ECX = 0 and EAX[2:1] has the value 10b; that is, software cannot enable the XSAVE feature set for AVX state but not for SSE state.

• XCR0[63:3] is reserved. Executing the XSETBV instruction causes a general-protection fault (#GP) if ECX = 0 and any bit in EDX or EAX[31:3] is not 0. Bits 63:3 of XCR0 are all 0 coming out of RESET.

Software operating with CPL > 0 may need to determine whether the XSAVE feature set and certain XSAVEenabled features have been enabled. If CPL > 0, execution of the MOV from CR4 instruction causes a generalprotection fault (#GP). The following alternative mechanisms allow software to discover the enabling of the XSAVE feature set regardless of CPL:

- The value of CR4.OSXSAVE is returned in CPUID.1:ECX.OSXSAVE[bit 27]. If software determines that CPUID.1:ECX.OSXSAVE = 1, the processor supports the XSAVE feature set and the feature set has been enabled in CR4.

- Executing the XGETBV instruction with ECX = 0 returns the value of XCR0 in EDX:EAX. XGETBV can be executed if CR4.OSXSAVE = 1 (if CPUID.1:ECX.OSXSAVE = 1), regardless of CPL.

Thus, software can use the following algorithm to determine the support and enabling for the XSAVE feature set:

- 1. Use CPUID to discover the value of CPUID.1:ECX.OSXSAVE.

- If the bit is 0, either the XSAVE feature set is not supported by the processor or has not been enabled by software. Either way, the XSAVE feature set is not available, nor are XSAVE-enabled features such as AVX.

- If the bit is 1, the processor supports the XSAVE feature set including the XGETBV instruction and it has been enabled by software. The XSAVE feature set can be used to manage x87 state (because XCR0[0] is always 1). Software requiring more detailed information can go on to the next step.

- Execute XGETBV with ECX = 0 to discover the value of XCR0. If XCR0[1] = 1, the XSAVE feature set can be used to manage SSE state. If XCR0[2] = 1, the XSAVE feature set can be used to manage AVX state and software can execute AVX instructions.

The IA32\_XSS MSR is zero coming out of RESET. If CR4.OSXSAVE = 1, CPUID.(EAX=0DH,ECX=1):EAX[3] = 1, and CPL = 0, executing the WRMSR instruction with ECX = DA0H writes the 64-bit value in EDX:EAX to the IA32\_XSS MSR (EAX is written to IA32\_XSS[31:0] and EDX to IA32\_XSS[63:32]). There is no mechanism by which software operating with CPL > 0 can discover the value of the IA32\_XSS MSR.

•••

# 13.4.3 Extended Region of an XSAVE Area

The extended region of an XSAVE area starts at byte offset 576 from the area's base address. The size of the extended region is determined by which state components the processor supports and which bits have been set in XCR0 | IA32\_XSS (see Section 13.3).

The XSAVE feature set uses the extended area for each state component *i*, where  $i \ge 2$ . (Currently, the extended region is used only for AVX state, which is state component 2.)

The extended region of the an XSAVE area may have one of two formats. The **standard format** is supported by all processors that support the XSAVE feature set; the **compacted format** is supported by those processors that support the compaction extensions to the XSAVE feature set (see Section 13.2). Bit 63 of the XCOMP\_BV field in the XSAVE header (see Section 13.4.2) indicates which format is used.

The following items describe the two possible formats of the extended region:

- Standard format. Each state component *i* (*i* ≥ 2) is located at the byte offset from the base address of the XSAVE area enumerated in CPUID.(EAX=0DH,ECX=*i*):EBX. (CPUID.(EAX=0DH,ECX=*i*):EAX enumerates the number of bytes required for state component *i*.

- **Compacted format**. Each state component *i* (*i* ≥ 2) is located at a byte offset from the base address of the XSAVE area based on the XCOMP\_BV field in the XSAVE header:

- If  $XCOMP_BV[i] = 0$ , state component *i* is not in the XSAVE area.

- If XCOMP\_BV[i] = 1, the following items apply:

- If XCOMP\_BV[*j*] = 0 for every *j*, 2 ≤ *j* < *i*, state component *i* is located at a byte offset 576 from the base address of the XSAVE area. (This item applies if *i* is the first bit set in bits 62:2 of the XCOMP\_BV; it implies that state component *i* is located at the beginning of the extended region.)

- Otherwise, let j, 2 ≤ j < i, be the greatest value such that XCOMP\_BV[j] = 1. Then state component i is located at a byte offset X from the location of state component j, where X is the number of bytes required for state component j as enumerated in CPUID.(EAX=0DH,ECX=j):EAX. (This item implies that state component i immediately follows the preceding state component whose bit is set in XCOMP\_BV.)</li>

...

## 13.5.1 x87 State

Instructions in the XSAVE feature set can manage the same state of the x87 FPU execution environment (**x87** state) that can be managed using the FXSAVE and FXRSTOR instructions. They organize all x87 state in the legacy region of the XSAVE area (see Section 13.4.1). This region is illustrated in Table 13-1; the x87 state is listed below, along with details of its interactions with the XSAVE feature set:

- Bytes 1:0, 3:2, 7:6. These are used for the x87 FPU Control Word (FCW), the x87 FPU Status Word (FSW), and the x87 FPU Opcode (FOP), respectively.

- Byte 4 is used for an abridged version of the x87 FPU Tag Word (FTW). The following items describe its usage:

- For each j, 0 ≤ j ≤ 7, XSAVE, XSAVEOPT, XSAVEC, and XSAVES save a 0 into bit j of byte 4 if x87 FPU data register STj has a empty tag; otherwise, XSAVE, XSAVEOPT, XSAVEC, and XSAVES save a 1 into bit j of byte 4.

- For each *j*,  $0 \le j \le 7$ , XRSTOR and XRSTORS establish the tag value for x87 FPU data register ST*j* as follows. If bit *j* of byte 4 is 0, the tag for ST*j* in the tag register for that data register is marked empty (11B); otherwise, the x87 FPU sets the tag for ST*j* based on the value being loaded into that register (see below).

- Bytes 15:8 are used as follows:

- If the instruction has no REX prefix, or if REX.W = 0:

- Bytes 11:8 are used for bits 31:0 of the x87 FPU Instruction Pointer Offset (FIP).

- If CPUID.(EAX=07H,ECX=0H):EBX[bit 13] = 0, bytes 13:12 are used for x87 FPU Instruction Pointer Selector (FPU CS). Otherwise, XSAVE, XSAVEOPT, XSAVEC, and XSAVES save these bytes as 0000H, and XRSTOR and XRSTORS ignore them.

- Bytes 15:14 are not used.

- If the instruction has a REX prefix with REX.W = 1, bytes 15:8 are used for the full 64 bits of FIP.

- Bytes 23:16 are used as follows:

- If the instruction has no REX prefix, or if REX.W = 0:

- Bytes 19:16 are used for bits 31:0 of the x87 FPU Data Pointer Offset (FDP).

- If CPUID.(EAX=07H,ECX=0H):EBX[bit 13] = 0, bytes 21:20 are used for x87 FPU Data Pointer Selector (FPU DS). Otherwise, XSAVE, XSAVEOPT, XSAVEC, and XSAVES save these bytes as 0000H; and XRSTOR and XRSTORS ignore them.

- Bytes 23:22 are not used.

- If the instruction has a REX prefix with REX.W = 1, bytes 23:16 are used for the full 64 bits of FDP.

- Bytes 31:24 are used for SSE state (see Section 13.5.2).

- Bytes 159:32 are used for the registers ST0–ST7 (MM0–MM7). Each of the 8 register is allocated a 128-bit region, with the low 80 bits used for the register and the upper 48 bits unused.

x87 state is XSAVE-managed but the x87 FPU feature is not XSAVE-enabled. The XSAVE feature set can operate on x87 state only if the feature set is enabled (CR4.OSXSAVE = 1).<sup>1</sup> Software can otherwise use x87 state even if the XSAVE feature set is not enabled.

# 13.5.2 SSE State

Instructions in the XSAVE feature set can manage the registers used by the streaming SIMD extensions (**SSE state**) just as the FXSAVE and FXRSTOR instructions do. They organize all SSE state in the legacy region of the XSAVE area (see Section 13.4.1). This region is illustrated in Table 13-1; the SSE state is listed below, along with details of its interactions with the XSAVE feature set:

- Bytes 23:0 are used for x87 state (see Section 13.5.1).

- Bytes 27:24 are used for the MXCSR register. XRSTOR and XRSTORS generate general-protection faults (#GP) in response to attempts to set any of the reserved bits of the MXCSR register.<sup>2</sup>

- Bytes 31:28 are used for the MXCSR\_MASK value. XRSTOR and XRSTORS ignore this field.

- Bytes 159:32 are used for x87 state.

- Bytes 287:160 are used for the registers XMM0–XMM7.

- Bytes 415:288 are used for the registers XMM8-XMM15. These fields are used only in 64-bit mode. Executions of XSAVE, XSAVEOPT, XSAVEC, and XSAVES outside 64-bit mode do not write to these bytes; executions of XRSTOR and XRSTORS outside 64-bit mode do not read these bytes and do not update XMM8-XMM15.

SSE state is XSAVE-managed but the SSE feature is not XSAVE-enabled. The XSAVE feature set can operate on SSE state only if the feature set is enabled (CR4.OSXSAVE = 1) and has been configured to manage SSE state (XCR0[1] = 1). Software can otherwise use SSE state even if the XSAVE feature set is not enabled or has not been configured to manage SSE state.

<sup>1.</sup> The processor ensures that XCR0[0] is always 1.

<sup>2.</sup> While MXCSR and MXCSR\_MASK are part of SSE state, their treatment by the XSAVE feature set is not the same as that of the XMM registers. See Section 13.6 through Section 13.10 for details.

# 13.5.3 AVX State

The register state used by the Intel<sup>®</sup> Advanced Vector Extensions (AVX) comprises the MXCSR register and 16 256-bit vector registers called YMM0–YMM15. The low 128 bits of each register YMM*i* is identical to the SSE register XMM*i*. Thus, the new state register state added by AVX comprises the upper 128 bits of the registers YMM0–YMM15. These 16 128-bit values are denoted YMM0\_H–YMM15\_H and are collectively called **AVX state**.

As noted in Section 13.1, the XSAVE feature set manages AVX state as state component 2. Thus, AVX state is located in the extended region of the XSAVE area (see Section 13.4.3).

As noted in Section 13.2, CPUID.(EAX=0DH,ECX=2):EBX enumerates the offset (in bytes, from the base of the XSAVE area) of the section of the extended region of the XSAVE area used for AVX state (when the standard format of the extended region is used). CPUID returns this value as 576. CPUID.(EAX=0DH,ECX=2):EAX enumerates the size (in bytes) required for AVX state. CPUID returns this value as 256.

The XSAVE feature set partitions YMM0\_H-YMM15\_H in a manner similar to that used for the XMM registers (see Section 13.5.2). Bytes 127:0 of the AVX-state section are used for YMM0\_H-YMM7\_H. Bytes 255:128 are used for YMM8\_H-YMM15\_H, but they are used only in 64-bit mode. (Executions of XSAVE, XSAVEOPT, XSAVEC, and XSAVES outside 64-bit mode do not write to bytes 255:128; executions of XRSTOR and XRSTORS outside 64-bit mode do not read these bytes and do not update YMM8\_H-YMM15\_H.)

AVX state is XSAVE-managed and the AVX feature is XSAVE-enabled. The XSAVE feature set can operate on AVX state only if the feature set is enabled (CR4.OSXSAVE = 1) and has been configured to manage AVX state (XCR0[1] = XCR0[2] = 1).<sup>1</sup> AVX instructions cannot be used unless the XSAVE feature set is enabled and has been configured to manage AVX state.

...

# 13.10 OPERATION OF XSAVES

The operation of XSAVES is similar to that of XSAVEC. The main differences are (1) XSAVES can be executed only if CPL = 0; (2) XSAVES can operate on the state components whose bits are set in XCR0 | IA32\_XSS; and (3) XSAVES uses the modified optimization (see Section 13.5.4). See Section 13.2 for details of how to determine whether XSAVES is supported.

The XSAVES instruction takes a single memory operand, which is an XSAVE area. In addition, the register pair EDX:EAX is an implicit operand used as a state-component bitmap (see Section 13.1) called the **instruction mask**. EDX:EAX & (XCR0 | IA32\_XSS) (the logical AND the instruction mask with the logical OR of XCR0 and IA32\_XSS) is the **requested-feature bitmap** (**RFBM**) of the state components to be saved.

The following conditions cause execution of the XSAVES instruction to generate a fault:

- If the XSAVE feature set is not enabled (CR4.OSXSAVE = 0), an invalid-opcode exception (#UD) occurs.

- If CR0.TS[bit 3] is 1, a device-not-available exception (#NM) occurs.

- If CPL > 0 or if the address of the XSAVE area is not 64-byte aligned, a general-protection exception (#GP) occurs.<sup>2</sup>

If none of these conditions cause a fault, execution of XSAVES writes the XSTATE\_BV field of the XSAVE header (see Section 13.4.2), setting XSTATE\_BV[i] (0  $\leq i \leq 63$ ) as follows:

• If RFBM[*i*] = 0, XSTATE\_BV[*i*] is written as 0.