# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

**Documentation Changes**

June 2024

**Notice:** The Intel<sup>®</sup> 64 and IA-32 architectures may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the specification updates.

Document Number: 252046-076

#### **Notices & Disclaimers**

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

All product plans and roadmaps are subject to change without notice.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, with the sole exception that a) you may publish an unmodified copy and b) code included in this document is licensed subject to the Zero-Clause BSD open source license (OBSD), <a href="https://opensource.org/licenses/0BSD">https://opensource.org/licenses/0BSD</a>. You may create software implementations based on this document and in compliance with the foregoing that are intended to execute on the Intel product(s) referenced in this document. No rights are granted to create modifications or derivatives of this document.

$\bigcirc$  Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

# Contents

| Revision History          | <br> | <br>• |       | <br>• |       | <br>• | • |       |  |   | • |     | • | <br>. 4 |

|---------------------------|------|-------|-------|-------|-------|-------|---|-------|--|---|---|-----|---|---------|

| Preface                   | <br> | <br>• |       |       |       |       | • |       |  |   | • |     | • | <br>. 7 |

| Summary Tables of Changes |      | <br>• | <br>• |       |       |       | • |       |  |   | • |     | • | <br>. 8 |

| Documentation Changes     | <br> | <br>• | <br>• | <br>• | <br>• | <br>• | • | <br>• |  | • | • | • • | • | <br>. 9 |

| Revision | Description                                                                                                                                                                                                                  | Date           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001     | Initial release                                                                                                                                                                                                              | November 2002  |

| -002     | <ul> <li>Added 1-10 Documentation Changes.</li> <li>Removed old Documentation Changes items that already have been incorporated in the published Software Developer's manual</li> </ul>                                      | December 2002  |

| -003     | <ul> <li>Added 9 -17 Documentation Changes.</li> <li>Removed Documentation Change #6 - References to bits Gen and Len Deleted.</li> <li>Removed Documentation Change #4 - VIF Information Added to CLI Discussion</li> </ul> | February 2003  |

| -004     | <ul><li>Removed Documentation changes 1-17.</li><li>Added Documentation changes 1-24.</li></ul>                                                                                                                              | June 2003      |

| -005     | <ul><li>Removed Documentation Changes 1-24.</li><li>Added Documentation Changes 1-15.</li></ul>                                                                                                                              | September 2003 |

| -006     | Added Documentation Changes 16- 34.                                                                                                                                                                                          | November 2003  |

| -007     | <ul><li>Updated Documentation changes 14, 16, 17, and 28.</li><li>Added Documentation Changes 35-45.</li></ul>                                                                                                               | January 2004   |

| -008     | <ul><li>Removed Documentation Changes 1-45.</li><li>Added Documentation Changes 1-5.</li></ul>                                                                                                                               | March 2004     |

| -009     | Added Documentation Changes 7-27.                                                                                                                                                                                            | May 2004       |

| -010     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1.</li></ul>                                                                                                                                 | August 2004    |

| -011     | Added Documentation Changes 2-28.                                                                                                                                                                                            | November 2004  |

| -012     | <ul><li>Removed Documentation Changes 1-28.</li><li>Added Documentation Changes 1-16.</li></ul>                                                                                                                              | March 2005     |

| -013     | <ul> <li>Updated title.</li> <li>There are no Documentation Changes for this revision of the document.</li> </ul>                                                                                                            | July 2005      |

| -014     | Added Documentation Changes 1-21.                                                                                                                                                                                            | September 2005 |

| -015     | <ul><li>Removed Documentation Changes 1-21.</li><li>Added Documentation Changes 1-20.</li></ul>                                                                                                                              | March 9, 2006  |

| -016     | Added Documentation changes 21-23.                                                                                                                                                                                           | March 27, 2006 |

| -017     | <ul><li>Removed Documentation Changes 1-23.</li><li>Added Documentation Changes 1-36.</li></ul>                                                                                                                              | September 2006 |

| -018     | Added Documentation Changes 37-42.                                                                                                                                                                                           | October 2006   |

| -019     | <ul><li>Removed Documentation Changes 1-42.</li><li>Added Documentation Changes 1-19.</li></ul>                                                                                                                              | March 2007     |

| -020     | Added Documentation Changes 20-27.                                                                                                                                                                                           | May 2007       |

| -021     | <ul><li>Removed Documentation Changes 1-27.</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                | November 2007  |

| -022     | <ul><li>Removed Documentation Changes 1-6</li><li>Added Documentation Changes 1-6</li></ul>                                                                                                                                  | August 2008    |

| -023     | <ul> <li>Removed Documentation Changes 1-6</li> <li>Added Documentation Changes 1-21</li> </ul>                                                                                                                              | March 2009     |

| Revision | Description                                                                                   | Date           |

|----------|-----------------------------------------------------------------------------------------------|----------------|

| -024     | <ul><li>Removed Documentation Changes 1-21</li><li>Added Documentation Changes 1-16</li></ul> | June 2009      |

| -025     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | September 2009 |

| -026     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-15</li></ul> | December 2009  |

| -027     | <ul><li>Removed Documentation Changes 1-15</li><li>Added Documentation Changes 1-24</li></ul> | March 2010     |

| -028     | <ul><li>Removed Documentation Changes 1-24</li><li>Added Documentation Changes 1-29</li></ul> | June 2010      |

| -029     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | September 2010 |

| -030     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | January 2011   |

| -031     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-29</li></ul> | April 2011     |

| -032     | <ul><li>Removed Documentation Changes 1-29</li><li>Added Documentation Changes 1-14</li></ul> | May 2011       |

| -033     | <ul><li>Removed Documentation Changes 1-14</li><li>Added Documentation Changes 1-38</li></ul> | October 2011   |

| -034     | <ul><li>Removed Documentation Changes 1-38</li><li>Added Documentation Changes 1-16</li></ul> | December 2011  |

| -035     | <ul><li>Removed Documentation Changes 1-16</li><li>Added Documentation Changes 1-18</li></ul> | March 2012     |

| -036     | <ul><li>Removed Documentation Changes 1-18</li><li>Added Documentation Changes 1-17</li></ul> | May 2012       |

| -037     | <ul><li>Removed Documentation Changes 1-17</li><li>Added Documentation Changes 1-28</li></ul> | August 2012    |

| -038     | <ul><li>Removed Documentation Changes 1-28</li><li>Add Documentation Changes 1-22</li></ul>   | January 2013   |

| -039     | <ul><li>Removed Documentation Changes 1-22</li><li>Add Documentation Changes 1-17</li></ul>   | June 2013      |

| -040     | <ul><li>Removed Documentation Changes 1-17</li><li>Add Documentation Changes 1-24</li></ul>   | September 2013 |

| -041     | <ul><li>Removed Documentation Changes 1-24</li><li>Add Documentation Changes 1-20</li></ul>   | February 2014  |

| -042     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-8</li></ul>    | February 2014  |

| -043     | <ul><li>Removed Documentation Changes 1-8</li><li>Add Documentation Changes 1-43</li></ul>    | June 2014      |

| -044     | <ul><li>Removed Documentation Changes 1-43</li><li>Add Documentation Changes 1-12</li></ul>   | September 2014 |

| -045     | <ul><li>Removed Documentation Changes 1-12</li><li>Add Documentation Changes 1-22</li></ul>   | January 2015   |

| -046     | <ul><li>Removed Documentation Changes 1-22</li><li>Add Documentation Changes 1-25</li></ul>   | April 2015     |

| -047     | <ul><li>Removed Documentation Changes 1-25</li><li>Add Documentation Changes 1-19</li></ul>   | June 2015      |

| Revision | Description                                                                                    | Date           |

|----------|------------------------------------------------------------------------------------------------|----------------|

| -048     | <ul> <li>Removed Documentation Changes 1-19</li> <li>Add Documentation Changes 1-33</li> </ul> | September 2015 |

| -049     | <ul><li>Removed Documentation Changes 1-33</li><li>Add Documentation Changes 1-33</li></ul>    | December 2015  |

| -050     | <ul><li>Removed Documentation Changes 1-33</li><li>Add Documentation Changes 1-9</li></ul>     | April 2016     |

| -051     | <ul><li>Removed Documentation Changes 1-9</li><li>Add Documentation Changes 1-20</li></ul>     | June 2016      |

| -052     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-22</li></ul>    | September 2016 |

| -053     | <ul><li>Removed Documentation Changes 1-22</li><li>Add Documentation Changes 1-26</li></ul>    | December 2016  |

| -054     | <ul><li>Removed Documentation Changes 1-26</li><li>Add Documentation Changes 1-20</li></ul>    | March 2017     |

| -055     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-28</li></ul>    | July 2017      |

| -056     | <ul><li>Removed Documentation Changes 1-28</li><li>Add Documentation Changes 1-18</li></ul>    | October 2017   |

| -057     | <ul><li>Removed Documentation Changes 1-18</li><li>Add Documentation Changes 1-29</li></ul>    | December 2017  |

| -058     | <ul><li>Removed Documentation Changes 1-29</li><li>Add Documentation Changes 1-17</li></ul>    | March 2018     |

| -059     | <ul><li>Removed Documentation Changes 1-17</li><li>Add Documentation Changes 1-24</li></ul>    | May 2018       |

| -060     | <ul><li>Removed Documentation Changes 1-24</li><li>Add Documentation Changes 1-23</li></ul>    | November 2018  |

| -061     | <ul><li>Removed Documentation Changes 1-23</li><li>Add Documentation Changes 1-21</li></ul>    | January 2019   |

| -062     | <ul><li>Removed Documentation Changes 1-21</li><li>Add Documentation Changes 1-28</li></ul>    | May 2019       |

| -063     | <ul><li>Removed Documentation Changes 1-28</li><li>Add Documentation Changes 1-34</li></ul>    | October 2019   |

| -064     | <ul><li>Removed Documentation Changes 1-34</li><li>Add Documentation Changes 1-36</li></ul>    | May 2020       |

| -065     | <ul><li>Removed Documentation Changes 1-36</li><li>Add Documentation Changes 1-31</li></ul>    | November 2020  |

| -066     | <ul><li>Removed Documentation Changes 1-31</li><li>Add Documentation Changes 1-24</li></ul>    | April 2021     |

| -067     | <ul><li>Removed Documentation Changes 1-24</li><li>Add Documentation Changes 1-30</li></ul>    | June 2021      |

| -068     | <ul><li>Removed Documentation Changes 1-30</li><li>Add Documentation Changes 1-29</li></ul>    | December 2021  |

| -069     | <ul><li>Removed Documentation Changes 1-29</li><li>Add Documentation Changes 1-18</li></ul>    | April 2022     |

| -070     | <ul><li>Removed Documentation Changes 1-18</li><li>Add Documentation Changes 1-41</li></ul>    | December 2022  |

| -071     | <ul> <li>Removed Documentation Changes 1-41</li> <li>Add Documentation Changes 1-23</li> </ul> | March 2023     |

| Revision | Description                                                                                 | Date           |

|----------|---------------------------------------------------------------------------------------------|----------------|

| -072     | <ul><li>Removed Documentation Changes 1-23</li><li>Add Documentation Changes 1-19</li></ul> | June 2023      |

| -073     | <ul><li>Removed Documentation Changes 1-19</li><li>Add Documentation Changes 1-19</li></ul> | September 2023 |

| -074     | <ul><li>Removed Documentation Changes 1-19</li><li>Add Documentation Changes 1-20</li></ul> | December 2023  |

| -075     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-20</li></ul> | March 2024     |

| -076     | <ul><li>Removed Documentation Changes 1-20</li><li>Add Documentation Changes 1-8</li></ul>  | June 2024      |

§

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

# **Affected Documents**

| Document Title                                                                                                         | Document Number/<br>Location |

|------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture                | 253665                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-L   | 253666                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, M-U   | 253667                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2C: Instruction Set Reference, V     | 326018                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2D: Instruction Set Reference, W-Z   | 334569                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1 | 253668                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B: System Programming Guide, Part 2 | 253669                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3C: System Programming Guide, Part 3 | 326019                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3D: System Programming Guide, Part 4 | 332831                       |

| Intel <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 4: Model Specific Registers          | 335592                       |

# Nomenclature

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# Summary Tables of Changes

The following table indicates documentation changes which apply to the  $Intel^{(R)}$  64 and IA-32 architectures. This table uses the following notations:

# **Codes Used in Summary Tables**

A violet change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# **Documentation Changes**

| No. | DOCUMENTATION CHANGES            |

|-----|----------------------------------|

| 1   | Updates to Chapter 1, Volume 2A  |

| 2   | Updates to Chapter 3, Volume 2A  |

| 3   | Updates to Chapter 1, Volume 3A  |

| 4   | Updates to Chapter 15, Volume 3B |

| 5   | Updates to Chapter 30, Volume 3C |

| 6   | Updates to Chapter 33, Volume 3C |

| 7   | Updates to Chapter 1, Volume 4   |

| 8   | Updates to Chapter 2, Volume 4   |

# **Documentation Changes**

Changes to the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual volumes follow, and are listed by chapter. Only chapters with changes are included in this document.

#### 1. Updates to Chapter 1, Volume 2A

Change bars and violet text show changes to Chapter 1 of the *Intel*<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-L.

\_\_\_\_\_

Changes to this chapter:

• Removed redundant information that consisted of repeated text regarding notational conventions and related literature. This information remains in Chapter 1 of Volume 1.

The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 2A, 2B, 2C, & 2D: Instruction Set Reference (order numbers 253666, 253667, 326018, and 334569), is part of a set that describes the architecture and programming environment of all Intel 64 and IA-32 architecture processors. Other volumes in this set are:

- The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture (Order Number 253665).

- The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 3A, 3B, 3C, & 3D: System Programming Guide (order numbers 253668, 253669, 326019, and 332831).

- The Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 4: Model-Specific Registers (order number 335592).

The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 1, describes the basic architecture and programming environment of Intel 64 and IA-32 processors. The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 2A, 2B, 2C, & 2D, describes the instruction set of the processor and the opcode structure. These volumes apply to application programmers and to programmers who write operating systems or executives. The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 3A, 3B, 3C, & 3D, describes the operating-system support environment of Intel 64 and IA-32 processors. These volumes target operating-system and BIOS designers. In addition, the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3B, addresses the programming environment for classes of software that host operating systems. The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 4, describes the model-specific registers of Intel 64 and IA-32 processors.

# 1.1 OVERVIEW OF VOLUME 2A, 2B, 2C, AND 2D: INSTRUCTION SET REFERENCE

A description of Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volumes 2A, 2B, 2C, & 2D, content follows:

**Chapter 1 — About This Manual.** Gives an overview of all volumes of the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, with chapter-specific details for the current volume.

**Chapter 2** — **Instruction Format.** Describes the machine-level instruction format used for all IA-32 instructions and gives the allowable encodings of prefixes, the operand-identifier byte (ModR/M byte), the addressing-mode specifier byte (SIB byte), and the displacement and immediate bytes.

**Chapter 3** — **Instruction Set Reference, A-L.** Describes Intel 64 and IA-32 instructions in detail, including an algorithmic description of operations, the effect on flags, the effect of operand- and address-size attributes, and the exceptions that may be generated. The instructions are arranged in alphabetical order. General-purpose, x87 FPU, Intel MMX<sup>™</sup> technology, SSE/SSE2/SSE3/SSE4 extensions, and system instructions are included.

**Chapter 4** — **Instruction Set Reference, M-U.** Continues the description of Intel 64 and IA-32 instructions started in Chapter 3. It starts Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2B.

**Chapter 5** — **Instruction Set Reference, V.** Continues the description of Intel 64 and IA-32 instructions started in chapters 3 and 4. This chapter starts Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2C.

**Chapter 6** — **Instruction Set Reference, W-Z.** Continues the description of Intel 64 and IA-32 instructions started in chapters 3, 4, and 5. It provides the balance of the alphabetized list of instructions and starts Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2D.

**Chapter 7** — **Safer Mode Extensions Reference.** Describes the safer mode extensions (SMX). SMX is intended for a system executive to support launching a measured environment in a platform where the identity of the software controlling the platform hardware can be measured for the purpose of making trust decisions.

**Chapter 8— Instruction Set Reference Unique to Intel® Xeon Phi<sup>™</sup> Processors.** Describes the instruction set that is unique to Intel® Xeon Phi<sup>™</sup> processors based on the Knights Landing and Knights Mill microarchitectures. The set is not supported in any other Intel processors.

**Appendix A** — **Opcode Map.** Gives an opcode map for the IA-32 instruction set.

**Appendix B** — **Instruction Formats and Encodings.** Gives the binary encoding of each form of each IA-32 instruction.

**Appendix C** — Intel<sup>®</sup> C/C++ Compiler Intrinsics and Functional Equivalents. Lists the Intel<sup>®</sup> C/C++ compiler intrinsics and their assembly code equivalents for each of the IA-32 MMX and SSE/SSE2/SSE3 instructions.

#### 2. Updates to Chapter 3, Volume 2A

Change bars and violet text show changes to Chapter 3 of the *Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 2A:* Instruction Set Reference, A-L.

\_\_\_\_\_

Changes to this chapter:

- Updated CPUID Leaf 06H, EAX bit 18 to align with text used in Volume 3, Chapter 15. The previous wording was causing confusion for some readers.

- Added the field name and definition of CPUID Leaf 06H, EAX bit 22.

- Updated CPUID Leaf 07H, Subleaf 2, to add enumeration for MONITOR\_MITG\_NO.

- Typo corrections as necessary.

#### CPUID—CPU Identification

| Opcode | Instruction | Op/<br>En | 64-Bit<br>Mode | Compat/<br>Leg Mode | Description                                                                                                                                                                    |

|--------|-------------|-----------|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OF A2  | CPUID       | ZO        | Valid          | Valid               | Returns processor identification and feature<br>information to the EAX, EBX, ECX, and EDX<br>registers, as determined by input entered in<br>EAX (in some cases, ECX as well). |

#### Instruction Operand Encoding

| Op/En | Operand 1 | Operand 2 | Operand 3 | Operand 4 |

|-------|-----------|-----------|-----------|-----------|

| ZO    | N/A       | N/A       | N/A       | N/A       |

#### Description

The ID flag (bit 21) in the EFLAGS register indicates support for the CPUID instruction. If a software procedure can set and clear this flag, the processor executing the procedure supports the CPUID instruction. This instruction operates the same in non-64-bit modes and 64-bit mode.

CPUID returns processor identification and feature information in the EAX, EBX, ECX, and EDX registers.<sup>1</sup> The instruction's output is dependent on the contents of the EAX register upon execution (in some cases, ECX as well). For example, the following pseudocode loads EAX with 00H and causes CPUID to return a Maximum Return Value and the Vendor Identification String in the appropriate registers:

Mov Eax, ooh Cpuid

Table 3-17 shows information returned, depending on the initial value loaded into the EAX register.

Two types of information are returned: basic and extended function information. If a value entered for CPUID.EAX is higher than the maximum input value for basic or extended function for that processor then the data for the highest basic information leaf is returned. For example, using some Intel processors, the following is true:

CPUID.EAX = 05H (\* Returns MONITOR/MWAIT leaf. \*) CPUID.EAX = 0AH (\* Returns Architectural Performance Monitoring leaf. \*) CPUID.EAX = 0BH (\* Returns Extended Topology Enumeration leaf. \*)<sup>2</sup> CPUID.EAX = 1FH (\* Returns V2 Extended Topology Enumeration leaf. \*)<sup>2</sup> CPUID.EAX = 8000008H (\* Returns linear/physical address size data. \*) CPUID.EAX = 8000000AH (\* INVALID: Returns same information as CPUID.EAX = 0BH. \*)

If a value entered for CPUID.EAX is less than or equal to the maximum input value and the leaf is not supported on that processor then 0 is returned in all the registers.

When CPUID returns the highest basic leaf information as a result of an invalid input EAX value, any dependence on input ECX value in the basic leaf is honored.

CPUID can be executed at any privilege level to serialize instruction execution. Serializing instruction execution guarantees that any modifications to flags, registers, and memory for previous instructions are completed before the next instruction is fetched and executed.

#### See also:

"Serializing Instructions" in Chapter 9, "Multiple-Processor Management," in the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

"Caching Translation Information" in Chapter 4, "Paging," in the Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

<sup>1.</sup> On Intel 64 processors, CPUID clears the high 32 bits of the RAX/RBX/RCX/RDX registers in all modes.

<sup>2.</sup> CPUID leaf 1FH is a preferred superset to leaf 0BH. Intel recommends first checking for the existence of CPUID leaf 1FH before using leaf 0BH.

| Initial EAX<br>Value |           | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Basic Cl  | PUID Information                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0H                   | EAX       | Maximum Input Value for Basic CPUID Information.                                                                                                                                                                                                                                                                                                                                                                  |

|                      | EBX       | "Genu"                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | ECX       | "ntel"                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | EDX       | "inel"                                                                                                                                                                                                                                                                                                                                                                                                            |

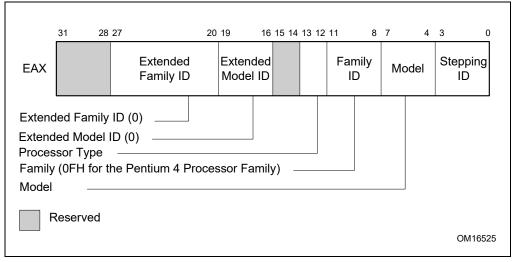

| 01H                  | EAX       | Version Information: Type, Family, Model, and Stepping ID (see Figure 3-6).                                                                                                                                                                                                                                                                                                                                       |

|                      | EBX       | Bits 07-00: Brand Index.<br>Bits 15-08: CLFLUSH line size (Value * 8 = cache line size in bytes; used also by CLFLUSHOPT).<br>Bits 23-16: Maximum number of addressable IDs for logical processors in this physical package*.<br>Bits 31-24: Initial APIC ID**.                                                                                                                                                   |

|                      | ECX       | Feature Information (see Figure 3-7 and Table 3-19).                                                                                                                                                                                                                                                                                                                                                              |

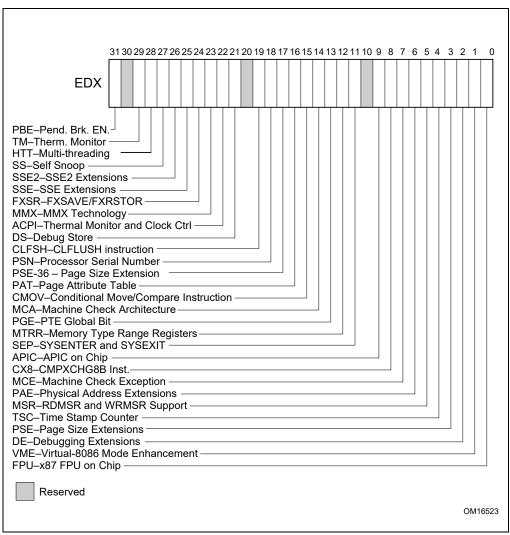

|                      | EDX       | Feature Information (see Figure 3-8 and Table 3-20).                                                                                                                                                                                                                                                                                                                                                              |

|                      |           | <ul> <li>NOTES:</li> <li>* The nearest power-of-2 integer that is not smaller than EBX[23:16] is the number of unique initial APIC IDs reserved for addressing different logical processors in a physical package. This field is only valid if CPUID.1.EDX.HTT[bit 28]= 1.</li> <li>** The 8-bit initial APIC ID in EBX[31:24] is replaced by the 32-bit x2APIC ID, available in Leaf OBH and Logf 15H</li> </ul> |

| 0211                 |           | Leaf 1FH.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 02H                  | EAX       | Cache and TLB Information (see Table 3-21).                                                                                                                                                                                                                                                                                                                                                                       |

|                      | EBX       | Cache and TLB Information.                                                                                                                                                                                                                                                                                                                                                                                        |

|                      | ECX       | Cache and TLB Information.                                                                                                                                                                                                                                                                                                                                                                                        |

| 0211                 | EDX       | Cache and TLB Information.                                                                                                                                                                                                                                                                                                                                                                                        |

| 03H                  | EAX       | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | EBX       | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | ECX       | Bits 00-31 of 96-bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)                                                                                                                                                                                                                                                                       |

|                      | EDX       | Bits 32-63 of 96-bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)                                                                                                                                                                                                                                                                       |

|                      |           | NOTES:<br>Processor serial number (PSN) is not supported in the Pentium 4 processor or later. On all models, use<br>the PSN flag (returned using CPUID) to check for PSN support before accessing the feature.                                                                                                                                                                                                    |

| CPUID le             | eaves abo | ve 2 and below 80000000H are visible only when IA32_MISC_ENABLE[bit 22] has its default value of 0.                                                                                                                                                                                                                                                                                                               |

|                      | Determ    | inistic Cache Parameters Leaf (Initial EAX Value = 04H)                                                                                                                                                                                                                                                                                                                                                           |

| 04H                  |           | NOTES:<br>Leaf 04H output depends on the initial value in ECX.*<br>See also: "INPUT EAX = 04H: Returns Deterministic Cache Parameters for Each Level" on page 251.                                                                                                                                                                                                                                                |

|                      | EAX       | Bits 04-00: Cache Type Field.<br>0 = Null - No more caches.<br>1 = Data Cache.<br>2 = Instruction Cache.<br>3 = Unified Cache.<br>4-31 = Reserved.                                                                                                                                                                                                                                                                |

| Initial EAX<br>Value |        | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |        | Bits 07-05: Cache Level (starts at 1).<br>Bit 08: Self Initializing cache level (does not need SW initialization).<br>Bit 09: Fully Associative cache.                                                                                                                                                                                                                                                                                                                                                                               |

|                      |        | Bits 13-10: Reserved.<br>Bits 25-14: Maximum number of addressable IDs for logical processors sharing this cache**, ***.<br>Bits 31-26: Maximum number of addressable IDs for processor cores in the physical<br>package**, ****, *****.                                                                                                                                                                                                                                                                                             |

|                      | EBX    | Bits 11-00: L = System Coherency Line Size**.<br>Bits 21-12: P = Physical Line partitions**.<br>Bits 31-22: W = Ways of associativity**.                                                                                                                                                                                                                                                                                                                                                                                             |

|                      | ECX    | Bits 31-00: S = Number of Sets**.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | EDX    | <ul> <li>Bit 00: Write-Back Invalidate/Invalidate.</li> <li>0 = WBINVD/INVD from threads sharing this cache acts upon lower level caches for threads sharing this cache.</li> <li>1 = WBINVD/INVD is not guaranteed to act upon lower level caches of non-originating threads sharing this cache.</li> </ul>                                                                                                                                                                                                                         |

|                      |        | <ul> <li>Bit 01: Cache Inclusiveness.</li> <li>0 = Cache is not inclusive of lower cache levels.</li> <li>1 = Cache is inclusive of lower cache levels.</li> <li>Bit 02: Complex Cache Indexing.</li> <li>0 = Direct mapped cache.</li> <li>1 = A complex function is used to index the cache, potentially using all address bits.</li> <li>Bits 31-03: Reserved = 0.</li> </ul>                                                                                                                                                     |

|                      |        | NOTES:<br>* If ECX contains an invalid sub leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf index n+1 is invalid if sub-<br>leaf n returns EAX[4:0] as 0.<br>** Add one to the return value to get the result.                                                                                                                                                                                                                                                                                                                         |

|                      |        | ***The nearest power-of-2 integer that is not smaller than (1 + EAX[25:14]) is the number of unique ini-<br>tial APIC IDs reserved for addressing different logical processors sharing this cache.                                                                                                                                                                                                                                                                                                                                   |

|                      |        | **** The nearest power-of-2 integer that is not smaller than (1 + EAX[31:26]) is the number of unique<br>Core_IDs reserved for addressing different processor cores in a physical package. Core ID is a subset of<br>bits of the initial APIC ID.                                                                                                                                                                                                                                                                                    |

|                      |        | ***** The returned value is constant for valid initial values in ECX. Valid ECX values start from 0.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                      | MONITO | R/MWAIT Leaf (Initial EAX Value = 05H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 05H                  | EAX    | Bits 15-00: Smallest monitor-line size in bytes (default is processor's monitor granularity).<br>Bits 31-16: Reserved = 0.                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      | EBX    | Bits 15-00: Largest monitor-line size in bytes (default is processor's monitor granularity).<br>Bits 31-16: Reserved = 0.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | ECX    | Bit 00: Enumeration of Monitor-Mwait extensions (beyond EAX and EBX registers) supported.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      |        | Bit 01: Supports treating interrupts as break-event for MWAIT, even when interrupts disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                      |        | Bits 31-02: Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | EDX    | Bits 03-00: Number of C0* sub C-states supported using MWAIT.<br>Bits 07-04: Number of C1* sub C-states supported using MWAIT.<br>Bits 11-08: Number of C2* sub C-states supported using MWAIT.<br>Bits 15-12: Number of C3* sub C-states supported using MWAIT.<br>Bits 19-16: Number of C4* sub C-states supported using MWAIT.<br>Bits 23-20: Number of C5* sub C-states supported using MWAIT.<br>Bits 27-24: Number of C6* sub C-states supported using MWAIT.<br>Bits 31-28: Number of C7* sub C-states supported using MWAIT. |

| Initial EAX<br>Value |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      |         | <ul> <li>NOTE:</li> <li>* The definition of C0 through C7 states for MWAIT extension are processor-specific C-states, not ACPI C-states.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                      | Thermal | and Power Management Leaf (Initial EAX Value = 06H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

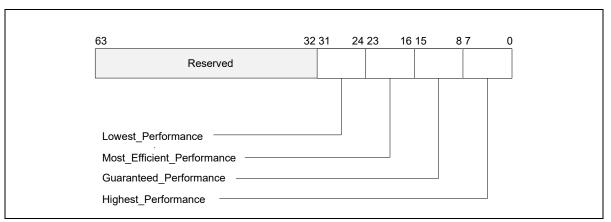

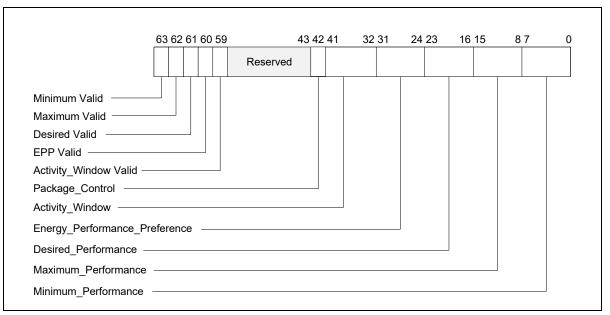

| 06H                  | EAX     | Bit 00: Digital temperature sensor is supported if set.<br>Bit 01: Intel Turbo Boost Technology available (see description of IA32_MISC_ENABLE[38]).<br>Bit 02: ARAT. APIC-Timer-always-running feature is supported if set.<br>Bit 03: Reserved.<br>Bit 04: PLN. Power limit notification controls are supported if set.<br>Bit 05: ECMD. Clock modulation duty cycle extension is supported if set.<br>Bit 06: PTM. Package thermal management is supported if set.<br>Bit 07: HWP. HWP base registers (IA32_PM_ENABLE[bit 0], IA32_HWP_CAPABILITIES, IA32_HWP_RE-<br>QUEST, IA32_HWP_STATUS) are supported if set.<br>Bit 08: HWP_Notification. IA32_HWP_INTERRUPT MSR is supported if set.<br>Bit 09: HWP_Activity_Window. IA32_HWP_REQUEST[bits 41:32] is supported if set.<br>Bit 10: HWP_Energy_Performance_Preference. IA32_HWP_REQUEST[bits 31:24] is supported if set.<br>Bit 11: HWP_Package_Level_Request. IA32_HWP_REQUEST_PKG MSR is supported if set.<br>Bit 12: Reserved.<br>Bit 13: HDC. HDC base registers IA32_PKG_HDC_CTL, IA32_PM_CTL1, IA32_THREAD_STALL MSRs are<br>supported if set.<br>Bit 15: HWP Capabilities. Highest Performance change is supported if set.<br>Bit 15: HWP PECI override is supported if set.<br>Bit 17: Flexible HWP is supported if set.<br>Bit 17: Flexible HWP is supported if set.<br>Bit 19: HW_FEEDBACK. IA32_HW_FEEDBACK_PTR MSR, IA32_HW_FEEDBACK_CONFIG MSR,<br>IA32_PACKAGE_THERM_STATUS MSR bit 26, and IA32_PACKAGE_THERM_INTERRUPT MSR bit 25 are<br>supported if set.<br>Bit 20: Ignoring Idle Logical Processor HWP request is supported if set.<br>Bit 21: Reserved.<br>Bit 22: HUP Control MSR Support. The IA32_HW_FCEDBACK_CHAR and<br>IA32_HW_FEEDBACK_THREAD_CONFIG MSRs are supported if set.<br>Bit 23: Intel® Thread Director supported if set. The IA32_HW_FEEDBACK_CHAR and<br>IA32_HW_FEEDBACK_THREAD_CONFIG MSRs are supported if set.<br>Bit 23: Intel® Thread Director Supported if set. The IA32_HW_FEEDBACK_CHAR and<br>IA32_HW_FEEDBACK_THREAD_CONFIG MSRs are supported if set.<br>Bit 23: Intel® Thread Director Supported if set. The IA32_HW_FEEDBACK_CHAR and<br>IA32_HW_FEEDBACK_THREAD_CONFIG MSRs are supported if set.<br>Bit 23: Intel® |  |

|                      | EBX     | Bits 03-00: Number of Interrupt Thresholds in Digital Thermal Sensor.<br>Bits 31-04: Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

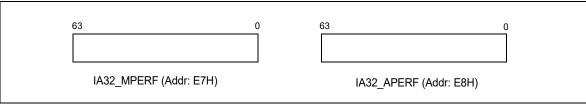

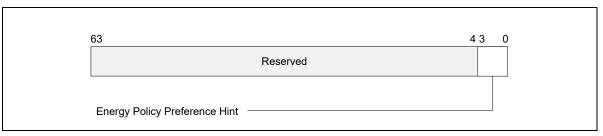

|                      | ECX     | Bit 00: Hardware Coordination Feedback Capability (Presence of IA32_MPERF and IA32_APERF). The capability to provide a measure of delivered processor performance (since last reset of the counters), as a percentage of the expected processor performance when running at the TSC frequency.<br>Bits 02-01: Reserved = 0.<br>Bit 03: The processor supports performance-energy bias preference if CPUID.06H:ECX.SETBH[bit 3] is set and it also implies the presence of a new architectural MSR called IA32_ENERGY_PERF_BIAS (1B0H).<br>Bits 07-04: Reserved = 0.<br>Bits 15-08: Number of Intel® Thread Director classes supported by the processor. Information for that many classes is written into the Intel Thread Director Table by the hardware.<br>Bits 31-16: Reserved = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Initial EAX<br>Value |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | EDX        | <ul> <li>Bits 07-00: Bitmap of supported hardware feedback interface capabilities.</li> <li>0 = When set to 1, indicates support for performance capability reporting.</li> <li>1 = When set to 1, indicates support for energy efficiency capability reporting.</li> <li>2-7 = Reserved</li> <li>Bits 11-08: Enumerates the size of the hardware feedback interface structure in number of 4 KB pages; add one to the return value to get the result.</li> <li>Bits 31-16: Index (starting at 0) of this logical processor's row in the hardware feedback interface structure. Note that on some parts the index may be same for multiple logical processors. On some parts the indices may not be contiguous, i.e., there may be unused rows in the hardware feedback interface structure.</li> <li>NOTE:</li> <li>Bits 0 and 1 will always be set together.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                      | Structure  | ed Extended Feature Flags Enumeration Leaf (Initial EAX Value = 07H, ECX = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 07H                  | EAX<br>EBX | Bits 31-00: Reports the maximum input value for supported leaf 7 sub-leaves.         Bit 00: FSGSBASE. Supports RDFSBASE/RDGSBASE/WRFSBASE/WRGSBASE if 1.         Bit 01: IA32_TSC_ADJUST MSR is supported if 1.         Bit 02: SGX. Supports Intel® Software Guard Extensions (Intel® SGX Extensions) if 1.         Bit 03: BM11.         Bit 04: HLE.         Bit 05: AVX2. Supports Intel® Advanced Vector Extensions 2 (Intel® AVX2) if 1.         Bit 06: FDP_EXCPTN_ONLY. x87 FPU Data Pointer updated only on x87 exceptions if 1.         Bit 07: MKPC. Supports Supervisor-Mode Execution Prevention if 1.         Bit 08: BM12.         Bit 09: Supports Enhanced REP MOVSB/STOSB if 1.         Bit 10: INVPCID. If 1, supports INVPCID instruction for system software that manages process-context identifiers.         Bit 11: RTM.         Bit 12: RDT-M. Supports Intel® Resource Director Technology (Intel® RDT) Monitoring capability if 1.         Bit 15: RDT-A. Supports Intel® Memory Protection Extensions if 1.         Bit 15: RDT-A. Supports Intel® Resource Director Technology (Intel® RDT) Allocation capability if 1.         Bit 16: AVX512F.         Bit 19: ADX.         Bit 20: SMAP. Supports Supervisor-Mode Access Prevention (and the CLAC/STAC instructions) if 1.         Bit 22: Reserved.         Bit 22: Reserved.         Bit 22: Reserved.         Bit 22: Intel Processor Trace.         Bit 26: AVX512PF. (Intel® Xeon P |  |

| Initial EAX<br>Value |     | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | ECX | Bit 00: PREFETCHWT1. (Intel® Xeon Phi <sup>™</sup> only.)<br>Bit 01: AVX512_VBMI.<br>Bit 02: UMIP. Supports user-mode instruction prevention if 1.<br>Bit 03: PKU. Supports protection keys for user-mode pages if 1.<br>Bit 04: OSPKE. If 1, OS has set CR4.PKE to enable protection keys (and the RDPKRU/WRPKRU instruc-                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      |     | tions).<br>Bit 05: WAITPKG.<br>Bit 06: AVX512_VBMI2.<br>Bit 07: CET_SS. Supports CET shadow stack features if 1. Processors that set this bit define bits 1:0 of the<br>IA32_U_CET and IA32_S_CET MSRs. Enumerates support for the following MSRs: IA32_INTERRUPT_SP-<br>P_TABLE_ADDR, IA32_PL3_SSP, IA32_PL2_SSP, IA32_PL1_SSP, and IA32_PL0_SSP.<br>Bit 08: GFNI.<br>Bit 09: VAES.<br>Bit 10: VPCLMULQDQ.<br>Bit 11: AVX512_VNNI.                                                                                                                                                                                                                                                                                                                                                                   |