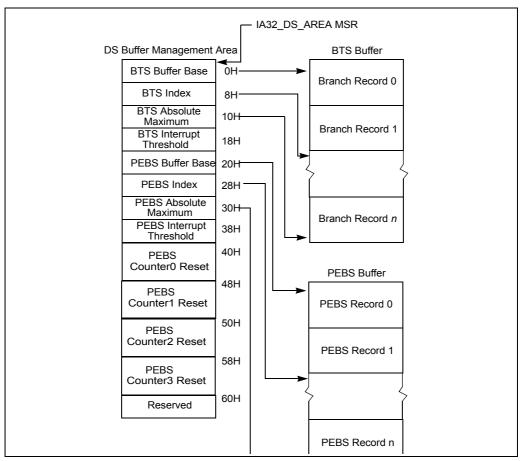

# Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual

Volume 3B: System Programming Guide, Part 2

**NOTE:** The Intel<sup>®</sup> 64 and IA-32 Architectures Software Developer's Manual consists of seven volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-L, Order Number 253666; Instruction Set Reference, Order Number 326018; System Programming Guide, Part 1, Order Number 253668; System Programming Guide, Part 2, Order Number 253669; System Programming Guide, Part 3, Order Number 326019. Refer to all seven volumes when evaluating your design needs.

Order Number: 253669-043US May 2012 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANT-ED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUB-CONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARIS-ING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUB-CONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel<sup>®</sup> AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the instructions in the correct sequence. AES-NI is available on select Intel<sup>®</sup> processors. For availability, consult your reseller or system manufacturer. For more information, see http://software.in-tel.com/en-us/articles/intel-advanced-encryption-standard-instructions-aes-ni/.

Intel<sup>®</sup> Hyper-Threading Technology (Intel<sup>®</sup> HT Technology) is available on select Intel<sup>®</sup> Core<sup>™</sup> processors. Requires an Intel<sup>®</sup> HT Technology-enabled system. Consult your PC manufacturer. Performance will vary depending on the specific hardware and software used. For more information including details on which processors support HT Technology, visit <u>http://www.intel.com/info/hyperthreading</u>.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit <u>http://www.intel.com/go/virtualization</u>.

Intel<sup>®</sup> 64 architecture Requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit <u>http://www.intel.com/info/em64t</u>.

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting operating system. Check with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

Intel, the Intel logo, Pentium, Xeon, Intel NetBurst, Intel Core, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo, Intel Core 2 Extreme, Intel Pentium D, Itanium, Intel SpeedStep, MMX, Intel Atom, and VTune are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <u>http://www.intel.com/design/literature.htm</u>

Copyright © 1997-2012 Intel Corporation. All rights reserved.

This chapter describes facilities of Intel 64 and IA-32 architecture used for power management and thermal monitoring.

# 14.1 ENHANCED INTEL SPEEDSTEP® TECHNOLOGY

Enhanced Intel SpeedStep<sup>®</sup> Technology was introduced in the Pentium M processor; it is available in Pentium 4, Intel Xeon, Intel<sup>®</sup> Core<sup>™</sup> Solo, Intel<sup>®</sup> Core<sup>™</sup> Duo, Intel<sup>®</sup> Atom<sup>™</sup> and Intel<sup>®</sup> Core<sup>™</sup> 2 Duo processors. The technology manages processor power consumption using performance state transitions. These states are defined as discrete operating points associated with different frequencies.

Enhanced Intel SpeedStep Technology differs from previous generations of Intel SpeedStep Technology in two ways:

- Centralization of the control mechanism and software interface in the processor by using model-specific registers.

- Reduced hardware overhead; this permits more frequent performance state transitions.

Previous generations of the Intel SpeedStep Technology require processors to be a deep sleep state, holding off bus master transfers for the duration of a performance state transition. Performance state transitions under the Enhanced Intel SpeedStep Technology are discrete transitions to a new target frequency.

Support is indicated by CPUID, using ECX feature bit 07. Enhanced Intel SpeedStep Technology is enabled by setting IA32\_MISC\_ENABLE MSR, bit 16. On reset, bit 16 of IA32\_MISC\_ENABLE MSR is cleared.

# 14.1.1 Software Interface For Initiating Performance State Transitions

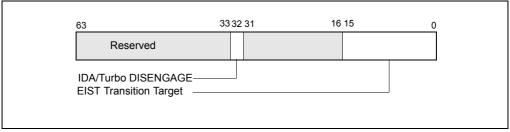

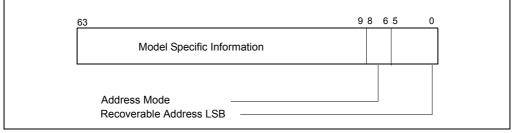

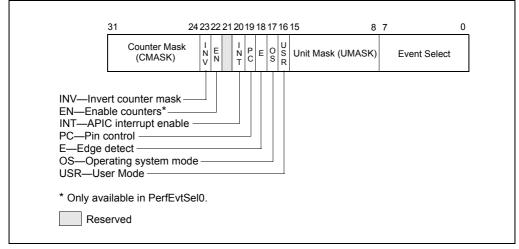

State transitions are initiated by writing a 16-bit value to the IA32\_PERF\_CTL register, see Figure 14-2. If a transition is already in progress, transition to a new value will subsequently take effect.

Reads of IA32\_PERF\_CTL determine the last targeted operating point. The current operating point can be read from IA32\_PERF\_STATUS. IA32\_PERF\_STATUS is updated dynamically.

The 16-bit encoding that defines valid operating points is model-specific. Applications and performance tools are not expected to use either IA32\_PERF\_CTL or IA32\_PERF\_STATUS and should treat both as reserved. Performance monitoring

tools can access model-specific events and report the occurrences of state transitions.

# 14.2 P-STATE HARDWARE COORDINATION

The Advanced Configuration and Power Interface (ACPI) defines performance states (P-state) that are used facilitate system software's ability to manage processor power consumption. Different P-state correspond to different performance levels that are applied while the processor is actively executing instructions. Enhanced Intel SpeedStep Technology supports P-state by providing software interfaces that control the operating frequency and voltage of a processor.

With multiple processor cores residing in the same physical package, hardware dependencies may exist for a subset of logical processors on a platform. These dependencies may impose requirements that impact coordination of P-state transitions. As a result, multi-core processors may require an OS to provide additional software support for coordinating P-state transitions for those subsets of logical processors.

A BIOS (following ACPI 3.0 specification) can choose to expose P-state as dependent and hardware-coordinated to OS power management (OSPM) policy. To support OSPMs, multi-core processors must have additional built-in support for P-state hardware coordination and feedback.

Intel 64 and IA-32 processors with dependent P-state amongst a subset of logical processors permit hardware coordination of P-state and provide a hardware-coordination feedback mechanism using IA32\_MPERF MSR and IA32\_APERF MSR. See Figure 14-1 for an overview of the two 64-bit MSRs and the bullets below for a detailed description:

| 63                     | 0 | 63 0                   |  |

|------------------------|---|------------------------|--|

|                        |   |                        |  |

| IA32_MPERF (Addr: E7H) |   | IA32_APERF (Addr: E8H) |  |

Figure 14-1. IA32\_MPERF MSR and IA32\_APERF MSR for P-state Coordination

- Use CPUID to check the P-State hardware coordination feedback capability bit. CPUID.06H.ECX[Bit 0] = 1 indicates IA32\_MPERF MSR and IA32\_APERF MSR are present.

- IA32\_MPERF MSR (0xE7) increments in proportion to a fixed frequency, which is configured when the processor is booted.

- IA32\_APERF MSR (0xE8) increments in proportion to actual performance, while accounting for hardware coordination of P-state and TM1/TM2; or software initiated throttling.

- The MSRs are per logical processor; they measure performance only when the targeted processor is in the C0 state.

- Only the IA32\_APERF/IA32\_MPERF ratio is architecturally defined; software should not attach meaning to the content of the individual of IA32\_APERF or IA32\_MPERF MSRs.

- When either MSR overflows, both MSRs are reset to zero and continue to increment.

- Both MSRs are full 64-bits counters. Each MSR can be written to independently. However, software should follow the guidelines illustrated in Example 14-1.

If P-states are exposed by the BIOS as hardware coordinated, software is expected to confirm processor support for P-state hardware coordination feedback and use the feedback mechanism to make P-state decisions. The OSPM is expected to either save away the current MSR values (for determination of the delta of the counter ratio at a later time) or reset both MSRs (execute WRMSR with 0 to these MSRs individually) at the start of the time window used for making the P-state decision. When not reset-ting the values, overflow of the MSRs can be detected by checking whether the new values read are less than the previously saved values.

Example 14-1 demonstrates steps for using the hardware feedback mechanism provided by IA32\_APERF MSR and IA32\_MPERF MSR to determine a target P-state.

#### Example 14-1. Determine Target P-state From Hardware Coordinated Feedback

DWORD PercentBusy; // Percentage of processor time not idle.

- // Measure "PercentBusy" during previous sampling window.

- // Typically, "PercentBusy" is measure over a time scale suitable for

- // power management decisions

$\parallel$

// RDMSR of MCNT and ACNT should be performed without delay.

// Software needs to exercise care to avoid delays between

// the two RDMSRs (for example, interrupts).

MCNT = RDMSR(IA32\_MPERF);

ACNT = RDMSR(IA32\_APERF);

// PercentPerformance indicates the percentage of the processor

// that is in use. The calculation is based on the PercentBusy,

// that is the percentage of processor time not idle and the P-state

// hardware coordinated feedback using the ACNT/MCNT ratio.

// Note that both values need to be calculated over the same

// time window.

PercentPerformance = PercentBusy \* (ACNT/MCNT);

// This example does not cover the additional logic or algorithms

// necessary to coordinate multiple logical processors to a target P-state.

```

TargetPstate = FindPstate(PercentPerformance);

```

```

if (TargetPstate != currentPstate) {

SetPState(TargetPstate);

}

// WRMSR of MCNT and ACNT should be performed without delay.

// Software needs to exercise care to avoid delays between

// the two WRMSRs (for example, interrupts).

WRMSR(IA32_MPERF, 0);

WRMSR(IA32_APERF, 0);

```

# 14.3 SYSTEM SOFTWARE CONSIDERATIONS AND OPPORTUNISTIC PROCESSOR PERFORMANCE OPERATION

An Intel 64 processor may support a form of processor operation that takes advantage of design headroom to opportunistically increase performance. In Intel Core i7 processors, Intel Turbo Boost Technology can convert thermal headroom into higher performance across multi-threaded and single-threaded workloads. In Intel Core 2 processors, Intel Dynamic Acceleration can convert thermal headroom into higher performance if only one thread is active.

# 14.3.1 Intel Dynamic Acceleration

Intel Core 2 Duo processor T 7700 introduces Intel Dynamic Acceleration (IDA). IDA takes advantage of thermal design headroom and opportunistically allows a single core to operate at a higher performance level when the operating system requests increased performance.

# 14.3.2 System Software Interfaces for Opportunistic Processor Performance Operation

Opportunistic processor operation, applicable to Intel Dynamic Acceleration and Intel Turbo Boost Technology, has the following characteristics:

• A transition from a normal state of operation (e.g. IDA/Turbo mode disengaged) to a target state is not guaranteed, but may occur opportunistically after the

corresponding enable mechanism is activated, the headroom is available and certain criteria are met.

- The opportunistic processor performance operation is generally transparent to most application software.

- System software (BIOS and Operating system) must be aware of hardware support for opportunistic processor performance operation and may need to temporarily disengage opportunistic processor performance operation when it requires more predictable processor operation.

- When opportunistic processor performance operation is engaged, the OS should use hardware coordination feedback mechanisms to prevent un-intended policy effects if it is activated during inappropriate situations.

#### 14.3.2.1 Discover Hardware Support and Enabling of Opportunistic Processor Operation

If an Intel 64 processor has hardware support for opportunistic processor performance operation, the power-on default state of IA32\_MISC\_ENABLE[38] indicates the presence of such hardware support. For Intel 64 processors that support opportunistic processor performance operation, the default value is 1, indicating its presence. For processors that do not support opportunistic processor performance operation, the default value is 0. The power-on default value of IA32\_MISC\_ENABLE[38] allows BIOS to detect the presence of hardware support of opportunistic processor performance operation.

IA32\_MISC\_ENABLE[38] is shared across all logical processors in a physical package. It is written by BIOS during platform initiation to enable/disable opportunistic processor operation in conjunction of OS power management capabilities, see Section 14.3.2.2. BIOS can set IA32\_MISC\_ENABLE[38] with 1 to disable opportunistic processor performance operation; it must clear the default value of IA32\_MISC\_ENABLE[38] to 0 to enable opportunistic processor performance operation. OS and applications must use CPUID leaf 06H if it needs to detect processors that has opportunistic processor operation enabled.

When CPUID is executed with EAX = 06H on input, Bit 1 of EAX in Leaf 06H (i.e. CPUID.06H:EAX[1]) indicates opportunistic processor performance operation, such as IDA, has been enabled by BIOS.

Opportunistic processor performance operation can be disabled by setting bit 38 of IA32\_MISC\_ENABLE. This mechanism is intended for BIOS only. If IA32\_MISC\_ENABLE[38] is set, CPUID.06H:EAX[1] will return 0.

#### 14.3.2.2 OS Control of Opportunistic Processor Performance Operation

There may be phases of software execution in which system software cannot tolerate the non-deterministic aspects of opportunistic processor performance operation. For example, when calibrating a real-time workload to make a CPU reservation request to the OS, it may be undesirable to allow the possibility of the processor delivering increased performance that cannot be sustained after the calibration phase.

System software can temporarily disengage opportunistic processor performance operation by setting bit 32 of the IA32\_PERF\_CTL MSR (0199H), using a read-modify-write sequence on the MSR. The opportunistic processor performance operation can be re-engaged by clearing bit 32 in IA32\_PERF\_CTL MSR, using a read-modify-write sequence. The DISENAGE bit in IA32\_PERF\_CTL is not reflected in bit 32 of the IA32\_PERF\_STATUS MSR (0198H), and it is not shared between logical processors in a physical package. In order for OS to engage IDA/Turbo mode, the BIOS must

• enable opportunistic processor performance operation, as described in Section 14.3.2.1,

• expose the operating points associated with IDA/Turbo mode to the OS.

#### 14.3.2.3 Required Changes to OS Power Management P-state Policy

Intel Dynamic Acceleration (IDA) and Intel Turbo Boost Technology can provide opportunistic performance greater than the performance level corresponding to the maximum qualified frequency of the processor (see CPUID's brand string information). System software can use a pair of MSRs to observe performance feedback. Software must query for the presence of IA32\_APERF and IA32\_MPERF (see Section 14.2). The ratio between IA32\_APERF and IA32\_MPERF is architecturally defined and a value greater than unity indicates performance increase occurred during the observation period due to IDA. Without incorporating such performance feedback, the target P-state evaluation algorithm can result in a non-optimal P-state target.

There are other scenarios under which OS power management may want to disable IDA, some of these are listed below:

- When engaging ACPI defined passive thermal management, it may be more effective to disable IDA for the duration of passive thermal management.

- When the user has indicated a policy preference of power savings over performance, OS power management may want to disable IDA while that policy is in effect.

# 14.3.2.4 Application Awareness of Opportunistic Processor Operation (Optional)

There may be situations that an end user or application software wishes to be aware of turbo mode activity. It is possible for an application-level utility to periodically check the occurrences of opportunistic processor operation. The basic elements of an algorithm is described below, using the characteristics of Intel Turbo Boost Technology as example.

Using an OS-provided timer service, application software can periodically calculate the ratio between unhalted-core-clockticks (UCC) relative to the unhalted-referenceclockticks (URC) on each logical processor to determine if that logical processor had been requested by OS to run at some frequency higher than the invariant TSC frequency, or the OS has determined system-level demand has reduced sufficiently to put that logical processor into a lower-performance p-state or even lower-activity state.

If an application software have access to information of the base operating ratio between the invariant TSC frequency and the base clock (133.33 MHz), it can convert the sampled ratio into a dynamic frequency estimate for each prior sampling period. The base operating ratio can be read from MSR\_PLATFORM\_INFO[15:8].

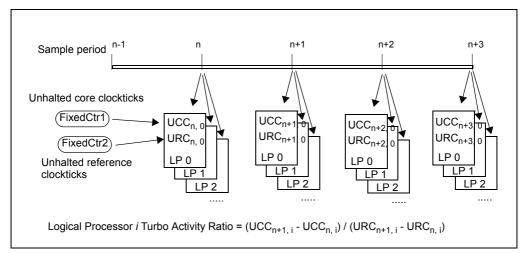

The periodic sampling technique is depicted in Figure 14-3 and described below:

Figure 14-3. Periodic Query of Activity Ratio of Opportunistic Processor Operation

• The sampling period chosen by the application (to program an OS timer service) should be sufficiently large to avoid excessive polling overhead to other applications or tasks managed by the OS.

- When the OS timer service transfers control, the application can use RDPMC (with ECX = 4000\_0001H) to read IA32\_PERF\_FIXED\_CTR1 (MSR address 30AH) to record the unhalted core clocktick (UCC) value; followed by RDPMC (ECX=4000\_0002H) to read IA32\_PERF\_FIXED\_CTR2 (MSR address 30BH) to record the unhalted reference clocktick (URC) value. This pair of values is needed for each logical processor for each sampling period.

- The application can calculate the Turbo activity ratio based on the difference of UCC between each sample period, over the difference of URC difference. The effective frequency of each sample period of the logical processor, *i*, can be estimated by:

$(UCC_{n+1, i} - UCC_{n, i})/(URC_{n+1, i} - URC_{n, i})* Base_operating_ratio* 133.33MHz$

It is possible that the OS had requested a lower-performance P-state during a sampling period. Thus the ratio  $(UCC_{n+1, i} - UCC_{n, i})/(URC_{n+1, i} - URC_{n, i})$  can reflect the average of Turbo activity (driving the ratio above unity) and some lower P-state transitions (causing the ratio to be < 1).

It is also possible that the OS might requested C-state transitions when the demand is low. The above ratio generally does not account for cycles any logical processor was idle. On Intel Core i7 processors, an application can make use of the time stamp counter (IA-32\_TSC) running at a constant frequency (i.e. Base\_operating\_ratio\* 133.33MHz) during C-states. Thus software can calculate ratios that can indicate fractions of sample period spent in the C0 state, using the unhalted reference clockticks and the invariant TSC. Note the estimate of fraction spent in C0 may be affected by SMM handler if the system software makes use of the "FREEZE\_WHILE\_SMM\_EN" capability to freeze performance counter values while the SMM handler is servicing an SMI (see Chapter 23, "Introduction to Virtual-Machine Extensions").

# 14.3.3 Intel Turbo Boost Technology

Intel Turbo Boost Technology is supported in Intel Core i7 processors and Intel Xeon processors based on Intel<sup>®</sup> microarchitecture code name Nehalem. It uses the same principle of leveraging thermal headroom to dynamically increase processor performance for single-threaded and multi-threaded/multi-tasking environment. The programming interface described in Section 14.3.2 also applies to Intel Turbo Boost Technology.

# 14.3.4 Performance and Energy Bias Hint support

Intel 64 processors may support additional software hint to guide the hardware heuristic of power management features to favor increasing dynamic performance or conserve energy consumption.

Software can detect processor's capability to support performance-energy bias preference hint by examining bit 3 of ECX in CPUID leaf 6. The processor supports this

capability if CPUID.06H:ECX.SETBH[bit 3] is set and it also implies the presence of a new architectural MSR called IA32\_ENERGY\_PERF\_BIAS (1B0H).

Software can program the lowest four bits of IA32\_ENERGY\_PERF\_BIAS MSR with a value from 0 - 15. The values represent a sliding scale, where a value of 0 (the default reset value) corresponds to a hint preference for highest performance and a value of 15 corresponds to the maximum energy savings. A value of 7 roughly translates into a hint to balance performance with energy consumption

| 63                              | 4 | 3 |

|---------------------------------|---|---|

| Reserved                        |   |   |

| Energy Policy Preference Hint – |   |   |

Figure 14-4. IA32\_ENERGY\_PERF\_BIAS Register

The layout of IA32\_ENERGY\_PERF\_BIAS is shown in Figure 14-4. The scope of IA32\_ENERGY\_PERF\_BIAS is per logical processor, which means that each of the logical processors in the package can be programmed with a different value. This may be especially important in virtualization scenarios, where the performance / energy requirements of one logical processor may differ from the other. Conflicting "hints" from various logical processors at higher hierarchy level will be resolved in favor of performance over energy savings.

Software can use whatever criteria it sees fit to program the MSR with the appropriate value. However, the value only serves as a hint to the hardware and the actual impact on performance and energy savings is model specific.

# 14.4 MWAIT EXTENSIONS FOR ADVANCED POWER MANAGEMENT

IA-32 processors may support a number of C-states<sup>1</sup> that reduce power consumption for inactive states. Intel Core Solo and Intel Core Duo processors support both deeper C-state and MWAIT extensions that can be used by OS to implement power management policy.

<sup>1.</sup> The processor-specific C-states defined in MWAIT extensions can map to ACPI defined C-state types (C0, C1, C2, C3). The mapping relationship depends on the definition of a C-state by processor implementation and is exposed to OSPM by the BIOS using the ACPI defined \_CST table.

Software should use CPUID to discover if a target processor supports the enumeration of MWAIT extensions. If CPUID.05H.ECX[Bit 0] = 1, the target processor supports MWAIT extensions and their enumeration (see Chapter 3, "Instruction Set Reference, A-L," of *Intel*® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A).

If CPUID.05H.ECX[Bit 1] = 1, the target processor supports using interrupts as break-events for MWAIT, even when interrupts are disabled. Use this feature to measure C-state residency as follows:

- Software can write to bit 0 in the MWAIT Extensions register (ECX) when issuing an MWAIT to enter into a processor-specific C-state or sub C-state.

- When a processor comes out of an inactive C-state or sub C-state, software can read a timestamp before an interrupt service routine (ISR) is potentially executed.

CPUID.05H.EDX allows software to enumerate processor-specific C-states and sub C-states available for use with MWAIT extensions. IA-32 processors may support more than one C-state of a given C-state type. These are called sub C-states. Numerically higher C-state have higher power savings and latency (upon entering and exiting) than lower-numbered C-state.

At CPL = 0, system software can specify desired C-state and sub C-state by using the MWAIT hints register (EAX). Processors will not go to C-state and sub C-state deeper than what is specified by the hint register. If CPL > 0 and if MONITOR/MWAIT is supported at CPL > 0, the processor will only enter C1-state (regardless of the C-state request in the hints register).

Executing MWAIT generates an exception on processors operating at a privilege level where MONITOR/MWAIT are not supported.

#### NOTE

If MWAIT is used to enter a C-state (including sub C-state) that is numerically higher than C1, a store to the address range armed by MONITOR instruction will cause the processor to exit MWAIT if the store was originated by other processor agents. A store from nonprocessor agent may not cause the processor to exit MWAIT.

# 14.5 THERMAL MONITORING AND PROTECTION

The IA-32 architecture provides the following mechanisms for monitoring temperature and controlling thermal power:

- 1. The **catastrophic shutdown detector** forces processor execution to stop if the processor's core temperature rises above a preset limit.

- 2. Automatic and adaptive thermal monitoring mechanisms force the processor to reduce it's power consumption in order to operate within predetermined temperature limits.

- 3. The **software controlled clock modulation mechanism** permits operating systems to implement power management policies that reduce power consumption; this is in addition to the reduction offered by automatic thermal monitoring mechanisms.

- 4. **On-die digital thermal sensor and interrupt mechanisms** permit the OS to manage thermal conditions natively without relying on BIOS or other system board components.

The first mechanism is not visible to software. The other three mechanisms are visible to software using processor feature information returned by executing CPUID with EAX = 1.

The second mechanism includes:

- **Automatic thermal monitoring** provides two modes of operation. One mode modulates the clock duty cycle; the second mode changes the processor's frequency. Both modes are used to control the core temperature of the processor.

- Adaptive thermal monitoring can provide flexible thermal management on processors made of multiple cores.

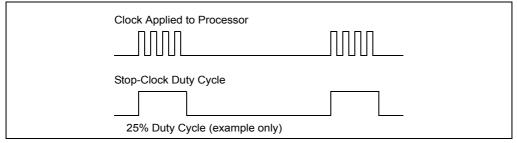

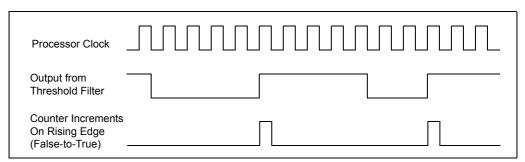

The third mechanism modulates the clock duty cycle of the processor. As shown in Figure 14-5, the phrase 'duty cycle' does not refer to the actual duty cycle of the clock signal. Instead it refers to the time period during which the clock signal is allowed to drive the processor chip. By using the stop clock mechanism to control how often the processor is clocked, processor power consumption can be modulated.

Figure 14-5. Processor Modulation Through Stop-Clock Mechanism

For previous automatic thermal monitoring mechanisms, software controlled mechanisms that changed processor operating parameters to impact changes in thermal conditions. Software did not have native access to the native thermal condition of the processor; nor could software alter the trigger condition that initiated software program control.

The fourth mechanism (listed above) provides access to an on-die digital thermal sensor using a model-specific register and uses an interrupt mechanism to alert software to initiate digital thermal monitoring.

# 14.5.1 Catastrophic Shutdown Detector

P6 family processors introduced a thermal sensor that acts as a catastrophic shutdown detector. This catastrophic shutdown detector was also implemented in Pentium 4, Intel Xeon and Pentium M processors. It is always enabled. When processor core temperature reaches a factory preset level, the sensor trips and processor execution is halted until after the next reset cycle.

# 14.5.2 Thermal Monitor

Pentium 4, Intel Xeon and Pentium M processors introduced a second temperature sensor that is factory-calibrated to trip when the processor's core temperature crosses a level corresponding to the recommended thermal design envelop. The trip-temperature of the second sensor is calibrated below the temperature assigned to the catastrophic shutdown detector.

#### 14.5.2.1 Thermal Monitor 1

The Pentium 4 processor uses the second temperature sensor in conjunction with a mechanism called Thermal Monitor 1 (TM1) to control the core temperature of the processor. TM1 controls the processor's temperature by modulating the duty cycle of the processor clock. Modulation of duty cycles is processor model specific. Note that the processors STPCLK# pin is not used here; the stop-clock circuitry is controlled internally.

Support for TM1 is indicated by CPUID.1:EDX.TM[bit 29] = 1.

TM1 is enabled by setting the thermal-monitor enable flag (bit 3) in IA32\_MISC\_ENABLE [see Chapter 34, "Model-Specific Registers (MSRs),"]. Following a power-up or reset, the flag is cleared, disabling TM1. BIOS is required to enable only one automatic thermal monitoring modes. Operating systems and applications must not disable the operation of these mechanisms.

#### 14.5.2.2 Thermal Monitor 2

An additional automatic thermal protection mechanism, called Thermal Monitor 2 (TM2), was introduced in the Intel Pentium M processor and also incorporated in newer models of the Pentium 4 processor family. Intel Core Duo and Solo processors, and Intel Core 2 Duo processor family all support TM1 and TM2. TM2 controls the core temperature of the processor by reducing the operating frequency and voltage of the processor and offers a higher performance level for a given level of power reduction than TM1.

TM2 is triggered by the same temperature sensor as TM1. The mechanism to enable TM2 may be implemented differently across various IA-32 processor families with different CPUID signatures in the family encoding value, but will be uniform within an IA-32 processor family.

Support for TM2 is indicated by CPUID.1:ECX.TM2[bit 8] = 1.

#### 14.5.2.3 Two Methods for Enabling TM2

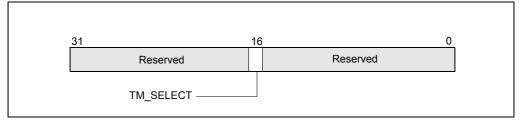

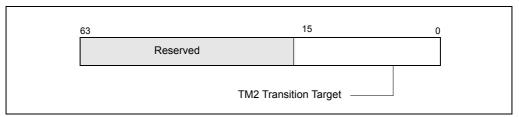

On processors with CPUID family/model/stepping signature encoded as 0x69n or 0x6Dn (early Pentium M processors), TM2 is enabled if the TM\_SELECT flag (bit 16) of the MSR\_THERM2\_CTL register is set to 1 (Figure 14-6) and bit 3 of the IA32\_MISC\_ENABLE register is set to 1.

Following a power-up or reset, the TM\_SELECT flag may be cleared. BIOS is required to enable either TM1 or TM2. Operating systems and applications must not disable mechanisms that enable TM1 or TM2. If bit 3 of the IA32\_MISC\_ENABLE register is set and TM\_SELECT flag of the MSR\_THERM2\_CTL register is cleared, TM1 is enabled.

#### Figure 14-6. MSR\_THERM2\_CTL Register On Processors with CPUID Family/Model/Stepping Signature Encoded as 0x69n or 0x6Dn

On processors introduced after the Pentium 4 processor (this includes most Pentium M processors), the method used to enable TM2 is different. TM2 is enable by setting bit 13 of IA32\_MISC\_ENABLE register to 1. This applies to Intel Core Duo, Core Solo, and Intel Core 2 processor family.

The target operating frequency and voltage for the TM2 transition after TM2 is triggered is specified by the value written to MSR\_THERM2\_CTL, bits 15:0 (Figure 14-7). Following a power-up or reset, BIOS is required to enable at least one of these two thermal monitoring mechanisms. If both TM1 and TM2 are supported, BIOS may choose to enable TM2 instead of TM1. Operating systems and applications must not disable the mechanisms that enable TM1or TM2; and they must not alter the value in bits 15:0 of the MSR\_THERM2\_CTL register.

Figure 14-7. MSR\_THERM2\_CTL Register for Supporting TM2

### 14.5.2.4 Performance State Transitions and Thermal Monitoring

If the thermal control circuitry (TCC) for thermal monitor (TM1/TM2) is active, writes to the IA32\_PERF\_CTL will effect a new target operating point as follows:

- If TM1 is enabled and the TCC is engaged, the performance state transition can commence before the TCC is disengaged.

- If TM2 is enabled and the TCC is engaged, the performance state transition specified by a write to the IA32\_PERF\_CTL will commence after the TCC has disengaged.

### 14.5.2.5 Thermal Status Information

The status of the temperature sensor that triggers the thermal monitor (TM1/TM2) is indicated through the thermal status flag and thermal status log flag in the IA32\_THERM\_STATUS MSR (see Figure 14-8).

The functions of these flags are:

- Thermal Status flag, bit 0 When set, indicates that the processor core temperature is currently at the trip temperature of the thermal monitor and that the processor power consumption is being reduced via either TM1 or TM2, depending on which is enabled. When clear, the flag indicates that the core temperature is below the thermal monitor trip temperature. This flag is read only.

- Thermal Status Log flag, bit 1 When set, indicates that the thermal sensor has tripped since the last power-up or reset or since the last time that software cleared this flag. This flag is a sticky bit; once set it remains set until cleared by software or until a power-up or reset of the processor. The default state is clear.

| 63 |                                       | 210 |

|----|---------------------------------------|-----|

|    | Reserved                              |     |

|    | Thermal Status Lo<br>Thermal Status — | og  |

#### Figure 14-8. IA32\_THERM\_STATUS MSR

After the second temperature sensor has been tripped, the thermal monitor (TM1/TM2) will remain engaged for a minimum time period (on the order of 1 ms). The thermal monitor will remain engaged until the processor core temperature drops below the preset trip temperature of the temperature sensor, taking hysteresis into account.

While the processor is in a stop-clock state, interrupts will be blocked from interrupting the processor. This holding off of interrupts increases the interrupt latency, but does not cause interrupts to be lost. Outstanding interrupts remain pending until clock modulation is complete.

The thermal monitor can be programmed to generate an interrupt to the processor when the thermal sensor is tripped. The delivery mode, mask and vector for this interrupt can be programmed through the thermal entry in the local APIC's LVT (see Section 10.5.1, "Local Vector Table"). The low-temperature interrupt enable and high-temperature interrupt enable flags in the IA32\_THERM\_INTERRUPT MSR (see Figure 14-9) control when the interrupt is generated; that is, on a transition from a temperature below the trip point to above and/or vice-versa.

| 63                                                                    | 2 1 | 10 |

|-----------------------------------------------------------------------|-----|----|

| Reserved                                                              |     |    |

| Low-Temperature Interrupt Enable<br>High-Temperature Interrupt Enable |     |    |

#### Figure 14-9. IA32\_THERM\_INTERRUPT MSR

- High-Temperature Interrupt Enable flag, bit 0 Enables an interrupt to be generated on the transition from a low-temperature to a high-temperature when set; disables the interrupt when clear.(R/W).

- Low-Temperature Interrupt Enable flag, bit 1 Enables an interrupt to be generated on the transition from a high-temperature to a low-temperature when set; disables the interrupt when clear.

The thermal monitor interrupt can be masked by the thermal LVT entry. After a power-up or reset, the low-temperature interrupt enable and high-temperature

interrupt enable flags in the IA32\_THERM\_INTERRUPT MSR are cleared (interrupts are disabled) and the thermal LVT entry is set to mask interrupts. This interrupt should be handled either by the operating system or system management mode (SMM) code.

Note that the operation of the thermal monitoring mechanism has no effect upon the clock rate of the processor's internal high-resolution timer (time stamp counter).

#### 14.5.2.6 Adaptive Thermal Monitor

The Intel Core 2 Duo processor family supports enhanced thermal management mechanism, referred to as Adaptive Thermal Monitor (Adaptive TM).

Unlike TM2, Adaptive TM is not limited to one TM2 transition target. During a thermal trip event, Adaptive TM (if enabled) selects an optimal target operating point based on whether or not the current operating point has effectively cooled the processor.

Similar to TM2, Adaptive TM is enable by BIOS. The BIOS is required to test the TM1 and TM2 feature flags and enable all available thermal control mechanisms (including Adaptive TM) at platform initiation.

Adaptive TM is available only to a subset of processors that support TM2.

In each chip-multiprocessing (CMP) silicon die, each core has a unique thermal sensor that triggers independently. These thermal sensor can trigger TM1 or TM2 transitions in the same manner as described in Section 14.5.2.1 and Section 14.5.2.2. The trip point of the thermal sensor is not programmable by software since it is set during the fabrication of the processor.

Each thermal sensor in a processor core may be triggered independently to engage thermal management features. In Adaptive TM, both cores will transition to a lower frequency and/or lower voltage level if one sensor is triggered.

Triggering of this sensor is visible to software via the thermal interrupt LVT entry in the local APIC of a given core.

# 14.5.3 Software Controlled Clock Modulation

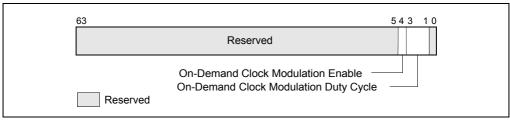

Pentium 4, Intel Xeon and Pentium M processors also support software-controlled clock modulation. This provides a means for operating systems to implement a power management policy to reduce the power consumption of the processor. Here, the stop-clock duty cycle is controlled by software through the IA32 CLOCK MODULATION MSR (see Figure 14-10).

The IA32\_CLOCK\_MODULATION MSR contains the following flag and field used to enable software-controlled clock modulation and to select the clock modulation duty cycle:

- On-Demand Clock Modulation Enable, bit 4 Enables on-demand software controlled clock modulation when set; disables software-controlled clock modulation when clear.

- **On-Demand Clock Modulation Duty Cycle, bits 1 through 3** Selects the on-demand clock modulation duty cycle (see Table 14-1). This field is only active when the on-demand clock modulation enable flag is set.

Note that the on-demand clock modulation mechanism (like the thermal monitor) controls the processor's stop-clock circuitry internally to modulate the clock signal. The STPCLK# pin is not used in this mechanism.

| Duty Cycle Field Encoding | Duty Cycle      |

|---------------------------|-----------------|

| 000B                      | Reserved        |

| 001B                      | 12.5% (Default) |

| 010B                      | 25.0%           |

| 011B                      | 37.5%           |

| 100B                      | 50.0%           |

| 101B                      | 63.5%           |

| 110B                      | 75%             |

| 111B                      | 87.5%           |

#### Table 14-1. On-Demand Clock Modulation Duty Cycle Field Encoding

The on-demand clock modulation mechanism can be used to control processor power consumption. Power management software can write to the IA32 CLOCK MODULATION MSR to enable clock modulation and to select a modula-

IA32\_CLOCK\_MODULATION MSR to enable clock modulation and to select a modulation duty cycle. If on-demand clock modulation and TM1 are both enabled and the thermal status of the processor is hot (bit 0 of the IA32\_THERM\_STATUS MSR is set), clock modulation at the duty cycle specified by TM1 takes precedence, regardless of the setting of the on-demand clock modulation duty cycle.

For Hyper-Threading Technology enabled processors, the

IA32\_CLOCK\_MODULATION register is duplicated for each logical processor. In order for the On-demand clock modulation feature to work properly, the feature must be enabled on all the logical processors within a physical processor. If the programmed duty cycle is not identical for all the logical processors, the processor clock will modulate to the highest duty cycle programmed.

For the P6 family processors, on-demand clock modulation was implemented through the chipset, which controlled clock modulation through the processor's STPCLK# pin.

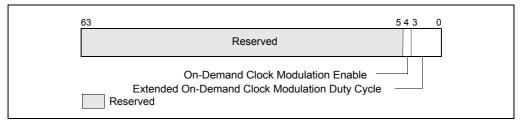

#### 14.5.3.1 Extension of Software Controlled Clock Modulation

Extension of the software controlled clock modulation facility supports on-demand clock modulation duty cycle with 4-bit dynamic range (increased from 3-bit range). Granularity of clock modulation duty cycle is increased to 6.25% (compared to 12.5%).

Four bit dynamic range control is provided by using bit 0 in conjunction with bits 3:1 of the IA32\_CLOCK\_MODULATION MSR (see Figure 14-11).

Figure 14-11. IA32\_CLOCK\_MODULATION MSR with Clock Modulation Extension

Extension to software controlled clock modulation is supported only if CPUID.06H:EAX[Bit 5] = 1. If CPUID.06H:EAX[Bit 5] = 0, then bit 0 of IA32\_CLOCK\_MODULATION is reserved.

#### 14.5.4 Detection of Thermal Monitor and Software Controlled Clock Modulation Facilities

The ACPI flag (bit 22) of the CPUID feature flags indicates the presence of the IA32\_THERM\_STATUS, IA32\_THERM\_INTERRUPT, IA32\_CLOCK\_MODULATION MSRs, and the xAPIC thermal LVT entry.

The TM1 flag (bit 29) of the CPUID feature flags indicates the presence of the automatic thermal monitoring facilities that modulate clock duty cycles.

#### 14.5.4.1 Detection of Software Controlled Clock Modulation Extension

Processor's support of software controlled clock modulation extension is indicated by CPUID.06H:EAX[Bit 5] = 1.

# 14.5.5 On Die Digital Thermal Sensors

On die digital thermal sensor can be read using an MSR (no I/O interface). In Intel Core Duo processors, each core has a unique digital sensor whose temperature is accessible using an MSR. The digital thermal sensor is the preferred method for reading the die temperature because (a) it is located closer to the hottest portions of the die, (b) it enables software to accurately track the die temperature and the potential activation of thermal throttling.

#### 14.5.5.1 Digital Thermal Sensor Enumeration

The processor supports a digital thermal sensor if CPUID.06H.EAX[0] = 1. If the processor supports digital thermal sensor, EBX[bits 3:0] determine the number of thermal thresholds that are available for use.

Software sets thermal thresholds by using the IA32\_THERM\_INTERRUPT MSR. Software reads output of the digital thermal sensor using the IA32\_THERM\_STATUS MSR.

#### 14.5.5.2 Reading the Digital Sensor

Unlike traditional analog thermal devices, the output of the digital thermal sensor is a temperature relative to the maximum supported operating temperature of the processor.

Temperature measurements returned by digital thermal sensors are always at or below TCC activation temperature. Critical temperature conditions are detected using the "Critical Temperature Status" bit. When this bit is set, the processor is operating at a critical temperature and immediate shutdown of the system should occur. Once the "Critical Temperature Status" bit is set, reliable operation is not guaranteed.

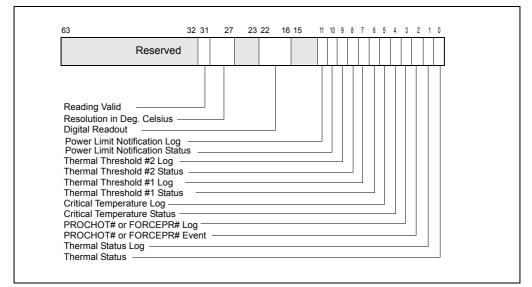

See Figure 14-12 for the layout of IA32\_THERM\_STATUS MSR. Bit fields include:

- Thermal Status (bit 0, RO) This bit indicates whether the digital thermal sensor high-temperature output signal (PROCHOT#) is currently active. Bit 0 = 1 indicates the feature is active. This bit may not be written by software; it reflects the state of the digital thermal sensor.

- Thermal Status Log (bit 1, R/WC0) This is a sticky bit that indicates the history of the thermal sensor high temperature output signal (PROCHOT#). Bit 1 = 1 if PROCHOT# has been asserted since a previous RESET or the last time software cleared the bit. Software may clear this bit by writing a zero.

• **PROCHOT# or FORCEPR# Event (bit 2, RO)** — Indicates whether PROCHOT# or FORCEPR# is being asserted by another agent on the platform.

#### Figure 14-12. IA32\_THERM\_STATUS Register

- PROCHOT# or FORCEPR# Log (bit 3, R/WC0) Sticky bit that indicates whether PROCHOT# or FORCEPR# has been asserted by another agent on the platform since the last clearing of this bit or a reset. If bit 3 = 1, PROCHOT# or FORCEPR# has been externally asserted. Software may clear this bit by writing a zero. External PROCHOT# assertions are only acknowledged if the Bidirectional Prochot feature is enabled.

- Critical Temperature Status (bit 4, RO) Indicates whether the critical temperature detector output signal is currently active. If bit 4 = 1, the critical temperature detector output signal is currently active.

- Critical Temperature Log (bit 5, R/WC0) Sticky bit that indicates whether the critical temperature detector output signal has been asserted since the last clearing of this bit or reset. If bit 5 = 1, the output signal has been asserted. Software may clear this bit by writing a zero.

- **Thermal Threshold #1 Status (bit 6, RO)** Indicates whether the actual temperature is currently higher than or equal to the value set in Thermal Threshold #1. If bit 6 = 0, the actual temperature is lower. If bit 6 = 1, the actual temperature is greater than or equal to TT#1. Quantitative information of actual temperature can be inferred from Digital Readout, bits 22:16.

- Thermal Threshold #1 Log (bit 7, R/WC0) Sticky bit that indicates whether the Thermal Threshold #1 has been reached since the last clearing of

this bit or a reset. If bit 7 = 1, the Threshold #1 has been reached. Software may clear this bit by writing a zero.

- Thermal Threshold #2 Status (bit 8, RO) Indicates whether actual temperature is currently higher than or equal to the value set in Thermal Threshold #2. If bit 8 = 0, the actual temperature is lower. If bit 8 = 1, the actual temperature is greater than or equal to TT#2. Quantitative information of actual temperature can be inferred from Digital Readout, bits 22:16.

- Thermal Threshold #2 Log (bit 9, R/WCO) Sticky bit that indicates whether the Thermal Threshold #2 has been reached since the last clearing of this bit or a reset. If bit 9 = 1, the Thermal Threshold #2 has been reached. Software may clear this bit by writing a zero.

- Power Limitation Status (bit 10, RO) Indicates whether the processor is currently operating below OS-requested P-state (specified in IA32\_PERF\_CTL) or OS-requested clock modulation duty cycle (specified in IA32\_CLOCK\_MODULATION). This field is supported only if CPUID.06H:EAX[bit 4] = 1. Package level power limit notification can be delivered independently to IA32\_PACKAGE\_THERM\_STATUS MSR.

- Power Notification Log (bit 11, R/WCO) Sticky bit that indicates the processor went below OS-requested P-state or OS-requested clock modulation duty cycle since the last clearing of this or RESET. This field is supported only if CPUID.06H:EAX[bit 4] = 1. Package level power limit notification is indicated independently in IA32\_PACKAGE\_THERM\_STATUS MSR.

- **Digital Readout (bits 22:16, RO)** Digital temperature reading in 1 degree Celsius relative to the TCC activation temperature.

0: TCC Activation temperature,

1: (TCC Activation - 1) , etc. See the processor's data sheet for details regarding TCC activation.

A lower reading in the Digital Readout field (bits 22:16) indicates a higher actual temperature.

- Resolution in Degrees Celsius (bits 30:27, RO) Specifies the resolution (or tolerance) of the digital thermal sensor. The value is in degrees Celsius. It is recommended that new threshold values be offset from the current temperature by at least the resolution + 1 in order to avoid hysteresis of interrupt generation.

- **Reading Valid (bit 31, RO)** Indicates if the digital readout in bits 22:16 is valid. The readout is valid if bit 31 = 1.

Changes to temperature can be detected using two thresholds (see Figure 14-13); one is set above and the other below the current temperature. These thresholds have the capability of generating interrupts using the core's local APIC which software must then service. Note that the local APIC entries used by these thresholds are also used by the Intel<sup>®</sup> Thermal Monitor; it is up to software to determine the source of a specific interrupt.

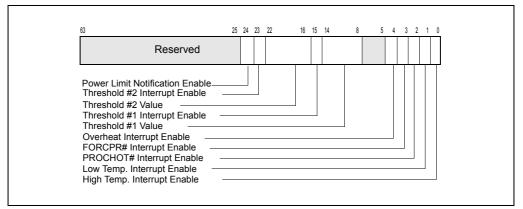

Figure 14-13. IA32\_THERM\_INTERRUPT Register

See Figure 14-13 for the layout of IA32\_THERM\_INTERRUPT MSR. Bit fields include:

- High-Temperature Interrupt Enable (bit 0, R/W) This bit allows the BIOS to enable the generation of an interrupt on the transition from low-temperature to a high-temperature threshold. Bit 0 = 0 (default) disables interrupts; bit 0 = 1 enables interrupts.

- Low-Temperature Interrupt Enable (bit 1, R/W) This bit allows the BIOS to enable the generation of an interrupt on the transition from high-temperature to a low-temperature (TCC de-activation). Bit 1 = 0 (default) disables interrupts; bit 1 = 1 enables interrupts.

- **PROCHOT# Interrupt Enable (bit 2, R/W)** This bit allows the BIOS or OS to enable the generation of an interrupt when PROCHOT# has been asserted by another agent on the platform and the Bidirectional Prochot feature is enabled. Bit 2 = 0 disables the interrupt; bit 2 = 1 enables the interrupt.

- FORCEPR# Interrupt Enable (bit 3, R/W) This bit allows the BIOS or OS to enable the generation of an interrupt when FORCEPR# has been asserted by another agent on the platform. Bit 3 = 0 disables the interrupt; bit 3 = 1 enables the interrupt.

- Critical Temperature Interrupt Enable (bit 4, R/W) Enables the generation of an interrupt when the Critical Temperature Detector has detected a critical thermal condition. The recommended response to this condition is a system shutdown. Bit 4 = 0 disables the interrupt; bit 4 = 1 enables the interrupt.

- Threshold #1 Value (bits 14:8, R/W) A temperature threshold, encoded relative to the TCC Activation temperature (using the same format as the Digital Readout). This threshold is compared against the Digital Readout and is used to

generate the Thermal Threshold #1 Status and Log bits as well as the Threshold #1 thermal interrupt delivery.

- Threshold #1 Interrupt Enable (bit 15, R/W) Enables the generation of an interrupt when the actual temperature crosses the Threshold #1 setting in any direction. Bit 15 = 0 enables the interrupt; bit 15 = 1 disables the interrupt.

- Threshold #2 Value (bits 22:16, R/W) —A temperature threshold, encoded relative to the TCC Activation temperature (using the same format as the Digital Readout). This threshold is compared against the Digital Readout and is used to generate the Thermal Threshold #2 Status and Log bits as well as the Threshold #2 thermal interrupt delivery.

- Threshold #2 Interrupt Enable (bit 23, R/W) Enables the generation of an interrupt when the actual temperature crosses the Threshold #2 setting in any direction. Bit 23 = 0 enables the interrupt; bit 23 = 1 disables the interrupt.

- Power Limit Notification Enable (bit 24, R/W) Enables the generation of power notification events when the processor went below OS-requested P-state or OS-requested clock modulation duty cycle. This field is supported only if CPUID.06H:EAX[bit 4] = 1. Package level power limit notification can be enabled independently by IA32\_PACKAGE\_THERM\_INTERRUPT MSR.

# 14.5.6 Power Limit Notification

Platform firmware may be capable of specifying a power limit to restrict power delivered to a platform component, such as a physical processor package. This constraint imposed by platform firmware may occasionally cause the processor to operate below OS-requested P or T-state. A power limit notification event can be delivered using the existing thermal LVT entry in the local APIC.

Software can enumerate the presence of the processor's support for power limit notification by verifying CPUID.06H:EAX[bit 4] = 1.

If CPUID.06H:EAX[bit 4] = 1, then IA32\_THERM\_INTERRUPT and IA32\_THERM\_STATUS provides the following facility to manage power limit notification:

- Bits 10 and 11 in IA32\_THERM\_STATUS informs software of the occurrence of processor operating below OS-requested P-state or clock modulation duty cycle setting (see Figure 14-12).

- Bit 24 in IA32\_THERM\_INTERRUPT enables the local APIC to deliver a thermal event when the processor went below OS-requested P-state or clock modulation duty cycle setting (see Figure 14-13).

# 14.6 PACKAGE LEVEL THERMAL MANAGEMENT

The thermal management facilities like IA32\_THERM\_INTERRUPT and IA32\_THERM\_STATUS are often implemented with a processor core granularity. To

facilitate software manage thermal events from a package level granularity, two architectural MSR is provided for package level thermal management. The IA32\_PACKAGE\_THERM\_STATUS and IA32\_PACKAGE\_THERM\_INTERRUPT MSRs use similar interfaces as IA32\_THERM\_STATUS and IA32\_THERM\_INTERRUPT, but are shared in each physical processor package.

Software can enumerate the presence of the processor's support for package level thermal management facility (IA32\_PACKAGE\_THERM\_STATUS and IA32\_PACKAGE\_THERM\_INTERRUPT) by verifying CPUID.06H:EAX[bit 6] = 1.

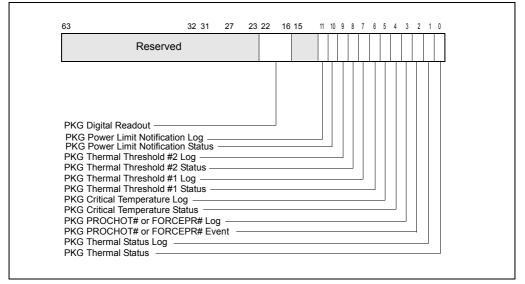

The layout of IA32\_PACKAGE\_THERM\_STATUS MSR is shown in Figure 14-14.

Figure 14-14. IA32\_PACKAGE\_THERM\_STATUS Register

- Package Thermal Status (bit 0, RO) This bit indicates whether the digital thermal sensor high-temperature output signal (PROCHOT#) for the package is currently active. Bit 0 = 1 indicates the feature is active. This bit may not be written by software; it reflects the state of the digital thermal sensor.

- Package Thermal Status Log (bit 1, R/WC0) This is a sticky bit that indicates the history of the thermal sensor high temperature output signal (PROCHOT#) of the package. Bit 1 = 1 if package PROCHOT# has been asserted since a previous RESET or the last time software cleared the bit. Software may clear this bit by writing a zero.

- **Package PROCHOT# Event (bit 2, RO)** Indicates whether package PROCHOT# is being asserted by another agent on the platform.

- Package PROCHOT# Log (bit 3, R/WC0) Sticky bit that indicates whether package PROCHOT# has been asserted by another agent on the platform since the last clearing of this bit or a reset. If bit 3 = 1, package PROCHOT# has been externally asserted. Software may clear this bit by writing a zero.

- **Package Critical Temperature Status (bit 4, RO)** Indicates whether the package critical temperature detector output signal is currently active. If bit 4 = 1, the package critical temperature detector output signal is currently active.

- Package Critical Temperature Log (bit 5, R/WC0) Sticky bit that indicates whether the package critical temperature detector output signal has been asserted since the last clearing of this bit or reset. If bit 5 = 1, the output signal has been asserted. Software may clear this bit by writing a zero.

- **Package Thermal Threshold #1 Status (bit 6, RO)** Indicates whether the actual package temperature is currently higher than or equal to the value set in Package Thermal Threshold #1. If bit 6 = 0, the actual temperature is lower. If bit 6 = 1, the actual temperature is greater than or equal to PTT#1. Quantitative information of actual package temperature can be inferred from Package Digital Readout, bits 22:16.

- Package Thermal Threshold #1 Log (bit 7, R/WC0) Sticky bit that indicates whether the Package Thermal Threshold #1 has been reached since the last clearing of this bit or a reset. If bit 7 = 1, the Package Threshold #1 has been reached. Software may clear this bit by writing a zero.

- **Package Thermal Threshold #2 Status (bit 8, RO)** Indicates whether actual package temperature is currently higher than or equal to the value set in Package Thermal Threshold #2. If bit 8 = 0, the actual temperature is lower. If bit 8 = 1, the actual temperature is greater than or equal to PTT#2. Quantitative information of actual temperature can be inferred from Package Digital Readout, bits 22:16.

- **Package Thermal Threshold #2 Log (bit 9, R/WC0)** Sticky bit that indicates whether the Package Thermal Threshold #2 has been reached since the last clearing of this bit or a reset. If bit 9 = 1, the Package Thermal Threshold #2 has been reached. Software may clear this bit by writing a zero.

- **Package Power Limitation Status (bit 10, RO)** Indicates package power limit is forcing one ore more processors to operate below OS-requested P-state. Note that package power limit violation may be caused by processor cores or by devices residing in the uncore. Software can examine IA32\_THERM\_STATUS to determine if the cause originates from a processor core (see Figure 14-12).

- Package Power Notification Log (bit 11, R/WCO) Sticky bit that indicates any processor in the package went below OS-requested P-state or OS-requested clock modulation duty cycle since the last clearing of this or RESET.

- **Package Digital Readout (bits 22:16, RO)** Package digital temperature reading in 1 degree Celsius relative to the package TCC activation temperature.

0: Package TCC Activation temperature,

1: (PTCC Activation - 1) , etc. See the processor's data sheet for details regarding PTCC activation.

A lower reading in the Package Digital Readout field (bits 22:16) indicates a higher actual temperature.

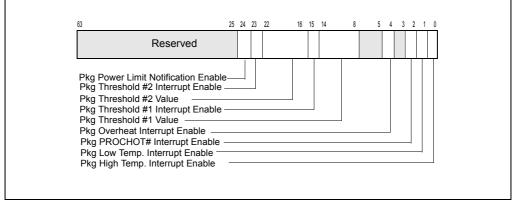

The layout of IA32\_PACKAGE\_THERM\_INTERRUPT MSR is shown in Figure 14-15.

Figure 14-15. IA32\_PACKAGE\_THERM\_INTERRUPT Register

- Package High-Temperature Interrupt Enable (bit 0, R/W) This bit allows the BIOS to enable the generation of an interrupt on the transition from low-temperature to a package high-temperature threshold. Bit 0 = 0 (default) disables interrupts; bit 0 = 1 enables interrupts.

- Package Low-Temperature Interrupt Enable (bit 1, R/W) This bit allows the BIOS to enable the generation of an interrupt on the transition from hightemperature to a low-temperature (TCC de-activation). Bit 1 = 0 (default) disables interrupts; bit 1 = 1 enables interrupts.

- **Package PROCHOT# Interrupt Enable (bit 2, R/W)** This bit allows the BIOS or OS to enable the generation of an interrupt when Package PROCHOT# has been asserted by another agent on the platform and the Bidirectional Prochot feature is enabled. Bit 2 = 0 disables the interrupt; bit 2 = 1 enables the interrupt.

- **Package Critical Temperature Interrupt Enable (bit 4, R/W)** Enables the generation of an interrupt when the Package Critical Temperature Detector has detected a critical thermal condition. The recommended response to this condition is a system shutdown. Bit 4 = 0 disables the interrupt; bit 4 = 1 enables the interrupt.

- **Package Threshold #1 Value (bits 14:8, R/W)** A temperature threshold, encoded relative to the Package TCC Activation temperature (using the same format as the Digital Readout). This threshold is compared against the Package

Digital Readout and is used to generate the Package Thermal Threshold #1 Status and Log bits as well as the Package Threshold #1 thermal interrupt delivery.

- Package Threshold #1 Interrupt Enable (bit 15, R/W) Enables the generation of an interrupt when the actual temperature crosses the Package Threshold #1 setting in any direction. Bit 15 = 0 enables the interrupt; bit 15 = 1 disables the interrupt.

- Package Threshold #2 Value (bits 22:16, R/W) —A temperature threshold, encoded relative to the PTCC Activation temperature (using the same format as the Package Digital Readout). This threshold is compared against the Package Digital Readout and is used to generate the Package Thermal Threshold #2 Status and Log bits as well as the Package Threshold #2 thermal interrupt delivery.

- Package Threshold #2 Interrupt Enable (bit 23, R/W) Enables the generation of an interrupt when the actual temperature crosses the Package Threshold #2 setting in any direction. Bit 23 = 0 enables the interrupt; bit 23 = 1 disables the interrupt.

- Package Power Limit Notification Enable (bit 24, R/W) Enables the generation of package power notification events.

# 14.6.1 Support for Passive and Active cooling

Passive and active cooling may be controlled by the OS power management agent through ACPI control methods. On platforms providing package level thermal management facility described in the previous section, it is recommended that active cooling (FAN control) should be driven by measuring the package temperature using the IA32\_PACKAGE\_THERM\_INTERRUPT MSR.

Passive cooling (frequency throttling) should be driven by measuring (a) the core and package temperatures, or (b) only the package temperature. If measured package temperature led the power management agent to choose which core to execute passive cooling, then all cores need to execute passive cooling. Core temperature is measured using the IA32\_THERMAL\_STATUS and

IA32\_THERMAL\_INTERRUPT MSRs. The exact implementation details depend on the platform firmware and possible solutions include defining two different thermal zones (one for core temperature and passive cooling and the other for package temperature and active cooling).

# 14.7 PLATFORM SPECIFIC POWER MANAGEMENT SUPPORT

This section covers power management interfaces that are not architectural but addresses the power management needs of several platform specific components.

Specifically, RAPL (Running Average Power Limit) interfaces provide mechanisms to enforce power consumption limit. Power limiting usages have specific usages in client and server platforms.

For client platform power limit control and for server platforms used in a data center, the following power and thermal related usages are desirable:

- Platform Thermal Management: Robust mechanisms to manage component, platform, and group-level thermals, either proactively or reactively (e.g., in response to a platform-level thermal trip point).

- Platform Power Limiting: More deterministic control over the system's power consumption, for example to meet battery life targets on rack- or container-level power consumption goals within a datacenter.

- Power/Performance Budgeting: Efficient means to control the power consumed (and therefore the sustained performance delivered) within and across platforms.

The server and client usage models are addressed by RAPL interfaces, which exposes multiple domains of power rationing within each processor socket. Generally, these RAPL domains may be viewed to include hierarchically:

- Package domain is the processor die.

- Memory domain include the directly-attached DRAM; additional power plane may constitutes a separate domain.

In order to manage the power consumed across multiple sockets via RAPL, individual limits must be programmed for each processor complex. Programming specific RAPL domain across multiple sockets is not supported.

# 14.7.1 RAPL Interfaces

RAPL interfaces consist of non-architectural MSRs. Each RAPL domain supports the following set of capabilities, some of which are optional as stated below.

- Power limit MSR interfaces to specify power limit, time window; lock bit, clamp bit etc.

- Energy Status Power metering interface providing energy consumption information.

- Perf Status (Optional) Interface providing information on the performance effects (regression) due to power limits. It is defined as a duration metric that measures the power limit effect in the respective domain. The meaning of duration is domain specific.

- Power Info (Optional) Interface providing information on the range of parameters for a given domain, minimum power, maximum power etc.

- Policy (Optional) 4-bit priority information which is a hint to hardware for dividing budget between sub-domains in a parent domain.

Each of the above capabilities requires specific units in order to describe them. Power is expressed in Watts, Time is expressed in Seconds and Energy is expressed in Joules. Scaling factors are supplied to each unit to make the information presented meaningful in a finite number of bits. Units for power, energy and time are exposed in the read-only MSR\_RAPL\_POWER\_UNIT MSR.

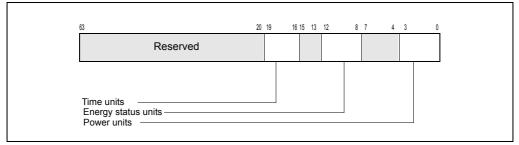

MSR\_RAPL\_POWER\_UNIT (Figure 14-16) provides the following information across all RAPL domains:

- **Power Units** (bits 3:0): Power related information (in Watts) is based on the multiplier, 1/ 2^PU; where PU is an unsigned integer represented by bits 3:0. Default value is 0011b, indicating power unit is in 1/8 Watts increment.

- Energy Status Units (bits 12:8): Energy related information (in Joules) is based on the multiplier, 1/2^ESU; where ESU is an unsigned integer represented by bits 12:8. Default value is 10000b, indicating energy status unit is in 15.3 micro-Joules increment.

- Time Units (bits 19:16): Time related information (in Seconds) is based on the multiplier, 1/ 2^TU; where TU is an unsigned integer represented by bits 19:16. Default value is 1010b, indicating time unit is in 976 micro-seconds increment.

# 14.7.2 RAPL Domains and Platform Specificity

The specific RAPL domains available in a platform varies across product segments. Platforms targeting client segment support the following RAPL domain hierarchy:

- Package

- Two power planes: PP0 and PP1 (PP1 may reflect to uncore devices)

Platforms targeting server segment support the following RAPL domain hierarchy:

- Package

- Power plane: PP0

- DRAM

Each level of the RAPL hierarchy provides respective set of RAPL interface MSRs. Table 14-2 lists the RAPL MSR interfaces available for each RAPL domain. The power limit MSR of each RAPL domain is located at offset 0 relative to an MSR base address which is non-architectural (see Chapter 34). The energy status MSR of each domain is located at offset 1 relative to the MSR base address of respective domain.

#### Table 14-2. RAPL MSR Interfaces and RAPL Domains

| Domain | Power Limit<br>(Offset 0) | Energy Status<br>(Offset 1) | Policy<br>(Offset 2) | Perf Status<br>(Offset 3)     | Power Info<br>(Offset 4) |

|--------|---------------------------|-----------------------------|----------------------|-------------------------------|--------------------------|

| PKG    | MSR_PKG_PO<br>WER_LIMIT   | MSR_PKG_ENER<br>GY_STATUS   | RESERVED             | MSR_PKG_RAPL_<br>PERF_STATUS  | MSR_PKG_PO<br>WER_INFO   |

| DRAM   | MSR_DRAM_<br>POWER_LIMIT  | MSR_DRAM_EN<br>ERGY_STATUS  | RESERVED             | MSR_DRAM_RAPL<br>_PERF_STATUS | MSR_DRAM_P<br>OWER_INFO  |

| PPO    | MSR_PP0_P0<br>WER_LIMIT   | MSR_PP0_ENER<br>GY_STATUS   | MSR_PP0_P<br>OLICY   | RESERVED                      | RESERVED                 |

| PP1    | MSR_PP1_P0<br>WER_LIMIT   | MSR_PP1_ENER<br>GY_STATUS   | MSR_PP1_P<br>OLICY   | RESERVED                      | RESERVED                 |

The presence of the optional MSR interfaces (the three right-most columns of Table 14-2) may be model-specific. See Chapter 34 for detail.

# 14.7.3 Package RAPL Domain

The MSR interfaces defined for the package RAPL domain are:

- MSR\_PKG\_POWER\_LIMIT allows software to set power limits for the package and measurement attributes associated with each limit,

- MSR\_PKG\_ENERGY\_STATUS reports measured actual energy usage,

- MSR\_PKG\_POWER\_INFO reports the package power range information for RAPL usage.

MSR\_PKG\_RAPL\_PERF\_STATUS can report the performance impact of power limiting, but its availability may be model-specific.

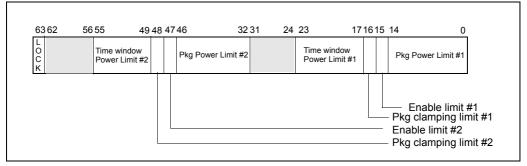

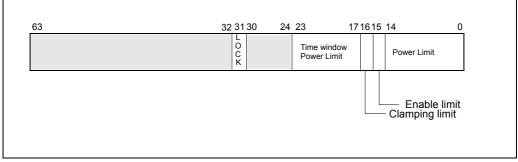

Figure 14-17. MSR\_PKG\_POWER\_LIMIT Register

MSR\_PKG\_POWER\_LIMIT allows a software agent to define power limitation for the package domain. Power limitation is defined in terms of average power usage (Watts) over a time window specified in MSR\_PKG\_POWER\_LIMIT. Two power limits can be specified, corresponding to time windows of different sizes. Each power limit provides independent clamping control that would permit the processor cores to go below OS-requested state to meet the power limits. A lock mechanism allow the software agent to enforce power limit settings. Once the lock bit is set, the power limit settings are static and un-modifiable until next RESET.

The bit fields of MSR\_PKG\_POWER\_LIMIT (Figure 14-17) are:

- **Package Power Limit #1**(bits 14:0): Sets the average power usage limit of the package domain corresponding to time window # 1. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- Enable Power Limit #1(bit 15): 0 = disabled; 1 = enabled.

- **Package Clamping Limitation #1** (bit 16): Allow going below OS-requested P/T state setting during time window specified by bits 23:17.

- **Time Window for Power Limit #1** (bits 23:17): Indicates the length of time window over which the power limit #1 The numeric value encoded by bits 23:17 is represented by the product of 2^Y \*F; where F is a single-digit decimal floating-point value between 1.0 and 1.3 with the fraction digit represented by bits 23:22, Y is an unsigned integer represented by bits 21:17. The unit of this field is specified by the "Time Units" field of MSR\_RAPL\_POWER\_UNIT.

- Package Power Limit #2(bits 46:32): Sets the average power usage limit of the package domain corresponding to time window # 2. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- **Enable Power Limit #2**(bit 47): 0 = disabled; 1 = enabled.

- **Package Clamping Limitation #2** (bit 48): Allow going below OS-requested P/T state setting during time window specified by bits 23:17.

- **Time Window for Power Limit #2** (bits 55:49): Indicates the length of time window over which the power limit #2 The numeric value encoded by bits 55:49 is represented by the product of 2^Y \*F; where F is a single-digit decimal floating-point value between 1.0 and 1.3 with the fraction digit represented by bits 55:54, Y is an unsigned integer represented by bits 53:49. The unit of this field is specified by the "Time Units" field of MSR\_RAPL\_POWER\_UNIT. This field may have a hard-coded value in hardware and ignores values written by software.

- Lock (bit 63): If set, all write attempts to this MSR are ignored until next RESET.

MSR\_PKG\_ENERGY\_STATUS is a read-only MSR. It reports the actual energy use for the package domain. This MSR is updated every ~1msec. It has a wraparound time of around 60 secs when power consumption is high, and may be longer otherwise.

| 63       | 32                  | 31  | 0 |

|----------|---------------------|-----|---|

|          | Reserved            |     |   |

|          | Total Energy Consum | ned |   |

| Reserved |                     |     |   |

Figure 14-18. MSR\_PKG\_ENERGY\_STATUS MSR

• **Total Energy Consumed** (bits 31:0): The unsigned integer value represents the total amount of energy consumed since that last time this register is cleared. The unit of this field is specified by the "Energy Status Units" field of MSR\_RAPL\_POWER\_UNIT.

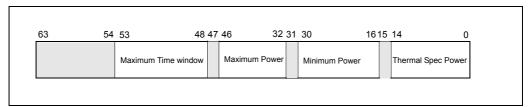

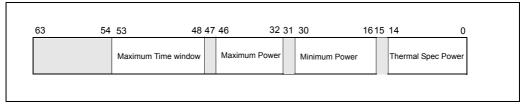

MSR\_PKG\_POWER\_INFO is a read-only MSR. It reports the package power range information for RAPL usage. This MSR provides maximum/minimum values (derived from electrical specification), thermal specification power of the package domain. It also provides the largest possible time window for software to program the RAPL interface.

#### Figure 14-19. MSR\_PKG\_POWER\_INFO Register

- **Thermal Spec Power** (bits 14:0): The unsigned integer value is the equivalent of thermal specification power of the package domain. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- **Minimum Power** (bits 30:16): The unsigned integer value is the equivalent of minimum power derived from electrical spec of the package domain. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- Maximum Power (bits 46:32): The unsigned integer value is the equivalent of maximum power derived from the electrical spec of the package domain. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- Maximum Time Window (bits 53:48): The unsigned integer value is the equivalent of largest acceptable value to program the time window of MSR\_PKG\_POWER\_LIMIT. The unit of this field is specified by the "Time Units" field of MSR\_RAPL\_POWER\_UNIT.

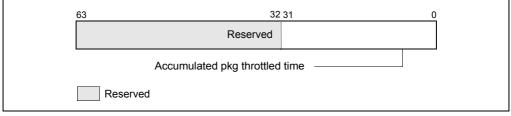

MSR\_PKG\_PERF\_STATUS is a read-only MSR. It reports the total time for which the package was throttled due to the RAPL power limits. Throttling in this context is defined as going below the OS-requested P-state or T-state. It has a wrap-around time of many hours. The availability of this MSR is platform specific (see Chapter 34).

Figure 14-20. MSR\_PKG\_PERF\_STATUS MSR

• Accumulated Package Throttled Time (bits 31:0): The unsigned integer value represents the cumulative time (since the last time this register is cleared) that the package has throttled. The unit of this field is specified by the "Time Units" field of MSR\_RAPL\_POWER\_UNIT.

# 14.7.4 PPO/PP1 RAPL Domains

The MSR interfaces defined for the PPO and PP1 domains are identical in layout. Generally, PPO refers to the processor cores. The availability of PP1 RAPL domain interface is platform-specific. For a client platform, PP1 domain refers to the power plane of a specific device in the uncore. For server platforms, PP1 domain is not supported, but its PP0 domain supports the MSR\_PP0\_PERF\_STATUS interface.

• MSR\_PP0\_POWER\_LIMIT/MSR\_PP1\_POWER\_LIMIT allow software to set power limits for the respective power plane domain.

#### POWER AND THERMAL MANAGEMENT

- MSR\_PP0\_ENERGY\_STATUS/MSR\_PP1\_ENERGY\_STATUS report actual energy usage on a power plane.

- MSR\_PP0\_POLICY/MSR\_PP1\_POLICY allow software to adjust balance for respective power plane.

MSR\_PP0\_PERF\_STATUS can report the performance impact of power limiting, but it is not available in client platform.

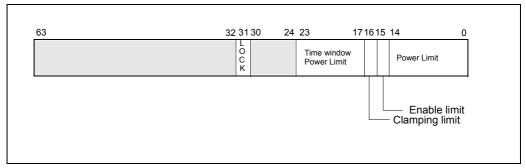

Figure 14-21. MSR\_PP0\_POWER\_LIMIT/MSR\_PP1\_POWER\_LIMIT Register

MSR\_PP0\_POWER\_LIMIT/MSR\_PP1\_POWER\_LIMIT allows a software agent to define power limitation for the respective power plane domain. A lock mechanism in each power plane domain allow the software agent to enforce power limit settings independently. Once a lock bit is set, the power limit settings in that power plane are static and un-modifiable until next RESET.

The bit fields of MSR\_PP0\_POWER\_LIMIT/MSR\_PP1\_POWER\_LIMIT (Figure 14-21) are:

- **Power Limit** (bits 14:0): Sets the average power usage limit of the respective power plane domain. The unit of this field is specified by the "Power Units" field of MSR\_RAPL\_POWER\_UNIT.

- **Enable Power Limit** (bit 15): 0 = disabled; 1 = enabled.

- **Clamping Limitation** (bit 16): Allow going below OS-requested P/T state setting during time window specified by bits 23:17.

- **Time Window for Power Limit** (bits 23:17): Indicates the length of time window over which the power limit #1 The numeric value encoded by bits 23:17 is represented by the product of 2^Y \*F; where F is a single-digit decimal floating-point value between 1.0 and 1.3 with the fraction digit represented by bits 23:22, Y is an unsigned integer represented by bits 21:17. The unit of this field is specified by the "Time Units" field of MSR\_RAPL\_POWER\_UNIT.

- Lock (bit 31): If set, all write attempts to the MSR and corresponding policy MSR\_PP0\_POLICY/MSR\_PP1\_POLICY are ignored until next RESET.

MSR\_PP0\_ENERGY\_STATUS/MSR\_PP1\_ENERGY\_STATUS is a read-only MSR. It reports the actual energy use for the respective power plane domain. This MSR is updated every ~1msec.

| 63       | 32                  | 31  | 0 |

|----------|---------------------|-----|---|