# Intel® 64 and IA-32 Architectures Software Developer's Manual

Volume 3C: System Programming Guide, Part 3

**NOTE:** The Intel® 64 and IA-32 Architectures Software Developer's Manual consists of ten volumes: Basic Architecture, Order Number 253665; Instruction Set Reference A-L, Order Number 253666; Instruction Set Reference M-U, Order Number 253667; Instruction Set Reference V-Z, Order Number 326018; Instruction Set Reference, Order Number 334569; System Programming Guide, Part 1, Order Number 253668; System Programming Guide, Part 2, Order Number 253669; System Programming Guide, Part 3, Order Number 326019; System Programming Guide, Part 4, Order Number 332831; Model-Specific Registers, Order Number 335592. Refer to all ten volumes when evaluating your design needs.

Order Number: 326019-075US

June 2021

Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>.

Intel, the Intel logo, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

${}^{*}\text{Other}$  names and brands may be claimed as the property of others.

Copyright © 1997-2021, Intel Corporation. All Rights Reserved.

# 22.1 OVERVIEW

This chapter describes the basics of virtual machine architecture and an overview of the virtual-machine extensions (VMX) that support virtualization of processor hardware for multiple software environments.

Information about VMX instructions is provided in *Intel*® *64 and IA-32 Architectures Software Developer's Manual, Volume 2B.* Other aspects of VMX and system programming considerations are described in chapters of *Intel*® *64 and IA-32 Architectures Software Developer's Manual, Volume 3B.*

# 22.2 VIRTUAL MACHINE ARCHITECTURE

Virtual-machine extensions define processor-level support for virtual machines on IA-32 processors. Two principal classes of software are supported:

- Virtual-machine monitors (VMM) A VMM acts as a host and has full control of the processor(s) and other

platform hardware. A VMM presents guest software (see next paragraph) with an abstraction of a virtual

processor and allows it to execute directly on a logical processor. A VMM is able to retain selective control of

processor resources, physical memory, interrupt management, and I/O.

- **Guest software** Each virtual machine (VM) is a guest software environment that supports a stack consisting of operating system (OS) and application software. Each operates independently of other virtual machines and uses on the same interface to processor(s), memory, storage, graphics, and I/O provided by a physical platform. The software stack acts as if it were running on a platform with no VMM. Software executing in a virtual machine must operate with reduced privilege so that the VMM can retain control of platform resources.

### 22.3 INTRODUCTION TO VMX OPERATION

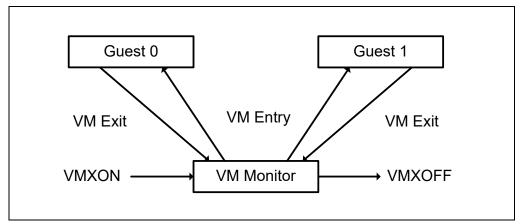

Processor support for virtualization is provided by a form of processor operation called VMX operation. There are two kinds of VMX operation: VMX root operation and VMX non-root operation. In general, a VMM will run in VMX root operation and guest software will run in VMX non-root operation. Transitions between VMX root operation and VMX non-root operation are called VMX transitions. There are two kinds of VMX transitions. Transitions into VMX non-root operation are called VM entries. Transitions from VMX non-root operation to VMX root operation are called VM exits.

Processor behavior in VMX root operation is very much as it is outside VMX operation. The principal differences are that a set of new instructions (the VMX instructions) is available and that the values that can be loaded into certain control registers are limited (see Section 22.8).

Processor behavior in VMX non-root operation is restricted and modified to facilitate virtualization. Instead of their ordinary operation, certain instructions (including the new VMCALL instruction) and events cause VM exits to the VMM. Because these VM exits replace ordinary behavior, the functionality of software in VMX non-root operation is limited. It is this limitation that allows the VMM to retain control of processor resources.

There is no software-visible bit whose setting indicates whether a logical processor is in VMX non-root operation. This fact may allow a VMM to prevent quest software from determining that it is running in a virtual machine.

Because VMX operation places restrictions even on software running with current privilege level (CPL) 0, guest software can run at the privilege level for which it was originally designed. This capability may simplify the development of a VMM.

### 22.4 LIFE CYCLE OF VMM SOFTWARE

Figure 22-1 illustrates the life cycle of a VMM and its guest software as well as the interactions between them. The following items summarize that life cycle:

- Software enters VMX operation by executing a VMXON instruction.

- Using VM entries, a VMM can then enter guests into virtual machines (one at a time). The VMM effects a VM entry using instructions VMLAUNCH and VMRESUME; it regains control using VM exits.

- VM exits transfer control to an entry point specified by the VMM. The VMM can take action appropriate to the

cause of the VM exit and can then return to the virtual machine using a VM entry.

- Eventually, the VMM may decide to shut itself down and leave VMX operation. It does so by executing the VMXOFF instruction.

Figure 22-1. Interaction of a Virtual-Machine Monitor and Guests

### 22.5 VIRTUAL-MACHINE CONTROL STRUCTURE

VMX non-root operation and VMX transitions are controlled by a data structure called a virtual-machine control structure (VMCS).

Access to the VMCS is managed through a component of processor state called the VMCS pointer (one per logical processor). The value of the VMCS pointer is the 64-bit address of the VMCS. The VMCS pointer is read and written using the instructions VMPTRST and VMPTRLD. The VMM configures a VMCS using the VMREAD, VMWRITE, and VMCLEAR instructions.

A VMM could use a different VMCS for each virtual machine that it supports. For a virtual machine with multiple logical processors (virtual processors), the VMM could use a different VMCS for each virtual processor.

#### 22.6 DISCOVERING SUPPORT FOR VMX

Before system software enters into VMX operation, it must discover the presence of VMX support in the processor. System software can determine whether a processor supports VMX operation using CPUID. If CPUID.1:ECX.VMX[bit 5] = 1, then VMX operation is supported. See Chapter 3, "Instruction Set Reference, A-L" of Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A.

The VMX architecture is designed to be extensible so that future processors in VMX operation can support additional features not present in first-generation implementations of the VMX architecture. The availability of extensible VMX features is reported to software using a set of VMX capability MSRs (see Appendix A, "VMX Capability Reporting Facility").

### 22.7 ENABLING AND ENTERING VMX OPERATION

Before system software can enter VMX operation, it enables VMX by setting CR4.VMXE[bit 13] = 1. VMX operation is then entered by executing the VMXON instruction. VMXON causes an invalid-opcode exception (#UD) if executed with CR4.VMXE = 0. Once in VMX operation, it is not possible to clear CR4.VMXE (see Section 22.8). System software leaves VMX operation by executing the VMXOFF instruction. CR4.VMXE can be cleared outside of VMX operation after executing of VMXOFF.

VMXON is also controlled by the IA32\_FEATURE\_CONTROL MSR (MSR address 3AH). This MSR is cleared to zero when a logical processor is reset. The relevant bits of the MSR are:

- **Bit 0 is the lock bit.** If this bit is clear, VMXON causes a general-protection exception. If the lock bit is set, WRMSR to this MSR causes a general-protection exception; the MSR cannot be modified until a power-up reset condition. System BIOS can use this bit to provide a setup option for BIOS to disable support for VMX. To enable VMX support in a platform, BIOS must set bit 1, bit 2, or both (see below), as well as the lock bit.

- **Bit 1 enables VMXON in SMX operation.** If this bit is clear, execution of VMXON in SMX operation causes a general-protection exception. Attempts to set this bit on logical processors that do not support both VMX operation (see Section 22.6) and SMX operation (see Chapter 6, "Safer Mode Extensions Reference," in *Intel*® 64 and IA-32 Architectures Software Developer's Manual, Volume 2D) cause general-protection exceptions.

- **Bit 2 enables VMXON outside SMX operation.** If this bit is clear, execution of VMXON outside SMX operation causes a general-protection exception. Attempts to set this bit on logical processors that do not support VMX operation (see Section 22.6) cause general-protection exceptions.

#### **NOTE**

A logical processor is in SMX operation if GETSEC[SEXIT] has not been executed since the last execution of GETSEC[SENTER]. A logical processor is outside SMX operation if GETSEC[SENTER] has not been executed or if GETSEC[SEXIT] was executed after the last execution of GETSEC[SENTER]. See Chapter 6, "Safer Mode Extensions Reference," in Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2D.

Before executing VMXON, software should allocate a naturally aligned 4-KByte region of memory that a logical processor may use to support VMX operation. This region is called the **VMXON region**. The address of the VMXON region (the VMXON pointer) is provided in an operand to VMXON. Section 23.11.5, "VMXON Region," details how software should initialize and access the VMXON region.

### 22.8 RESTRICTIONS ON VMX OPERATION

VMX operation places restrictions on processor operation. These are detailed below:

In VMX operation, processors may fix certain bits in CR0 and CR4 to specific values and not support other values. VMXON fails if any of these bits contains an unsupported value (see "VMXON—Enter VMX Operation" in Chapter 29). Any attempt to set one of these bits to an unsupported value while in VMX operation (including VMX root operation) using any of the CLTS, LMSW, or MOV CR instructions causes a general-protection exception. VM entry or VM exit cannot set any of these bits to an unsupported value. Software should consult the VMX capability MSRs IA32\_VMX\_CR0\_FIXED0 and IA32\_VMX\_CR0\_FIXED1 to determine how bits in CR0 are fixed (see Appendix A.7). For CR4, software should consult the VMX capability MSRs IA32\_VMX\_CR4\_FIXED0 and IA32\_VMX\_CR4\_FIXED1 (see Appendix A.8).

### **NOTES**

The first processors to support VMX operation require that the following bits be 1 in VMX operation: CR0.PE, CR0.NE, CR0.PG, and CR4.VMXE. The restrictions on CR0.PE and CR0.PG imply that VMX

<sup>1.</sup> Future processors may require that a different amount of memory be reserved. If so, this fact is reported to software using the VMX capability-reporting mechanism.

#### INTRODUCTION TO VIRTUAL MACHINE EXTENSIONS

operation is supported only in paged protected mode (including IA-32e mode). Therefore, guest software cannot be run in unpaged protected mode or in real-address mode.

Later processors support a VM-execution control called "unrestricted guest" (see Section 23.6.2). If this control is 1, CR0.PE and CR0.PG may be 0 in VMX non-root operation (even if the capability MSR IA32\_VMX\_CR0\_FIXED0 reports otherwise). Such processors allow guest software to run in unpaged protected mode or in real-address mode.

- VMXON fails if a logical processor is in A20M mode (see "VMXON—Enter VMX Operation" in Chapter 29). Once

the processor is in VMX operation, A20M interrupts are blocked. Thus, it is impossible to be in A20M mode in

VMX operation.

- The INIT signal is blocked whenever a logical processor is in VMX root operation. It is not blocked in VMX non-root operation. Instead, INITs cause VM exits (see Section 24.2, "Other Causes of VM Exits").

- Intel® Processor Trace (Intel PT) can be used in VMX operation only if IA32\_VMX\_MISC[14] is read as 1 (see Appendix A.6). On processors that support Intel PT but which do not allow it to be used in VMX operation, execution of VMXON clears IA32\_RTIT\_CTL.TraceEn (see "VMXON—Enter VMX Operation" in Chapter 29); any attempt to write IA32\_RTIT\_CTL while in VMX operation (including VMX root operation) causes a general-protection exception.

<sup>1. &</sup>quot;Unrestricted guest" is a secondary processor-based VM-execution control. If bit 31 of the primary processor-based VM-execution controls is 0, VMX non-root operation functions as if the "unrestricted guest" VM-execution control were 0. See Section 23.6.2.

### 23.1 OVERVIEW

A logical processor uses **virtual-machine control data structures** (**VMCSs**) while it is in VMX operation. These manage transitions into and out of VMX non-root operation (VM entries and VM exits) as well as processor behavior in VMX non-root operation. This structure is manipulated by the new instructions VMCLEAR, VMPTRLD, VMREAD, and VMWRITE.

A VMM can use a different VMCS for each virtual machine that it supports. For a virtual machine with multiple logical processors (virtual processors), the VMM can use a different VMCS for each virtual processor.

A logical processor associates a region in memory with each VMCS. This region is called the **VMCS region**. Software references a specific VMCS using the 64-bit physical address of the region (a **VMCS pointer**). VMCS pointers must be aligned on a 4-KByte boundary (bits 11:0 must be zero). These pointers must not set bits beyond the processor's physical-address width. <sup>2,3</sup>

A logical processor may maintain a number of VMCSs that are **active**. The processor may optimize VMX operation by maintaining the state of an active VMCS in memory, on the processor, or both. At any given time, at most one of the active VMCSs is the **current** VMCS. (This document frequently uses the term "the VMCS" to refer to the current VMCS.) The VMLAUNCH, VMREAD, VMRESUME, and VMWRITE instructions operate only on the current VMCS.

The following items describe how a logical processor determines which VMCSs are active and which is current:

- The memory operand of the VMPTRLD instruction is the address of a VMCS. After execution of the instruction, that VMCS is both active and current on the logical processor. Any other VMCS that had been active remains so, but no other VMCS is current.

- The VMCS link pointer field in the current VMCS (see Section 23.4.2) is itself the address of a VMCS. If VM entry is performed successfully with the 1-setting of the "VMCS shadowing" VM-execution control, the VMCS referenced by the VMCS link pointer field becomes active on the logical processor. The identity of the current VMCS does not change.

- The memory operand of the VMCLEAR instruction is also the address of a VMCS. After execution of the instruction, that VMCS is neither active nor current on the logical processor. If the VMCS had been current on the logical processor, the logical processor no longer has a current VMCS.

The VMPTRST instruction stores the address of the logical processor's current VMCS into a specified memory location (it stores the value FFFFFFFF\_FFFFFFH if there is no current VMCS).

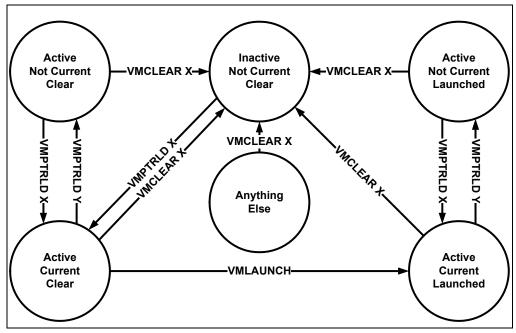

The **launch state** of a VMCS determines which VM-entry instruction should be used with that VMCS: the VMLAUNCH instruction requires a VMCS whose launch state is "clear"; the VMRESUME instruction requires a VMCS whose launch state is "launched". A logical processor maintains a VMCS's launch state in the corresponding VMCS region. The following items describe how a logical processor manages the launch state of a VMCS:

- If the launch state of the current VMCS is "clear", successful execution of the VMLAUNCH instruction changes the launch state to "launched".

- The memory operand of the VMCLEAR instruction is the address of a VMCS. After execution of the instruction, the launch state of that VMCS is "clear".

- There are no other ways to modify the launch state of a VMCS (it cannot be modified using VMWRITE) and there is no direct way to discover it (it cannot be read using VMREAD).

<sup>1.</sup> The amount of memory required for a VMCS region is at most 4 KBytes. The exact size is implementation specific and can be determined by consulting the VMX capability MSR IA32 VMX BASIC to determine the size of the VMCS region (see Appendix A.1).

<sup>2.</sup> Software can determine a processor's physical-address width by executing CPUID with 80000008H in EAX. The physical-address width is returned in bits 7:0 of EAX.

<sup>3.</sup> If IA32\_VMX\_BASIC[48] is read as 1, these pointers must not set any bits in the range 63:32; see Appendix A.1.

Figure 23-1 illustrates the different states of a VMCS. It uses "X" to refer to the VMCS and "Y" to refer to any other VMCS. Thus: "VMPTRLD X" always makes X current and active; "VMPTRLD Y" always makes X not current (because it makes Y current); VMLAUNCH makes the launch state of X "launched" if X was current and its launch state was "clear"; and VMCLEAR X always makes X inactive and not current and makes its launch state "clear".

The figure does not illustrate operations that do not modify the VMCS state relative to these parameters (e.g., execution of VMPTRLD X when X is already current). Note that VMCLEAR X makes X "inactive, not current, and clear," even if X's current state is not defined (e.g., even if X has not yet been initialized). See Section 23.11.3.

Figure 23-1. States of VMCS X

Because a shadow VMCS (see Section 23.10) cannot be used for VM entry, the launch state of a shadow VMCS is not meaningful. Figure 23-1 does not illustrate all the ways in which a shadow VMCS may be made active.

# 23.2 FORMAT OF THE VMCS REGION

A VMCS region comprises up to 4-KBytes. The format of a VMCS region is given in Table 23-1.

| Byte Offset | Contents                                                                              |  |

|-------------|---------------------------------------------------------------------------------------|--|

| 0           | Bits 30:0: VMCS revision identifier Bit 31: shadow-VMCS indicator (see Section 23.10) |  |

| 4           | VMX-abort indicator                                                                   |  |

| 8           | VMCS data (implementation-specific format)                                            |  |

Table 23-1. Format of the VMCS Region

The exact size is implementation specific and can be determined by consulting the VMX capability MSR IA32\_VMX\_BASIC to determine the size of the VMCS region (see Appendix A.1).

The first 4 bytes of the VMCS region contain the **VMCS revision identifier** at bits 30:0. Processors that maintain VMCS data in different formats (see below) use different VMCS revision identifiers. These identifiers enable software to avoid using a VMCS region formatted for one processor on a processor that uses a different format. Bit 31 of this 4-byte region indicates whether the VMCS is a shadow VMCS (see Section 23.10).

Software should write the VMCS revision identifier to the VMCS region before using that region for a VMCS. The VMCS revision identifier is never written by the processor; VMPTRLD fails if its operand references a VMCS region whose VMCS revision identifier differs from that used by the processor. (VMPTRLD also fails if the shadow-VMCS indicator is 1 and the processor does not support the 1-setting of the "VMCS shadowing" VM-execution control; see Section 23.6.2) Software can discover the VMCS revision identifier that a processor uses by reading the VMX capability MSR IA32\_VMX\_BASIC (see Appendix A.1).

Software should clear or set the shadow-VMCS indicator depending on whether the VMCS is to be an ordinary VMCS or a shadow VMCS (see Section 23.10). VMPTRLD fails if the shadow-VMCS indicator is set and the processor does not support the 1-setting of the "VMCS shadowing" VM-execution control. Software can discover support for this setting by reading the VMX capability MSR IA32\_VMX\_PROCBASED\_CTLS2 (see Appendix A.3.3).

The next 4 bytes of the VMCS region are used for the **VMX-abort indicator**. The contents of these bits do not control processor operation in any way. A logical processor writes a non-zero value into these bits if a VMX abort occurs (see Section 26.7). Software may also write into this field.

The remainder of the VMCS region is used for **VMCS data** (those parts of the VMCS that control VMX non-root operation and the VMX transitions). The format of these data is implementation-specific. VMCS data are discussed in Section 23.3 through Section 23.9. To ensure proper behavior in VMX operation, software should maintain the VMCS region and related structures (enumerated in Section 23.11.4) in writeback cacheable memory. Future implementations may allow or require a different memory type<sup>3</sup>. Software should consult the VMX capability MSR IA32 VMX BASIC (see Appendix A.1).

### 23.3 ORGANIZATION OF VMCS DATA

The VMCS data are organized into six logical groups:

- **Guest-state area.** Processor state is saved into the guest-state area on VM exits and loaded from there on VM entries.

- Host-state area. Processor state is loaded from the host-state area on VM exits.

- VM-execution control fields. These fields control processor behavior in VMX non-root operation. They

determine in part the causes of VM exits.

- VM-exit control fields. These fields control VM exits.

- VM-entry control fields. These fields control VM entries.

- VM-exit information fields. These fields receive information on VM exits and describe the cause and the nature of VM exits. On some processors, these fields are read-only.<sup>4</sup>

The VM-execution control fields, the VM-exit control fields, and the VM-entry control fields are sometimes referred to collectively as VMX controls.

<sup>1.</sup> Earlier versions of this manual specified that the VMCS revision identifier was a 32-bit field. For all processors produced prior to this change, bit 31 of the VMCS revision identifier was 0.

<sup>2.</sup> Logical processors that use the same VMCS revision identifier use the same size for VMCS regions.

<sup>3.</sup> Alternatively, software may map any of these regions or structures with the UC memory type. Doing so is strongly discouraged unless necessary as it will cause the performance of transitions using those structures to suffer significantly. In addition, the processor will continue to use the memory type reported in the VMX capability MSR IA32\_VMX\_BASIC with exceptions noted in Appendix A.1.

<sup>4.</sup> Software can discover whether these fields can be written by reading the VMX capability MSR IA32\_VMX\_MISC (see Appendix A.6).

### 23.4 GUEST-STATE AREA

This section describes fields contained in the guest-state area of the VMCS. VM entries load processor state from these fields and VM exits store processor state into these fields. See Section 25.3.2 and Section 26.3 for details.

### 23.4.1 Guest Register State

The following fields in the guest-state area correspond to processor registers:

- Control registers CR0, CR3, and CR4 (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- Debug register DR7 (64 bits: 32 bits on processors that do not support Intel 64 architecture).

- RSP, RIP, and RFLAGS (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- The following fields for each of the registers CS, SS, DS, ES, FS, GS, LDTR, and TR:

- Selector (16 bits).

- Base address (64 bits; 32 bits on processors that do not support Intel 64 architecture). The base-address fields for CS, SS, DS, and ES have only 32 architecturally-defined bits; nevertheless, the corresponding VMCS fields have 64 bits on processors that support Intel 64 architecture.

- Segment limit (32 bits). The limit field is always a measure in bytes.

- Access rights (32 bits). The format of this field is given in Table 23-2 and detailed as follows:

- The low 16 bits correspond to bits 23:8 of the upper 32 bits of a 64-bit segment descriptor. While bits 19:16 of code-segment and data-segment descriptors correspond to the upper 4 bits of the segment limit, the corresponding bits (bits 11:8) are reserved in this VMCS field.

- Bit 16 indicates an **unusable segment**. Attempts to use such a segment fault except in 64-bit mode. In general, a segment register is unusable if it has been loaded with a null selector.<sup>2</sup>

- Bits 31:17 are reserved.

Table 23-2. Format of Access Rights

| Bit Position(s) | Field                                              |  |

|-----------------|----------------------------------------------------|--|

| 3:0             | Segment type                                       |  |

| 4               | S — Descriptor type (0 = system; 1 = code or data) |  |

| 6:5             | DPL — Descriptor privilege level                   |  |

| 7               | P — Segment present                                |  |

| 11:8            | Reserved                                           |  |

| 12              | AVL — Available for use by system software         |  |

<sup>1.</sup> This chapter uses the notation RAX, RIP, RSP, RFLAGS, etc. for processor registers because most processors that support VMX operation also support Intel 64 architecture. For processors that do not support Intel 64 architecture, this notation refers to the 32-bit forms of those registers (EAX, EIP, ESP, EFLAGS, etc.). In a few places, notation such as EAX is used to refer specifically to lower 32 bits of the indicated register.

<sup>2.</sup> There are a few exceptions to this statement. For example, a segment with a non-null selector may be unusable following a task switch that fails after its commit point; see "Interrupt 10—Invalid TSS Exception (#TS)" in Section 6.14, "Exception and Interrupt Handling in 64-bit Mode," of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A. In contrast, the TR register is usable after processor reset despite having a null selector; see Table 10-1 in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

| Table 23-2.  | Format of    | Access | Rights | (Contd.)   |

|--------------|--------------|--------|--------|------------|

| I dule LJ-L. | i Ollilat Ol | MCCE33 | Mulica | i Corrida. |

| Bit Position(s) | Field                                                                |  |

|-----------------|----------------------------------------------------------------------|--|

| 13              | Reserved (except for CS)<br>L — 64-bit mode active (for CS only)     |  |

| 14              | /B — Default operation size (0 = 16-bit segment; 1 = 32-bit segment) |  |

| 15              | G — Granularity                                                      |  |

| 16              | Segment unusable (0 = usable; 1 = unusable)                          |  |

| 31:17           | Reserved                                                             |  |

The base address, segment limit, and access rights compose the "hidden" part (or "descriptor cache") of each segment register. These data are included in the VMCS because it is possible for a segment register's descriptor cache to be inconsistent with the segment descriptor in memory (in the GDT or the LDT) referenced by the segment register's selector.

The value of the DPL field for SS is always equal to the logical processor's current privilege level (CPL).<sup>1</sup>

On some processors, executions of VMWRITE ignore attempts to write non-zero values to any of bits 11:8 or bits 31:17. On such processors, VMREAD always returns 0 for those bits, and VM entry treats those bits as if they were all 0 (see Section 25.3.1.2).

- The following fields for each of the registers GDTR and IDTR:

- Base address (64 bits; 32 bits on processors that do not support Intel 64 architecture).

- Limit (32 bits). The limit fields contain 32 bits even though these fields are specified as only 16 bits in the architecture.

#### The following MSRs:

- IA32 DEBUGCTL (64 bits)

- IA32 SYSENTER CS (32 bits)

- IA32\_SYSENTER\_ESP and IA32\_SYSENTER\_EIP (64 bits; 32 bits on processors that do not support Intel 64 architecture)

- IA32\_PERF\_GLOBAL\_CTRL (64 bits). This field is supported only on processors that support the 1-setting of the "load IA32\_PERF\_GLOBAL\_CTRL" VM-entry control.

- IA32\_PAT (64 bits). This field is supported only on processors that support either the 1-setting of the "load IA32\_PAT" VM-entry control or that of the "save IA32\_PAT" VM-exit control.

- IA32\_EFER (64 bits). This field is supported only on processors that support either the 1-setting of the "load IA32\_EFER" VM-entry control or that of the "save IA32\_EFER" VM-exit control.

- IA32\_BNDCFGS (64 bits). This field is supported only on processors that support either the 1-setting of the "load IA32\_BNDCFGS" VM-entry control or that of the "clear IA32\_BNDCFGS" VM-exit control.

- IA32\_RTIT\_CTL (64 bits). This field is supported only on processors that support either the 1-setting of the "load IA32\_RTIT\_CTL" VM-entry control or that of the "clear IA32\_RTIT\_CTL" VM-exit control.

- IA32\_S\_CET (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-entry control.

- IA32\_INTERRUPT\_SSP\_TABLE\_ADDR (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-entry control.

- IA32\_PKRS (64 bits). This field is supported only on processors that support the 1-setting of the "load PKRS" VM-entry control.

<sup>1.</sup> In protected mode, CPL is also associated with the RPL field in the CS selector. However, the RPL fields are not meaningful in real-address mode or in virtual-8086 mode.

- The shadow-stack pointer register SSP (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-entry control.

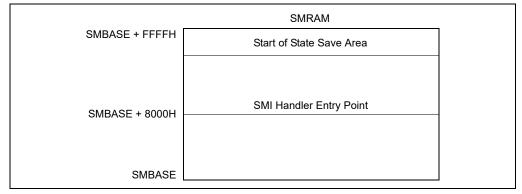

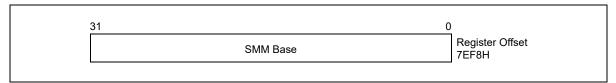

- The register SMBASE (32 bits). This register contains the base address of the logical processor's SMRAM image.

# 23.4.2 Guest Non-Register State

In addition to the register state described in Section 23.4.1, the guest-state area includes the following fields that characterize quest state but which do not correspond to processor registers:

Activity state (32 bits). This field identifies the logical processor's activity state. When a logical processor is

executing instructions normally, it is in the active state. Execution of certain instructions and the occurrence

of certain events may cause a logical processor to transition to an inactive state in which it ceases to execute

instructions.

The following activity states are defined: 1

- 0: **Active**. The logical processor is executing instructions normally.

- 1: HLT. The logical processor is inactive because it executed the HLT instruction.

- 2: Shutdown. The logical processor is inactive because it incurred a triple fault<sup>2</sup> or some other serious error.

- 3: **Wait-for-SIPI**. The logical processor is inactive because it is waiting for a startup-IPI (SIPI).

Future processors may include support for other activity states. Software should read the VMX capability MSR IA32\_VMX\_MISC (see Appendix A.6) to determine what activity states are supported.

• **Interruptibility state** (32 bits). The IA-32 architecture includes features that permit certain events to be blocked for a period of time. This field contains information about such blocking. Details and the format of this field are given in Table 23-3.

| Bit<br>Position(s) | Bit Name              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | Blocking by STI       | See the "STI—Set Interrupt Flag" section in Chapter 4 of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B.  Execution of STI with RFLAGS.IF = 0 blocks maskable interrupts on the instruction boundary following its execution. Setting this bit indicates that this blocking is in effect.                                                                                                                                                                                                  |

| 1                  | Blocking by<br>MOV SS | See Section 6.8.3, "Masking Exceptions and Interrupts When Switching Stacks," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.  Execution of a MOV to SS or a POP to SS blocks or suppresses certain debug exceptions as well as interrupts (maskable and nonmaskable) on the instruction boundary following its execution. Setting this bit indicates that this blocking is in effect. <sup>2</sup> This document uses the term "blocking by MOV SS," but it applies equally to POP SS. |

| 2                  | Blocking by SMI       | See Section 30.2, "System Management Interrupt (SMI)." System-management interrupts (SMIs) are disabled while the processor is in system-management mode (SMM). Setting this bit indicates that blocking of SMIs is in effect.                                                                                                                                                                                                                                                                                           |

Table 23-3. Format of Interruptibility State

<sup>1.</sup> Execution of the MWAIT instruction may put a logical processor into an inactive state. However, this VMCS field never reflects this state. See Section 26.1.

<sup>2.</sup> A triple fault occurs when a logical processor encounters an exception while attempting to deliver a double fault.

Table 23-3. Format of Interruptibility State (Contd.)

| Bit<br>Position(s) | Bit Name                | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                  | Blocking by NMI         | See Section 6.7.1, "Handling Multiple NMIs," in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A and Section 30.8, "NMI Handling While in SMM."                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                         | Delivery of a non-maskable interrupt (NMI) or a system-management interrupt (SMI) blocks subsequent NMIs until the next execution of IRET. See Section 24.3 for how this behavior of IRET may change in VMX non-root operation. Setting this bit indicates that blocking of NMIs is in effect. Clearing this bit does not imply that NMIs are not (temporarily) blocked for other reasons.  If the "virtual NMIs" VM-execution control (see Section 23.6.1) is 1, this bit does not control the blocking of NMIs. Instead, it refers to "virtual-NMI blocking" (the fact that guest software is not ready for an NMI). |

| 4                  | Enclave<br>interruption | Set to 1 if the VM exit occurred while the logical processor was in enclave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |                         | Such VM exits includes those caused by interrupts, non-maskable interrupts, system-management interrupts, INIT signals, and exceptions occurring in enclave mode as well as exceptions encountered during the delivery of such events incident to enclave mode.                                                                                                                                                                                                                                                                                                                                                        |

|                    |                         | A VM exit that is incident to delivery of an event injected by VM entry leaves this bit unmodified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31:5               | Reserved                | VM entry will fail if these bits are not 0. See Section 25.3.1.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **NOTES:**

- 1. Nonmaskable interrupts and system-management interrupts may also be inhibited on the instruction boundary following such an execution of STI.

- 2. System-management interrupts may also be inhibited on the instruction boundary following such an execution of MOV or POP.

- **Pending debug exceptions** (64 bits; 32 bits on processors that do not support Intel 64 architecture). IA-32 processors may recognize one or more debug exceptions without immediately delivering them. This field contains information about such exceptions. This field is described in Table 23-4.

Table 23-4. Format of Pending-Debug-Exceptions

| Bit<br>Position(s) | Bit Name              | Notes                                                                                                                                                                              |

|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0                | B3 - B0               | When set, each of these bits indicates that the corresponding breakpoint condition was met. Any of these bits may be set even if the corresponding enabling bit in DR7 is not set. |

| 11:4               | Reserved              | VM entry fails if these bits are not 0. See Section 25.3.1.5.                                                                                                                      |

| 12                 | Enabled<br>breakpoint | When set, this bit indicates that at least one data or I/O breakpoint was met and was enabled in DR7.                                                                              |

| 13                 | Reserved              | VM entry fails if this bit is not 0. See Section 25.3.1.5.                                                                                                                         |

| 14                 | BS                    | When set, this bit indicates that a debug exception would have been triggered by single-step execution mode.                                                                       |

| 15                 | Reserved              | VM entry fails if this bit is not 0. See Section 25.3.1.5.                                                                                                                         |

<sup>1.</sup> For example, execution of a MOV to SS or a POP to SS may inhibit some debug exceptions for one instruction. See Section 6.8.3 of Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A. In addition, certain events incident to an instruction (for example, an INIT signal) may take priority over debug traps generated by that instruction. See Table 6-2 in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A.

| Table 23-4. | Format of | Pendina | -Debua | -Except | ions (Contd.) |

|-------------|-----------|---------|--------|---------|---------------|

|             |           |         |        |         |               |

| Bit<br>Position(s) | Bit Name | Notes                                                                                                                                                                                                                                                                                                                        |

|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                 | RTM      | When set, this bit indicates that a debug exception (#DB) or a breakpoint exception (#BP) occurred inside an RTM region while advanced debugging of RTM transactional regions was enabled (see Section 16.3.7, "RTM-Enabled Debugger Support," of Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1).1 |

| 63:17              | Reserved | VM entry fails if these bits are not 0. See Section 25.3.1.5. Bits 63:32 exist only on processors that support Intel 64 architecture.                                                                                                                                                                                        |

#### **NOTES:**

- 1. In general, the format of this field matches that of DR6. However, DR6 **clears** bit 16 to indicate an RTM-related exception, while this field **sets** the bit to indicate that condition.

- **VMCS link pointer** (64 bits). If the "VMCS shadowing" VM-execution control is 1, the VMREAD and VMWRITE instructions access the VMCS referenced by this pointer (see Section 23.10). Otherwise, software should set this field to FFFFFFFFFFFFFH to avoid VM-entry failures (see Section 25.3.1.5).

- **VMX-preemption timer value** (32 bits). This field is supported only on processors that support the 1-setting of the "activate VMX-preemption timer" VM-execution control. This field contains the value that the VMX-preemption timer will use following the next VM entry with that setting. See Section 24.5.1 and Section 25.7.4.

- Page-directory-pointer-table entries (PDPTEs; 64 bits each). These four (4) fields (PDPTE0, PDPTE1, PDPTE2, and PDPTE3) are supported only on processors that support the 1-setting of the "enable EPT" VM-execution control. They correspond to the PDPTEs referenced by CR3 when PAE paging is in use (see Section 4.4 in the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A). They are used only if the "enable EPT" VM-execution control is 1.

- **Guest interrupt status** (16 bits). This field is supported only on processors that support the 1-setting of the "virtual-interrupt delivery" VM-execution control. It characterizes part of the guest's virtual-APIC state and does not correspond to any processor or APIC registers. It comprises two 8-bit subfields:

- Requesting virtual interrupt (RVI). This is the low byte of the guest interrupt status. The processor treats this value as the vector of the highest priority virtual interrupt that is requesting service. (The value 0 implies that there is no such interrupt.)

- Servicing virtual interrupt (SVI). This is the high byte of the guest interrupt status. The processor treats

this value as the vector of the highest priority virtual interrupt that is in service. (The value 0 implies that

there is no such interrupt.)

See Chapter 28 for more information on the use of this field.

• **PML index** (16 bits). This field is supported only on processors that support the 1-setting of the "enable PML" VM-execution control. It contains the logical index of the next entry in the page-modification log. Because the page-modification log comprises 512 entries, the PML index is typically a value in the range 0–511. Details of the page-modification log and use of the PML index are given in Section 27.2.6.

# 23.5 HOST-STATE AREA

This section describes fields contained in the host-state area of the VMCS. As noted earlier, processor state is loaded from these fields on every VM exit (see Section 26.5).

All fields in the host-state area correspond to processor registers:

- CR0, CR3, and CR4 (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- RSP and RIP (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- Selector fields (16 bits each) for the segment registers CS, SS, DS, ES, FS, GS, and TR. There is no field in the host-state area for the LDTR selector.

- Base-address fields for FS, GS, TR, GDTR, and IDTR (64 bits each; 32 bits on processors that do not support Intel 64 architecture).

- The following MSRs:

- IA32\_SYSENTER\_CS (32 bits)

- IA32\_SYSENTER\_ESP and IA32\_SYSENTER\_EIP (64 bits; 32 bits on processors that do not support Intel 64 architecture).

- IA32\_PERF\_GLOBAL\_CTRL (64 bits). This field is supported only on processors that support the 1-setting of the "load IA32\_PERF\_GLOBAL\_CTRL" VM-exit control.

- IA32\_PAT (64 bits). This field is supported only on processors that support the 1-setting of the "load IA32\_PAT" VM-exit control.

- IA32\_EFER (64 bits). This field is supported only on processors that support the 1-setting of the "load IA32\_EFER" VM-exit control.

- IA32\_S\_CET (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-exit control.

- IA32\_INTERRUPT\_SSP\_TABLE\_ADDR (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-exit control.

- IA32\_PKRS (64 bits). This field is supported only on processors that support the 1-setting of the "load PKRS" VM-exit control.

- The shadow-stack pointer register SSP (64 bits; 32 bits on processors that do not support Intel 64 architecture). This field is supported only on processors that support the 1-setting of the "load CET state" VM-exit control.

In addition to the state identified here, some processor state components are loaded with fixed values on every VM exit; there are no fields corresponding to these components in the host-state area. See Section 26.5 for details of how state is loaded on VM exits.

### 23.6 VM-EXECUTION CONTROL FIELDS

The VM-execution control fields govern VMX non-root operation. These are described in Section 23.6.1 through Section 23.6.8.

### 23.6.1 Pin-Based VM-Execution Controls

The pin-based VM-execution controls constitute a 32-bit vector that governs the handling of asynchronous events (for example: interrupts). Table 23-5 lists the controls. See Chapter 26 for how these controls affect processor behavior in VMX non-root operation.

<sup>1.</sup> Some asynchronous events cause VM exits regardless of the settings of the pin-based VM-execution controls (see Section 24.2).

| Bit Position(s) | Name                              | Description                                                                                                                                                                                                                                                                    |

|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | External-interrupt exiting        | If this control is 1, external interrupts cause VM exits. Otherwise, they are delivered normally through the guest interrupt-descriptor table (IDT). If this control is 1, the value of RFLAGS.IF does not affect interrupt blocking.                                          |

| 3               | NMI exiting                       | If this control is 1, non-maskable interrupts (NMIs) cause VM exits. Otherwise, they are delivered normally using descriptor 2 of the IDT. This control also determines interactions between IRET and blocking by NMI (see Section 24.3).                                      |

| 5               | Virtual NMIs                      | If this control is 1, NMIs are never blocked and the "blocking by NMI" bit (bit 3) in the interruptibility-state field indicates "virtual-NMI blocking" (see Table 23-3). This control also interacts with the "NMI-window exiting" VM-execution control (see Section 23.6.2). |

| 6               | Activate VMX-<br>preemption timer | If this control is 1, the VMX-preemption timer counts down in VMX non-root operation; see Section 24.5.1. A VM exit occurs when the timer counts down to zero; see Section 24.2.                                                                                               |

| 7               | Process posted interrupts         | If this control is 1, the processor treats interrupts with the posted-interrupt notification vector (see Section 23.6.8) specially, updating the virtual-APIC page with posted-interrupt requests (see Section 28.6).                                                          |

Table 23-5. Definitions of Pin-Based VM-Execution Controls

All other bits in this field are reserved, some to 0 and some to 1. Software should consult the VMX capability MSRs IA32\_VMX\_PINBASED\_CTLS and IA32\_VMX\_TRUE\_PINBASED\_CTLS (see Appendix A.3.1) to determine how to set reserved bits. Failure to set reserved bits properly causes subsequent VM entries to fail (see Section 25.2.1.1).

The first processors to support the virtual-machine extensions supported only the 1-settings of bits 1, 2, and 4. The VMX capability MSR IA32\_VMX\_PINBASED\_CTLS will always report that these bits must be 1. Logical processors that support the 0-settings of any of these bits will support the VMX capability MSR IA32\_VMX\_TRUE\_PINBASED\_CTLS MSR, and software should consult this MSR to discover support for the 0-

settings of these bits. Software that is not aware of the functionality of any one of these bits should set that bit to 1.

#### 23.6.2 Processor-Based VM-Execution Controls

The processor-based VM-execution controls constitute three vectors that govern the handling of synchronous events, mainly those caused by the execution of specific instructions. These are the **primary processor-based VM-execution controls** (32 bits), the **secondary processor-based VM-execution controls** (32 bits), and the tertiary **VM-execution controls** (64 bits).

Table 23-6 lists the primary processor-based VM-execution controls. See Chapter 24 for more details of how these controls affect processor behavior in VMX non-root operation.

| Bit Position(s) | Name                     | Description                                                                                                                                                                                                                              |

|-----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2               | Interrupt-window exiting | If this control is 1, a VM exit occurs at the beginning of any instruction if RFLAGS.IF = 1 and there are no other blocking of interrupts (see Section 23.4.2).                                                                          |

| 3               | Use TSC offsetting       | This control determines whether executions of RDTSC, executions of RDTSCP, and executions of RDMSR that read from the IA32_TIME_STAMP_COUNTER MSR return a value modified by the TSC offset field (see Section 23.6.5 and Section 24.3). |

| 7               | HLT exiting              | This control determines whether executions of HLT cause VM exits.                                                                                                                                                                        |

| 9               | INVLPG exiting           | This determines whether executions of INVLPG cause VM exits.                                                                                                                                                                             |

| 10              | MWAIT exiting            | This control determines whether executions of MWAIT cause VM exits.                                                                                                                                                                      |

| 11              | RDPMC exiting            | This control determines whether executions of RDPMC cause VM exits.                                                                                                                                                                      |

Table 23-6. Definitions of Primary Processor-Based VM-Execution Controls

<sup>1.</sup> Some instructions cause VM exits regardless of the settings of the processor-based VM-execution controls (see Section 24.1.2), as do task switches (see Section 24.2).

Table 23-6. Definitions of Primary Processor-Based VM-Execution Controls (Contd.)

| Bit Position(s) | Name                        | Description                                                                                                                                                                                                                   |

|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12              | RDTSC exiting               | This control determines whether executions of RDTSC and RDTSCP cause VM exits.                                                                                                                                                |

| 15              | CR3-load exiting            | In conjunction with the CR3-target controls (see Section 23.6.7), this control determines whether executions of MOV to CR3 cause VM exits. See Section 24.1.3.                                                                |

|                 |                             | The first processors to support the virtual-machine extensions supported only the 1-setting of this control.                                                                                                                  |

| 16              | CR3-store exiting           | This control determines whether executions of MOV from CR3 cause VM exits.                                                                                                                                                    |

|                 |                             | The first processors to support the virtual-machine extensions supported only the 1-setting of this control.                                                                                                                  |

| 17              | Activate tertiary controls  | This control determines whether the tertiary processor-based VM-execution controls are used. If this control is 0, the logical processor operates as if all the tertiary processor-based VM-execution controls were also 0.   |

| 19              | CR8-load exiting            | This control determines whether executions of MOV to CR8 cause VM exits.                                                                                                                                                      |

| 20              | CR8-store exiting           | This control determines whether executions of MOV from CR8 cause VM exits.                                                                                                                                                    |

| 21              | Use TPR shadow              | Setting this control to 1 enables TPR virtualization and other APIC-virtualization features. See Chapter 28.                                                                                                                  |

| 22              | NMI-window<br>exiting       | If this control is 1, a VM exit occurs at the beginning of any instruction if there is no virtual-NMI blocking (see Section 23.4.2).                                                                                          |

| 23              | MOV-DR exiting              | This control determines whether executions of MOV DR cause VM exits.                                                                                                                                                          |

| 24              | Unconditional I/O exiting   | This control determines whether executions of I/O instructions (IN, INS/INSB/INSW/INSD, OUT, and OUTS/OUTSB/OUTSW/OUTSD) cause VM exits.                                                                                      |

| 25              | Use I/O bitmaps             | This control determines whether I/O bitmaps are used to restrict executions of I/O instructions (see Section 23.6.4 and Section 24.1.3).                                                                                      |

|                 |                             | For this control, "0" means "do not use I/O bitmaps" and "1" means "use I/O bitmaps." If the I/O bitmaps are used, the setting of the "unconditional I/O exiting" control is ignored.                                         |

| 27              | Monitor trap flag           | If this control is 1, the monitor trap flag debugging feature is enabled. See Section 24.5.2.                                                                                                                                 |

| 28              | Use MSR bitmaps             | This control determines whether MSR bitmaps are used to control execution of the RDMSR and WRMSR instructions (see Section 23.6.9 and Section 24.1.3).                                                                        |

|                 |                             | For this control, "0" means "do not use MSR bitmaps" and "1" means "use MSR bitmaps." If the MSR bitmaps are not used, all executions of the RDMSR and WRMSR instructions cause VM exits.                                     |

| 29              | MONITOR exiting             | This control determines whether executions of MONITOR cause VM exits.                                                                                                                                                         |

| 30              | PAUSE exiting               | This control determines whether executions of PAUSE cause VM exits.                                                                                                                                                           |

| 31              | Activate secondary controls | This control determines whether the secondary processor-based VM-execution controls are used. If this control is 0, the logical processor operates as if all the secondary processor-based VM-execution controls were also 0. |

All other bits in this field are reserved, some to 0 and some to 1. Software should consult the VMX capability MSRs IA32\_VMX\_PROCBASED\_CTLS and IA32\_VMX\_TRUE\_PROCBASED\_CTLS (see Appendix A.3.2) to determine how to set reserved bits. Failure to set reserved bits properly causes subsequent VM entries to fail (see Section 25.2.1.1).

The first processors to support the virtual-machine extensions supported only the 1-settings of bits 1, 4–6, 8, 13–16, and 26. The VMX capability MSR IA32\_VMX\_PROCBASED\_CTLS will always report that these bits must be 1. Logical processors that support the 0-settings of any of these bits will support the VMX capability MSR IA32\_VMX\_TRUE\_PROCBASED\_CTLS MSR, and software should consult this MSR to discover support for the 0-settings of these bits. Software that is not aware of the functionality of any one of these bits should set that bit to 1.

Bit 31 of the primary processor-based VM-execution controls determines whether the secondary processor-based VM-execution controls are used. If that bit is 0, VM entry and VMX non-root operation function as if all the secondary processor-based VM-execution controls were 0. Processors that support only the 0-setting of bit 31 of

the primary processor-based VM-execution controls do not support the secondary processor-based VM-execution controls.

Table 23-7 lists the secondary processor-based VM-execution controls. See Chapter 24 for more details of how these controls affect processor behavior in VMX non-root operation.

Table 23-7. Definitions of Secondary Processor-Based VM-Execution Controls

| Bit Position(s) | Name                                     | Description                                                                                                                                                                                                                |

|-----------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | Virtualize APIC accesses                 | If this control is 1, the logical processor treats specially accesses to the page with the APIC-access address. See Section 28.4.                                                                                          |

| 1               | Enable EPT                               | If this control is 1, extended page tables (EPT) are enabled. See Section 27.2.                                                                                                                                            |

| 2               | Descriptor-table exiting                 | This control determines whether executions of LGDT, LIDT, LLDT, LTR, SGDT, SIDT, SLDT, and STR cause VM exits.                                                                                                             |

| 3               | Enable RDTSCP                            | If this control is 0, any execution of RDTSCP causes an invalid-opcode exception (#UD).                                                                                                                                    |

| 4               | Virtualize x2APIC mode                   | If this control is 1, the logical processor treats specially RDMSR and WRMSR to APIC MSRs (in the range 800H–8FFH). See Section 28.5.                                                                                      |

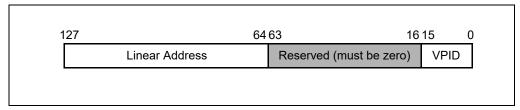

| 5               | Enable VPID                              | If this control is 1, cached translations of linear addresses are associated with a virtual-processor identifier (VPID). See Section 27.1.                                                                                 |

| 6               | WBINVD exiting                           | This control determines whether executions of WBINVD and WBNOINVD cause VM exits.                                                                                                                                          |

| 7               | Unrestricted guest                       | This control determines whether guest software may run in unpaged protected mode or in real-address mode.                                                                                                                  |

| 8               | APIC-register virtualization             | If this control is 1, the logical processor virtualizes certain APIC accesses. See Section 28.4 and Section 28.5.                                                                                                          |

| 9               | Virtual-interrupt<br>delivery            | This controls enables the evaluation and delivery of pending virtual interrupts as well as the emulation of writes to the APIC registers that control interrupt prioritization.                                            |

| 10              | PAUSE-loop exiting                       | This control determines whether a series of executions of PAUSE can cause a VM exit (see Section 23.6.13 and Section 24.1.3).                                                                                              |

| 11              | RDRAND exiting                           | This control determines whether executions of RDRAND cause VM exits.                                                                                                                                                       |

| 12              | Enable INVPCID                           | If this control is 0, any execution of INVPCID causes a #UD.                                                                                                                                                               |

| 13              | Enable<br>VM functions                   | Setting this control to 1 enables use of the VMFUNC instruction in VMX non-root operation. See Section 24.5.6.                                                                                                             |

| 14              | VMCS shadowing                           | If this control is 1, executions of VMREAD and VMWRITE in VMX non-root operation may access a shadow VMCS (instead of causing VM exits). See Section 23.10 and Section 29.3.                                               |

| 15              | Enable ENCLS exiting                     | If this control is 1, executions of ENCLS consult the ENCLS-exiting bitmap to determine whether the instruction causes a VM exit. See Section 23.6.16 and Section 24.1.3.                                                  |

| 16              | RDSEED exiting                           | This control determines whether executions of RDSEED cause VM exits.                                                                                                                                                       |

| 17              | Enable PML                               | If this control is 1, an access to a guest-physical address that sets an EPT dirty bit first adds an entry to the page-modification log. See Section 27.2.6.                                                               |

| 18              | EPT-violation #VE                        | If this control is 1, EPT violations may cause virtualization exceptions (#VE) instead of VM exits. See Section 24.5.7.                                                                                                    |

| 19              | Conceal VMX from<br>PT                   | If this control is 1, Intel Processor Trace suppresses from PIPs an indication that the processor was in VMX non-root operation and omits a VMCS packet from any PSB+ produced in VMX non-root operation (see Chapter 31). |

| 20              | Enable<br>XSAVES/XRSTORS                 | If this control is 0, any execution of XSAVES or XRSTORS causes a #UD.                                                                                                                                                     |

| 22              | Mode-based<br>execute control for<br>EPT | If this control is 1, EPT execute permissions are based on whether the linear address being accessed is supervisor mode or user mode. See Chapter 27.                                                                      |

| 23              | Sub-page write<br>permissions for<br>EPT | If this control is 1, EPT write permissions may be specified at the granularity of 128 bytes. See Section 27.2.4.                                                                                                          |

| Bit Position(s) | Name                                   | Description                                                                                                                                                                                                                                  |

|-----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24              | Intel PT uses guest physical addresses | If this control is 1, all output addresses used by Intel Processor Trace are treated as guest-<br>physical addresses and translated using EPT. See Section 24.5.4.                                                                           |

| 25              | Use TSC scaling                        | This control determines whether executions of RDTSC, executions of RDTSCP, and executions of RDMSR that read from the IA32_TIME_STAMP_COUNTER MSR return a value modified by the TSC multiplier field (see Section 23.6.5 and Section 24.3). |

| 26              | Enable user wait and pause             | If this control is 0, any execution of TPAUSE, UMONITOR, or UMWAIT causes a #UD.                                                                                                                                                             |

| 28              | Enable ENCLV exiting                   | If this control is 1, executions of ENCLV consult the ENCLV-exiting bitmap to determine whether the instruction causes a VM exit. See Section 23.6.17 and Section 24.1.3.                                                                    |

Table 23-7. Definitions of Secondary Processor-Based VM-Execution Controls (Contd.)

All other bits in this field are reserved to 0. Software should consult the VMX capability MSR IA32\_VMX\_PROCBASED\_CTLS2 (see Appendix A.3.3) to determine which bits may be set to 1. Failure to clear reserved bits causes subsequent VM entries to fail (see Section 25.2.1.1).

Table 23-8 lists the tertiary processor-based VM-execution controls. See Chapter 24 for more details of how these controls affect processor behavior in VMX non-root operation.

Table 23-8. Definitions of Tertiary Processor-Based VM-Execution Controls

| Bit Position(s) | Name              | Description                                                             |

|-----------------|-------------------|-------------------------------------------------------------------------|

| 0               | LOADIWKEY exiting | This control determines whether executions of LOADIWKEY cause VM exits. |

All other bits in this field are reserved to 0. Software should consult the VMX capability MSR IA32\_VMX\_PROCBASED\_CTLS3 (see Appendix A.3.4) to determine which bits may be set to 1. Failure to clear reserved bits causes subsequent VM entries to fail (see Section 25.2.1.1).

# 23.6.3 Exception Bitmap

The **exception bitmap** is a 32-bit field that contains one bit for each exception. When an exception occurs, its vector is used to select a bit in this field. If the bit is 1, the exception causes a VM exit. If the bit is 0, the exception is delivered normally through the IDT, using the descriptor corresponding to the exception's vector.

Whether a page fault (exception with vector 14) causes a VM exit is determined by bit 14 in the exception bitmap as well as the error code produced by the page fault and two 32-bit fields in the VMCS (the **page-fault error-code mask** and **page-fault error-code match**). See Section 24.2 for details.

# 23.6.4 I/O-Bitmap Addresses

The VM-execution control fields include the 64-bit physical addresses of **I/O bitmaps** A and B (each of which are 4 KBytes in size). I/O bitmap A contains one bit for each I/O port in the range 0000H through 7FFFH; I/O bitmap B contains bits for ports in the range 8000H through FFFFH.

A logical processor uses these bitmaps if and only if the "use I/O bitmaps" control is 1. If the bitmaps are used, execution of an I/O instruction causes a VM exit if any bit in the I/O bitmaps corresponding to a port it accesses is 1. See Section 24.1.3 for details. If the bitmaps are used, their addresses must be 4-KByte aligned.

# 23.6.5 Time-Stamp Counter Offset and Multiplier

The VM-execution control fields include a 64-bit **TSC-offset** field. If the "RDTSC exiting" control is 0 and the "use TSC offsetting" control is 1, this field controls executions of the RDTSC and RDTSCP instructions. It also controls executions of the RDMSR instruction that read from the IA32\_TIME\_STAMP\_COUNTER MSR. For all of these, the value of the TSC offset is added to the value of the time-stamp counter, and the sum is returned to guest software in EDX:EAX.