# **Prescott New Instructions Software Developer's Guide**

252490-004 January 2004

### **Revision History**

| .002 | Table 2-1: Revised function 4H and 8000006H.Section 2.1.2: Corrected extended family encoding display algorithm.Table 2.5: Revised for consistency.Figure 2.6: Added clarification.Section 4.3.1: Corrected LDDQU type usage. |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .003 | Included intrinsics.<br>Included opcodes.<br>Corrected comment in Example 4.1.                                                                                                                                                |

| .004 | Corrects errors and omissions in description of instructions. Adds some new information.<br>Provides encoding information (see Appendix A).                                                                                   |

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Improper use of reserved or undefined features or instructions may cause unpredictable behavior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from their unauthorized use.

The Intel<sup>®</sup> processors may contain design defects or errors known as errata. Current characterized errata are available on request.

Intel, Pentium, Intel Xeon, Intel Pentium III Xeon, Intel NetBurst, MMX, and Celeron, are trademarks or registered trademarks of Intel Corporation and its subsidiaries in the United States and other countries.

Prescott is a code name that is used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a Hyper-Threading Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call 1-800-548-4725 or visit Intel's website at http://www.intel.com Copyright © 2003-2004 Intel Corporation

### CONTENTS

| СНАРТЕ             |                                                                                    |

|--------------------|------------------------------------------------------------------------------------|

|                    | ENERATION INTEL® PROCESSOR OVERVIEW                                                |

| 1.1.               | KEY FEATURES         1-1           HYPER-THREADING TECHNOLOGY         1-1          |

| 1.2.<br>1.3.       | HYPER-THREADING TECHNOLOGY       1-1         ENHANCED CPUID CAPABILITIES       1-2 |

| 1.3.<br>1.4.       | PRESCOTT NEW INSTRUCTIONS                                                          |

| 1.4.1.             | One Instruction That Improves x87-FP Integer Conversion                            |

| 1.4.2.             | Three Instructions Enhance LOAD/MOVE/DUPLICATE Performance 1-3                     |

| 1.4.3.             | One Instruction Provides Specialized 128-bit Unaligned Data Load                   |

| 1.4.4.             | Two Instructions Provide Packed Addition/Subtraction1-4                            |

| 1.4.5.             | Four Instructions Provide Horizontal Addition/Subtraction                          |

| 1.4.6.             | Two Instructions Improve Synchronization Between Agents                            |

| СНАРТ              |                                                                                    |

|                    |                                                                                    |

| 2.1.               | VALUES RETURNED USING CPUID 2-1                                                    |

| CHAPTE             | ER 3<br>CTION SET REFERENCE                                                        |

| 3.1.               | INTERPRETING THE INSTRUCTION REFERENCE PAGES                                       |

| 3.2.               | PRESCOTT NEW INSTRUCTIONS                                                          |

| ·                  | ADDSUBPD: Packed Double-FP Add/Subtract                                            |

|                    | ADDSUBPS: Packed Single-FP Add/Subtract                                            |

|                    | FISTTP: Store Integer with Truncation                                              |

|                    | HADDPD: Packed Double-FP Horizontal Add                                            |

|                    | HADDPS: Packed Single-FP Horizontal Add                                            |

|                    | HSUBPD: Packed Double-FP Horizontal Subtract                                       |

|                    | HSUBPS: Packed Single-FP Horizontal Subtract                                       |

|                    | LDDQU: Load Unaligned Integer 128 bits                                             |

|                    | MONITOR: Setup Monitor Address                                                     |

|                    | MOVDDUP: Move One Double-FP and Duplicate                                          |

|                    | MOVSHDUP: Move Packed Single-FP High and Duplicate                                 |

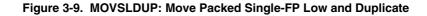

|                    | MOVSLDUP: Move Packed Single-FP Low and Duplicate                                  |

|                    | MWAIT: Monitor Wait                                                                |

| СНАРТИ             | ER 4                                                                               |

|                    | I AND APPLICATION PROGRAMMING GUIDELINES                                           |

| 4.1.               | SYSTEM PROGRAMMING MODEL AND REQUIREMENTS 4-1                                      |

| 4.1.1.             | Enabling Support in a System Executive                                             |

| 4.1.2.             | FXSAVE/FXRSTOR Replaces Use of FSAVE/FRSTOR4-1                                     |

| 4.1.3.<br>4.1.4.   | Initialization                                                                     |

| 4.1.4.<br>4.1.4.1. | Exception Handler                                                                  |

| 4.1.4.1.           | Numeric Error flag and IGNNE#                                                      |

| 4.1.4.2.           | Technology Emulation                                                               |

| 4.1.5.             | Detecting Availability of MONITOR/MWAIT                                            |

| 4.2.               | APPLICATION PROGRAMMING MODEL. 4-2                                                 |

|                    |                                                                                    |

| 4.2.1.   | Detecting PNI Extensions Using CPUID             | .4-3 |

|----------|--------------------------------------------------|------|

| 4.2.2.   | Detecting Support for MONITOR/MWAIT Instructions |      |

| 4.3.     | GUIDELINES FOR PNI EXTENSIONS                    |      |

| 4.3.1.   | Guideline for Data Movement Instructions         | .4-4 |

| 4.3.2.   | Guideline for Packed ADDSUBxx Instructions       | .4-4 |

| 4.3.3.   | Guideline for FISTTP                             | .4-5 |

| 4.3.4.   | Guideline for Unaligned 128-bit Load             | .4-6 |

| 4.3.5.   | Guideline for Horizontal Add/Subtract            | .4-7 |

| 4.3.6.   | Guideline for MONITOR/MWAIT                      |      |

| 4.3.6.1. | MONITOR/MWAIT Address Range Determination.       | .4-8 |

| 4.3.6.2. | Waking-up From MWAIT                             |      |

| APPEN    |                                                  |      |

| A.1.     | INSTRUCTION SUMMARY                              | A-1  |

| A.1.1.   | PNI Formats and Encodings Table                  | A-2  |

### **FIGURES**

| FIGURES     |                                                             |

|-------------|-------------------------------------------------------------|

| Figure 1-1. | Two Logical Processors in One Physical Package              |

| Figure 2-1. | Version Information Returned by CPUID in EAX                |

| Figure 2-2. | Extended Feature Information Returned in the ECX Register   |

| Figure 2-3. | Feature Information Returned in the EDX Register            |

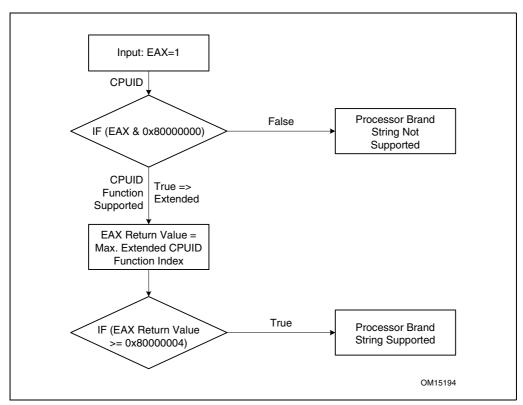

| Figure 2-4. | Determination of Support for the Processor Brand String2-15 |

| Figure 2-5. | Algorithm for Extracting Maximum Processor Frequency        |

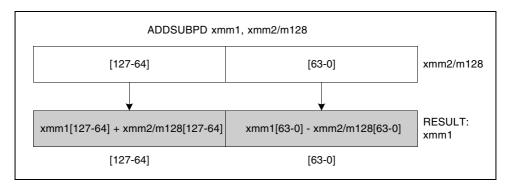

| Figure 3-1. | ADDSUBPD: Packed Double-FP Add/Subtract                     |

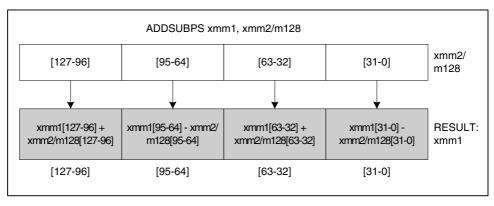

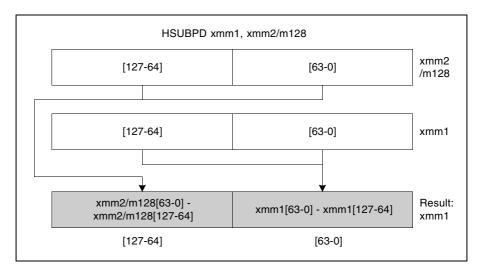

| Figure 3-2. | ADDSUBPS: Packed Single-FP Add/Subtract                     |

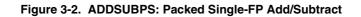

| Figure 3-3. | HADDPD: Packed Double-FP Horizontal Add                     |

| Figure 3-4. | HADDPS: Packed Single-FP Horizontal Add                     |

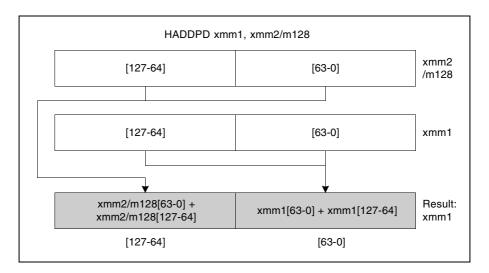

| Figure 3-5. | HSUBPD: Packed Double-FP Horizontal Subtract                |

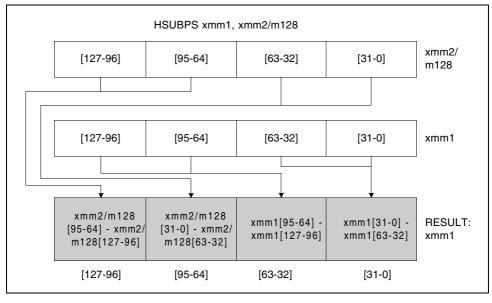

| Figure 3-6. | HSUBPS: Packed Single-FP Horizontal Subtract                |

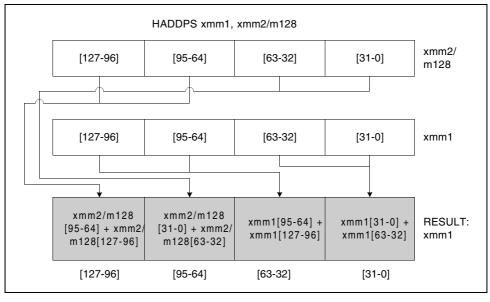

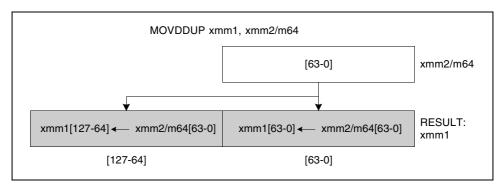

| Figure 3-7. | MOVDDUP: Move One Double-FP and Duplicate                   |

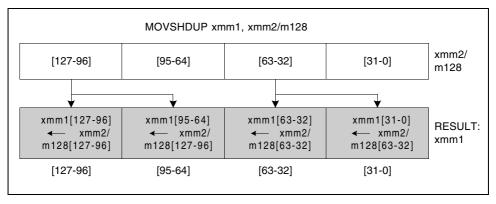

| Figure 3-8. | MOVSHDUP: Move Packed Single-FP High and Duplicate          |

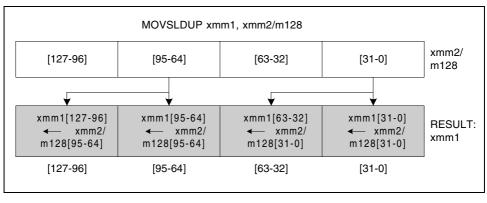

| Figure 3-9. | MOVSLDUP: Move Packed Single-FP Low and Duplicate           |

### TABLES

| TABLES     |                                                                       |   |

|------------|-----------------------------------------------------------------------|---|

| Table 2-1. | Information Returned by CPUID Instruction2-                           | 1 |

| Table 2-2. | Highest CPUID Source Operand for IA-32 Processors2-4                  | 4 |

| Table 2-3. | Processor Type Field                                                  | 5 |

| Table 2-4. | More on Extended Feature Information Returned in the ECX Register 2-7 | 7 |

| Table 2-5. | More on Feature Information Returned in the EDX Register              | 9 |

| Table 2-6. | Encoding of Cache and TLB Descriptors                                 | 2 |

| Table 2-7. | Processor Brand String Returned with Pentium 4 Processor              | 6 |

| Table 2-8. | Mapping of Brand Indices and IA-32 Processor Brand Strings2-18        | 8 |

| Table A-1. | x87 FPU and SIMD Floating-point Exceptions A-                         | 1 |

| Table A-2. | PNI Instruction Set Summary A-                                        |   |

| Table A-3. | PNI Formats and Encodings of PNI Floating-Point Instructions          | 3 |

| Table A-4. | Formats and Encodings for PNI Event Management Instructions A-3       | 3 |

| Table A-5. | Formats and Encodings for PNI Integer and Move Instructions           | 4 |

|            |                                                                       |   |

### CHAPTER 1 NEXT GENERATION INTEL<sup>®</sup> PROCESSOR OVERVIEW

### 1.1. KEY FEATURES

Prescott is the code name for a new generation of IA32 processors. The technology incorporates an enhanced Intel<sup>®</sup> NetBurst<sup>®</sup> microarchitecture. Other features include:

- Support for Hyper-Threading (HT) Technology<sup>1</sup>

- Prescott New Instructions (PNI)

- Deeper pipelining to enable higher frequency

- A High-speed System Bus

Prescott improves on the Pentium<sup>®</sup> 4 processor's hyper-pipelined technology to achieve even higher clock rates than previous generations of Pentium 4 processors. At the same time, the new processor has larger first-level and second-level caches, more store buffers, write-combining buffers.

Support for PNI does not require new OS support for saving and restoring the new state during a context switch, beyond that provided for Streaming SIMD Extensions. The instruction set is compatible with all software written for Intel<sup>®</sup> architecture microprocessors.

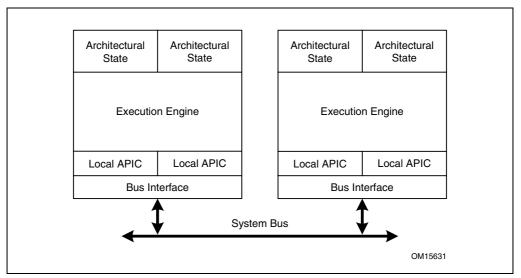

### 1.2. HYPER-THREADING TECHNOLOGY

Hyper-Threading Technology (HT Technology) makes a single physical processor appear as multiple logical processors by running two threads simultaneously. This is accomplished by duplicating the architecture state for each logical processor in the physical processor and sharing the physical execution resources within a physical processor package between the logical processors. Each logical processor maintains a complete architecture state (see Figure 1-1).

From a software or architecture perspective, this means operating systems and user programs can schedule processes or threads to logical processors as they would on conventional physical processors. From a microarchitectural perspective, this means that instructions from both logical processors will persist and execute simultaneously on shared execution resources.

<sup>1.</sup> Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a Hyper-Threading Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

HT Technology is available across the server, workstation and desktop segments in the IA-32 processor family. Software detects support for HT Technology in IA-32 processors by using the CPUID instruction. All HT Technology configurations require a chipset and BIOS that utilize the technology, and an operating system that includes optimizations for HT Technology. See *www.intel.com/info/hyperthreading* for more information.

Figure 1-1. Two Logical Processors in One Physical Package

A system with processors that are HT Technology capable appear to the operating system and application software as having twice the number of processors as the number of physical processors. Operating systems manage logical processors as they do physical processors, scheduling run-able tasks or threads to logical processors.

Processors supporting HT Technology deliver higher performance than a comparable physical processor that do not support HT technology. However, HT Technology does not deliver the same performance as a multiprocessor system with two physical processors.

### 1.3. ENHANCED CPUID CAPABILITIES

The CPUID instruction has been enhanced to support the following new features:

- PNI, including MONITOR-MWAIT support

- Debug Trace Store Qualification

- Enhanced Intel<sup>®</sup> SpeedStep<sup>®</sup> technology (uses model-specific registers on the processor)

The behavior of the CPUID instruction has not changed (although more values are returned). The instruction provides a wealth of information that are organized into pages or leaves; leaves are queried by loading different values in EAX and then executing the instruction.

For detailed information, see Chapter 2, CPUID Extensions.

### 1.4. PRESCOTT NEW INSTRUCTIONS

PNI consists of 13 new instructions that accelerate performance of Streaming SIMD Extensions technology, Streaming SIMD Extensions 2 technology, and x87-FP math capabilities. The new technology is compatible with existing software written for Intel architecture microprocessors and existing software should continue to run correctly, without modification, on microprocessors that incorporate these extensions.

The new instructions are summarized in the following sections.

### 1.4.1. One Instruction That Improves x87-FP Integer Conversion

FISTTP (Store Integer and Pop from x87-FP with Truncation) behaves like the FISTP instruction but uses truncation, irrespective of the rounding mode specified in the floating-point control word (FCW). The instruction converts the top of stack (ST0) to integer with rounding to truncate and pop the stack.

FISTTP is available in three precisions: short integer (word or 16-bit), integer (double word or 32-bit), and long integer (64-bit). With FISTTP, applications no longer need to change the FCW when truncation is desired. This instruction is the only x87-FP instruction in PNI.

# 1.4.2. Three Instructions Enhance LOAD/MOVE/DUPLICATE Performance

MOVSHDUP loads/moves 128-bits, duplicating the second and fourth 32-bit data elements.

- MOVSHDUP OperandA OperandB

- OperandA (128 bits, four data elements):  $3_a$ ,  $2_a$ ,  $1_a$ ,  $0_a$

- OperandB (128 bits, four data elements): 3<sub>b</sub>, 2<sub>b</sub>, 1<sub>b</sub>, 0<sub>b</sub>

- Result (stored in OperandA): 3<sub>b</sub>, 3<sub>b</sub>, 1<sub>b</sub>, 1<sub>b</sub>

MOVSLDUP loads/moves 128-bits, duplicating the first and third 32-bit data elements.

- MOVSLDUP OperandA OperandB

- OperandA (128 bits, four data elements): 3<sub>a</sub>, 2<sub>a</sub>, 1<sub>a</sub>, 0<sub>a</sub>

- OperandB (128 bits, four data elements): 3<sub>b</sub>, 2<sub>b</sub>, 1<sub>b</sub>, 0<sub>b</sub>

- Result (stored in OperandA):  $2_b$ ,  $2_b$ ,  $0_b$ ,  $0_b$

MOVDDUP loads/moves 64-bits (bits[63-0] if the source is a register) and returns the same 64 bits in both the lower and upper halves of the 128-bit result register. This duplicates the 64 bits from the source.

- MOVDDUP OperandA OperandB

- OperandA (128 bits, two data elements):  $1_a$ ,  $0_a$

- OperandB (64 bits, one data element): 0<sub>b</sub>

- Result (stored in OperandA): 0<sub>b</sub>, 0<sub>b</sub>

### 1.4.3. One Instruction Provides Specialized 128-bit Unaligned Data Load

LDDQU is a special 128-bit unaligned load designed to avoid cache line splits. If the address of the load is aligned on a 16-byte boundary, LDQQU loads the 16 bytes requested. If the address of the load is not aligned on a 16-byte boundary, LDDQU loads a 32-byte block starting at the 16-byte aligned address immediately below the load request. It then extracts the requested 16 bytes.

The instruction provides significant performance improvement on 128-bit unaligned memory accesses at the cost of some usage model restrictions.

### 1.4.4. Two Instructions Provide Packed Addition/Subtraction

ADDSUBPS has two 128-bit operands. The instruction performs single-precision addition on the second and fourth pairs of 32-bit data elements within the operands; and single-precision subtraction on the first and third pairs. This instruction is effective at evaluating complex products on packed single-precision data.

- ADDSUBPS OperandA OperandB

- OperandA (128 bits, four data elements):  $3_a$ ,  $2_a$ ,  $1_a$ ,  $0_a$

- OperandB (128 bits, four data elements): 3<sub>b</sub>, 2<sub>b</sub>, 1<sub>b</sub>, 0<sub>b</sub>

- Result (stored in OperandA):  $3_a+3_b$ ,  $2_a-2_b$ ,  $1_a+1_b$ ,  $0_a-0_b$

ADDSUBPD has two 128-bit operands. The instruction performs double-precision addition on the second pair of quadwords, and double-precision subtraction on the first pair. This instruction is useful when evaluating complex products on packed double-precision data.

- ADDSUBPD OperandA OperandB

- OperandA (128 bits, two data elements):  $1_a, 0_a$

- OperandB (128 bits, two data elements): 1<sub>b</sub>, 0<sub>b</sub>

- Result (stored in OperandA): 1<sub>a</sub>+1<sub>b</sub>, 0<sub>a</sub>-0<sub>b</sub>

### 1.4.5. Four Instructions Provide Horizontal Addition/Subtraction

Most SIMD instructions operate vertically. This means that the result in position i of the result is a function of the elements in position i of both operands. Horizontal addition/subtraction operates horizontally. This means that contiguous data elements from the same operand are used to produce a result data element.

HADDPS performs a single-precision addition on contiguous data elements. The first data element of the result is obtained by adding the first and second elements of the first operand; the second element by adding the third and fourth elements of the first operand; the third by adding the first and second elements of the second operand; and the fourth by adding the third and fourth elements of the second operand.

- HADDPS OperandA OperandB

- OperandA (128 bits, four data elements):  $3_a$ ,  $2_a$ ,  $1_a$ ,  $0_a$

- OperandB (128 bits, four data elements): 3<sub>b</sub>, 2<sub>b</sub>, 1<sub>b</sub>, 0<sub>b</sub>

- Result (Stored in OperandA):  $3_b+2_b$ ,  $1_b+0_b$ ,  $3_a+2_a$ ,  $1_a+0_a$

HSUBPS performs a single-precision subtraction on contiguous data elements. The first data element of the result is obtained by subtracting the second element of the first operand from the first element of the first operand; the second element by subtracting the fourth element of the first operand from the third element of the first operand; the third by subtracting the second element of the second element of the second operand from the first element of the second operand; and the fourth by subtracting the fourth element of the second operand.

- HSUBPS OperandA OperandB

- OperandA (128 bits, four data elements):  $3_a$ ,  $2_a$ ,  $1_a$ ,  $0_a$

- OperandB (128 bits, four data elements):  $3_b$ ,  $2_b$ ,  $1_b$ ,  $0_b$

- Result (Stored in OperandA):  $2_b-3_b$ ,  $0_b-1_b$ ,  $2_a-3_a$ ,  $0_a-1_a$

HADDPD performs a double-precision addition on contiguous data elements. The first data element of the result is obtained by adding the first and second elements of the first operand; the second element by adding the first and second elements of the second operand.

- HADDPD OperandA OperandB

- OperandA (128 bits, two data elements):  $1_a$ ,  $0_a$

- OperandB (128 bits, two data elements): 1<sub>b</sub>, 0<sub>b</sub>

- Result (Stored in OperandA):  $1_b + 0_b$ ,  $1_a + 0_a$

HSUBPD performs a double-precision subtraction on contiguous data elements. The first data element of the result is obtained by subtracting the second element of the first operand from the first element of the first operand; the second element by subtracting the second element of the second element of the second operand from the first element of the second operand.

- HSUBPD OperandA OperandB

- OperandA (128 bits, two data elements): 1<sub>a</sub>, 0<sub>a</sub>

- OperandB (128 bits, two data elements): 1<sub>b</sub>, 0<sub>b</sub>

- Result (Stored in OperandA):  $0_b 1_b, 0_a 1_a$

## 1.4.6. Two Instructions Improve Synchronization Between Agents

MONITOR sets up an address range used to monitor write-back stores.

MWAIT enables a logical processor to enter into an optimized state while waiting for a writeback store to the address range set up by the MONITOR instruction.

Support for MONITOR/MWAIT is indicated by the CPUID MONITOR/MWAIT Software need not check for support of SSE in order to use the MONITOR/MWAIT.

### CHAPTER 2 CPUID EXTENSIONS

### 2.1. VALUES RETURNED USING CPUID

CPUID instruction and feature-identification bits have been added for software to identify the features offered by Prescott New Instructions. Table 2-1 shows the value in EAX before a call to CPUID and the value returned.

For impacted areas, note the bold type.

| Initial EAX<br>Value | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      | Basic CPUID Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| OH                   | EAX Maximum Input Value for Basic CPUID Information (see Table 2-2)<br>EBX "Genu"<br>ECX "ntel"<br>EDX "inel"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 01H                  | <ul> <li>EAX Version Information: Type, Family, Model, and Stepping ID (see Figure 2-1)</li> <li>EBX Bits 7-0: Brand Index<br/>Bits 7-0: Brand Index<br/>Bits 15-8: CLFLUSH line size (Value * 8 = cache line size in bytes)<br/>Bits 23-16: Number of logical processors per physical processor; two for<br/>the Pentium 4 processor supporting Hyper-Threading Technology<br/>Bits 31-24: Local APIC ID</li> <li>ECX Extended Feature Information (see Figure 2-2 and Table 2-4)<br/>Feature Information (see Figure 2-3 and Table 2-5)</li> </ul>                                                                                                                                                                |  |  |  |  |

| 02H                  | EAXCache and TLB Information (see Table 2-6)EBXCache and TLB InformationECXCache and TLB InformationEDXCache and TLB Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 03H                  | <ul> <li>EAX Reserved.</li> <li>EBX Reserved.</li> <li>ECX Bits 00-31 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)</li> <li>EDX Bits 32-63 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the value in this register is reserved.)</li> <li>NOTE: Processor serial number (PSN) is not supported in the Pentium 4 processor or later. On all models, use the PSN flag (returned using CPUID) to check for PSN support before accessing the feature. See AP-485, Intel Processor Identification and the CPUID Instruction (Order Number 241618) for more information on PSN.</li> </ul> |  |  |  |  |

#### Table 2-1. Information Returned by CPUID Instruction

| Id                   |                          | Information Returned by CPUID Instruction (Contd.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initial EAX<br>Value |                          | Information Provided about the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 04H                  | EAX<br>EBX<br>ECX        | Deterministic Cache Parameters Leaf<br>Bits 4-0: Cache Type**<br>Bits 7-5: Cache Level (starts at 1)<br>Bits 8: Self Initializing cache level (does not need SW initialization)<br>Bits 9: Fully Associative cache<br>Bits 13-10: Reserved<br>Bits 25-14: Number of threads sharing this cache*<br>Bits 31-26: Number of processor cores on this die (Multicore)*<br>Bits 11-00: L = System Coherency Line Size*<br>Bits 21-12: P = Physical Line partitions*<br>Bits 31-22: W = Ways of associativity*<br>Bits 31-00: S = Number of Sets* |

|                      | EDX                      | Reserved = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      |                          | *Add one to the value in the register file to get the number. For<br>example, the number of processor cores is EAX[31:26]+1.<br>** Cache Types fields<br>0 = Null - No more caches<br>1 = Data Cache<br>2 = Instruction Cache<br>3 = Unified Cache<br>4-31 = Reserved                                                                                                                                                                                                                                                                      |

|                      |                          | NOTE: CPUID leaves > 3 < 80000000 are only visible when<br>IA32_CR_MISC_ENABLES.BOOT_NT4 (bit 22) is clear (Default)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5H                   | EAX<br>EBX               | MONITOR/MWAIT Leaf<br>Bits 15-00: Smallest monitor-line size in bytes (default is processor's<br>monitor granularity)<br>Bits 31-16: Reserved = 0<br>Bits 15-00: Largest monitor-line size in bytes (default is processor's                                                                                                                                                                                                                                                                                                                |

|                      |                          | monitor granularity)<br>Bits 31-16: Reserved = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      | ECX<br>EDX               | Reserved = 0<br>Reserved = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      |                          | Extended Function CPUID Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 80000000H            | EAX<br>EBX<br>ECX<br>EDX | Maximum Input Value for Extended Function CPUID Information (see<br>Table 2-2).<br>Reserved<br>Reserved<br>Reserved<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                            |

| 80000001H            | EAX<br>EBX<br>ECX<br>EDX | Extended Processor Signature and Extended Feature Bits. (Currently<br>Reserved<br>Reserved<br>Reserved<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 2-1. Information Returned by CPUID Instruction (Contd.)

| Initial EAX<br>Value | Information Provided about the Processor                                                                                                                                                                         |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8000002H             | EAX       Processor Brand String         EBX       Processor Brand String Continued         ECX       Processor Brand String Continued         EDX       Processor Brand String Continued                        |

| 8000003H             | EAXProcessor Brand String ContinuedEBXProcessor Brand String ContinuedECXProcessor Brand String ContinuedEDXProcessor Brand String Continued                                                                     |

| 8000004H             | EAX       Processor Brand String Continued         EBX       Processor Brand String Continued         ECX       Processor Brand String Continued         EDX       Processor Brand String Continued              |

| 8000005H             | EAXReserved = 0EBXReserved = 0ECXReserved = 0EDXReserved = 0                                                                                                                                                     |

| 8000006H             | EAX       Reserved = 0         EBX       Reserved = 0         ECX       Bits 0-7: Cache Line Size         Bits 15-12: L2 Associativity         Bits 31-16: Cache size in 1K units         EDX       Reserved = 0 |

| 8000007H             | EAXReserved = 0EBXReserved = 0ECXReserved = 0EDXReserved = 0                                                                                                                                                     |

| 8000008H             | EAXReserved = 0EBXReserved = 0ECXReserved = 0EDXReserved = 0                                                                                                                                                     |

#### Table 2-1. Information Returned by CPUID Instruction (Contd.)

### INPUT EAX = 0: Returns CPUID's Highest Value for Basic Processor Information and the Vendor Identification String

When CPUID executes with EAX set to 0, the processor returns the highest value the CPUID recognizes for returning basic processor information. The value is returned in the EAX register (see Table 2-2) and is processor specific.

A vendor identification string is also returned in EBX, EDX, and ECX. For Intel processors, the string is "GenuineIntel" and is expressed:

EBX  $\leftarrow$  756e6547h (\* "Genu", with G in the low nibble of BL \*) EDX  $\leftarrow$  49656e69h (\* "ineI", with i in the low nibble of DL \*) ECX  $\leftarrow$  6c65746eh (\* "ntel", with n in the low nibble of CL \*)

### IINPUT EAX = 80000000H: Returns CPUID's Highest Value for Extended Processor Information

When CPUID executes with EAX set to 0, the processor returns the highest value the processor recognizes for returning extended processor information. The value is returned in the EAX register (see Table 2-2) and is processor specific.

|                                                                                     | Highest Value in EAX  |                               |  |  |

|-------------------------------------------------------------------------------------|-----------------------|-------------------------------|--|--|

| IA-32 Processors                                                                    | Basic Information     | Extended Function Information |  |  |

| Earlier Intel486 Processors                                                         | CPUID Not Implemented | CPUID Not Implemented         |  |  |

| Later Intel486 Processors and<br>Pentium Processors                                 | 01H                   | Not Implemented               |  |  |

| Pentium Pro and Pentium II<br>Processors, Intel <sup>®</sup> Celeron™<br>Processors | 02H                   | Not Implemented               |  |  |

| Pentium III Processors                                                              | 03H                   | Not Implemented               |  |  |

| Pentium 4 Processors                                                                | 02H                   | 8000004H                      |  |  |

| Intel Xeon Processors                                                               | 02H                   | 8000004H                      |  |  |

| Pentium M Processor                                                                 | 02H                   | 8000004H                      |  |  |

| Pentium 4 Processor supporting<br>Hyper-Threading Technology                        | 05H                   | 8000008H                      |  |  |

Table 2-2. Highest CPUID Source Operand for IA-32 Processors

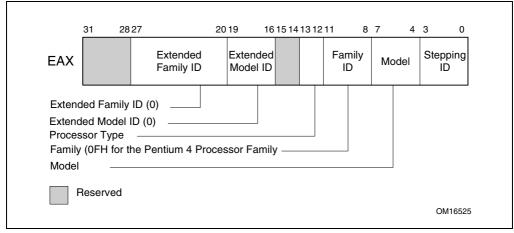

#### INPUT EAX = 1: Returns Model, Family and Stepping Information

When CPUID executes with EAX set to 1, version information is returned in EAX (see Figure 2-1). For example: model, family, and processor type for the first processor in the Intel Pentium 4 family is returned as follows:

- Model—0000B

- Family—1111B

- Processor Type—00B

See Table 2-3 for available processor type values. Stepping IDs are provided as needed.

#### **CPUID EXTENSIONS**

### intel

Figure 2-1. Version Information Returned by CPUID in EAX

#### Table 2-3. Processor Type Field

| Туре                                                   | Encoding |

|--------------------------------------------------------|----------|

| Original OEM Processor                                 | 00B      |

| Intel <sup>®</sup> OverDrive <sup>®</sup> Processor    | 01B      |

| Dual processor (not applicable to Intel486 processors) | 10B      |

| Intel reserved.                                        | 11B      |

#### NOTE

See AP-485, *Intel Processor Identification and the CPUID Instruction* (Order Number 241618) and Chapter 13 in the *IA-32 Intel Architecture Software Developer's Manual, Volume 1*, for information on identifying earlier IA-32 processors.

The Extended Family ID and Extended Model ID need be examined only if the Family ID reaches 0FH. Always display processor information as a combination of family, model and stepping.

Integrate the ID fields into a display as:

```

Displayed family = ((Extended Family ID(4-bits) << 4)) (8-bits)

+ Family ID (4-bits zero extended to 8-bits)</pre>

```

Compute the displayed model from the Model ID and the Extended Model ID as:

```

Displayed Model = ((Extended Model ID (4-bits) << 4))(8-bits)

+ Model (4-bits zero extended to 8-bits)</pre>

```

#### INPUT EAX = 1: Returns Additional Information in EBX

When CPUID executes with EAX set to 1, additional information is returned to the EBX register:

- Brand index (low byte of EBX) this number provides an entry into a brand string table that contains brand strings for IA-32 processors. More information about this field is provided later in this section.

- CLFLUSH instruction cache line size (second byte of EBX) this number indicates the size of the cache line flushed with CLFLUSH instruction in 8-byte increments. This field was introduced in the Pentium 4 processor.

- Local APIC ID (high byte of EBX) this number is the 8-bit ID that is assigned to the local APIC on the processor during power up. This field was introduced in the Pentium 4 processor.

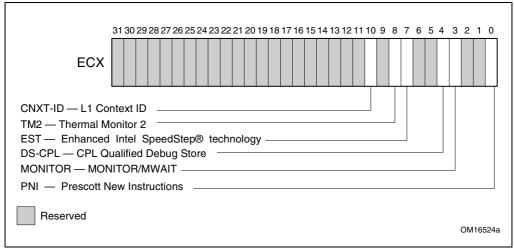

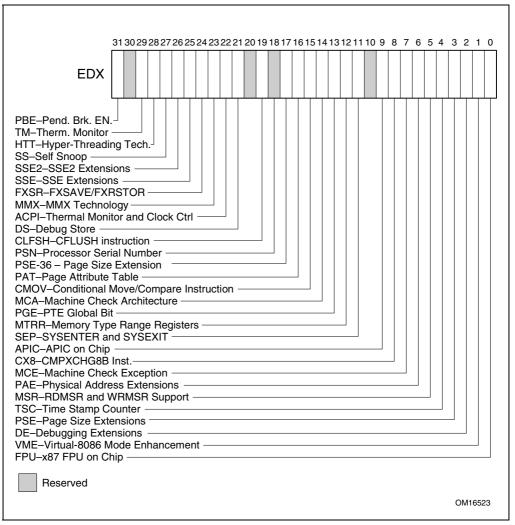

#### **INPUT EAX = 1: Returns Feature Information in ECX and EDX**

When CPUID executes with EAX set to 1, feature information is returned in ECX and EDX.

- Figure 2-2 and Table 2-4 show encodings for ECX.

- Figure 2-3 and Table 2-5 show encodings for EDX.

For all feature flags, a 1 indicates that the feature is supported. Use Intel to properly interpret feature flags.

#### NOTE

Software must confirm that a processor feature is present using feature flags returned by CPUID prior to using the feature. Software should not depend on future offerings retaining all features.

#### **CPUID EXTENSIONS**

## intel

Figure 2-2. Extended Feature Information Returned in the ECX Register

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                       |  |  |  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | PNI      | Prescott New Instructions (PNI). A value of 1 indicates the processor<br>supports this technology.                                                                                                                                                                |  |  |  |

| 3     | MONITOR  | MONITOR/MWAIT. A value of 1 indicates the processor supports this feature.                                                                                                                                                                                        |  |  |  |

| 4     | DS-CPL   | <b>CPL Qualified Debug Store</b> . A value of 1 indicates the processor supports the extensions to the Debug Store feature to allow for branch message storage qualified by CPL.                                                                                  |  |  |  |

| 7     | EST      | Enhanced Intel SpeedStep technology. A value of 1 indicates that the processor supports this technology.                                                                                                                                                          |  |  |  |

| 8     | TM2      | <b>Thermal Monitor 2</b> . A value of 1 indicates whether the processor supports this technology.                                                                                                                                                                 |  |  |  |

| 10    | CNXT-ID  | L1 Context ID. A value of 1 indicates the L1 data cache mode can be set to either adaptive mode or shared mode. A value of 0 indicates this feature is not supported. See definition of the IA32_MISC_ENABLE MSR Bit 24 (L1 Data Cache Context Mode) for details. |  |  |  |

| Table 2-4 | More on Ex | tended Feature  | Information | Returned in t | he ECX Register   |

|-----------|------------|-----------------|-------------|---------------|-------------------|

|           |            | tenueu i cature |             | neturneu mit  | The LOA Tregister |

Into

Figure 2-3. Feature Information Returned in the EDX Register

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | FPU      | Floating Point Unit On-Chip. The processor contains an x87 FPU.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 1     | VME      | Virtual 8086 Mode Enhancements. Virtual 8086 mode enhancements, including CR4.VME for controlling the feature, CR4.PVI for protected mode virtual interrupts, software interrupt indirection, expansion of the TSS with the software indirection bitmap, and EFLAGS.VIF and EFLAGS.VIP flags.                                                                                                                                                     |  |

| 2     | DE       | <b>Debugging Extensions.</b> Support for I/O breakpoints, including CR4.DE for controlling the feature, and optional trapping of accesses to DR4 and DR5.                                                                                                                                                                                                                                                                                         |  |

| 3     | PSE      | <b>Page Size Extension.</b> Large pages of size 4Mbyte are supported, including CR4.PSE for controlling the feature, the defined dirty bit in PDE (Page Directory Entries), optional reserved bit trapping in CR3, PDEs, and PTEs.                                                                                                                                                                                                                |  |

| 4     | TSC      | Time Stamp Counter. The RDTSC instruction is supported, including CR4.TSD for controlling privilege.                                                                                                                                                                                                                                                                                                                                              |  |

| 5     | MSR      | <b>Model Specific Registers RDMSR and WRMSR Instructions.</b> The RDMSR and WRMSR instructions are supported. Some of the MSRs are implementation dependent.                                                                                                                                                                                                                                                                                      |  |

| 6     | PAE      | <b>Physical Address Extension.</b> Physical addresses greater than 32 bits are supported: extended page table entry formats, an extra level in the page translation tables is defined, 2 Mbyte pages are supported instead of 4 Mbyte pages if PAE bit is 1. The actual number of address bits beyond 32 is not defined, and is implementation specific.                                                                                          |  |

| 7     | MCE      | <b>Machine Check Exception</b> . Exception 18 is defined for Machine Checks, including CR4.MCE for controlling the feature. This feature does not define the model-specific implementations of machine-check error logging, reporting, and processor shutdowns. Machine Check exception handlers may have to depend on processor version to do model specific processing of the exception, or test for the presence of the Machine Check feature. |  |

| 8     | CX8      | <b>CMPXCHG8B Instruction.</b> The compare-and-exchange 8 bytes (64 bits) instruction is supported (implicitly locked and atomic).                                                                                                                                                                                                                                                                                                                 |  |

| 9     | APIC     | <b>APIC On-Chip.</b> The processor contains an Advanced Programmable Interrupt Controller (APIC), responding to memory mapped commands in the physical address range FFFE0000H to FFFE0FFFH (by default - some processors permit the APIC to be relocated).                                                                                                                                                                                       |  |

| 10    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 11    | SEP      | SYSENTER and SYSEXIT Instructions. The SYSENTER and SYSEXIT and associated MSRs are supported.                                                                                                                                                                                                                                                                                                                                                    |  |

| 12    | MTRR     | <b>Memory Type Range Registers.</b> MTRRs are supported. The MTRRcap MSR contains feature bits that describe what memory types are supported, how many variable MTRRs are supported, and whether fixed MTRRs are supported.                                                                                                                                                                                                                       |  |

| 13    | PGE      | <b>PTE Global Bit.</b> The global bit in page directory entries (PDEs) and page table entries (PTEs) is supported, indicating TLB entries that are common to different processes and need not be flushed. The CR4.PGE bit controls this feature.                                                                                                                                                                                                  |  |

| Table 2-5. More on Feature Information Returned in the EDX Registe |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                             |  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 14    | MCA      | <b>Machine Check Architecture.</b> The Machine Check Architecture, which provides a compatible mechanism for error reporting in P6 family, Pentium 4, and Intel Xeon processors, and future processors, is supported. The MCG_CAP MSR contains feature bits describing how many banks of error reporting MSRs are supported.                                            |  |

| 15    | CMOV     | <b>Conditional Move Instructions.</b> The conditional move instruction CMOV is supported. In addition, if x87 FPU is present as indicated by the CPUID.FPU feature bit, then the FCOMI and FCMOV instructions are supported                                                                                                                                             |  |

| 16    | PAT      | <b>Page Attribute Table.</b> Page Attribute Table is supported. This feature augments the Memory Type Range Registers (MTRRs), allowing an operating system to specify attributes of memory on a 4K granularity through a linear address.                                                                                                                               |  |

| 17    | PSE-36   | <b>36-Bit Page Size Extension.</b> Extended 4-MByte pages that are capable of addressing physical memory beyond 4 GBytes are supported. This feature indicates that the upper four bits of the physical address of the 4-MByte page is encoded by bits 13-16 of the page directory entry.                                                                               |  |

| 18    | PSN      | <b>Processor Serial Number.</b> The processor supports the 96-bit processor identification number feature and the feature is enabled.                                                                                                                                                                                                                                   |  |

| 19    | CLFSH    | CLFLUSH Instruction. CLFLUSH Instruction is supported.                                                                                                                                                                                                                                                                                                                  |  |

| 20    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                |  |

| 21    | DS       | <b>Debug Store.</b> The processor supports the ability to write debug information into a memory resident buffer. This feature is used by the branch trace store (BTS) and precise event-based sampling (PEBS) facilities (see Chapter 15, <i>Debugging and Performance Monitoring</i> , in the <i>IA-32 Intel Architecture Software Developer's Manual, Volume 3</i> ). |  |

| 22    | ACPI     | Thermal Monitor and Software Controlled Clock Facilities. The processor implements internal MSRs that allow processor temperature to be monitored and processor performance to be modulated in predefined duty cycles under software control.                                                                                                                           |  |

| 23    | MMX      | Intel MMX Technology. The processor supports the Intel MMX technology.                                                                                                                                                                                                                                                                                                  |  |

| 24    | FXSR     | <b>FXSAVE and FXRSTOR Instructions.</b> The FXSAVE and FXRSTOR instructions are supported for fast save and restore of the floating point context. Presence of this bit also indicates that CR4.OSFXSR is available for an operating system to indicate that it supports the FXSAVE and FXRSTOR instructions                                                            |  |

| 25    | SSE      | SSE. The processor supports the SSE extensions.                                                                                                                                                                                                                                                                                                                         |  |

| 26    | SSE2     | SSE2. The processor supports the SSE2 extensions.                                                                                                                                                                                                                                                                                                                       |  |

| 27    | SS       | <b>Self Snoop.</b> The processor supports the management of conflicting memory types by performing a snoop of its own cache structure for transactions issued to the bus                                                                                                                                                                                                |  |

#### Table 2-5. More on Feature Information Returned in the EDX Register (Contd.)

| Bit # | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                           |  |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 28    | HTT      | Hyper-Threading Technology. The processor supports Hyper-Threading Technology.                                                                                                                                                                                                                                                                                        |  |

| 29    | ТМ       | <b>Thermal Monitor.</b> The processor implements the thermal monitor automatic hermal control circuitry (TCC).                                                                                                                                                                                                                                                        |  |

| 30    | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                              |  |

| 31    | PBE      | <b>Pending Break Enable.</b> The processor supports the use of the FERR#/PBE# pin when the processor is in the stop-clock state (STPCLK# is asserted) to signal the processor that an interrupt is pending and that the processor should return to normal operation to handle the interrupt. Bit 10 (PBE enable) in the IA32_MISC_ENABLE MSR enables this capability. |  |

#### Table 2-5. More on Feature Information Returned in the EDX Register (Contd.)

#### INPUT EAX = 2: Cache and TLB Information Returned in EAX, EBX, ECX, EDX

When CPUID executes with EAX set to 2, the processor returns information about the processor's internal caches and TLBs in the EAX, EBX, ECX, and EDX registers.

The encoding is as follows:

- The least-significant byte in register EAX (register AL) indicates the number of times the CPUID instruction must be executed with an input value of 2 to get a complete description of the processor's caches and TLBs. The first member of the family of Pentium 4 processors will return a 1.

- The most significant bit (bit 31) of each register indicates whether the register contains valid information (set to 0) or is reserved (set to 1).

- If a register contains valid information, the information is contained in 1 byte descriptors. Table 2-6 shows the encoding of these descriptors. Note that the order of descriptors in the EAX, EBX, ECX, and EDX registers is not defined; that is, specific bytes are not designated to contain descriptors for specific cache or TLB types. The descriptors may appear in any order.

| Descriptor<br>Value | Cache or TLB Description                                                                    |

|---------------------|---------------------------------------------------------------------------------------------|

| 00H                 | Null descriptor                                                                             |

| 01H                 | Instruction TLB: 4K-Byte Pages, 4-way set associative, 32 entries                           |

| 02H                 | Instruction TLB: 4M-Byte Pages, 4-way set associative, 2 entries                            |

| 03H                 | Data TLB: 4K-Byte Pages, 4-way set associative, 64 entries                                  |

| 04H                 | Data TLB: 4M-Byte Pages, 4-way set associative, 8 entries                                   |

| 06H                 | 1st-level instruction cache: 8K Bytes, 4-way set associative, 32 byte line size             |

| 08H                 | 1st-level instruction cache: 16K Bytes, 4-way set associative, 32 byte line size            |

| 0AH                 | 1st-level data cache: 8K Bytes, 2-way set associative, 32 byte line size                    |

| 0CH                 | 1st-level data cache: 16K Bytes, 4-way set associative, 32 byte line size                   |

| 22H                 | 3rd-level cache: 512K Bytes, 4-way set associative, 64 byte line size, 128 byte sector size |

| 23H                 | 3rd-level cache: 1M Bytes, 8-way set associative, 64 byte line size, 128 byte sector size   |

| 25H                 | 3rd-level cache: 2M Bytes, 8-way set associative, 64 byte line size, 128 byte sector size   |

| 29H                 | 3rd-level cache: 4M Bytes, 8-way set associative, 64 byte line size, 128 byte sector size   |

| 2CH                 | 1st-level data cache: 32K Bytes, 8-way set associative, 64 byte line size                   |

| 30H                 | 1st-level instruction cache: 32K Bytes, 8-way set associative, 64 byte line size            |

| 40H                 | No 2nd-level cache or, if processor contains a valid 2nd-level cache, no 3rd-level cache    |

| 41H                 | 2nd-level cache: 128K Bytes, 4-way set associative, 32 byte line size                       |

| 42H                 | 2nd-level cache: 256K Bytes, 4-way set associative, 32 byte line size                       |

| 43H                 | 2nd-level cache: 512K Bytes, 4-way set associative, 32 byte line size                       |

| 44H                 | 2nd-level cache: 1M Byte, 4-way set associative, 32 byte line size                          |

| 45H                 | 2nd-level cache: 2M Byte, 4-way set associative, 32 byte line size                          |

| 50H                 | Instruction TLB: 4-KByte and 2-MByte or 4-MByte pages, 64 entries                           |

| 51H                 | Instruction TLB: 4-KByte and 2-MByte or 4-MByte pages, 128 entries                          |

| 52H                 | Instruction TLB: 4-KByte and 2-MByte or 4-MByte pages, 256 entries                          |

| 5BH                 | Data TLB: 4-KByte and 4-MByte pages, 64 entries                                             |

| 5CH                 | Data TLB: 4-KByte and 4-MByte pages,128 entries                                             |

| 5DH                 | Data TLB: 4-KByte and 4-MByte pages,256 entries                                             |

| 60H                 | 1st-level data cache: 16KB, 8-way set associative, 64 byte line size                        |

| 66H                 | 1st-level data cache: 8KB, 4-way set associative, 64 byte line size                         |

| 67H                 | 1st-level data cache: 16KB, 4-way set associative, 64 byte line size                        |

| 68H                 | 1st-level data cache: 32KB, 4-way set associative, 64 byte line size                        |

| 70H                 | Trace cache: 12K-µop, 8-way set associative                                                 |

Table 2-6. Encoding of Cache and TLB Descriptors

| Descriptor<br>Value | Cache or TLB Description                                                               |

|---------------------|----------------------------------------------------------------------------------------|

| 71H                 | Trace cache: 16K-µop, 8-way set associative                                            |

| 72H                 | Trace cache: 32K-µop, 8-way set associative                                            |

| 78H                 | 2nd-level cache: 1M Byte, 8-way set associative, 64byte line size                      |

| 79H                 | 2nd-level cache: 128KB, 8-way set associative, 64 byte line size, 128 byte sector size |

| 7AH                 | 2nd-level cache: 256KB, 8-way set associative, 64 byte line size, 128 byte sector size |

| 7BH                 | 2nd-level cache: 512KB, 8-way set associative, 64 byte line size, 128 byte sector size |

| 7CH                 | 2nd-level cache: 1MB, 8-way set associative, 64 byte line size, 128 byte sector size   |

| 7DH                 | 2nd-level cache: 2M Byte, 8-way set associative, 64byte line size                      |

| 82H                 | 2nd-level cache: 256K Byte, 8-way set associative, 32 byte line size                   |

| 83H                 | 2nd-level cache: 512K Byte, 8-way set associative, 32 byte line size                   |

| 84H                 | 2nd-level cache: 1M Byte, 8-way set associative, 32 byte line size                     |

| 85H                 | 2nd-level cache: 2M Byte, 8-way set associative, 32 byte line size                     |

| 86H                 | 2nd-level cache: 512K Byte, 4-way set associative, 64 byte line size                   |

| 87H                 | 2nd-level cache: 1M Byte, 8-way set associative, 64 byte line size                     |

| B0H                 | Instruction TLB: 4K-Byte Pages, 4-way set associative, 128 entries                     |

| B3H                 | Data TLB: 4K-Byte Pages, 4-way set associative, 128 entries                            |

| Table 2-6. Encoding of Cache and TLB Descriptors (Contd.) |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

#### Example 2-1. Example of Cache and TLB Interpretation

The first member of the family of Pentium 4 processors returns the following information about caches and TLBs when the CPUID executes with an input value of 2:

EAX 66 5B 50 01H EBX 0H ECX 0H EDX 00 7A 70 00H

Which means:

- The least-significant byte (byte 0) of register EAX is set to 01H. This indicates that CPUID needs to be executed once with an input value of 2 to retrieve complete information about caches and TLBs.

- The most-significant bit of all four registers (EAX, EBX, ECX, and EDX) is set to 0, indicating that each register contains valid 1-byte descriptors.

- Bytes 1, 2, and 3 of register EAX indicate that the processor has:

- 50H a 64-entry instruction TLB, for mapping 4-KByte and 2-MByte or 4-MByte pages.

- 5BH a 64-entry data TLB, for mapping 4-KByte and 4-MByte pages.

- 66H an 8-KByte 1st level data cache, 4-way set associative, with a 64-byte cache line size.

- The descriptors in registers EBX and ECX are valid, but contain NULL descriptors.

- Bytes 0, 1, 2, and 3 of register EDX indicate that the processor has:

- 00H NULL descriptor.

- 70H a 12-KByte 1st level code cache, 4-way set associative, with a 64-byte cache line size.

- 7AH a 256-KByte 2nd level cache, 8-way set associative, with a sectored, 64-byte cache line size.

- 00H NULL descriptor.

#### METHODS FOR RETURNING BRANDING INFORMATION

Use the following techniques to access branding information:

- 1. Processor brand string method; this method also returns the processor's maximum operating frequency.

- 2. Processor brand index; this method uses a software supplied brand string table.

These two methods are discussed in the following sections. For methods that are available in early processors, see Section: "Identification of Earlier IA-32 Processors" in Chapter 14 of the *IA-32 Intel Architecture Software Developer's Manual, Volume 1.*

#### **The Processor Brand String Method**

Figure 2-4 describes the algorithm used for detection of the brand string. Processor brand identification software should execute this algorithm on all IA-32 architecture compatible processors.

This method (introduced with Pentium 4 processors) returns an ASCII brand identification string and the maximum operating frequency of the processor to the EAX, EBX, ECX, and EDX registers.

Figure 2-4. Determination of Support for the Processor Brand String

#### How Brand Strings Work

To use the brand string method, execute CPUID with EAX input of 8000002H through 80000004H. For each input value, CPUID returns 16 ASCII characters using EAX, EBX, ECX, and EDX. The returned string will be NULL terminated.

Table 2-7 shows the brand string that is returned by the first processor in the Pentium 4 processor family.

| EAX Input Value | Return Values                                                            | ASCII Equivalent                      |

|-----------------|--------------------------------------------------------------------------|---------------------------------------|

| 8000002H        | EAX = 20202020H<br>EBX = 20202020H<br>ECX = 20202020H<br>EDX = 6E492020H | ""<br>""<br>"nl"                      |

| 80000003H       | EAX = 286C6574H<br>EBX = 50202952H<br>ECX = 69746E65H<br>EDX = 52286D75H | "(let"<br>"P )R"<br>"itne"<br>"R(mu"  |

| 80000004H       | EAX = 20342029H<br>EBX = 20555043H<br>ECX = 30303531H<br>EDX = 007A484DH | " 4 )"<br>" UPC"<br>"0051"<br>"∖0zHM" |

#### Extracting the Maximum Processor Frequency from Brand Strings

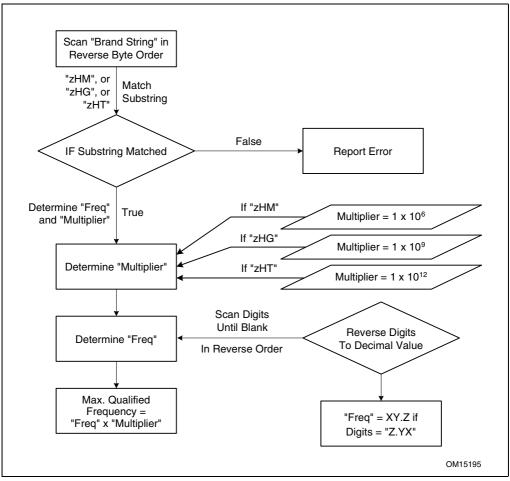

Figure 2-5 provides an algorithm which software can use to extract the maximum processor operating frequency from the processor brand string.

#### NOTE

When a frequency is given in a brand string, it is the maximum qualified frequency of the processor, not the frequency at which the processor is currently running.

Figure 2-5. Algorithm for Extracting Maximum Processor Frequency

#### The Processor Brand Index Method

The brand index method (introduced with Pentium III Xeon processors) provides an entry point into a brand identification table that is maintained in memory by system software and is accessible from system- and user-level code. In this table, each brand index is associate with an ASCII brand identification string that identifies the official Intel family and model number of a processor.

When CPUID executes with EAX set to 1, the processor returns a brand index to the low byte in EBX. Software can then use this index to locate the brand identification string for the processor in the brand identification table. The first entry (brand index 0) in this table is

reserved, allowing for backward compatibility with processors that do not support the brand identification feature.

Table 2-8 shows brand indices that have identification strings associated with them.

| Brand Index | Brand String                                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Branu Sunny                                                                                                                                                            |

| 0H          | This processor does not support the brand identification feature                                                                                                       |

| 01H         | Intel <sup>®</sup> Celeron <sup>®</sup> processor <sup>†</sup>                                                                                                         |