# Intel® Trust Domain Extensions (Intel® TDX) Module Base Architecture Specification

348549-001US

September 2021

#### **Notices and Disclaimers**

Intel Corporation ("Intel") provides these materials as-is, with no express or implied warranties.

All products, dates, and figures specified are preliminary, based on current expectations, and are subject to change without notice. Intel does not guarantee the availability of these interfaces in any future product. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described might contain design defects or errors known as errata, which might cause the product to deviate from published specifications. Current, characterized errata are available on request.

Intel technologies might require enabled hardware, software, or service activation. Some results have been estimated or simulated. Your costs and results might vary.

No product or component can be absolutely secure.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted that includes the subject matter disclosed herein.

No license (express, implied, by estoppel, or otherwise) to any intellectual-property rights is granted by this document.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice.

Copies of documents that have an order number and are referenced in this document or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting http://www.intel.com/design/literature.htm.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

Other names and brands might be claimed as the property of others.

September 2021 Page 2 of 133

# **Table of Contents**

|    | SECTION 1: INTROD | UCTION AND OVERVIEW                                                  | 10 |

|----|-------------------|----------------------------------------------------------------------|----|

|    | 1. About this Doo | cument                                                               | 11 |

|    | 1.1. Scope of t   | his Document                                                         | 11 |

| 5  | 1.2. Document     | t Organization                                                       | 11 |

|    |                   |                                                                      |    |

|    | •                 |                                                                      |    |

|    |                   | irement and Definition Commitment Levels                             |    |

|    | •                 |                                                                      |    |

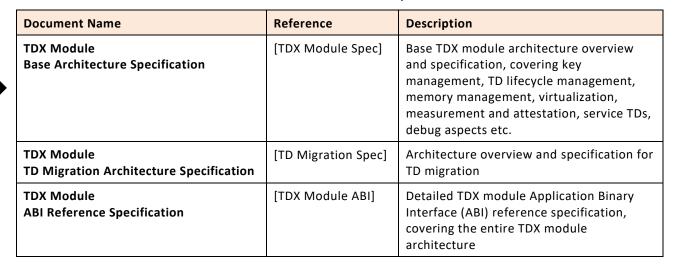

| 10 | _                 | sPublic Documents                                                    |    |

| 10 |                   | TDX Public Documents                                                 |    |

|    | 2. Overview of In | itel® Trust Domain Extensions                                        | 17 |

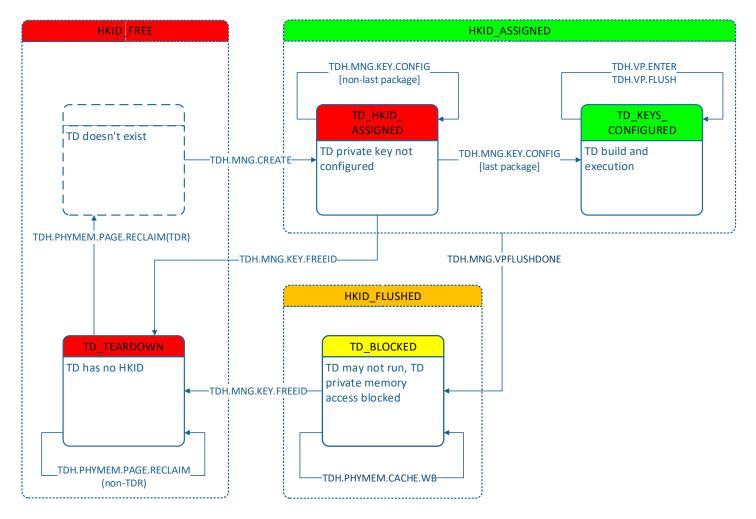

|    | 2.1. Intel TDX    | Module Lifecycle                                                     | 17 |

|    |                   | -Time Configuration and Intel TDX Module Loading                     |    |

| 15 |                   | ATED: Intel TDX Module Initialization, Enumeration and Configuration |    |

|    | 2.2. Guest TD     | Life Cycle Overview                                                  | 10 |

|    |                   | t TD Buildt                                                          |    |

|    |                   | t TD Execution                                                       |    |

|    |                   | t TD Management during its Run-Time                                  |    |

|    |                   |                                                                      |    |

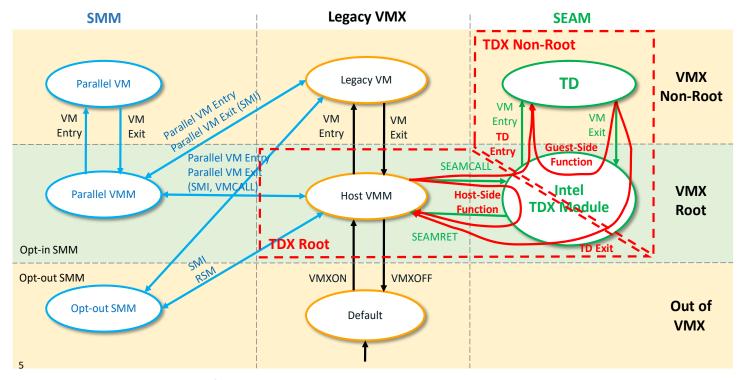

| 20 |                   | Operation Modes and Transitions                                      |    |

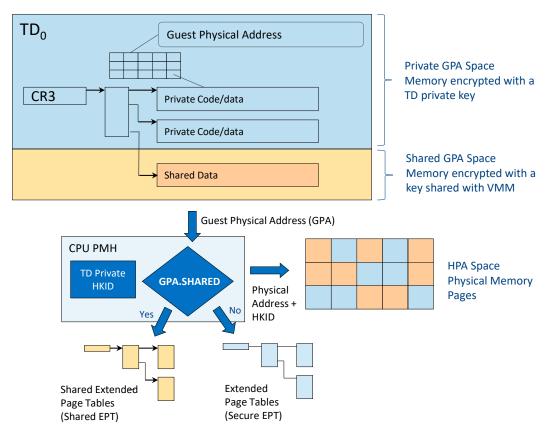

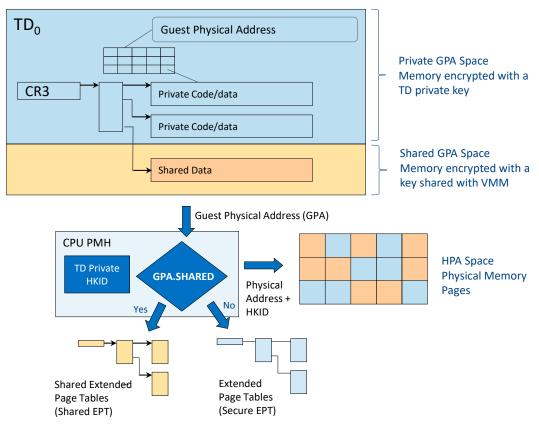

|    |                   | Private Memory Protection                                            |    |

|    |                   | Memory Encryption                                                    |    |

|    | 2.4.2. Addr       | ess Translation                                                      | 20 |

|    | 2.5. Guest TD     | State Protection                                                     | 21 |

| 25 | 2.6. Intel TDX    | I/O Model                                                            | 21 |

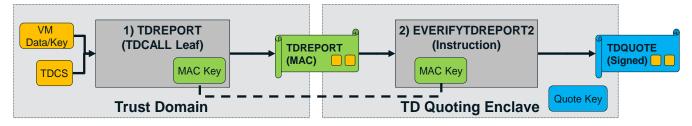

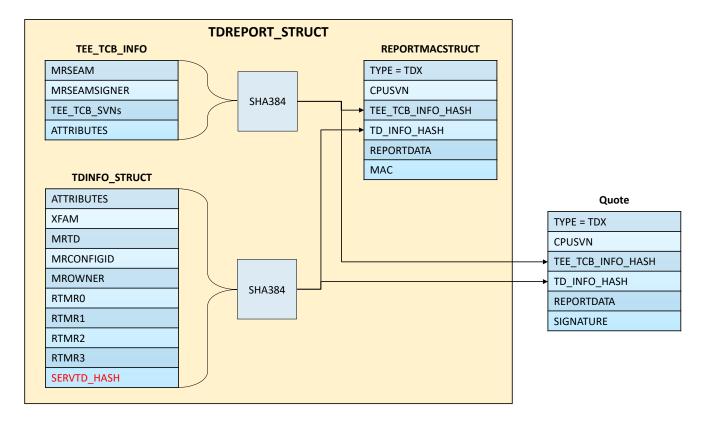

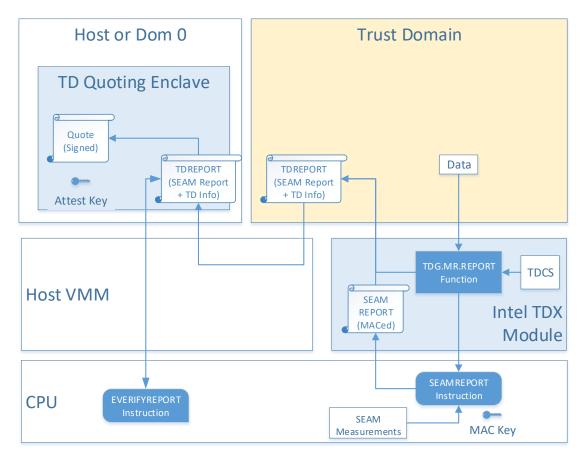

|    | 2.7. Measuren     | nent and Attestation                                                 | 22 |

|    | 2.8. Intel TDX    | Managed Control Structures                                           | 22 |

|    | 2.9. Intel TDX    | Interface Functions                                                  | 23 |

|    |                   | -Side (SEAMCALL Leaf) Interface Functions                            |    |

| 30 |                   | t-Side (TDCALL Leaf) Interface Functions                             |    |

|    | 3. Software Use ( | Cases                                                                | 26 |

|    | 3.1. Intel TDX    | Module Lifecycle                                                     | 26 |

|    |                   | ATED: Intel TDX Module Platform-Scope Initialization                 |    |

|    | 3.1.2. Intel      | TDX Module Reload and Update                                         | 26 |

| 35 | 3.2. TD Build     |                                                                      | 27 |

|    | 3.3. TD Run Tii   | me                                                                   | 29 |

|    |                   | te Memory Management                                                 |    |

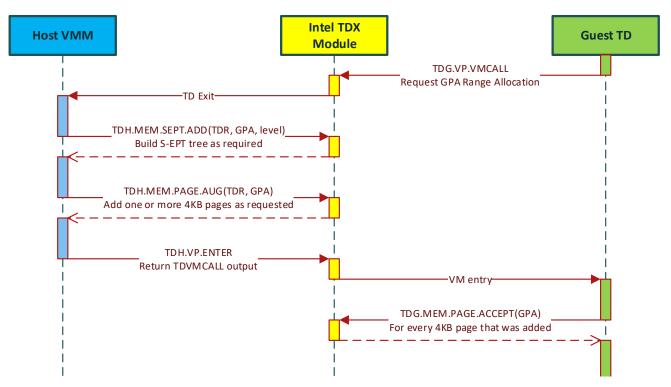

|    |                   | Dynamic Page Addition (Shared to Private Conversion)                 |    |

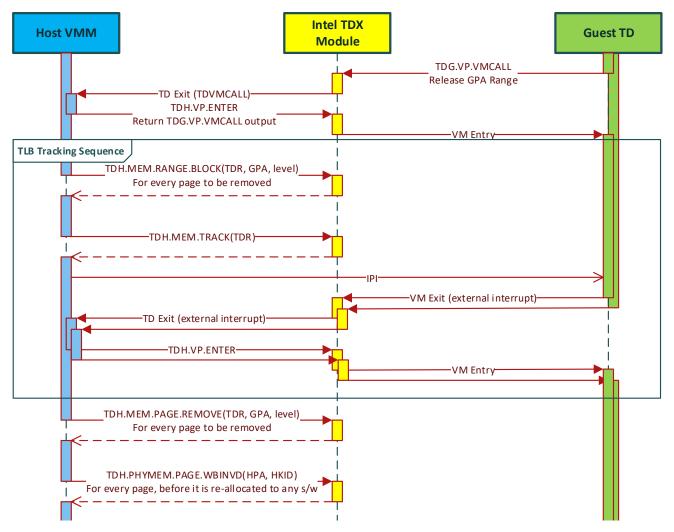

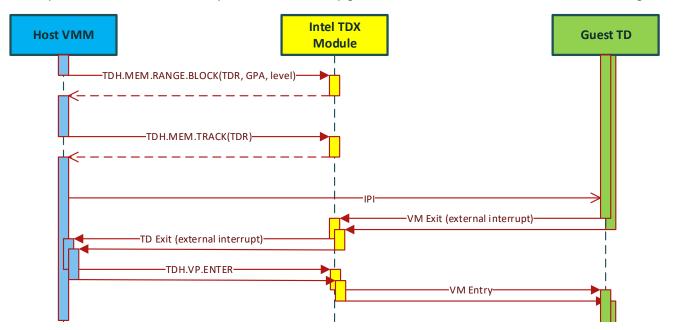

|    | 3.3.1.2.          | Dynamic Page Removal (Private to Shared Conversion)                  | 30 |

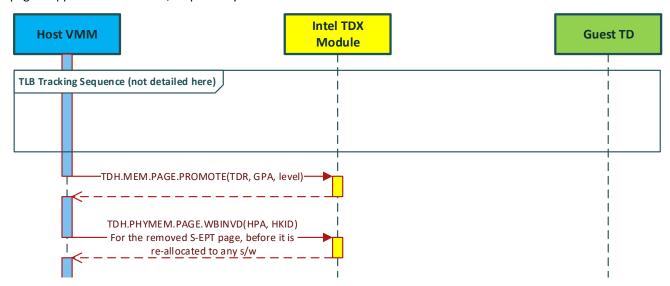

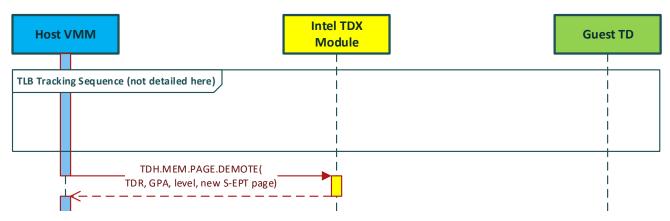

| 40 | 3.3.1.3.          | Page Promotion (Mapping Merge)                                       | 31 |

|    |                   | Page Demotion (Mapping Split)                                        |    |

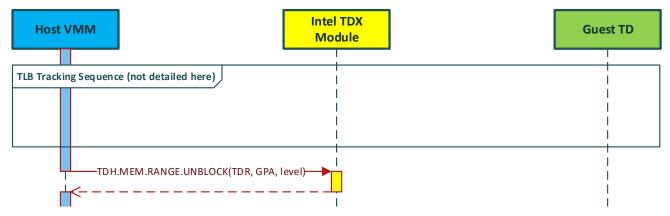

|    |                   | GPA Range Unblock                                                    |    |

|    |                   | t TD Execution                                                       |    |

|    |                   | TD VCPU First-Time Invocation                                        |    |

| 45 |                   | TD VCPU Entry, Exit on TDG.VP.VMCALL and Re-Entry                    |    |

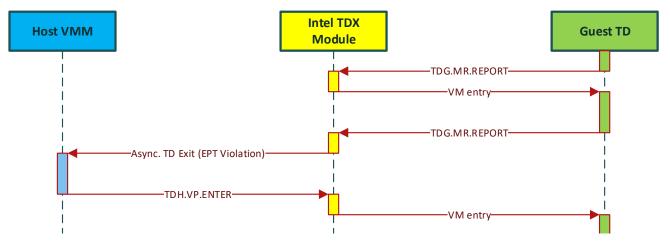

|    |                   | TD VCPU Entry, Exit on Asynchronous Event and Re-Entry               |    |

|    | 5.5.2.4.          | Ouest-Jiue Fuiiclions                                                | 35 |

|    | 3.3.2.5. TD VCPU Rescheduling (Migration to Another LP)                                                                                                   | 36 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

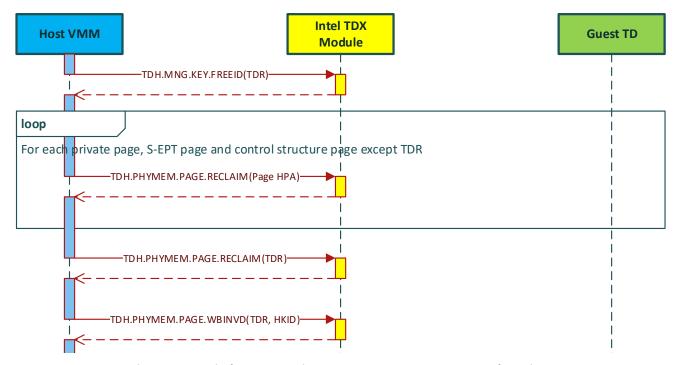

|    | 3.4. TD Destruction                                                                                                                                       | 37 |

|    | SECTION 2: INTEL TDX MODULE ARCHITECTURE SPECIFICATION                                                                                                    | 39 |

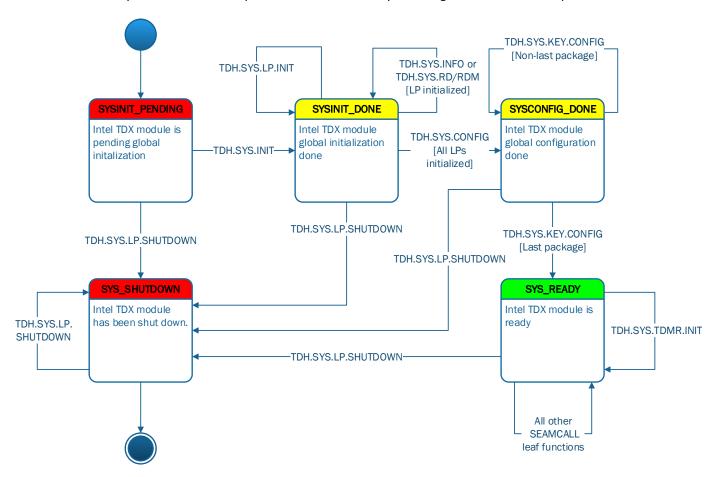

|    | 4. UPDATED: Intel TDX Module Lifecycle: Enumeration, Initialization and Shutdown                                                                          | 40 |

| 5  | 4.1. UPDATED: Overview                                                                                                                                    | 40 |

|    | 4.1.1. UPDATED: Initialization and Configuration Flow                                                                                                     |    |

|    | 4.1.2. UPDATED: Intel TDX Module Lifecycle State Machine                                                                                                  |    |

|    | 4.1.3. Platform Compatibility and Configuration Checking                                                                                                  |    |

|    | 4.1.3.1. Overview                                                                                                                                         |    |

| 10 | 4.1.3.2. MSR Sampling and Checks                                                                                                                          |    |

|    | 4.1.3.3. UPDATED: CPUID Sampling, Checks and Enumeration                                                                                                  |    |

|    | 4.1.4. Physical Memory Configuration Overview                                                                                                             |    |

|    | 4.1.4.2. TDMRs and PAMT Arrays Configuration                                                                                                              |    |

|    |                                                                                                                                                           |    |

| 15 | 4.2. Intel TDX Module Initialization Interface                                                                                                            |    |

|    | 4.2.1. Global Initialization: TDH.SYS.INIT                                                                                                                |    |

|    | 4.2.2. LP-Scope Initialization: TDH.SYS.LP.INIT                                                                                                           |    |

|    | 4.2.4. Global Configuration: TDH.SYS.CONFIG                                                                                                               |    |

| 20 | 4.2.5. Package-Scope Key Configuration: TDH.SYS.KEY.CONFIG                                                                                                |    |

| 20 | 4.3. TDMR and PAMT Initialization                                                                                                                         |    |

|    |                                                                                                                                                           |    |

|    | 4.4. Intel TDX Module Shutdown                                                                                                                            |    |

|    | 4.4.2. Shutdown Initiated by the Host Vivini (as Fait of Module Opdate)                                                                                   |    |

|    | , , , , , , , , , , , , , , , , , , ,                                                                                                                     |    |

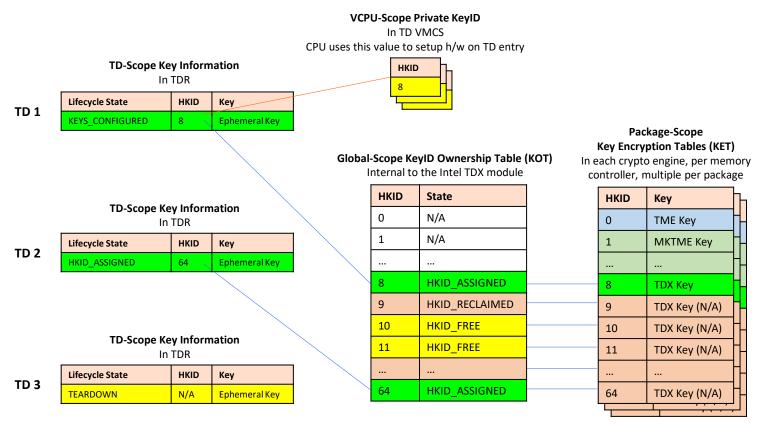

| 25 | 5. Key Management                                                                                                                                         | 46 |

|    | 5.1. Objectives                                                                                                                                           | 40 |

|    | 5.2. Background: HKID Space Partitioning                                                                                                                  | 40 |

|    | 5.3. Key Management Tables                                                                                                                                | 4  |

|    | 5.4. Combined Key Management State                                                                                                                        | 45 |

|    |                                                                                                                                                           |    |

| 30 | 5.5. Key Management Sequences                                                                                                                             |    |

|    | 5.5.1. Intel TDX Module Initialization: Setting an Ephemeral Key and Reserving an HKID for Intel TI 5.5.2. TD Creation, Keys Assignment and Configuration |    |

|    | 5.5.2. TD Creation, keys Assignment and Corniguration                                                                                                     |    |

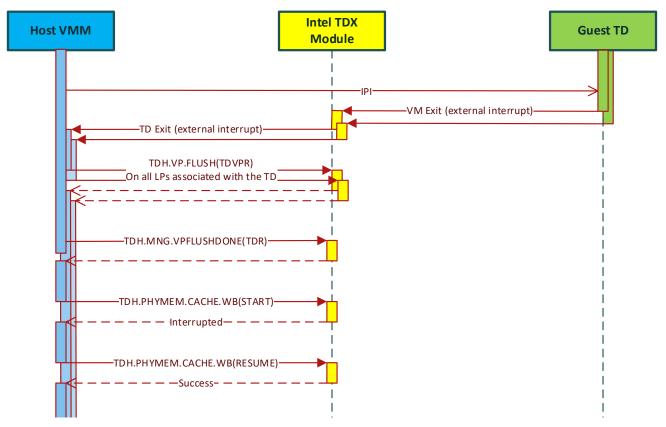

|    | 5.5.5. 10 Keys Necialitation, TEB and Cache Flush                                                                                                         |    |

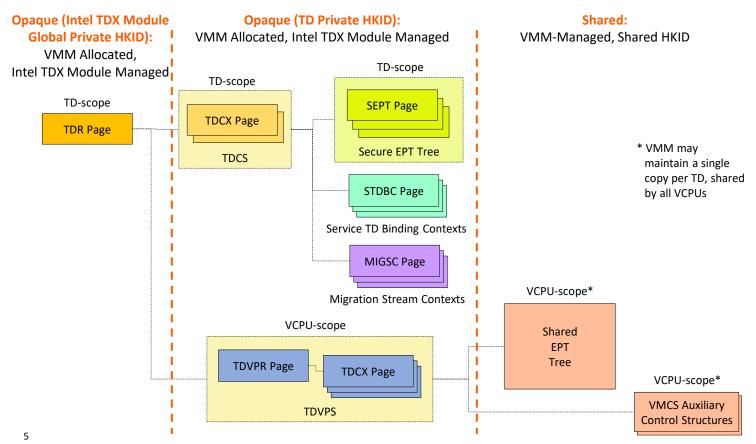

|    | 6. UPDATED: TD Non-Memory State (Metadata) and Control Structures                                                                                         | 51 |

| 35 | 6.1. Overview                                                                                                                                             | 5. |

|    | 6.1.1. Opaque vs. Shared Control Structures                                                                                                               |    |

|    | 6.1.2. Scope of Control Structures                                                                                                                        | 52 |

|    | 6.2. TD-Scope Control Structures                                                                                                                          | 5  |

|    | 6.2.1. TDR (Trust Domain Root)                                                                                                                            |    |

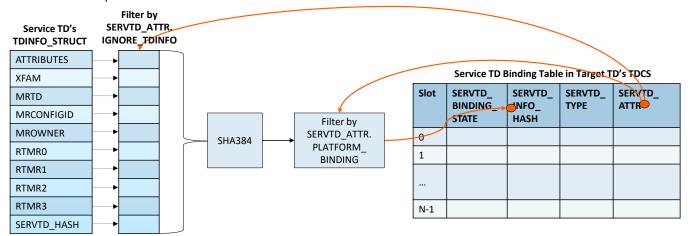

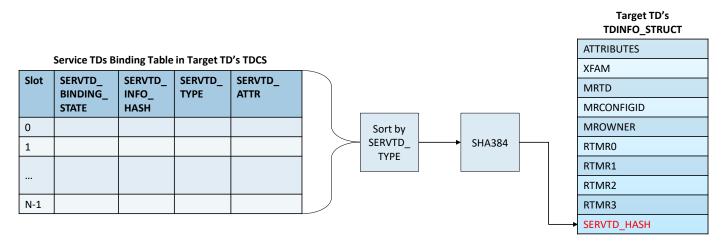

| 40 | 6.2.2. UPDATED: TDCS (Trust Domain Control Structure)                                                                                                     | 52 |

|    | 6.3. TD VCPU-Scope Control Structures                                                                                                                     | 52 |

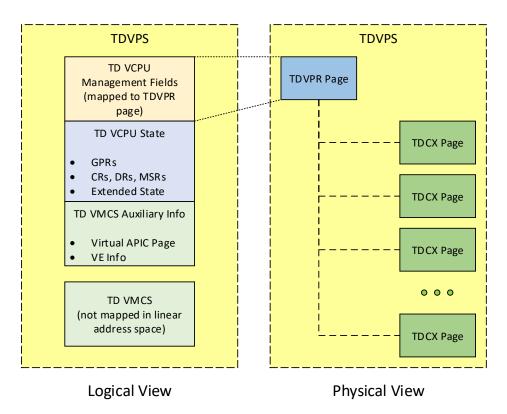

|    | 6.3.1. Trust Domain Virtual Processor State (TDVPS)                                                                                                       |    |

|    | 6.3.1.1. UPDATED: Physical View of TDVPS: TDVPR/TDCX                                                                                                      | 53 |

|    | 6.3.1.2. Logical View of TDVPS                                                                                                                            |    |

| 45 | 6.3.2. Non-Protected Control Structures: Shared EPT and VMCS Auxiliary Control Structures                                                                 | 54 |

|    | 6.4. UPDATED: TD Non-Memory State (Metadata) Access Functions                                                                                             | 54 |

|    | 6.5. Concurrency Restrictions and Enforcement                                                                                                             | 5, |

|    | 5.5. 55557667 Nestrictions and Enjordement imminimum.                                                                                                     |    |

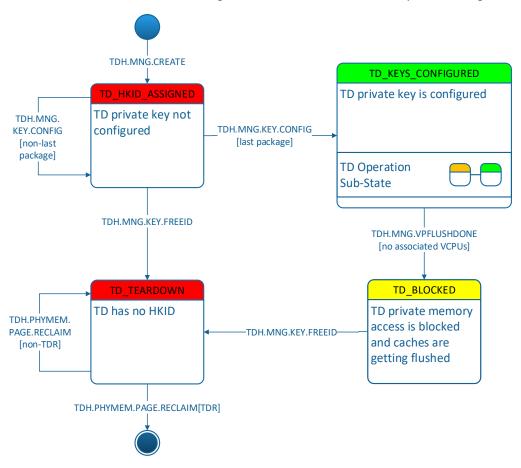

|    | 7. UPD         | ATED: TD Life Cycle Management                                                            | 55 |

|----|----------------|-------------------------------------------------------------------------------------------|----|

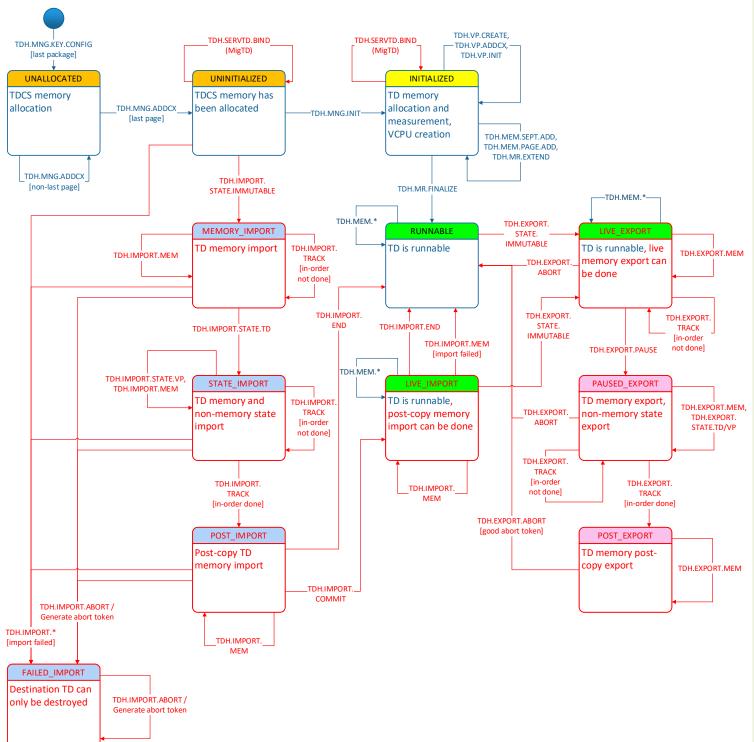

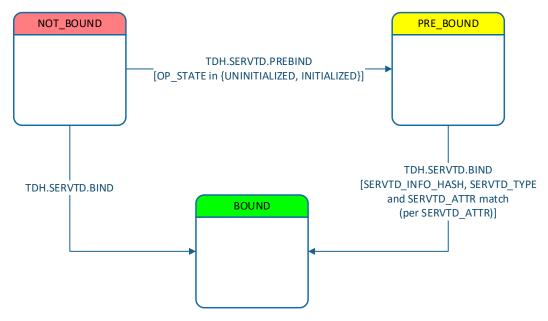

|    | 7.1.           | TD Life Cycle State Machine                                                               | 55 |

|    | 7.2.           | UPDATED: OP_STATE: TD Operation Secondary-Level State Machine                             | 55 |

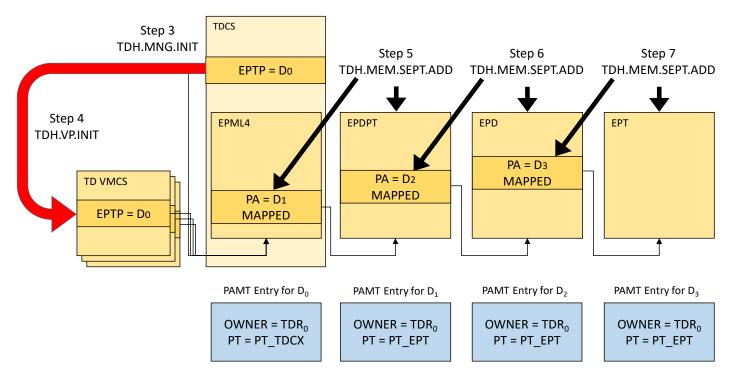

|    | 7.3.           | TD Creation Sequence                                                                      | 56 |

| 5  | 7.4.           | VCPU Creation and Initialization Sequence                                                 | 57 |

|    | 7.5.           | TD Teardown Sequence                                                                      |    |

|    |                | ·                                                                                         |    |

|    | 8. Phys        | sical Memory Management                                                                   |    |

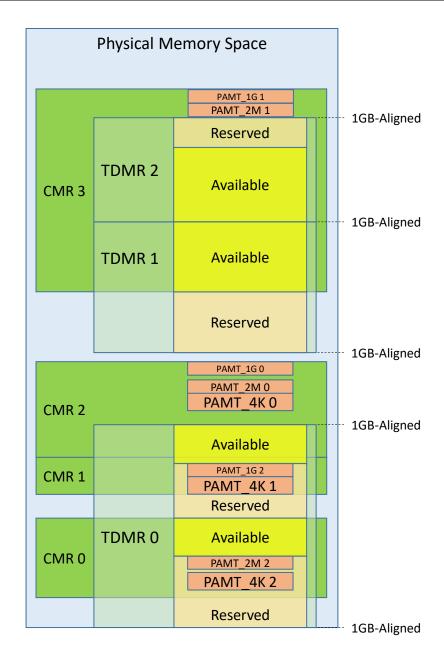

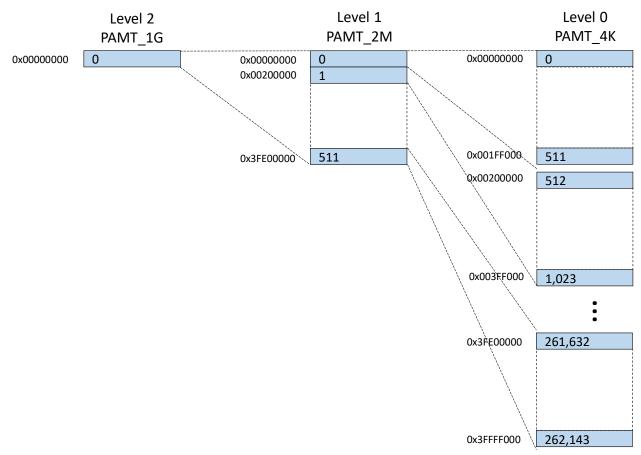

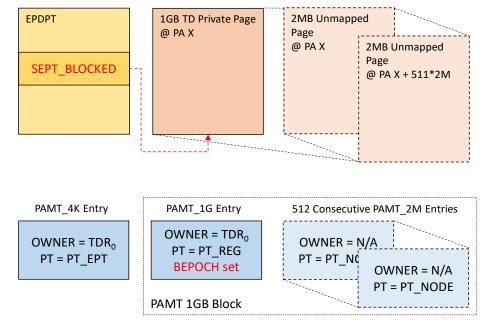

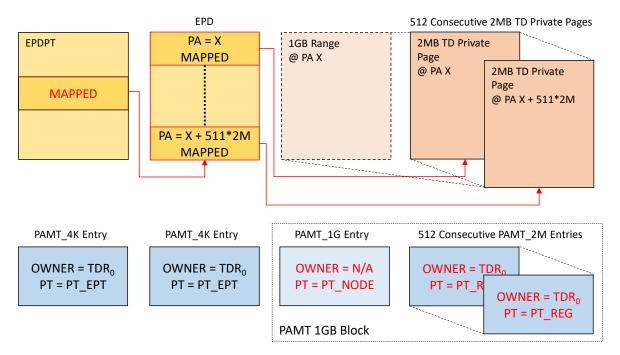

|    | 8.1.           | UPDATED: Trust Domain Memory Regions (TDMRs) and Physical Address Metadata Tables (PAMTs) | 59 |

|    | 8.2.           | UPDATED: TDMR Details                                                                     | 59 |

| 10 | <i>8.3</i> .   | PAMT Details                                                                              |    |

|    | 8.3.2          | ,                                                                                         |    |

|    | 8.3.2          | ı                                                                                         |    |

|    | 8.3.3          | 5 //                                                                                      |    |

|    | 8.3.4          | 4. PAMT Hierarchy                                                                         | 61 |

| 15 | 8.4.           | Adding Physical Pages                                                                     | 62 |

|    | 8.4.2          |                                                                                           |    |

|    | 8.4.2          |                                                                                           |    |

|    | 8.4.3          | 3. Adding Pages and Mapping to the Guest TD's GPA                                         | 62 |

|    | 8.5.           | Reclaiming Physical Pages                                                                 | 62 |

| 20 | 8.5.2          | 1. Reclaiming Pages not Mapped to the Guest TD                                            | 62 |

|    | 8.5.2          |                                                                                           |    |

|    | 8.5.3          | 3. Reclaiming Physical Pages as Part of TD Private Memory Management                      | 62 |

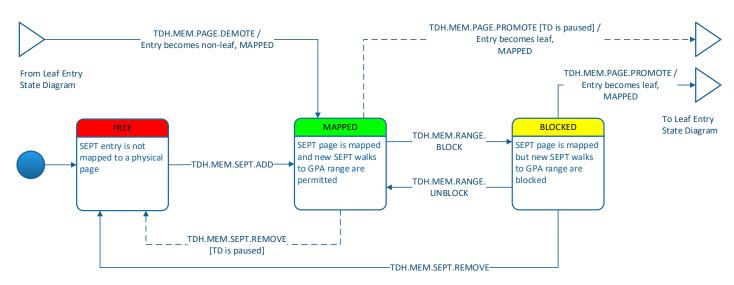

|    | 9. TD P        | Private Memory Management                                                                 | 6/ |

|    | 9.1.           | Overview                                                                                  |    |

|    |                |                                                                                           |    |

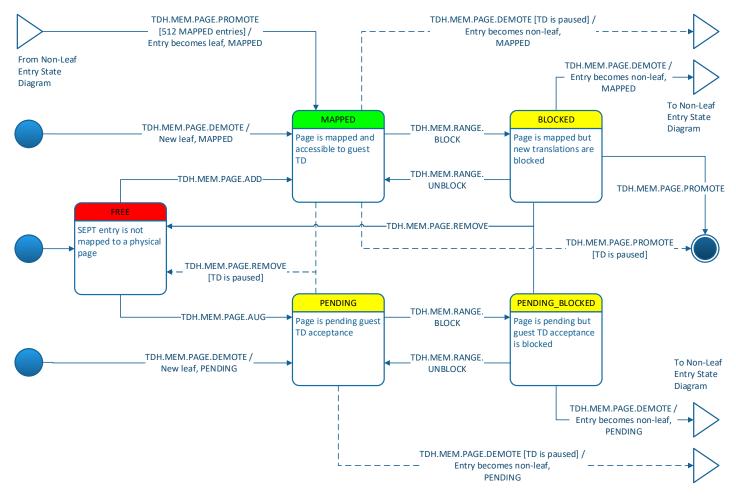

| 25 |                | Secure EPT Entry                                                                          |    |

|    | 9.2.2<br>9.2.2 |                                                                                           |    |

|    |                |                                                                                           |    |

|    |                | Secure EPT Walk                                                                           |    |

|    | 9.4.           | Secure EPT Induced TD Exits                                                               |    |

| 30 | 9.5.           | Secure EPT Induced Exceptions                                                             | 67 |

|    | 9.6.           | UPDATED: Secure EPT Concurrency                                                           | 67 |

|    | 9.7.           | Introduction to TLB Tracking                                                              | 67 |

|    | 9.8.           | Secure EPT Build and Update: TDH.MEM.SEPT.ADD                                             | 68 |

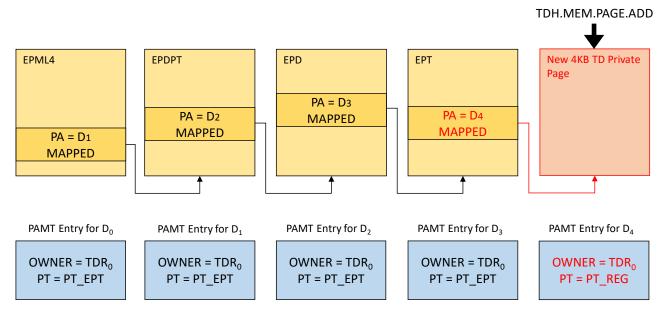

|    | 9.9.           | Adding TD Private Pages during TD Build Time: TDH.MEM.PAGE.ADD                            | 69 |

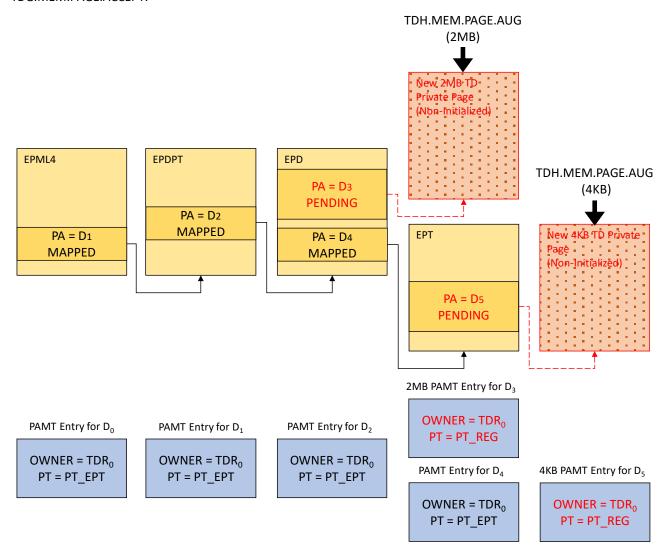

| 35 | 9.10.          | Dynamically Adding TD Private Pages                                                       | 70 |

|    | 9.10           | .1. Overview                                                                              | 70 |

|    | 9.10           | .0                                                                                        |    |

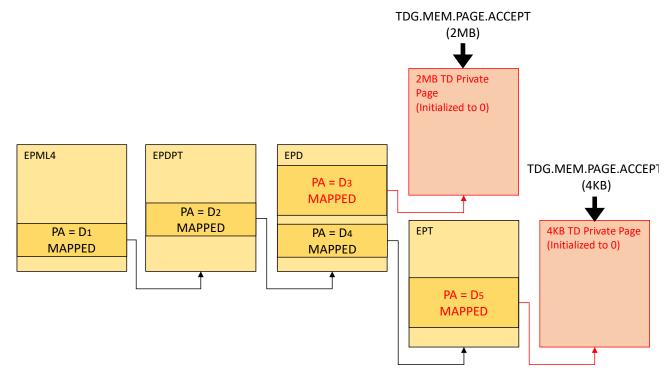

|    | 9.10           |                                                                                           |    |

|    |                | 10.3.1. Description                                                                       |    |

| 40 | 9.             | 10.3.2. TDG.MEM.PAGE.ACCEPT Concurrency                                                   | 73 |

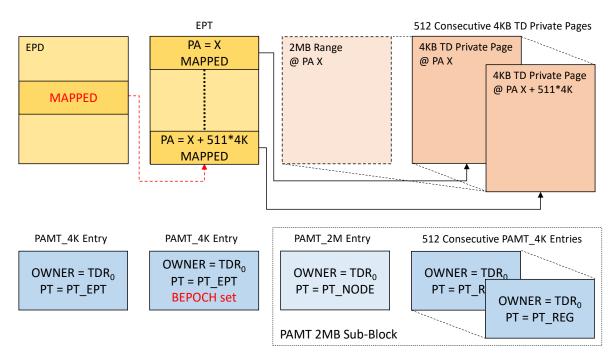

|    | 9.11.          | Page Merge: TDH.MEM.PAGE.PROMOTE                                                          | 73 |

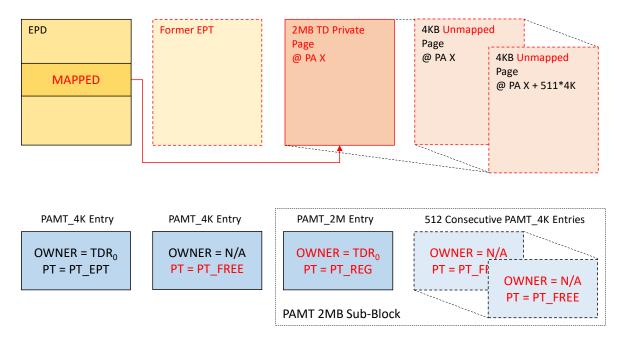

|    | 9.12.          | Page Split: TDH.MEM.PAGE.DEMOTE                                                           | 75 |

|    | 9.13.          | Relocating TD Private Pages: TDH.MEM.PAGE.RELOCATE                                        | 76 |

|    | 9.14.          | Removing TD Private Pages: TDH.MEM.PAGE.REMOVE                                            | 77 |

|    | •              |                                                                                           |    |

|    | 9.16.             | Unblocking a GPA Range: TDH.MEM.RANGE.UNBLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

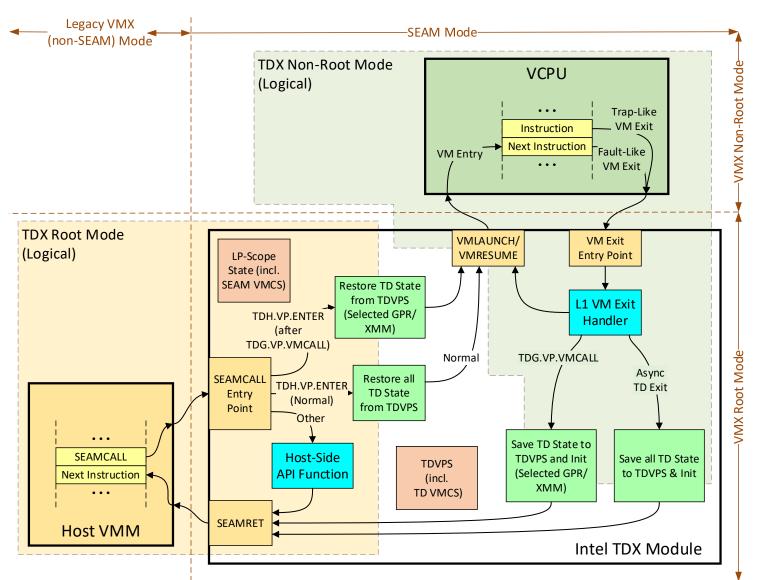

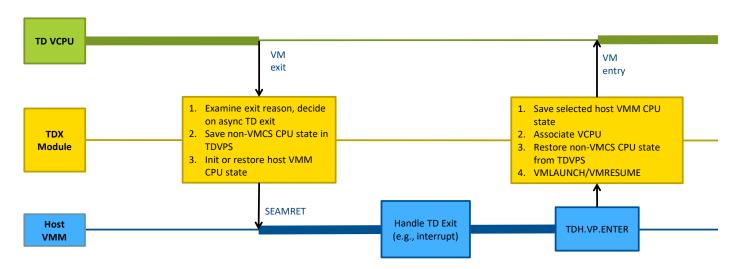

|    | 10. TD \          | /CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |

|    | 10.1.             | VCPU Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |

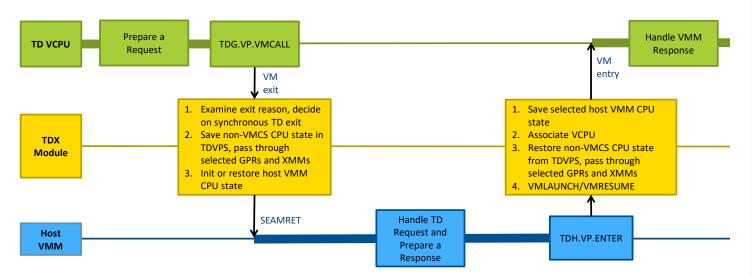

|    | 10.1.1.           | . Initial TD Entry, Asynchronous TD Exit and Subsequent TD Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |

| 5  | 10.1.2            | . Synchronous TD Exit and Subsequent TD Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

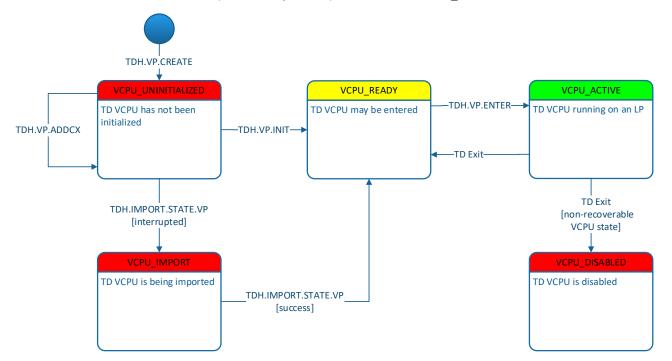

|    | 10.1.3            | . UPDATED: VCPU Activity State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

|    | 10.2.             | TD VCPU TLB Address Space Identifier (ASID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82 |

|    | 10.2.1            | and the second s |    |

|    | 10.2.2.           | . INVEPT by the Host VMM for Managing the Shared EPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82 |

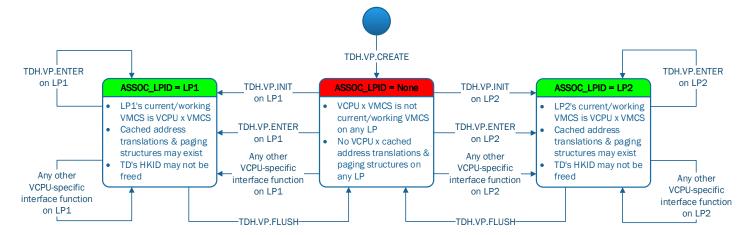

| 10 | 10.3.             | VCPU-to-LP Association                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82 |

|    | 10.3.1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | 10.3.2.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | 10.3.3            | . Performance Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83 |

|    | 11. UPD           | PATED: CPU Virtualization (Non-Root Mode Operation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84 |

| 15 | 11.1.             | Initial State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|    | 11.1.1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | 11.1.2            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _  |

|    | 11.1.3            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 20 | 11.1.4.<br>11.1.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

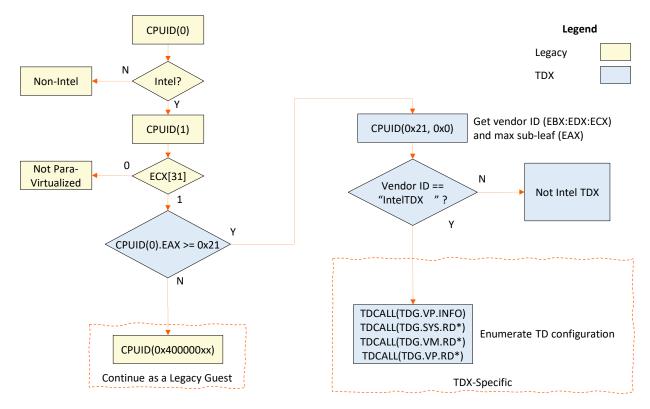

| 20 | 11.2.             | UPDATED: Guest TD Run Time Environment Enumeration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    | 11.3.             | CPU Mode Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|    | 11.4.             | Instructions Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86 |

|    | 11.4.1.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 25 | 11.4.2            | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|    | 11.4.3            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|    | 11.4.4            | Other Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87 |

|    | 11.5.             | Extended Feature Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87 |