# Intel<sup>®</sup> Trusted Execution Technology

Software Development Guide Measured Launched Environment Developer's Guide

June 2008

Document Number: 315168-005

Intel® Trusted Execution Technology

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use.

No computer system can provide absolute security under all conditions. Intel<sup>®</sup> Trusted Execution Technology (TXT) is a security technology under development by Intel and requires for operation a computer system with Intel<sup>®</sup> Virtualization Technology, a Intel<sup>®</sup> Trusted Execution Technology compatible measured virtual machine monitor. In addition, Intel<sup>®</sup> Trusted Execution Technology compatible measured virtual machine monitor. In addition, Intel<sup>®</sup> Trusted Execution Technology requires the system to contain a TPMv1.2 as defined by the Trusted Computing Group and specific software for some uses. See http://www.intel.com/ for more information.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor

Intel, Pentium, Intel Xeon, Intel NetBurst, Intel Core Solo, Intel Core Duo, Intel Pentium D, Itanium, MMX, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright © 2006-2008 Intel Corporation

Intel® Trusted Execution Technology

# **Contents**

1

2

| 1.1    | Measurement and Intel <sup>®</sup> Trusted Execution Technology       |  |  |  |

|--------|-----------------------------------------------------------------------|--|--|--|

| 1.2    | Dynamic Root of Trust                                                 |  |  |  |

|        | 1.2.1 Launch Sequence                                                 |  |  |  |

| 1.3    | Storing the Measurement                                               |  |  |  |

| 1.4    | Controlled Take-down                                                  |  |  |  |

| 1.5    | SMX and VMX Interaction                                               |  |  |  |

| 1.6    | Authenticated Code Module                                             |  |  |  |

| 1.7    | Chipset Support                                                       |  |  |  |

| 1.8    | TPM Usage                                                             |  |  |  |

| 1.9    | PCR Usage                                                             |  |  |  |

| 1.7    | 1.9.1 PCR 17                                                          |  |  |  |

|        | 1.9.2 PCR 18                                                          |  |  |  |

| 1.10   | DMA Protection                                                        |  |  |  |

| 1.10   | 1.10.1 DMA Protected Range (DPR)                                      |  |  |  |

|        | 1.10.2 Intel® Virtualization Technology (Intel® VT) for Dire          |  |  |  |

|        | VT-d) Protected Memory Regions (PMRs)                                 |  |  |  |

| 1.11   | Intel <sup>®</sup> TXT Shutdown                                       |  |  |  |

|        | 1.11.1 Reset Conditions                                               |  |  |  |

| Measu  | red Launched Environment                                              |  |  |  |

| 2.1    | MLE Architecture Overview                                             |  |  |  |

| 2.2    | MLE Launch                                                            |  |  |  |

| 2.2    | 2.2.1 Intel <sup>®</sup> TXT Detection and Processor Preparation      |  |  |  |

|        | 2.2.2 Detection of Previous Errors                                    |  |  |  |

|        | 2.2.3 Loading the SINIT AC Module                                     |  |  |  |

|        | 2.2.4 Loading the MLE and Processor Rendezvous                        |  |  |  |

|        | 2.2.5 Performing a Measured Launch                                    |  |  |  |

| 2.3    | MLE Initialization                                                    |  |  |  |

| 2.4    | MLE Operation                                                         |  |  |  |

|        | 2.4.1 Address Space Correctness                                       |  |  |  |

|        | 2.4.2 Address Space Integrity                                         |  |  |  |

|        | 2.4.3 Physical RAM Regions                                            |  |  |  |

|        | 2.4.4 Intel <sup>®</sup> Trusted Execution Technology Chipset Regions |  |  |  |

|        | 2.4.5 Protecting Secrets                                              |  |  |  |

|        | 2.4.6 Machine Specific Register Handling                              |  |  |  |

|        | 2.4.7 Interrupts and Exceptions                                       |  |  |  |

|        | 2.4.8 ACPI Power Management Support                                   |  |  |  |

| 2.5    | MLE Teardown                                                          |  |  |  |

| 2.6    | Other Considerations                                                  |  |  |  |

|        | 2.6.1 Saving MSR State across a Measured Launch                       |  |  |  |

| Verify | ing Measured Launched Environments                                    |  |  |  |

| 3.1    | Overview                                                              |  |  |  |

| 5.1    | 3.1.1 LCP Components                                                  |  |  |  |

|            |        | 3.1.2<br>3.1.3       | Policy List Types<br>Supported Cryptographic Algorithms                            |      |

|------------|--------|----------------------|------------------------------------------------------------------------------------|------|

|            | 3.2    |                      | ngine Logic                                                                        |      |

|            | 0.2    | 3.2.1                | Combining Policies                                                                 |      |

|            | 3.3    | Measuri              | ng the Enforced Policy                                                             |      |

|            |        | 3.3.1                | No Policy Data                                                                     |      |

|            |        | 3.3.2                | LCP Policy Allow Any                                                               |      |

|            |        | 3.3.3                | LCP Policy Hash Only                                                               |      |

|            |        | 3.3.4                | Unsigned LCP_POLICY_DATA                                                           |      |

|            | 3.4    | 3.3.5<br>Rovocat     | Force Platform Owner Policyion                                                     |      |

|            | 3.4    | 3.4.1                | SINIT Revocation                                                                   |      |

| 4          | Develo | opment ar            | nd Deployment Considerations                                                       | . 50 |

|            | 4.1    | Launch               | Control Policy Creation                                                            | . 50 |

|            | 4.2    |                      | Errors and Remediation                                                             |      |

|            | 4.3    | Deployn              | nent                                                                               | . 51 |

|            |        | 4.3.1                | LCP Provisioning                                                                   | .51  |

|            |        | 4.3.2                | SINIT Selection                                                                    | . 51 |

| Appendix A | Intel® |                      | ution Technology Authenticated Code Modules                                        |      |

|            | A.1    | Authent              | icated Code Module Format                                                          |      |

|            |        | A.1.1<br>A.1.2       | Memory type cacheability restrictions<br>Authentication and execution of AC module |      |

| Appendix B | SMX I  | nteractior           | with Platform                                                                      | . 62 |

|            | B.1    | Intel <sup>®</sup> T | rusted Execution Technology Configuration Registers                                | . 62 |

|            | B.2    | TPM Pla              | tform Configuration Registers                                                      | . 70 |

|            | B.3    | Intel <sup>®</sup> T | rusted Execution Technology Device Space                                           | . 70 |

| Appendix C | Intel® | TXT Heap             | Memory                                                                             | .72  |

|            | C.1    | BIOS Da              | ata Format                                                                         | 73   |

|            | C.2    | OS to M              | LE Data Format                                                                     | .74  |

|            | C.3    | OS to S              | INIT Data Format                                                                   | .74  |

|            | C.4    | SINIT to             | MLE Data Format                                                                    | .75  |

| Appendix D | LCP D  | ata Struct           | ures                                                                               | .78  |

|            | D.1    | LCP_PO               | LICY                                                                               | . 78 |

|            | D.2    | LCP_PO               | LICY_DATA                                                                          | . 79 |

|            | D.3    | LCP_UN               | SIGNED_POLICY_DATA                                                                 | . 79 |

|            |        | D.3.1<br>D.3.2       | LCP_POLICY_LIST                                                                    |      |

|            | D.4    | Structur             | e Endianness                                                                       | . 81 |

|            | D.5    | Errorcoc             | le Values                                                                          | . 81 |

# **Figures**

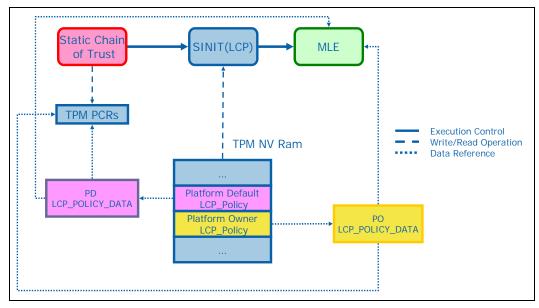

| Figure 1. Launch Control Policy Components | 43 |

|--------------------------------------------|----|

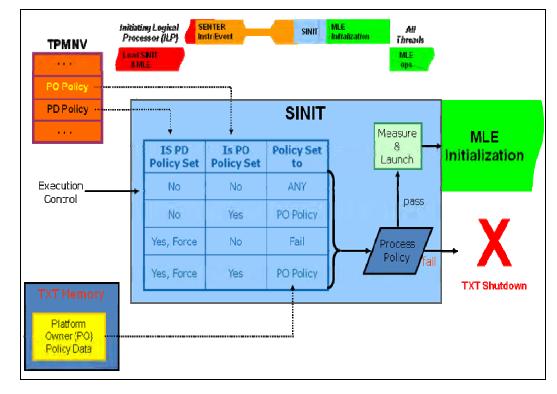

| Figure 2. SINIT LCP Internal Flow          |    |

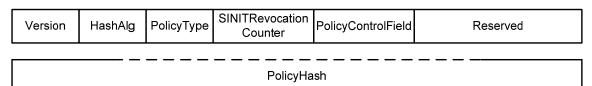

| Figure 3. LCP_POLICY Structure             | 45 |

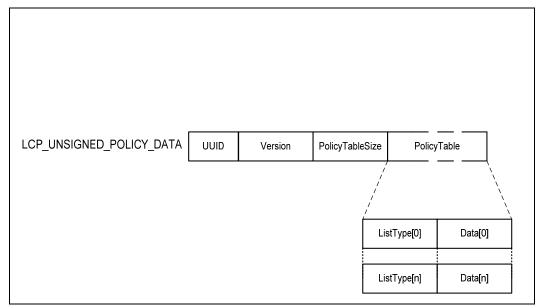

| Figure 4. *_POLICY_DATA Structures         | 46 |

# **Tables**

| Table 1. MLE Header structure                                               | 15 |

|-----------------------------------------------------------------------------|----|

| Table 2. MLE/SINIT Capabilities Field Bit Definitions                       | 16 |

| Table 3. Authenticated Code Module Format                                   | 54 |

| Table 4. AC module Flags Description                                        | 56 |

| Table 5. AC module CodeControl Description                                  |    |

| Table 6. Chipset AC Module Information Table                                | 58 |

| Table 7. Chipset ID List                                                    | 59 |

| Table 8. TXT_ACM_CHIPSET_ID Format                                          | 59 |

| Table 9. Configuration Registers Relevant to MLE                            | 62 |

| Table 10. TXT.STS Bit Definitions                                           | 66 |

| Table 11. TXT.ESTS Bit Definitions                                          | 67 |

| Table 12. TXT.VER.FSBIF Bit Definitions                                     | 67 |

| Table 13. TXT.DIDVID Bit Definitions                                        |    |

| Table 14. TXT.ERRORCODE Register Bit Format                                 | 68 |

| Table 15. Type Field Encodings for Processor-Initiated Intel® TXT Shutdowns | 68 |

| Table 16. TXT.E2STS Register Bit Format                                     | 69 |

| Table 17. TPM Locality Address Mapping                                      | 70 |

| Table 18. Intel <sup>®</sup> Trusted Execution Technology Heap              |    |

| Table 19. BIOS Data Table                                                   | 73 |

| Table 20. OS to SINIT Data Table                                            |    |

| Table 21. SINIT to MLE Data Table                                           | 75 |

| Table 22. SINIT Memory Descriptor Record                                    | 77 |

| Table 23. LCP Error Values                                                  | 81 |

§

# **Revision History**

| Revision<br>Number | Description                                                                                                                                                                                                             | Revision Date |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| -001               | Initial release.                                                                                                                                                                                                        | May 2006      |

| -002               | <ul><li>Established public document number</li><li>Edited throughout for clarity.</li></ul>                                                                                                                             | August 2006   |

| -003               | Added launched environment consideration     Renamed LT to Intel <sup>®</sup> TXT                                                                                                                                       | October 2006  |

| -004               | Updated for production platforms     Use MLE terminology                                                                                                                                                                | August 2007   |

| -005               | <ul> <li>Updated for latest structure versions and new RLP wakeup mechanism</li> <li>Added Launch Control Policy information</li> <li>Removed TEP Appendix</li> <li>Many miscellaneous changes and additions</li> </ul> | June 2008     |

§

# 1 Overview

Intel's technology for safer computing, Intel<sup>®</sup> Trusted Execution Technology (Intel<sup>®</sup> TXT), defines platform-level enhancements that provide the building blocks for creating trusted platforms.

Whenever the word trust is used, there must be a definition of who is doing the trusting and what is being trusted. This enhanced platform helps to provide the authenticity of the controlling environment such that those wishing to rely on the platform can make an appropriate trust decision. The enhanced platform determines the identity of the controlling environment by accurately measuring the controlling software (see Section 1.1).

Another aspect of the trust decision is the ability of the platform to resist attempts to change the controlling environment. The enhanced platform will resist attempts by software processes to change the controlling environment or bypass the bounds set by the controlling environment.

What is the controlling environment for this enhanced platform? The platform is a set of extensions designed to provide a measured and controlled launch of system software that will then establish a protected environment for itself and any additional software that it may execute.

These extensions enhance two areas:

- The launching of the Measured Launched Environment (MLE)

- The protection of the MLE from potential corruption

The enhanced platform provides these launch and control interfaces using Safer Mode Extensions (SMX).

The SMX interface includes the following functions:

- Measured launch of the MLE

- Mechanisms to ensure the above measurement is protected and stored in a secure location

- Protection mechanisms that allow the MLE to control attempts to modify itself

# 1.1 Measurement and Intel<sup>®</sup> Trusted Execution Technology

Intel TXT uses the term *measurement* frequently. Measuring software involves processing the executable such that the result (a) is unique and (b) indicates changes in the executable. A cryptographic hash algorithm meets these needs.

A cryptographic hash algorithm is sensitive to even one-bit changes to the measured entity. A cryptographic hash algorithm also produces outputs that are sufficiently large so the potential for collisions (where two hash values are the same) is extremely small. When the term measurement is used in this specification, the meaning is that the measuring process takes a cryptographic hash of the measured entity.

The controlling environment is provided by system software such as an OS kernel or VMM. The software launched using the SMX instructions is known as the Measured Launched Environment (MLE). MLEs provide different launch mechanisms and increased protection (offering protection from possible software corruption).

# 1.2 Dynamic Root of Trust

A central objective of the Intel TXT platform is to provide a measurement of the launched execution environment.

One measurement is made when the platform boots, using techniques defined by the Trusted Computing Group (TCG). The TCG defines a Root of Trust for Measurement (RTM) that executes on each platform reset; it creates a chain of trust from reset to the measured environment. As the measurement always executes at platform reset, the TCG defines this type of RTM as a Static RTM (SRTM).

Maintaining a chain of trust for a length of time may be challenging for an MLE meant for use in Intel TXT; this is because an MLE may operate in an environment that is constantly exposed to unknown software entities. To address this issue, the enhanced platform provides another RTM with Intel TXT instructions. The TCG terminology for this option is Dynamic Root of Trust for Measurement (DRTM). The advantage of a DRTM (also called the 'late launch' option) is that the launch of the measured environment can occur at any time without resorting to a platform reset. It is possible to launch a MLE, execute for a time, terminate the MLE, execute without virtualization, and then launch the MLE again. One possible sequence is:

- 1. During the BIOS load: (a) launch an MLE for use by the BIOS, (b) terminate the MLE when its work is done, (c) continue with BIOS processing and hand off to an OS.

- 2. Then, the OS loads and launches a different MLE.

In both instances, the platform measures each MLE and ensures the proper storage of the MLE measurement value.

### 1.2.1 Launch Sequence

When launching a MLE, the environment must load two code modules into memory. One module is the MLE. The other is known as an authenticated code (AC) module. The AC module is only in use during the measurement and verification process and is chipset-specific. It is digitally signed by the chipset vendor; the launch process must successfully validate the digital signature before continuing.

With the AC module and MLE in memory, the launching environment can invoke the GETSEC[SENTER] instruction provided by SMX.

GETSEC[SENTER] broadcasts messages to the chipset and other physical or logical processors in the platform. In response, other logical processors perform basic cleanup, signal readiness to proceed, and wait for messages to join the environment created by the MLE. As this sequence requires synchronization, there is an initiating logical processor (ILP) and responding logical processor(s) (RLP(s)).

After all logical processors signal their readiness to join and are in the wait state, the initiating logical processor loads, authenticates, and executes the AC module. The AC module tests for various chipset and processor configurations and ensures the platform has an acceptable configuration. It then measures and launches the MLE.

The MLE initialization routine completes system configuration changes (including redirecting INITs, SMIs, interrupts, etc.); it then issues a new SMX instruction that wakes up the responding logical processors (RLPs) and brings them into the measured environment. At this point, all logical processors and the chipset are correctly configured.

At some later point, it is possible for the MLE to exit and then be launched again, without issuing a system reset.

# 1.3 Storing the Measurement

SMX operation during the launch provides an accurate measurement of the MLE. After creating the measurement, the initiating logical processor stores that measurement in the Trusted Platform Module (TPM), defined by the TCG. An enhanced platform includes mechanisms that ensure that the measurement of the MLE (completed during the launch process) is properly reported to the TPM.

With the MLE measurement in the TPM, the MLE can use the measurement value to protect sensitive information and detect potential unauthorized changes to the MLE itself.

# 1.4 Controlled Take-down

Because the MLE controls the platform, exiting the MLE is a controlled process. The process includes: (a) shutting down any guest VMs if they were created; (b) and ensuring that memory previously used does not leak sensitive information.

The MLE cleans up after itself and terminates the MLE control of the environment. If a VMM was running, the MLE may choose to turn control of the platform over to the software that was running in one of the VMs.

# 1.5 SMX and VMX Interaction

A VM abort may occur while in SMX operation. This behavior is described in the *Intel* 64 and IA-32 Software Developer Manual, Volume 3B. Note that entering authenticated code execution mode or launching of a measured environment affects the behavior and response of the logical processors to certain external pin events.

# 1.6 Authenticated Code Module

To support the establishment of a measured environment, SMX enables the capability of an authenticated code execution mode. This provides the ability for a special code module, referred to as an authenticated code module (AC module), to be loaded into internal RAM (referred to as authenticated code execution area) within the processor. The AC module is first authenticated and then executed using a tamper resistant mechanism.

Authentication is achieved through the use of a digital signature in the header of the AC module. The processor calculates a hash of the AC module and uses the result to validate the signature. Using SMX, a processor will only initialize processor state or execute the AC module if it passes authentication. Since the authenticated code module is held within the internal RAM of the processor, execution of the module can occur in isolation with respect to the contents of external memory or activities on the external processor bus.

# 1.7 Chipset Support

One important feature the chipset provides is DMA protection via Intel® Virtualization Technology (Intel® VT) for Directed I/O (Intel® VT-d). Intel® VT-d, under control of the MLE, allows the MLE to protect itself and any other software such as guest VMs from unauthorized device access to memory. Intel VT-d blocks access to specific physical memory pages and the enforcement of the block occurs for all DMA access to the protected pages. See Chapter 1.10 for more information on DMA protection mechanisms.

The Intel TXT architecture also provides extensions that access certain chipset registers and TPM address space.

Chipset registers that interact with SMX are accessed from two regions of memory by system software using memory read/write protocols. These two memory regions,

Intel TXT Public space and Intel TXT Private space, are mappings to the same set of chipset registers but with different read/write permissions depending on which space the memory access came through. The Intel TXT Private space is not accessible to system software until it is unlocked by SMX instructions.

The storage spaces accessible within a TPM device are grouped by a locality attribute and are a separate set of address ranges from the Intel TXT Public and Private spaces. The following localities are defined:

- Locality 0 : Non-trusted and legacy TPM operation

- Locality 1 : An environment for use by the Trusted Operating System

- Locality 2 : Trusted OS

- Locality 3 : Authenticated Code Module

- Locality 4 : Intel TXT hardware use only

# 1.8 TPM Usage

Intel TXT makes extensive use of the Trusted Platform Module (TPM) defined by the Trusted Computing Group (TCG) in the *TCG TPM Specification, Version 1.2.* The TPM provides a repository for measurements and the mechanisms to make use of the measurements. The system makes use of the measurements to both report the current platform configuration and to provide long-term protection of sensitive information.

The TPM stores measurements in Platform Configuration Registers (PCRs). PCRs provide a storage area that allows an unlimited number of measurements in a fixed amount of space. They provide this feature by an inherent property of cryptographic hashes. Outside entities never write directly to a PCR register, they "extend" PCR contents. The extend operation takes the current value of the PCR, appends the new value, performs a cryptographic hash on the combined value, and the hash result is the new PCR value. One of the properties of cryptographic hashes is that they are order dependent. This means hashing A then B produces a different result from hashing B then A. This ordering property allows the PCR contents to indicate the order of measurements.

Sending measurement values from the measuring agent to the TPM is a critical platform task. The Dynamic Root of Trust for Measurement (DRTM) requires specific messages to flow from the DRTM to the TPM. The Intel TXT DRTM is the GETSEC[SENTER] instruction and the system ensures GETSEC[SENTER] has special messages to communicate to the TPM. These special messages take advantage of TPM localities 3 and 4 to protect the messages and inform the TPM that GETSEC[SENTER] is sending the messages.

# 1.9 PCR Usage

As part of the measured launch, Intel TXT will extend measurements of the elements and configuration values of the dynamic root of trust into certain TPM PCRs. The constituent values of these measurements (indicated below) are provided in the SinitMleData structure described in Appendix C.4.

While the MLE may choose to extend additional values into these PCRs, the values described below are those present immediately after the MLE receives control following the GETSEC[SENTER] instruction.

## 1.9.1 PCR 17

PCR 17 is initialized using the TPM\_HASH\_START/TPM\_HASH\_END sequence. The HASH\_DATA provided in this sequence is the concatenation of the SHA-1 hash of the SINIT ACM that was used in the launch process and the 4 byte value of the SENTER parameters (in EDX and also in SinitMleData.EdxSenterFlags). As part of this sequence, PCRs 17-23 are reset to 0. The hash of SINIT is also stored in the SinitMleData.SinitHash field.

PCR 17 is then extended with the SHA-1 hash of the following items concatenated in this order:

SHA-1 hash of BIOS ACM – SinitMleData.BiosAcmID (20 bytes)

STM opt-in indicator - SinitMleData.MsegValid (8 bytes)

SHA-1 hash of the STM (or all 0s if opt-out) – SinitMleData.StmHash (20 bytes)

LCP Control Field of used policy (PD or PO) – SinitMleData.PolicyControl (4 bytes)

SHA-1 hash of used policy (or all 0s if chosen not to be extended) – SinitMleData.LcpPolicyHash (20 bytes)

MLE-chosen Capabilities (or all 0s if chosen not to be extended) – OsSinitData.Capabilities (4 bytes)

Thus, PCR 17's final value will be:

Extend ( SHA-1( SinitMleData.SinitHash | SinitMleData.EdxSenterFlags ) )

Extend (SHA-1 (SinitMleData.BiosAcm.ID | SinitMleData.MsegValid | SinitMleData.StmHash | SinitMleData.PolicyControl | SinitMleData.LcpPolicyHash | (OsSinitData.Capabilities, 0) ))

Where the Extend() operation is a SHA-1 hash of the previous value in the PCR concatenated with the value being extended (the previous value is 20 bytes of 0s in the case of the first extend to a PCR).

#### 1.9.2 PCR 18

PCR 18 will be extended with the SHA-1 hash of the MLE, as reported in the SinitMleData.MleHash field.

Thus, PCR 18's final value will be:

Extend (SinitMleData.MleHash)

# 1.10 DMA Protection

This chapter briefly describes the two chipset mechanisms that can be used to protect regions of memory from DMA access by busmaster devices. More details on these mechanisms can be found in the External Design Specification (EDS) of the targeted chipset family and Intel<sup>®</sup> *Virtualization Technology for Directed I/O Architecture Specification*.

### 1.10.1 DMA Protected Range (DPR)

The DMA Protected Range (DPR) is a region of contiguous physical memory whose last byte is the byte before the start of TSEG, and which is protected from all DMA access. The DPR size is set and locked by BIOS. This protection is applied to the final physical address after any other translations (e.g. Intel VT-d, GART, etc.).

The DPR covers the Intel TXT heap and SINIT AC Module reserved memory (as specified in the TXT.SINIT.BASE/TXT.SINIT.SIZE registers). On current systems it is 3MB in size, and though this may change in the future it will always be large enough to cover the heap and SINIT regions.

The MLE itself may reside in the DPR as long as it does not conflict with either the SINIT or heap areas. If it does reside in the DPR then it need not be covered by the Intel VT-d Protected Memory Regions.

## 1.10.2 Intel® Virtualization Technology (Intel® VT) for Directed I/O (Intel® VT-d) Protected Memory Regions (PMRs)

The Intel® VT-d Protected Memory Regions (PMRs) are two ranges of physical addresses that are protected from DMA access. One region must be in the lower 4GB of memory and the other must be in the upper 4GB. Either or both may be unused.

The use of the PMRs is not mutually exclusive of DMA remapping. If the MLE enables DMA remapping, it should place the Intel VT-d page tables within the PMR region(s) in order to protect them from DMA activity prior to turning on remapping. While it is not required that PMRs be disabled once DMA remapping is enabled, if the MLE wants to manage all DMA protection through remapping tables then it must explicitly disable the PMR(s).

The MLE may reside within one of the PMR regions. If the MLE is not within the DPR region then it must be within one of the PMR regions, else SINIT will not permit the environment to be launched.

For more details of the PMRs, see the Intel<sup>®</sup> Virtualization Technology for Directed I/O Architecture Specification.

# 1.11 Intel<sup>®</sup> TXT Shutdown

## 1.11.1 Reset Conditions

When an Intel TXT shutdown condition occurs, the processor or software writes an error code indicating the reason for the failure to the TXT.ERRORCODE register. It then writes to the TXT.CMD.RESET command register, initiating a platform reset. After the write to TXT.CMD.RESET, the processor enters a shutdown sleep state with all external pin events, bus or error events, machine check signaling, and MONITOR/MWAIT event signaling masked. Only the assertion of reset back to the processor takes it out of this sleep state. The Intel TXT error code register is not cleared by the platform reset; this makes the error code accessible for post-reset diagnostics.

An Intel TXT shutdown can be generated by the processor during execution of certain GETSEC leaf functions (for example: ENTERACCS, EXITAC, SENTER, SEXIT), where recovery from an error condition is not considered reliable. This situation should be interpreted as an abort of authenticated execution or measured environment launch.

A legacy IA-32 triple-fault shutdown condition is also converted to an Intel TXT shutdown sequence if the triple-fault shutdown occurs during authenticated code execution mode or while the measured environment is active. The same is true for other legacy non-SMX specific fault shutdown error conditions. Legacy shutdown to Intel TXT shutdown conversions are defined as the mode of operation between:

- Execution of the GETSEC functions ENTERACCS and EXITAC

- Recognition of the message signaling the beginning of the processor rendezvous after GETSEC[SENTER] and the message signaling the completion of the processor rendezvous

Additionally, there is a special case. If the processor is in VMX operation while the measured environment is active, a triple-fault shutdown condition that causes a guest exiting event back to the Virtual Machine Monitor (VMM) supersedes conversion to the Intel TXT shutdown sequence. In this situation, the VMM remains in control after the error condition that occurred at the guest level and there is no need to abort processor execution.

Given the above situation, if the triple-fault shutdown occurs at the root level of the MLE or a VMX abort is detected, then an Intel TXT shutdown sequence is signaled. For more details on a VMX abort, see Chapter 23, "VM Exits," in the *Intel 64 and IA-32 Software Developer Manuals, Volume 3B.*

§

# 2 Measured Launched Environment

Intel TXT can be used to launch any type of code. However, this section describes the launch, operation and teardown of a Virtual Machine Monitor (VMM) using Intel TXT; any other code would have a similar sequence.

# 2.1 MLE Architecture Overview

Any Measured Launched Environment (MLE) will generally consist of three main sections of code: the initialization, the dispatch routine, and the shutdown. The initialization code is run each time the Intel TXT environment is launched. This code includes code to setup the MLE on the ILP and join code to initialize the RLPs.

After initialization, the MLE behaves like the unmeasured version would have; in the case of a VMM, this is trapping various guest operations and virtualizing certain processor states.

Finally the MLE prepares for shutdown by again synchronizing the processors, clearing any state and executing the GETSEC[SEXIT] instruction.

Table 1 shows the format of the MLE Header structure which is stored within the MLE image. The MLE Header structure is used by the SINIT AC module to set up the correct initial MLE state and to find the MLE entry point. The header is part of the MLE hash.

| Field          | Offset | Size<br>(bytes) | Description                                                                         |

|----------------|--------|-----------------|-------------------------------------------------------------------------------------|

| UUID           | 0      | 16              | Identifies this structure                                                           |

| HeaderLen      | 16     | 4               | Length of header in bytes                                                           |

| Version        | 20     | 4               | Version number of this structure                                                    |

| EntryPoint     | 24     | 4               | Linear entry point of MLE                                                           |

| FirstValidPage | 28     | 4               | Starting linear address of (first valid page of) MLE                                |

| MleStart       | 32     | 4               | Offset within MLE binary file of first<br>byte of MLE as specified in page<br>table |

| MleEnd         | 36     | 4               | Offset within MLE binary file of last<br>byte of MLE as specified in page<br>table  |

#### Table 1. MLE Header structure

| Capabilities | 40 | 4 | Bit vector of MLE-supported<br>capabilities |

|--------------|----|---|---------------------------------------------|

|--------------|----|---|---------------------------------------------|

**UUID:** This field contains a UUID which uniquely identifies this MLE Header Structure. The UUID is defined as follows:

| ULONG | UUID0; | // 9082AC5A |

|-------|--------|-------------|

| ULONG | UUID1; | // 74A7476F |

| ULONG | UUID2; | // A2555C0F |

| ULONG | UUID3; | // 42B651CB |

HeaderLen: this field contains the length in bytes of the MLE Header Structure.

**Version:** this field contains the version of the MLE header, where the upper two bytes are the major version and the lower two bytes are the minor version. Changes in the major version indicate that an incompatible change in behavior is required of the MLE or that the format of this structure is not backwards compatible. Version 2.0 (20000H) is the currently supported version.

**EntryPoint:** this field is the linear address, within the MLE's linear address space, at which the ILP will begin execution upon completion of the GETSEC[SENTER] instruction.

**FirstValidPage:** this field is the starting linear address of the MLE. This will be verified by SINIT to match the first valid entry in the MLE page tables.

**MieStart / MieEnd:** these fields are intended for use by system software that needs to know which portion of an MLE binary file is the MLE, as defined by its page table. This might be useful for calculating the MLE hash when the entire binary file is not being used as the MLE.

**Capabilities:** this bit vector represents TXT-related capabilities that the MLE supports. It will be used by the SINIT AC module to determine whether the MLE is compatible with it and as needed for any optional capabilities. The currently defined bits for this are:

| Bit position | Description                                                                      |  |

|--------------|----------------------------------------------------------------------------------|--|

| 0            | Support for GETSEC[WAKEUP] for RLP wakeup (1)                                    |  |

|              | All MLEs should support this.                                                    |  |

| 1            | Support for RLP wakeup using MONITOR address<br>(SinitMleData.RlpWakeupAddr) (1) |  |

|              | All MLEs should support this.                                                    |  |

| 31:2         | Reserved (must be 0)                                                             |  |

#### Table 2. MLE/SINIT Capabilities Field Bit Definitions

# 2.2 MLE Launch

At some point system software will start an Intel TXT environment. This may be done at operating system loader time or could be done after the operating system boots. From this point on we will assume that the operating system is starting the Intel TXT environment and refer to this code as the system software.

After the measured environment startup, the application processors (RLPs) will not respond to SIPIs as they did before SENTER. Once the measured environment is launched, the RLPs cannot run the real-mode MP startup code. An alternative MP startup algorithm will need to be developed. The new MP startup algorithm would not require the RLPs to leave protected mode with paging on. The OS may also be required to detect whether a measured environment has been established and use this information to decide which MP startup algorithm is appropriate (the standard MP startup algorithm or the modified algorithm).

This section shows the pseudocode for preparing the system for the SMX measured launch. The following describes the process in a number of sub-sections:

- Intel TXT detection and processor preparation

- Detection of previous errors

- Loading the SINIT AC module

- Loading the MLE and processor rendezvous

- Performing a measured launch

# 2.2.1 Intel<sup>®</sup> TXT Detection and Processor Preparation

This action is only performed by the ILP.

Lines 1 - 4: Before attempting to launch the measured environment, the system software should check that the processor supports VMX and SMX (the check for VMX support is not necessary if the environment to be launched will not use VMX). For details on detecting and enabling VMX see chapter 19, "Introduction to Virtual-Machine Extensions", in the *Intel 64 and IA-32 Software Developer Manuals, Volume 3B.* For details on detecting and enabling SMX support see chapter 6, "Safer Mode Extensions Reference", in the *Intel 64 and IA-32 Software Developer Manuals, Volume 2B*.

Lines 5 - 9: System software should check that the chipset supports Intel TXT prior to launching the measured environment. The presence of the Intel TXT chipset can be detected by executing GETSEC[CAPABILITIES] with EAX=0 & EBX=0. This instruction will return the 'Intel TXT Chipset' bit set in EAX if an Intel TXT chipset is present. The processor must enable SMX before executing the GETSEC instruction.

Lines 10 – 12: System software should also verify that the processor supports all of the GETSEC instruction leaf indices that will be needed. The minimal set of instructions required will depend on the system software and MLE, but is most likely SENTER, SEXIT, WAKEUP, SMCTRL, and PARAMETERS. The supported leaves are indicated in the EAX register after executing the GETSEC[CAPABILITIES] instruction as indicated above.

#### Listing 1. Intel<sup>®</sup> TXT Detection Pseudocode

//

```

// Intel TXT detection

11

1. CPUID(EAX=1);

2. IF (SMX not supported) OR (VMX not supported) {

3.

Fail measured environment startup;

4.}

11

// Enable SMX on ILP & check for Intel TXT chipset

11

5. CR4.SMXE = 1;

6.GETSEC[CAPABILITIES];

7. IF (Intel TXT chipset NOT present) {

8.

Fail measured environment startup;

9.}

10.IF (All needed SMX GETSEC leaves are NOT supported) {

Fail measured environment startup;

11.

12.

```

## 2.2.2 Detection of Previous Errors

In order to prevent a cycle of failures or system resets, it is necessary for the system software to check for errors from a previous launch. Errors that are detected by system software prior to executing the GETSEC[SENTER] instruction will be specific to that software and, if persisted, will be in a manner specific to the software. Errors generated during execution of the GETSEC[SENTER] instruction result in a system reset and the error code being stored in the TXT.ERRORCODE register. Possible remediation steps are described in section 4.2.

Lines 1 - 3: The error code from an error generated during the GETSEC[SENTER] instruction is stored in the TXT.ERRORCODE register, which is persistent across soft resets. A non-zero value indicates an error. Error codes are specific to an SINIT AC module and can be found in a text file that is distributed with the module.

Lines 4 - 6: If there was a TXT reset event, either as the result of an error during the GETSEC[SENTER] instruction or specifically generated by an MLE, the TXT\_RESET.STS bit of the TXT.ESTS register will be set. In order to maintain TXT integrity, the GETSEC[SENTER] instruction will fail if this bit is set. System software should detect this condition as early as possible and, after taking the appropriate remediative action, power cycle the system to clear this bit and permit a launch.

#### Listing 2. Error Detection Pseudocode

```

//

// Detect previous GETSEC[SENTER] failures

//

1. IF (TXT.ERRORCODE != 0) {

2. Take remediative action;

3. }

//

// Detect previous TXT Reset

```

```

//

4.IF (TXT.ESTS[TXT_RESET.STS] != 0) {

5. Power-cycle system;

6.}

```

## 2.2.3 Loading the SINIT AC Module

This action is only performed by the ILP.

BIOS may already have the correct SINIT AC module loaded into memory or system software may need to load the SINIT code from disk into memory. The system software may determine if a SINIT AC module is already loaded by examining the preferred SINIT load location (see below) for a valid SINIT AC module header.

System software should always use the most recent version of the SINIT AC module available to it. It can determine this by comparing the Date fields in the AC module headers.

System software should also match a prospective SINIT AC module to the chipset before loading and attempting to launch the module. This is described in the next two sections of this document.

System software owns the policy for deciding which SINIT module to load. It must load the previously loaded SINIT AC module in order to unseal data sealed to a previously launched environment. If an SINIT AC module is to be changed (e.g. upgraded to the latest version), the system software must allow the user to migrate secrets prior to loading the new SINIT AC module.

The BIOS reserves a region of physically contiguous memory for the SINIT AC module, which it specifies through the TXT.SINIT.BASE and TXT.SINIT.SIZE Intel TXT configuration registers. By convention, 128 KBytes of physically contiguous memory is allocated for the purpose of loading the SINIT AC module. System software must use this region for any SINIT AC module that it loads.

The SINIT AC module must be located on a 4 KByte aligned memory location. The SINIT AC module must be mapped WB using the MTRRs and all other memory must be mapped to one of the supportable memory types returned by GETSEC[PARAMETERS]. The MTRRs which map the SINIT AC module must not overlap more than 4 KBytes of memory beyond the end of the SINIT AC image. See the GETSEC[ENTERACCS] instruction and the Authenticated Code Module Format, Appendix A.1, for more details on these restrictions.

The pages containing the SINIT AC module image must be present in memory before attempting to launch the measured environment. The SINIT AC module image must be loaded below 4 GBytes. System software should check that the SINIT AC module will fit within the AC execution region as specified by the GETSEC[PARAMETERS] leaf. System software should not utilize the memory immediately after the SINIT AC module up to the next 4 KByte boundary. On certain Intel TXT implementations, execution of the SINIT AC module will corrupt this region of memory.

#### 2.2.3.1 Matching an AC Module to the Chipset

As part of system software loading an SINIT AC module, the system software should first verify that the file to be loaded is really an SINIT AC module. This may be done at installation time or runtime. Lines 1 - 10 in Listing 3 below show how to do this.

Each AC module is designed for a specific chipset or set of chipsets. Software can examine the Chipset ID List embedded in the AC module binary to determine which chipsets an AC module supports. Software should read the chipset's TXT.DIDVID register and parse the Chipset ID List to find a matching entry. Attempting to execute an AC module that does not match the chipset's TXT.DIDVID register will result in a failure of the AC module to complete normal execution and an Intel TXT Shutdown.

Lines 11 - 26 in the following pseudocode show how to check for a valid match between a chipset and an AC module image.

#### Listing 3. AC Module Matching Pseudocode

```

// see Table 3

TXT_ACM_HEADER

*AcmHdr;

TXT CHIPSET ACM INFO TABLE

*InfoTable;

// see Table 6

11

// Find the Chipset AC Module Information Table

11

1. AcmHdr = (TXT_ACM_HEADER *)AcmImageBase;

2.UserAreaOffset = (AcmHdr->HeaderLen + AcmHdr->ScratchSize)*4;

3. InfoTable = (TXT CHIPSET ACM INFO TABLE *)(AcmBase +

UserAreaOffset);

11

// Verify image is really an AC module

11

1. IF (InfoTable->UUID0 != 0x7FC03AAA) OR

2. (InfoTable->UUID1 != 0x18DB46A7) OR

3.

(InfoTable->UUID2 != 0x8F69AC2E) OR

4. (InfoTable->UUID3 != 0x5A7F418D) {

5.

Fail: not an AC module;

6. }

11

// Verify it is an SINIT AC module

11

7. IF (AcmHdr->ModuleType != 2) OR

8.

(InfoTable->ChipsetACMType != 1) {

9.

Fail: not an SINIT AC module;

10.}

11

// Match AC module to system chipset

11

LIST *ChipsetIdList; // see Table 7

*ChipsetId; // see Table 8

TXT_ACM_CHIPSET_ID_LIST

TXT_ACM_CHIPSET_ID

```

```

11.ChipsetIdList = (TXT_ACM_CHIPSET_ID_LIST *)

(AcmImageBase + InfoTable->ChipsetIdList);

11

// Search through all ChipsetId entries and check for a match.

11

12.FOR (i = 0; i < ChipsetIdList->Count; i++) {

13.

11

// Check for a match with this ChipsetId entry.

14.

15.

11

16.

ChipsetId = ChipsetIdList->ChipsetId[i];

IF ((TXT.DIDVID[VID] == ChipsetId->VendorId) &&

17.

18.

(TXT.DIDVID[DID] == ChipsetId->DeviceId) &&

19.

((((ChipsetId->Flags & 0x1) == 0) &&

20.

(TXT.DIDVID[RID] == ChipsetId->RevisionId)) ||

21.

(((ChipsetId->Flags & 0x1) == 0x1) &&

22.

(TXT.DIDVID[RID] & ChipsetId->RevisionId != 0)))) {

23.

AC module matches system chipset;

24.

}

25.}

26.AC module does not match system chipset;

```

#### 2.2.3.2 Verifying Compatibility of SINIT with the MLE

Over time, new features and capabilities may be added to the SINIT AC module that can be utilized by an MLE that is aware of those features. Likewise, features or capabilities may be added that *require* an MLE to be aware of them in order to interoperate properly. In order to expose these features and capabilities and permit the MLE and SINIT to determine whether they support a compatible set, the MLE header contains a Capabilities field (see Table 1) that corresponds to the Capabilities field in the SINIT AC module Information Table (see Table 6).

In addition, the MinMleHeaderVer field in the AC module Information Table allows SINIT to indicate that it requires a certain minimal version of an MLE. This allows for new behaviors or features that require support from the MLE, but which older MLEs would not be aware of.

Listing 4 shows the pseudocode for the MLE to determine if it is compatible with the provided SINIT AC module.

Whiles lines 4 – 6 may be redundant with current SINIT AC modules if the MLE supports both RLP wakeup mechanisms, this permits graceful handling of future changes.

#### Listing 4. SINIT/MLE Compatibility Pseudocode

```

//

// Check that SINIT supports this version of the MLE

//

1. IF (InfoTable->MinMleHeaderVer > MleHeader.Version) {

2. Fail: SINIT requires a newer MLE

3. }

//

// Check that the known RLP wakeup mechanisms are supported

//

4. IF (MLE does NOT support at least one RLP wakeup mechanism

specified in InfoTable->Capabilities) {

5. Fail: RLP wakeup mechanisms are incompatible

6. }

```

#### 2.2.4 Loading the MLE and Processor Rendezvous

#### 2.2.4.1 Loading the MLE

System software allocates memory for the MLE and MLE page table. The MLE is not required to be loaded into physically contiguous memory. The pages containing the MLE image must be pinned in memory and all these pages must be located in physical memory below 4 GBytes.

System software creates an MLE page table structure to map the entire MLE image. The pages containing the MLE page tables must be pinned in memory prior to

launching the measured environment. The MLE page table structure must be in the format of the IA-32 Physical Address Extension (PAE) page table structure.

The MLE page table has several special requirements:

- The MLE page tables may contain only 4 KByte pages.

- A breadth-first search of page tables must produce increasing physical addresses.

- Neither the MLE nor the page tables may overlap certain regions of memory:

- device memory (PCI, PCIe\*, etc.)

- addresses between [640k, 1M) or above Top of Memory (TOM)

- ISA hole (if enabled)

- the Intel TXT heap or SINIT memory regions

- Intel VT-d DMAR tables

- There may not be any invalid (not-present) page table entries after the first valid entry (i.e. there may not be any gaps in the MLE's linear address space).

- The Page Directories must be in a lower physical address than the Page Tables.

- The Page-Directory-Pointer-Table must be in a lower physical address than the Page-Directories.

- The page table pages must be in lower physical addresses than the MLE.

Later, the SINIT AC module will check that the MLE page table matches these requirements before calculating the MLE digest. The second rule above implies that the MLE must be loaded into physical memory in an ordered fashion: a scan of MLE virtual addresses must find increasing physical addresses. The system software can order its list of physical pages before loading the MLE image into memory.

The MLE is not required to begin at linear address 0. There may be any number of invalid/not-present entries in the page table prior to the beginning of the MLE pages (i.e. first valid page). The starting linear address should be placed in the FirstValidPage field of the MLE header structure (see Section 2.1).

If the MLE will use this page table after launch then it needs to ensure that the entry point page is identity-mapped so that when it enables paging post-launch, the physical address of the instruction after paging is enabled will correspond to its linear address in the paged environment.

System software writes the physical base address of the MLE page table's page directory to the Intel TXT Heap. The size in bytes of the MLE image is also written to the Intel TXT Heap; see Appendix C.

# 2.2.4.2 Intel<sup>®</sup> Trusted Execution Technology Heap Initialization

Information can be passed from system software to the SINIT AC module and from system software to the MLE using the Intel TXT Heap. The SINIT AC module will also use this region to pass data to the MLE.

The system software launching the measured environment is responsible for initializing the following in the Intel TXT Heap memory (this initialization must be completed before executing GETSEC[SENTER]):

- Initialize contents of the Intel TXT Heap Memory (see Appendix C)

- Initialize contents of the OsMleData (see Appendix C) and OsMleDataSize (with the size of the OsMleData field + 8H) fields.

- Initialize contents of the OsSinitData (see Appendix C.3) and OsSinitDataSize (with the size of the OsSinitData field + 8H) fields.

The OsMleData structure has fields for specifying regions of memory to protect from DMA (PMR Low/High Base/Size) using Intel VT-d. As described in Chapter 1.10, the MLE must be protected from DMA by being contained within either the DMA Protected Range (DPR) or one of the Intel VT-d Protected Memory Regions (PMRs). If the MLE resides within the DPR then the PMR fields of the OsMleData structure may be set to 0. Otherwise, these fields must specify a region that contains the MLE and the page tables. However, the PMR fields can specify a larger region (and separate region, since there are two ranges) than just the MLE if there is additional data that should be protected.

If the system software is using Intel VT-d DMA remapping to protect areas of memory from DMA then it must disable this before it executes GETSEC[SENTER]. In order to do this securely, system software should determine what PMR range(s) are necessary to cover all of the address range being DMA protected using the remapping tables. It should then initialize the PMR(s) appropriately and enable them before disabling remapping. The PMR values it provides in the OsSinitData PMR fields must correspond to the values that it has programmed. Once the MLE has control, it can re-enable remapping using the previous tables (after validating them).

If the MLE or subsequent code will be enabling Intel VT-d DMA remapping then the DMAR information that will be needed should be protected from malicious DMA activity until the remapping tables can be established to protect it. The SINIT AC module makes a copy of the DMAR tables in the SinitMleData region (located at an offset specified by the SinitVtdDmarTable field). Because this region is within the TXT heap, it is protected from DMA by the DPR. If the MLE or subsequent code does not use this copy of the DMAR tables, then it should protect the original tables (within the ACPI area) with the PMR range specified to SINIT. Likewise, the memory range used for the remapping tables should also be protected with the PMRs until remapping is enabled.

#### 2.2.4.3 Rendezvousing Processors and Saving State

Line 1: If launching the measured environment after operating system boot, then all processors should be brought to a rendezvous point before executing GETSEC[SENTER]. At the rendezvous point each processor will set up for GETSEC[SENTER] and save any state needed to resume after the measured launch. If processors are not rendezvoused before executing SENTER, then the processors that did not rendezvous will lose their current operating state including possibly the fact that an in-service interrupt has not been acknowledged.

Lines 2 – 6: All processors check that they support SMX and enable SMX in CR4.SMXE.

Line 7: Log and clear any pending Machine Checks.

Line 8: Check that certain CRO bits are in the required state for a successful measured environment launch.

Line 9: System software allocates memory to save its state for restoration post measured launch. The OsMleData portion of the Intel TXT Heap has been reserved for this purpose (see Appendix C.1), though the size must be set appropriately for the memory to be available.

Line 10: The BSP (the ILP) saves enough state in memory to allow a return to OS execution after the measured launch and then continues launch execution. The BSP is the processor with IA32\_APIC\_BASE MSR.BSP = 1. The remaining Intel TXT processors (RLPs) save enough state in memory to allow return to OS execution after measured launch then execute HLT or spin waiting for transition to the measured environment.

Certain MSRs are modified by executing the GETSEC[SENTER] instruction. For example, bits within the IA32\_MISC\_ENABLE and IA32\_DEBUGCTL MSRs are set to predetermined values. It may be desirable to restore certain bits within these MSRs to their pre-launch state after the MLE launch. If this is desired, then before executing GETSEC[SENTER], software should save the contents of these MSRs in the OsMleData area. The launched software can restore the original values into these MSRs after the GETSEC[SENTER] returns or, alternatively, the MLE can restore these MSRs with their original values during MLE initialization.

It is expected that most MLEs will want to restore the MTRR and IA32\_MISC\_ENABLE MSR states after the MLE launch, to provide optimal performance of the system.

#### Listing 5. Pseudocode for Rendezvousing Processors and Saving State

```

1. Rendezvous all processors;

11

// The following code is run on all processors

11

// Enable SMX

11

2. CPUID(EAX=1);

3. IF (SMX not supported) OR (VMX not supported) {

4.

Fail measured environment startup;

5. } ELSE {

6.

CR4.SMXE = 1;

7.}

8. Clear Machine Check Status Registers;

9. Ensure CR0.CD=0, CR0.NW=0, and CR0.NE=1;

11

// Save current system software state in Intel TXT Heap

11

10.Allocate memory for OsMleData;

11.Fill in OsMleData with system software state (including MTRR

and IA32_MISC_ENABLE MSR states);

```

### 2.2.5 Performing a Measured Launch

#### 2.2.5.1 MTRR Setup Prior to GETSEC[SENTER] Execution

System software must set up the variable range MTRRs to map all of memory (except the region containing the SINIT AC module) to one of the supported memory types as returned by GETSEC[PARAMETERS], before executing GETSEC[SENTER]. System software first saves the current MTRR settings in the OsMleData area and verifies that the default memory type is one of the types returned by GETSEC[PARAMETERS] (default memory type is specified in the IA32\_MTRR\_DEF\_TYPE MSR). Next the variable range MTRRs are set to map the SINIT AC module as WB. The SINIT AC module must be covered by the MTRRs such that no more than (4K-1) bytes after the module are mapped WB. For example, if an SINIT AC module is 11K bytes in size, an 8K and a 4K or three 4K MTRRs should be used to map it, not a single 32K MTRR. Any unused variable range MTRRs should have their valid bit cleared.

Listing 6 shows the pseudocode for correctly setting the ILP and RLP MTRRs. This code follows the recommendation in the IA-32 Software Developer's Manual.

After MTRR setup is complete, the RLPs mask interrupts (by executing CLI), signal the ILP that they have interrupts masked, and execute halt. Before executing GETSEC[SENTER], the ILP waits for all RLPs to indicate that they have disabled their interrupts. If the ILP executed a GETSEC[SENTER] while an RLP was servicing an interrupt, the interrupt servicing would not complete, possibly leaving the interrupting device unable to generate further interrupts.

#### Listing 6. MTRR Setup Pseudocode

```

11

// Pre-MTRR change

11

1. Disable interrupts (via CLI);

2. Wait for all processors to reach this point;

3. Disable and flush caches (i.e. CRO.CD=1, CRO.NW=0, WBINVD);

4. Save CR4

5. IF (CR4.PGE == 1) {

6.

Clear CR4.PGE

7.}

8. Flush TLBs

9. Disable all MTRRs (i.e. IA32_MTRR_DEF_TYPE.e=0)

11

// Use MTRRs to map SINIT memory region as WB, all other regions

// are mapped to a value reported supportable by

// GETSEC[PARAMETERS]

11

10.Set default memory type (IA32_MTRR_DEF_TYPE.type) to one

reported by GETSEC[PARAMETERS];

11.Disable all fixed MTRRs (IA32_MTRR_DEF_TYPE.fe=0);

12.Disable all variable MTRRs (clear valid bit);

13.Read SINIT size from the SINIT AC header;

```

```

14. Program variable MTRRs to cover the AC execution region,

memtype=WB (re-enable each one used);

11

// Post-MTRR changes

11

15.Flush caches (WBINVD);

16.Flush TLBs;

17.Enable MTRRs (i.e. MTRRdefType.e=1);

18.Enable caches (i.e. CRO.CD=0, CRO.NW=0);

19.Restore CR4;

20.Wait for all processors to reach this point;

21.Enable interrupts;

11

// RLPs stop here

11

22.IF (IA32_APIC_BASE.BSP != 1) {

23.

CLI;

set bit indicating we have interrupts disabled;

24.

25.

HLT;

26.}

27.Wait for all RLPs to signal that they have their interrupts

disabled

```

#### 2.2.5.2 Selection of Launch Capabilities

System software must select the capabilities that it wishes to use for the launch. It must choose a subset of the capabilities supported by the SINIT AC module. For mandatory capabilities, such as the RLP wakeup mechanism, one of the supported options must be chosen.

28.OsSinitData.Capabilities = selected capabilities;

#### 2.2.5.3 TPM Preparation

System software must ensure that the TPM is ready to accept commands and that there is no currently active locality (TPM.ACCESS\_x.activeLocality bit is clear for all localities) before executing the GETSEC[SENTER] instruction.

29.Read TPM Status Register until it is ready to accept a command 32.For all localities x, ensure that ACCESS\_x.activeLocality is 0

Intel® Trusted Execution Technology

#### 2.2.5.4 Intel<sup>®</sup> Trusted Execution Technology Launch

The ILP is now ready to launch the measuring process. System software executes the GETSEC[SENTER] instruction. See chapter 6, "Safer Mode Extensions Reference", in the *Intel 64 and IA-32 Software Developer Manuals, Volume 2B* for the details of GETSEC[SENTER] operation.

30.EBX = Physical Base Address of SINIT AC Module

31.ECX = size of the SINIT AC Module in bytes

32.EDX = 0

33.GETSEC[SENTER]

# 2.3 MLE Initialization

This section describes the initialization of the MLE. Listing 7 shows the pseudocode for MLE initialization.

The MLE initialization code is executed on the ILP when the SINIT AC module executes the GETSEC[EXITAC] instruction—the MLE initialization code is the first MLE code to run after GETSEC[SENTER] and within the measured environment. The SINIT AC module obtains the MLE initialization code entry point for the MLE EntryPoint field in the MLE Header data structure whose address is specified in the OsSinitData entry in the Intel TXT Heap. The MLE initialization code is responsible for setting up the protections necessary to safely launch any additional environments or software. The initialization includes Intel TXT hardware initialization, waking and initializing the RLPs, MLE software initialization and initialization of the STM (if one is being used). Section 2.3 describes the details of MLE initialization.

During MLE initialization, the ILP executes the GETSEC[WAKEUP] instruction, bringing all the RLPs into the MLE initialization code. Each RLP gets its initial state from the MLE JOIN data structure. The ILP sets up the MLE JOIN data structure and loads its physical address in the TXT.MLE.JOIN register prior to executing GETSEC[WAKEUP]. Generally the RLP initialization code will be very similar to the ILP initialization code.

If the MLE restores any state from the environment of the launching system software then it must first validate this state before committing it. This is because state from the environment prior to the GETSEC[SENTER] instruction is not considered trustworthy and could lead to loss of MLE integrity.

Lines 1 – 8: The MLE loads CR3 with the MLE page directory physical address and enables paging. The SINIT AC module has just transferred control to the MLE with paging off, now the MLE must setup its own environment. The MLE's GDT is loaded at line 3 and the MLE does a far jump to load the correct MLE CS and cause a fetch of the MLE descriptor from the GDT. At line 5 a stack is setup for the MLE initialization routine and, at line 6, the MLE segment registers are loaded. Next the MLE loads its IDT and initializes the exception handlers.

All of the instructions and data that are used before paging is enabled must reside on the same physical page as the MLE entry point and must access data with relative addressing. This is because the page tables may have been subverted by untrusted

code prior to launch and so the MLE entry point's page may have been copied to a different physical address than the original. The MLE must also verify that this page is identity mapped prior to enabling paging (to ensure that the linear address of the instruction following enabling of paging is the same as its physical address).

If the MLE does not enable paging then it must also validate that the physical addresses specified in the page table used for the launch are the expected ones. And as above, it must do this in code that resides on the same physical page as the MLE entry point and uses only relative addressing. The reason for this validation is that the page table could have been altered to place the MLE pages at different physical addresses than expected, without having altered the MLE measurement.

Because the MLE page table that was used for measurement does not contain pages other than those belonging to the MLE, if it wishes to continue to run in a paged environment it will need to either extend the page tables to map the additional address space needed (e.g. TXT configuration space, etc.) or to create new page tables. This should be done after it has finished establishing a safe environment. The cacheability requirements for the address space of any MLE-established page tables must follow the guidelines below.

Line 9: The MLE checks the MTRRs which were saved in the OsMleData area of the Intel TXT Heap (see Appendix C). It looks for overlapping regions with invalid memory type combinations and variable MTRRs describing non-contiguous memory regions. If either of these checks fails the MLE should fail the measured launch or correct the failure.

Before the original MTRRs are restored, the MLE must ensure that all its own pages will be mapped with defined memory types once the variable MTRRs are enabled. The MLE must ensure that the combined memory type as specified by the page table entry and variable MTRRs results in a defined memory type.

If using the STM opt-in option, the MLE must check that the MSEG region of memory is covered by a variable MTRR with memory type UC. The MLE must ensure that this MTRR contains memory type UC during the entire operation of the Intel TXT environment.

The MLE must also ensure that the TXT Device Space (0xFED20000 – 0xFED4FFFF) is mapped as UC so that accesses to these addresses will be properly handled by the chipset.

Line 10: The MLE should check that the system memory map that it will use is consistent with the memory regions and types as specified in the Memory Descriptor Records (MDRs) returned in the SinitMleData structure. Alternately, the MLE may use this table as its map of system memory. This check is necessary as the system memory map is most likely generated by untrusted software and so could contain regions that, if used for trusted code or secrets, might lead to compromise of that data. If the MLE will be using PCI Express\* devices, it should verify that it is accessing their configuration space through the address range specified by the PCIE MDR type (3).

Line 11: The MLE should also verify that the Intel VT-d PMR settings that were used by SINIT to program the Intel VT-d engines, as specified in the OsSinitData structure, contain the expected values. While the MLE can only be launched if the settings cover itself and its page tables (or the pages fall within the DPR), settings beyond these regions could have been subverted by untrusted code prior to the launch.

Line 12: The MLE should restore the IA32\_MISC\_ENABLE MSR to the value saved in the OsMleData structure. This MSR was set to predefined values as part of SENTER in order to provide a more consistent environment to the authenticated code module. Most MLEs should be able to safely restore the previous value without any need to verify it.

Lines 13 – 17: If this is the ILP then the MLE does the one-time initialization, builds the MLE JOIN data structure and wakes the RLPs. This structure contains the physical addresses of the MLE entry point and the MLE GDT, along with the MLE GDT size. The ILP writes the physical address of this structure to the TXT.MLE.JOIN register. An RLP will read the startup information from the MLE JOIN data structure when it is awakened. The MLE writer should ensure that the MLE JOIN data structure does not cross a page boundary between two non-contiguous pages. The MLE image must be built or loaded such that its GDT is located on a single page. Enough of the RLP entry point code must be on a single page to allow the RLPs to enable paging.

Lines 18 – 27: The MLE must look at the OsSinitData.Capabilities field to see which RLP wakeup mechanism was chosen by the pre-SENTER code and thus used by SINIT. If the MLE wants to enforce that certain capabilities or wakeup mechanism was used then it can choose to error if it finds that not to be the case. For future compatibility, MLEs should support both RLP wakeup mechanisms.

Line 30: The MLE checks several items to ensure they are consistent across all processors:

- All processors must have consistent SMM Monitor Control MSR settings. The processors must all be opt-in and have the same MSEG region or the processors must be all opt-out. The MLE must also check that the MSEG region in the SMM Monitor Control MSR matches what is contained in the TXT.MSEG.BASE register.

- Ensure all processors have compatible VMX features. The compatible VMX features will depend on the specific MLE implementation. For example, some implementation may require all processors support Virtual Interrupt Pending.

- Ensure all processors have compatible feature sets. Some MLE implementations may depend on certain feature being available on all processors. For example, some MLE implementation may depend on all processors supporting SSE2.

- Ensure all processors have a valid microcode patch loaded or all processors have the same microcode patch loaded. This check will depend on the specific MLE implementation. Some MLE implementations may require the same patch be loaded on all processors, other MLE implementations may contain a microcode patch revocation list and require all processors have a microcode patch loaded which is not on the revocation list.

Line 31: The MLE must wakeup the RLPs while the memory type for the SINIT AC module region is writeback. This is a requirement of the MONITOR mechanism for RLP wakeup. Since this is not guaranteed to be true of the original MTRRs, it is safest to wait until after the RLPs have been awakened before restoring the MTRRs to their pre-SENTER values. Alternatively, the MLE could ensure that this is the case and adjust the MTRRs if it is not. It could then restore the MTRRs before waking the RLPs. In either case, when restoring the MTRRs they should be made the same for each processor.

Line 32: The MLE enables VMX in the CR4 register. This is required before any VMX instruction can be executed.

Line 33: The MLE allocates and sets up the root controlling VMCS then executes VMXON, enabling VMX root operation.

Lines 34 – 38: The MLE sets up the guest VM. At line 34 the MLE allocates memory for the guest VMCS. This memory must be 4K byte aligned. The MLE executes VMCLEAR with a pointer to this VMCS in order to mark this VMCS clear and allow a VMLAUNCH of the guest VM. At line 36 the MLE executes VMPTRLD so that it can initialize the VMCS at line 37. Now at line 38 the guest VM is launched for the first time.

Note: On the last extend of the TPM by the SINIT AC module, it may not wait to see if the command is complete – so the MLE needs to make sure that the TPM is ready before using it.

#### Listing 7: MLE Initialization Pseudocode

```

11

// MLE entry point - ILP and RLP(s) enter here

11

1. Load CR3 with MLE page table pointer (OsSinitData.MLE

PageTableBaseLow/High);

2. Enable paging;

3. Load the GDTR with the linear address of MLE GDT;

4. Long jump to force reload the new CS;

5. Load MLE SS, ESP;

6. Load MLE DS, ES, FS, GS;

7. Load the IDTR with the linear address of MLE IDT;

8. Initialize exception handlers;

11

// Validate state

11

9. Check MTRR settings from OsMleData area;

10.Validate system memory map against MDRs

11.Validate VT-d PMR settings against expected values

12.Restore IA32_MISC_ENABLE MSR from OsMleData

11

// Wake RLPs

11

13.IF (ILP) {

Initialize memory protection and other data structures;

14.

15.

Build JOIN structure;

TXT.MLE.JOIN = physical address of JOIN structure;

16.

17.

IF (RLP exist) {

18.

IF (OsSinitData.Capabilities is set to MONITOR

wakeup mechanism) {

19.

SinitMleData.RlpWakeupAddr = 1;

20.

}

ELSE IF (OsSinitData.Capabilities is set to GETSEC

21.

wakeup mechanism) {

22.

GETSEC[WAKEUP];

23.

}

```

```

24

ELSE {

25.